Изобретение относится к автоматике и вычислительной технике и может быть использовано для разработки микросхем троичной логики, позволяющей повысить производительность устройств, унифицированных с микросхемами двоичной логики.

Известен базовый логический элемент (ЛЭ) двоичной логики «И-НЕ». Наиболее распространенными аналогами являются, например, ЛЭ, выполненные по ТТЛ-технологии [1] - Шило В.Л., Популярные цифровые микросхемы, Челябинск, «Металлургия», 1988. Он содержит (Рис.1.20, с.36 [1]): общую шину, шину источника положительного напряжения питания, входную и выходную шины, четыре резистора, один диод и четыре транзистора, соединенные по схеме ЛЭ «И-НЕ». Этот ЛЭ не может выполнять функцию «И» в троичной логике и обладает повышенным потреблением энергии. За прототип изобретения принят базовый ЛЭ двоичной логики «И-НЕ», выполненный по КМОП-технологии (Рис.2.8, с.200 [1]).

ЛЭ «И-НЕ» (Фиг.1) содержит: общую шину 1, шину 2 источника положительного напряжения, первую 4 и вторую 5 входные шины и четыре МОП-транзистора 8, 9, 10 и 11. Первый 8 и второй 9 транзисторы с каналом р-проводимости, третий 10 и четвертый 11 с каналом n-проводимости. Транзисторы 8 и 9 соединены параллельно и подключены к шине питания 2 с одной стороны и к выходной шине 16 с другой. Транзисторы 10 и 11 соединены последовательно и подключены к выходной шине 16 и общей шине. ЛЭ работает следующим образом. Если на обоих входах присутствуют напряжения высокого уровня, то оба транзистора р-проводимости закрыты, транзисторы n-проводимости открыты и на выходной шине 16 будет напряжение низкого уровня. При всех других комбинациях напряжений на входных шинах один из транзисторов р-проводимости или оба эти транзистора будут открыты, а транзисторы n-проводимости (по одному или оба) закрыты, и на выходной шине будет напряжение высокого уровня. Таким образом, этот элемент выполняет функцию «И» с отрицанием в соответствии с таблицей истинности 1.

В двоичной логике используют однополярные сигналы алфавита {0, 1} положительной логики или {0, -1} отрицательной двоичной логики.

В троичной логике используют биполярные сигналы алфавита {-1, 0, 1}.

Функция ЛЭ троичного логики «И» может быть представлена таблицей истинности 2.

1 0 0

0 0 0

0 0-1

Логические элементы двоичной логики не реализуют такую функцию троичной логики. Техническим результатом изобретения является увеличение производительности устройств логики при их использовании в вычислительной технике, по сравнению с аналогичными устройствами двоичной логики.

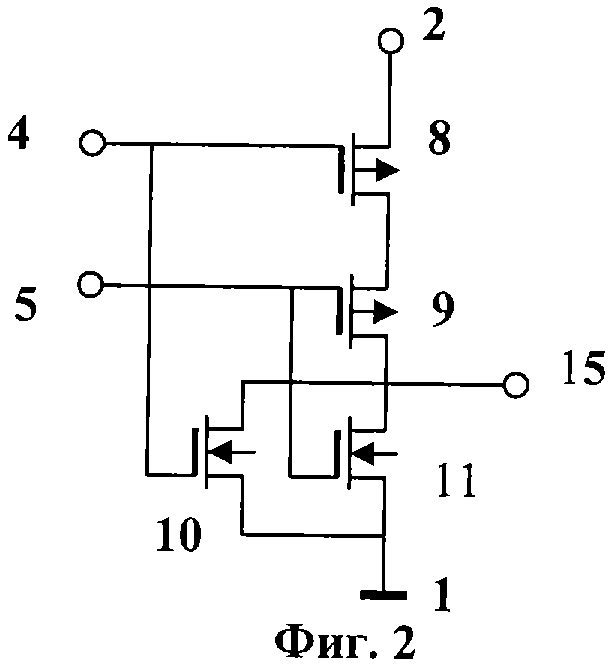

Используя ЛЭ «И-НЕ» двоичной логики и ЛЭ «ИЛИ-НЕ» можно реализовать функцию троичной логики «И». На Фиг.2 показана электрическая схема двоичного ЛЭ «ИЛИ-НЕ», выполненного по КМОП-технологии. ЛЭ содержит: общую шину 1, шину 2 источника положительного напряжения, первую 4 и вторую 5 входные шины и четыре МОП-транзистора 8, 9, 10 и 11. Первый 8 и второй 9 транзисторы с каналом р-проводимости, третий 10 и четвертый 11 с каналом n-проводимости. В схеме ЛЭ «ИЛИ-НЕ» (Фиг.2) транзисторы 8 и 9 с каналом р-проводимости соединены последовательно и подключены к шине питания 2 с одной стороны и к выходной шине 15 с другой. Транзисторы 10 и 11 n-проводимости соединены параллельно и подключены к выходной шине 15 и общей шине 1. Этот ЛЭ работает следующим образом. Если на обоих входах присутствуют напряжения низкого уровня, то оба транзистора р-проводимости открыты, транзисторы n-проводимости закрыты и на выходной шине будет напряжение высокого уровня. При всех других комбинациях напряжений на входных шинах один из транзисторов р-проводимости или оба эти транзистора будут закрыты, а транзисторы n-проводимости (по одному или оба) открыты, и на выходной шине будет напряжение низкого уровня. Таким образом, этот элемент выполняет функцию «ИЛИ» с отрицанием в соответствии с таблицей истинности 3.

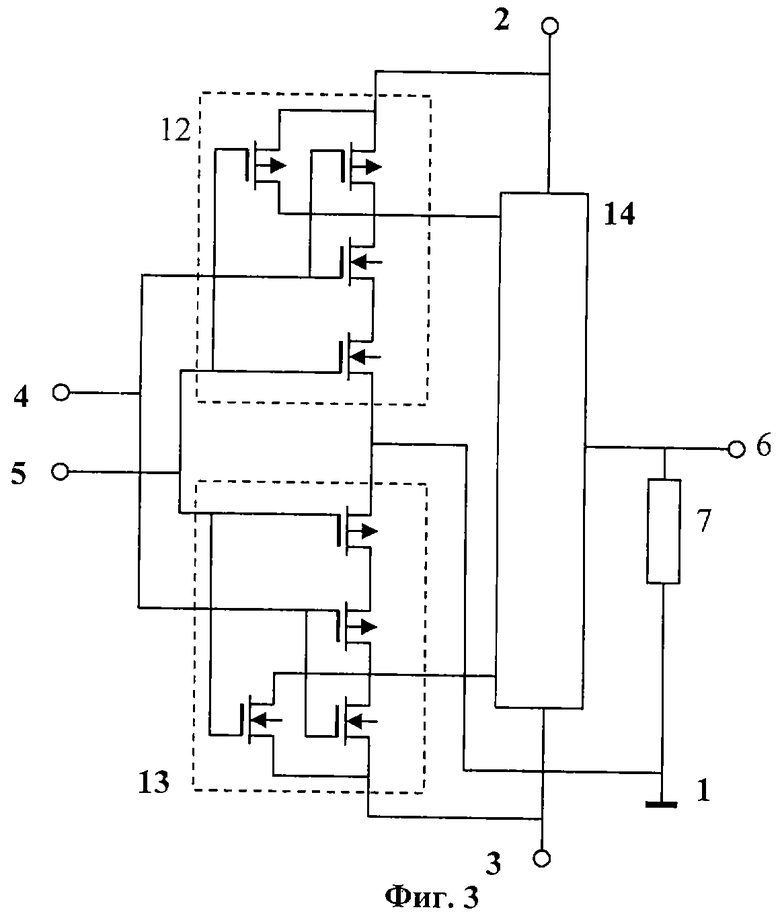

Логическое устройство троичной логики «И» (Фиг.3) содержит: общую шину 1, шины положительного 2 и отрицательного 3 напряжений питания, две входные шины 4 и 5, выходную шину 6, нагрузку 7, первый логический элемент «И-НЕ» 12 двоичной положительной логики, выполненный по КМОП-технологии, второй логический элемент «ИЛИ-НЕ» 13 двоичной положительной логики и элемент объединения сигналов 14. Первый ЛЭ «И-НЕ» 12 подключен к шине 2 положительного напряжения питания и к общей шине 1, второй ЛЭ «ИЛИ-НЕ» 13 подключен к общей шине 1 клеммой для подключения питания и к шине 3 отрицательного напряжения питания клеммой для подключения общей шины. Одноименные входы первого и второго ЛЭ соединены между собой и подключены к входным шинам 4 и 5. Выход первого ЛЭ 12 подключен к первому входу элемента объединения сигналов 16, выход второго ЛЭ 13 подключен ко второму входу элемента объединения сигналов 15, а выход элемента объединения сигналов подключен к выходной шине 6 и нагрузке 7.

Первый ЛЭ 12 при не отрицательных сигналах на входах работает так же, как в двоичной логике. На напряжения отрицательной полярности этот элемент реагирует, как на напряжения низкого уровня. Таким образом, при биполярных сигналах на входах ЛЭ 12 работает в соответствии с таблицей истинности 4.

0 1 1

1 1 1

1 1 1

Второй ЛЭ «ИЛИ-НЕ» 13 (Фиг.3) работает следующим образом. Последовательно соединенные транзисторы 8 и 9 с каналом р-проводимости открываются только в том случае, когда одновременно на двух входных шинах 4 и 5 присутствуют высокие уровни отрицательного напряжения. В этом случае параллельно соединенные транзисторы 10 и 11 n-проводимости закрыты, и выход 15 находится под напряжением низкого уровня. Во всех остальных комбинациях напряжений на входных шинах 4 и 5, хотя бы один из транзисторов 8 или 9 закрыт и хотя бы один из транзисторов 10 и 11 открыт, и на выход 15 передается отрицательное напряжение источника питания. Таким образом, при биполярных сигналах на входах ЛЭ 13 работает в соответствии с таблицей истинности 5.

-1 -1 -1

-1 -1 -1

-1 -1 0

Если в качестве элемента объединения 14 использовать суммирующий операционный усилитель, то логические состояния определяются простым суммированием уровней сигналов с выходов первого 16 и второго 15 ЛЭ, в соответствии с таблицей истинности 6.

-1 0 0

0 0 0

0 0 1

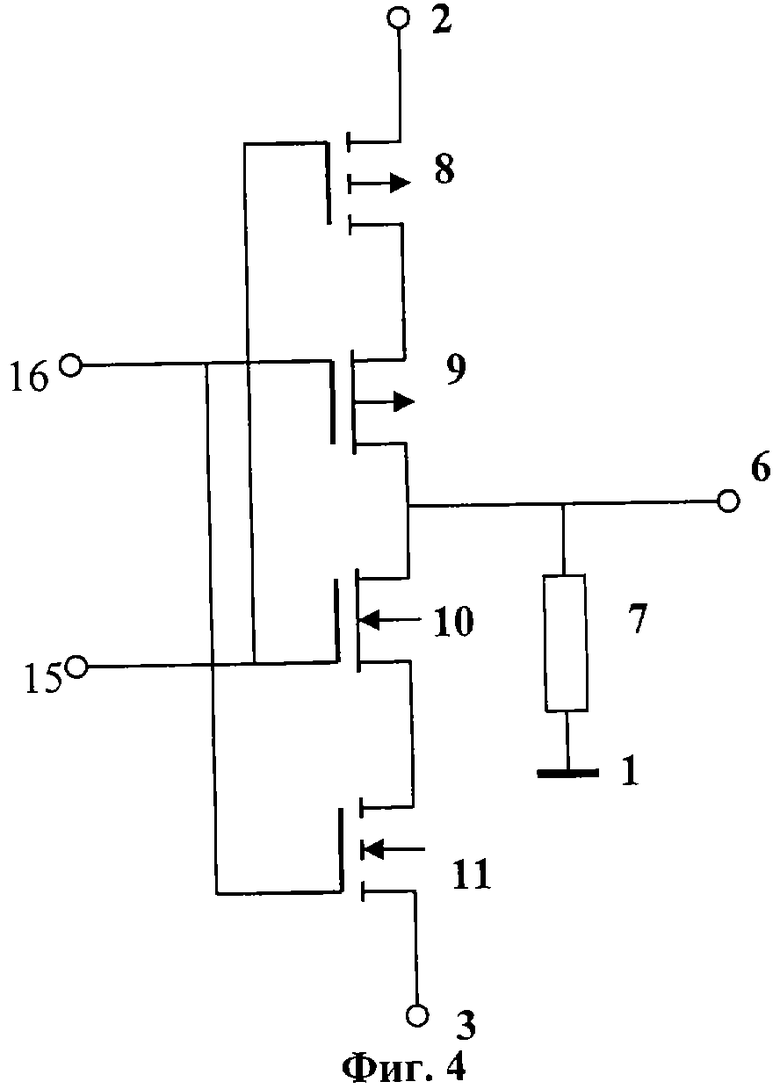

Суммирующий операционный усилитель - сложное и энергоемкое устройство, поэтому целесообразно вместо него использовать новый ЛЭ «2НЕ» (второе отрицание) троичной логики. Этот элемент может быть выполнен с использованием МОП-транзисторов, как показано на Фиг.4. ЛЭ «2НЕ» содержит: общую шину 1, шины 2 и 3 источников положительного и отрицательного напряжения, два входа 16 и 15, выходную шину 6, нагрузку 7 и четыре МОП-транзистора 8, 9, 10 и 11, соединенных между собой последовательно. Первый 8 и второй 9 транзисторы выполнены с каналом р-проводимости, а третий 10 и четвертый 11 - с каналом n-проводимости. При этом пороговые напряжения транзисторов такие, что каналы первого 8 и четвертого 11 транзисторов закрыты при нулевом напряжении на затворах, а у второго 9 и третьего 10 транзисторов каналы открыты при нулевом напряжении на затворах.

Последовательно соединенные первый 8 и второй 9 транзисторы включены между шиной 2 положительного напряжения питания и выходной шиной 6. Последовательно соединенные третий 10 и четвертый 11 транзисторы включены между выходной шиной 6 и шиной 3 отрицательного напряжения питания. Затворы первого 8 и третьего 10 транзисторов соединены между собой и подключены ко второй входной шине 15, а затворы второго 9 и четвертого 11 транзисторов соединены между собой и подключены к первой входной шине 16. Следует отметить, что первый вход 16 предназначен для приема не отрицательных сигналов, а второй вход 15 - для приема не положительных сигналов.

Это устройство работает следующим образом. Если на первый вход 16 подается напряжение низкого уровня, а на второй вход 15 - отрицательное напряжение высокого уровня, первый транзистор 8 открывается и через открытый второй транзистор 9 положительное напряжение шины 2 передается на выходную шину 6 и выделяется на нагрузке 7. При этом цепь от шины 3 источника отрицательного напряжения к выходной шине 6 разомкнута, так как третий транзистор 10 запирается при отрицательном напряжении на затворе и четвертый транзистор 11 закрыт при низком уровне напряжения на затворе.

Если на первый вход 16 подается положительное напряжение высокого уровня и на второй вход 15 - отрицательное напряжение высокого уровня, то разомкнуты обе цепи: от источника положительного напряжения (шина 2) к выходной шине 6 и от источника отрицательного напряжения (шина 3) к выходной шине 6, так как второй 8 и третий 9 транзисторы закрыты. При этом выходная шина находится под потенциалом общей шины 1 через связь с нагрузкой 7.

Если на первый вход 16 подается положительное напряжение высокого уровня, а на второй вход 15 - напряжение низкого уровня, то четвертый транзистор 11 открывается и через открытый третий транзистор 10 отрицательное напряжение от шины 3 передается на выходную шину 6 и выделяется на нагрузке 7. При этом цепь от шины 2 источника положительного напряжения к выходной шине 6 разомкнута, так как второй транзистор 9 запирается при положительном напряжении на затворе и первый транзистор 8 закрыт при низком уровне напряжения на затворе. ЛЭ троичной логики «2НЕ» работает в соответствии с таблицей истинности 7.

Следует отметить еще одно состояние ЛЭ «ИЛИ-НЕ», когда оба входа находятся при низком уровне напряжений. В этом случае первый и четвертый транзисторы закрыты, и выходная шина находится под потенциалом общей шины из-за связи ее через нагрузку 7. Согласно таблице истинности 8 этого ЛЭ он осуществляет операцию «сложение» с инверсией полярности. В результате такой комбинации мы получаем элемент, который с точностью до знака соответствует операции «И», работает в соответствии с таблицей истинности 8.

1 0 0

0 0 0

0 0 -1

Общими элементами прототипа изобретения и устройства являются логический элемент «И-НЕ» положительной двоичной логики, выполненный по КМОП-технологии, общая шина, шина источника положительного напряжения питания, первая и вторая входные шины и выходная шина.

Практически логическое устройство «И» может быть выполнено на ЛЭ «ИЛИ-НЕ» и ЛЭ «И-НЕ» двоичной логики, например, серии 561, выпускаемой промышленностью. Логическое устройство «2НЕ», входящее в состав устройства троичной логики «И», может быть выполнено на транзисторах, выпускаемых промышленностью:

- транзистор 8 - IRF9640;

- транзистор 9 - IRF9510;

- транзистор 10 - IRF120;

- транзистор 11 - IRFP244;

- транзистор 12 - ZVP4424A;

- транзистор 13 - ZVN4424A;

- транзистор 14 - IRF9140;

- транзистор 15 - IRF710.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ИЛИ" | 2004 |

|

RU2278469C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ОТРИЦАНИЕ" (ВАРИАНТЫ) | 2004 |

|

RU2287895C2 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2729887C1 |

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ | 2013 |

|

RU2545325C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ "МИНИМУМ" | 2020 |

|

RU2727145C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

Изобретение относится к автоматике и вычислительной технике, обеспечивая функцию троичной логики. Технический результат заключается в повышении производительности устройств, унифицированных с микросхемами двоичной логики. Устройство «И» (фиг.3) содержит последовательно соединенные между шинами источников положительного (2) и отрицательного (3) напряжений питания логические элементы (ЛЭ) «И-HE» (12) двоичной логики и ЛЭ «ИЛИ-НЕ» (13), выполненные по КМОП-технологии, входы которых соединены с входными шинами (4, 5), а выходы (15, 16) - соответственно с первым и вторым входами элемента объединения (14), выход которого соединен с нагрузкой (7). Точка соединения выводов питания обоих ЛЭ (12, 13) подключена к общей шине (1). 2 з.п. ф-лы, 4 ил., 8 табл.

| Устройство для изготовления пружин | 1988 |

|

SU1563821A2 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Логический элемент на КМДП-транзисторах | 1985 |

|

SU1262721A1 |

| RU 2102835 C1, 20.01.1998. | |||

Авторы

Даты

2006-08-10—Публикация

2004-11-01—Подача