Изобретение относится к цифровым процессорам, таким как микропроцессоры, и особо к процессорам с уменьшенным энергопотреблением, в частности к процессорам мобильных устройств с автономным источником электропитания.

Известны средства, обеспечивающие снижение энергопотребления в цифровых процессорах, путем использования соответствующей элементной базы. Такой элементной базой являются МОП- и КМОП-транзисторы [1]. Эти структуры отличаются очень высоким сопротивлением для тока затвора, вследствие чего в статическом состоянии МОП-вентили практически не потребляют тока от управляющих ими схем. Поэтому потребляемая мощность в периоды, когда входные сигналы постоянны, незначительна. Однако во время переключения состояния с "0" на "1" или с "1" на "0" потребляется существенная мощность. Происходит это по двум причинам. Во-первых, между электродами МОП-транзистора имеются емкости. Эти емкости должны всякий раз при переключении вентиля перезаряжаться от управляющего вентиля. Во-вторых, в КМОП-структурах во время изменения входных сигналов и "понижающая" и "повышающая" части структуры в определенной степени открыты. В результате между линией положительного питающего напряжения и землей кратковременно возникает сквозной ток.

На МОП- и КМОП-структурах построены все процессоры фирмы Intel 1-5-го поколений. Упомянутые ограничения в части возможностей по снижению электропотребления привели к тому, что в процессорах Intel 6 поколения Р6, которые построены на тех же структурах, введены средства управления энергопотреблением, позволяющие уменьшить потребляемую мощность до 10 раз [2].

В процессорах Р6 уменьшение потребляемой мощности достигается прекращением тактирования большинства узлов процессора, т.е. прекращением работы этих узлов. В результате уменьшение потребляемой мощности приводит одновременно к существенному сокращению функциональных возможностей процессора. Так, в самом щадящем режиме Auto Halt, Power Down, т.е. при минимальном снижении энергопотребления отслеживаются только кэш-попадания. В следующем в порядке снижения энергопотребления режиме Stop Grant прекращается исполнение инструкций и обслуживание прерываний.

В процессорах 6-го поколения фирмы Intel Pentium II/III Celeron имеются дополнительные режимы Sleep и Deep Sleep. В режиме Sleep, при котором потребляемый ток становится меньше 1 А, не воспринимаются не только прерывания, но и любые циклы слежения. В состоянии "глубокого сна" Deep Sleep процессор не выполняет никаких функций. При этом потребляемый ток снижается до долей А.

В мобильных процессорах семейства Р6 введен новый режим Quick Start, при котором не отслеживаются транзакции других процессоров, а слежение ведется только за приоритетными агентами шины.

Таким образом, в микропроцессорах шестого поколения остается нерешенным техническое противоречие, состоящее в том, что за снижение энергопотребления в цифровых процессорах приходится платить сокращением функциональных возможностей процессора, причем сокращение возможностей происходит на качественном уровне, а не на количественном, т.е. возможности не ухудшаются на какую-то величину, а просто исчезают. Это значит, что могут возникнуть ситуации, в которых процессор не сможет выполнить предложенную ему в данный момент задачу.

Этого недостатка лишено техническое решение согласно [3], в котором снижение электропотребления достигается за счет предварительного определения и последующей активации только той страницы памяти, к которой относится адресуемая в данной момент ячейка. Однако это техническое решение обеспечивает снижение энергопотребления только в одной из четырех основных составных частей процессора, а именно в памяти, и не снижает энергопотребление в других частях = арифметико-логическом устройстве, регистрах данных и устройстве управления.

В связи с этим в самое последнее время (2002-2003 г.) фирмой Intel был создан процессор Pentium-M, использующий новую технологию Centrino [4]. Эта технология позволяет уменьшить энергопотребление без сокращения функциональных возможностей процессора. Технология Centrino предусматривает:

- взаимосвязь адаптированного к загрузке процессора выбора рабочей точки в координатах "тактовая частота- напряжение питания";

- осуществляемое автоматически включение усилителей считывания данных только непосредственно при приеме данных;

- параллельное декодирование микроопераций в блоке обработки арифметических команд и в блоке управления памятью;

- замену управления стеком на уровне команд аппаратным управлением;

- активация только того квадранта кэш-памяти, с которым предстоит обмен данных;

- повышение скорости конвейерной работы блоков процессора благодаря более точному прогнозированию программного кода, подлежащего передаче из памяти в процессор.

Согласно результатам испытаний, представленным в [4], вычислительный запас, т.е. произведение производительности на время, в течение которого эта производительность демонстрировалась, у процессора Pentium-М примерно в 2 раза больше, чем у его ближайших предшественников. В то же время, как показывают упомянутые результаты по крайней мере в ряде режимов (например, решение целочисленных задач), энергопотребление остается слишком высоким, чтобы обеспечить желательное для пользователя время непрерывной работы мобильного процессора с автономным питанием (5-6 часов). Правда, некоторые из указанных выше технических решений (выбор рабочей точки, прогнозирование кода) имеют технически неограниченные возможности наращивания с тем, чтобы уменьшить энергопотребление в известных блоках процессора. Однако технические средства, реализующие эти решения, при своей работе сами потребляют определенную электрическую мощность. При этом с каждым наращиванием упомянутых возможностей приращение выигрыша в снижении энергопотребления известными способами уменьшается, а приращение собственно потребления в новых блоках остается постоянным. Это приводит к техническому противоречию, состоящему в том, что снижение энергопотребления в известных блоках по мере наращивания возможностей новых блоков в лучшем случае не превосходит, а в худшем становится меньше, чем увеличение энергопотребления в новых блоках.

Наиболее близким по технической сущности к предлагаемому устройству является цифровой процессор ЭВМ, построенный по общеизвестной схеме [5], т.е. содержащий устройство управления с тактовым генератором, выполненные на МОП- и (или) КМОП-тригеррах и соединенные между собой шиной данных арифметико-логическое устройство, регистры данных и память, а также линии передачи синхроимпульсов, соединяющие тактовый генератор с синхровходами триггеров, образующих регистры данных и регистры арифметико-логического устройства и памяти.

Техническим результатом изобретения является снижение энергопотребления в цифровых процессорах сверх предела, обусловленного энергозатратами в самих известных средствах, используемых для снижения потребляемой мощности.

Указанный технический результат достигается тем, что в цифровой процессор, построенный на МОП- и (или) КМОП-структурах, введены задатчик разрядности и коммутаторы. Коммутаторы включаются в линии передачи синхроимпульсов таким образом, что выходы коммутаторов соединены с синхровходами триггеров, образующих регистры данных и регистры арифметико-логического устройства и памяти или часть этих регистров. Управляющие входы коммутаторов соединены с выходом задатчика разрядности, вход которого соединен с выходом устройства управления.

Задатчик разрядности благодаря своей связи по входу с устройством управления позволяет преобразовать команду - код программы, определяющую необходимую точность вычислений, в управляющие коды. Эти коды, благодаря связи задатчика разрядности по выходу с коммутаторами, позволяют установить такое состояние коммутаторов, что они, будучи по сигнальному входу включены в линию передачи синхроимпульсов, обеспечивают тактирование либо всех триггеров в регистрах данных, арифметико-логического устройства и памяти, либо (при требуемой точности вычислений, меньшей, чем определяемая разрядностью процессора) тактирование только определенной части триггеров этих регистров. В результате среднее число изменений состояний триггеров уменьшается и среднее энергопотребление снижается. При этом процессор выполняет все поставленные ему задачи, так как при поступлении задачи с большей необходимой точностью вычислений, состояние коммутаторов изменяется таким образом, что тактируется большее, вплоть до максимального для данного процессора число разрядов. Обработка команды - кода, задающей точность вычислений, и изменения состояний коммутаторов приводят к дополнительным энергозатратам. Но эти затраты имеют место один раз за все время выполнения данной задачи (если задача вообще допускает точность вычислений, меньшую, чем определяемая разрядностью процессора, а иначе сама команда-код, задающая точность, и соответственно дополнительные энерогозатраты отсутствуют). Количество же предотвращаемых изменений состояний триггеров, определяемое количеством операндов в программе, намного больше, чем число изменений состояний триггеров, которые приводят к дополнительным энергозатратам. Поэтому снижение энергопотребления при задействовании новых средств, предусмотренных изобретением, всегда больше, чем дополнительные энергозатраты на функционирование этих средств. Таким образом, предложение разрешает указанное выше техническое противоречие.

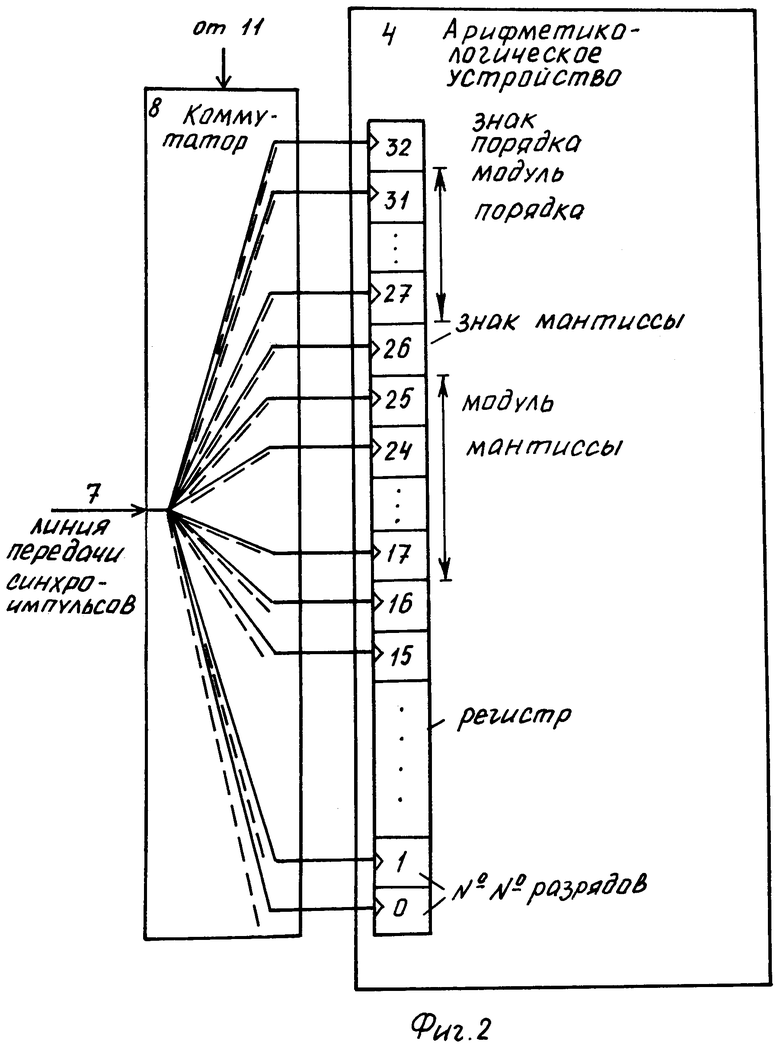

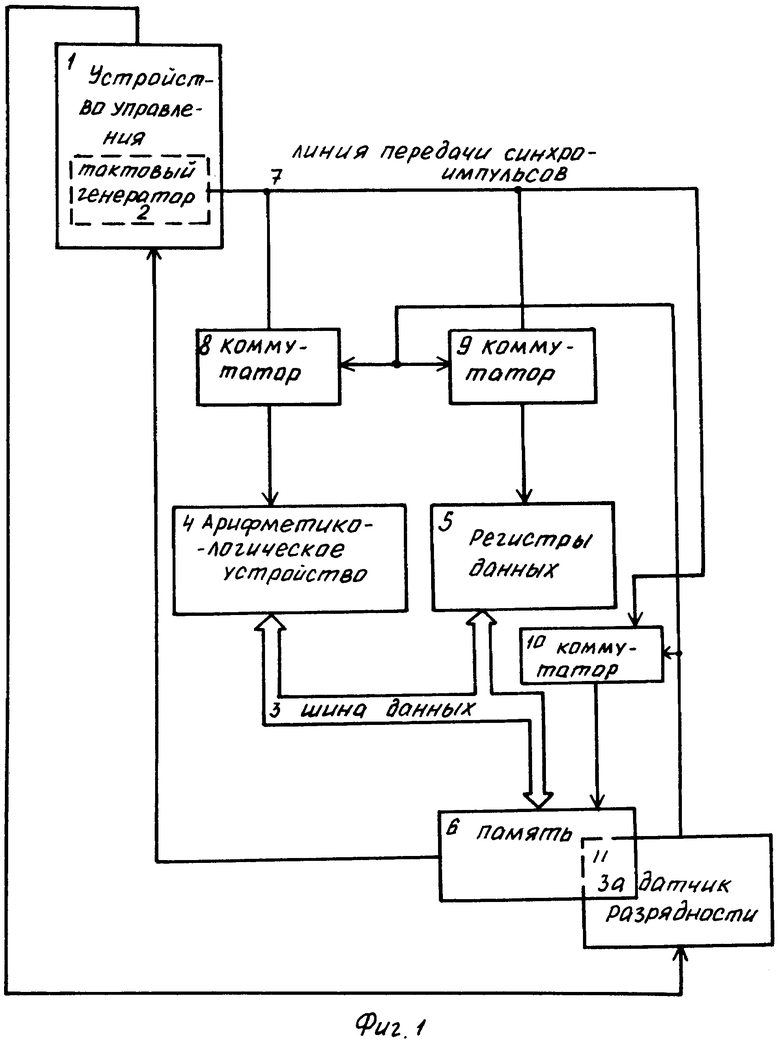

Сущность изобретения поясняется фиг.1, 2, где на фиг.1 приведена функциональная схема цифрового процессора, на фиг.2 - пример состояния коммутатора и одного из регистров арифметико-логического устройства для случая 32-разрядного процессора при представлении чисел в формате с плавающей запятой с необходимой точностью, обеспечиваемой 16 разрядами.

Цифровой процессор содержит устройство управления 1 с тактовым генератором 2, выполненные на МОП- и (или) КМОП-триггерах и соединенные между собой шиной данных 3, арифметико-логическое устройство 4, регистры данных 5, память 6, а также линии передачи синхроимпульсов 7, соединяющие тактовый генератор 2 с синхровходами триггеров, образующих регистры данных 5 и регистры арифметико-логического устройства 4 и памяти 6, при этом ввод линий передачи синхроимпульсов 7 на синхровходы триггеров по меньшей мере одного из регистров блоков 4, 5, 6 выполнен через коммутаторы 8, 9, 10, управляющие входы которых соединены с выходом задатчика разрядности 11, а вход задатчика разрядности 11 соединен с выходом устройства управления 1, вход которого соединен с выходом памяти 6.

Процессор работает следующим образом. При выполнении на N-разрядном процессоре программы, которая должна обеспечить точность вычислений, соответствующую заданному отстоянию δ единицы от ближайшего дробного числа, предваряющая программу соответствующая значению δ команда-код поступает из памяти 6 в устройство управления 1. Эта команда-код предписывает пересылку в дешифратор задатчика разрядности 11 одного из чисел в диапазоне от 1 до N, хранящихся в выделенных для задатчика 11 регистрах памяти 6. Например, если δ=2-10, a N=32, то таким числом будет 16. Дешифратор задатчика разрядности 11, получив двоичный код этого числа, вырабатывает и посылает соответствующий единичный сигнал на управляющие входы коммутаторов 8, 9, 10. Коммутаторы 8, 9, 10 переходят в состояние, показанное на фиг.2 штриховыми линиями, т.е. прекращают передачу синхроимпульсов от тактового генератора 2 по линии передачи синхроимпульсов 7 на синхровыходы триггеров с 0 по (N-m-n-2)-й, т.е. в данном примере с 0-го по 16-й разрядов в регистрах данных 5, регистрах арифметико-логического устройства 4 и памяти 6. Здесь m - количество разрядов, отводимых для представления модуля мантиссы числа-операнда, n - количество разрядов, отводимых для представления модуля порядка этого числа. (В рассматриваемом примере m=9; n=5). В результате упомянутые триггеры до нового изменения состояния коммутаторов 8, 9, 10, т.е. до считывания в памяти 6 новой команды-кода, определяющей необходимость новой точности вычислений, остаются в неизменном состоянии, а именно в том, в каком они оказались после первого рассмотренного здесь изменения состояния коммутаторов 8, 9, 10. Поэтому вышеупомянутые триггеры не переключаются, и электрическая мощность в этих триггерах не потребляется. Поскольку содержание разрядов с 0-го по 16-й не меняется, точность вычислений падает, но остается в допустимых для данной задачи пределах.

В остальном процессор работает обычным образом. Требуемые для выполнения программы данные считываются из памяти 6 и поступают в регистры данных 5. Туда же могут поступать данные из арифметико-логического устройства 4. Арифметико-логическое устройство 4 выполняет с кодами данных, хранящимися в регистрах данных 5, операции, предусмотренные программой и представленные набором управляющих сигналов, передаваемых из устройства управления 1 в арифметико-логическое устройство 4. Коды результатов операций записываются в соответствии с программой в регистре-аккумуляторе из числа регистров данных 5, откуда передаются либо в другие регистры данных 5, либо в память 6.

Построение вновь введенных блоков процессора известно, (см., например, [6] - коммутаторы, [5], дешифраторы (стр.27) и память (стр.42), образующие в совокупности задатчик разрядности). Прекращение работы части триггеров младших разрядов в блоках процессора, хранящих или обрабатывающих коды данных, приводит к снижению точности вычислений, но благодаря задатчику разрядности сохраняет точность в необходимых пределах и в то же время снижает среднюю потребляемую мощность процессора.

Источники информации

1. Д.Гивоне, Р.Россер, "Микропроцессоры и микрокомпьютеры" M., 1983.

2. M.Гук, В.Юров, "Процессоры Pentium 4, Athlon и Duron", СПБ. 2001.

3. PAT US 2003028749 от 2003-02-06, G-06 F 12/00.

4. Кайрат Ахметов Intel Centrino: детальный обзор технологии, подробные тесты производительности и энергосбережения на примере ноутбуков ASUS SIN и Roverbook Nautilius В 570, www.ferra.ru/online/mobilis/24836.

5. Л.Н.Королев "Микропроцессоры, микро- и мини-ЭВМ", M., 1988.

6. С.Хвощ и др. Микропроцессоры и микроЭВМ, Л., 1987, с.163.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ПРОЦЕССОР | 2004 |

|

RU2290686C2 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОСТАДИЙНОЙ МНОГОПОТОЧНОЙ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ И СПОСОБ ОБРАБОТКИ С ИСПОЛЬЗОВАНИЕМ ДАННОГО МОДУЛЯ | 2018 |

|

RU2681365C1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Имитатор гидроакустических сигналов | 1978 |

|

SU765865A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

Изобретение относится к цифровым процессорам, в частности к микропроцессорам с уменьшенным энергопотреблением. Технический результат заключается в снижении энергопотребления. Технический результат достигается за счет того, что в состав процессора введены регистры данных, память, арифметико-логическое устройство, шина данных, устройство управления с тактовым генератором, линия передачи синхроимпульсов, задатчик разрядности и коммутаторы. 2 ил.

Цифровой процессор, содержащий арифметико-логическое устройство, регистры данных и память, включающие регистры, выполненные на МОП- и (или) КМОП-триггерах и соединенные между собой шиной данных, линию передачи синхроимпульсов, а также устройство управления с тактовым генератором, причем выход тактового генератора соединен с линией передачи синхроимпульсов, отличающийся тем, что в его состав введены коммутаторы, сигнальные входы которых соединены с выходами линий передачи синхроимпульсов, а выходы соединены с синхровходами триггеров, по меньшей мере, одного из указанных регистров, и задатчик разрядности, преобразующий содержащиеся в памяти команды-коды, определяющие точность вычислений в коды управления коммутаторами, причем команды-коды с выхода памяти поступают на вход задатчика разрядности через устройство управления, а с выхода задатчика разрядности команды-коды поступают на управляющие входы коммутаторов, которые обеспечивают тактирование определенной части триггеров, соответствующей заданной точности вычислений.

| СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕССОР | 1995 |

|

RU2147378C1 |

| Процессор аппроксимационной обработки информации | 1988 |

|

SU1501089A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| US 2003028749 А1, 06.02.2003 | |||

| GB 2062308 A, 20.05.1981. | |||

Авторы

Даты

2006-12-27—Публикация

2004-09-06—Подача