Изобретение относится к вычислительной технике, в частности к устройствам обработки данных, и может найти применение в микропроцессорных системах с сокращенным набором команд.

Известно устройство чтения из кэш-памяти, например, содержащееся в микропроцессоре 79R3081 компании IDT (США). Указанное устройство включает блок формирования адреса, конвейерные регистры-защелки 1А, 1В, 2В, блок преобразования адреса, память данных, память тэгов, блок сравнения, блок управления и генератор тактовых импульсов, причем выход блока формирования адреса подключен к входу конвейерного регистра-защелки 1А, выход которого подключен к блоку преобразования адреса, выход блока преобразования адреса подключен к входу конвейерного регистра-защелки 1В, выход которого подключен к адресным входам памяти данных и памяти тэгов и к входу блока сравнения, к другому входу которого подключен выход памяти тэгов, выход блока сравнения и выход памяти данных подключен к входу конвейерного регистра защелки 2 В, выход блока управления подключен к управляющим входам памяти данных и памяти тэгов, синхронизация схемы задается генератором тактовых импульсов, который имеет два выхода, (см. "The IDT79R3071, IDT79R3081 RISC Controller Hardware User's Manual" Revision 2.0 April 4, 1994).

Недостатком известного устройства является то, что на адресные входы памяти данных и памяти тэгов подается сигнал с выхода регистра защелки 1 В, таким образом оставляя промежуток времени всего в две фазы на выполнение чтения из памяти тэгов и выполнение сравнения содержимого памяти тэгов с физическим адресом, поступающим с выхода регистра защелки 1В, что не позволяет повысить быстродействие микропроцессорной системы в целом.

Наиболее близким к патентуемому устройству чтения из кэш-памяти является устройство, входящее в состав 64-разрядного микропроцессора 79RC64574/64575. Устройство чтения из кэш-памяти включает блок формирования адреса, конвейерные регистры-защелки 1А, 1В, 2В, блок преобразования адреса, память данных, память тэгов, блок сравнения, блок управления и генератор тактовых импульсов с двумя выходами, причем выход блока формирования адреса подключен к входу конвейерного регистра-защелки 1А, выход которого подключен к входу блока преобразования адреса и к адресным входам памяти данных и памяти тэгов соответственно, выход блока преобразования адреса подключен к входу конвейерного регистра-защелки 1В, выход которого подключен к входу блока сравнения, к другому входу которого подключен выход памяти тэгов, выход памяти данных подключен к входу конвейерного регистра защелки 2В, к другому входу которого подключен выход блока сравнения, выход блока управления подключен к управляющим входам памяти данных и памяти тэгов, синхронизация схемы задается генератором тактовых импульсов, который имеет два выхода, один выход генератора тактовых импульсов соединен с одним из входов блока управления и входом регистра 1А, а другой выход генератора тактовых импульсов соединен с другим входом блока управления и входами регистров 1В и 2В. В данном устройстве индексация памяти данных и памяти тэгов осуществляется по виртуальному адресу, т.е. по выходу регистра 1А, который формируется на одну фазу раньше, чем физический адрес. Такое решение позволяет исключить время преобразования адреса из критического пути конвейера на данной стадии. Параметры памяти данных и памяти тэгов являются одинаковыми и временная диаграмма обращения к памяти данных и памяти тэгов также является одинаковой. Такой подход проще реализовать технически, так как память строится на однотипных ячейках. Кроме того, при единой временной диаграмме схема управления двумя типами памяти гораздо проще (см. "79RC64574/64575 User Reference Manual", Version 1.0 April 2000 http://www.idt.com/docs/79RC64574_MA_63402.pdf).

Однако такой подход одновременного считывания имеет недостаток: поскольку, с точки зрения логики работы микропроцессора, содержимое памяти тэгов нужно иметь значительно раньше, чем содержимое памяти данных, так как содержимое тэгов используется блоком сравнения для формирования признака попадания в кэш-память. При таком подходе требования по быстродействию автоматически налагаются и на компактную и быструю память тэгов и на память данных, которые значительно больше по объему, что ведет к повышению энергопотребления и занимаемой площади и является ограничивающим фактором по быстродействию.

Задачей изобретения является повышение быстродействия конвейерной системы микропроцессора с сокращенным набором команд и снижение энергопотребления.

Техническим результатом является разделение циклов чтения памяти данных и памяти тэгов кэш-памяти микропроцессора, что позволяет сформировать признак попадания в кэш-память на пол-фазы быстрее, чем будет доступно содержимое памяти данных при одновременном снижении требований к быстродействию памяти данных.

Указанные задача и технический результат достигаются в устройстве чтения из кэш-памяти, включающем блок формирования адреса, конвейерные регистры-защелки 1А, 1В, 2А, 2В, блок преобразования адреса, память данных, память тэгов, блок сравнения, блок управления и генератор тактовых импульсов с двумя выходами, причем выход блока формирования адреса подключен к входу конвейерного регистра-защелки 1А, выход которого подключен к входу блока преобразования адреса и к адресным входам памяти данных и памяти тэгов соответственно, выход блока преобразования адреса подключен к входу конвейерного регистра-защелки 1В, выход которого подключен к входу блока сравнения, к другому входу которого подключен выход памяти тэгов, выход памяти данных подключен к входу конвейерного регистра защелки 2В, один выход генератора тактовых импульсов соединен с одним из входов блока управления и входами регистров 1А и 2А, а другой выход генератора тактовых импульсов соединен с другим входом блока управления и входами регистров 1В и 2В, блок управления имеет два выхода, один из которых подключен к входу памяти данных, а другой к входу памяти тэгов, а выход блока сравнения подключен к входу конвейерного регистра-защелки 2А.

Ускоренное формирование признака попадания в кэш-память позволяет сократить время формирования сигнала остановки конвейера, что позволяет увеличить тактовую частоту всего конвейера. При этом снижение требования по быстродействию к памяти данных позволит снизить энергопотребление и занимаемую площадь данного блока.

Для выполнения заявленных задачи и технического результата устройство чтения из кэш-памяти обеспечивает формирование сигнала попадания в кэш и запись его в конвейерный регистр защелку по второму сигналу phi_A и считывание содержимого памяти данных и запись его в конвейерный регистр защелку по второму сигналу phi_B с момента начала формирования адреса.

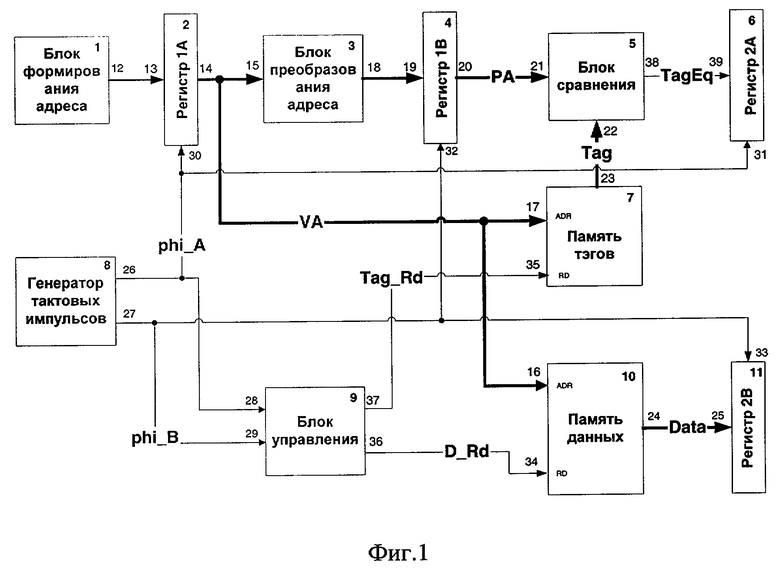

На фиг.1 изображена блок-схема патентуемого устройства чтения кэш-памяти.

На фиг.2 - схема блока преобразования адреса.

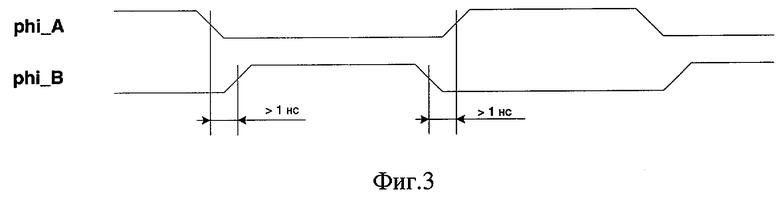

На фиг.3 - форма тактовых импульсов.

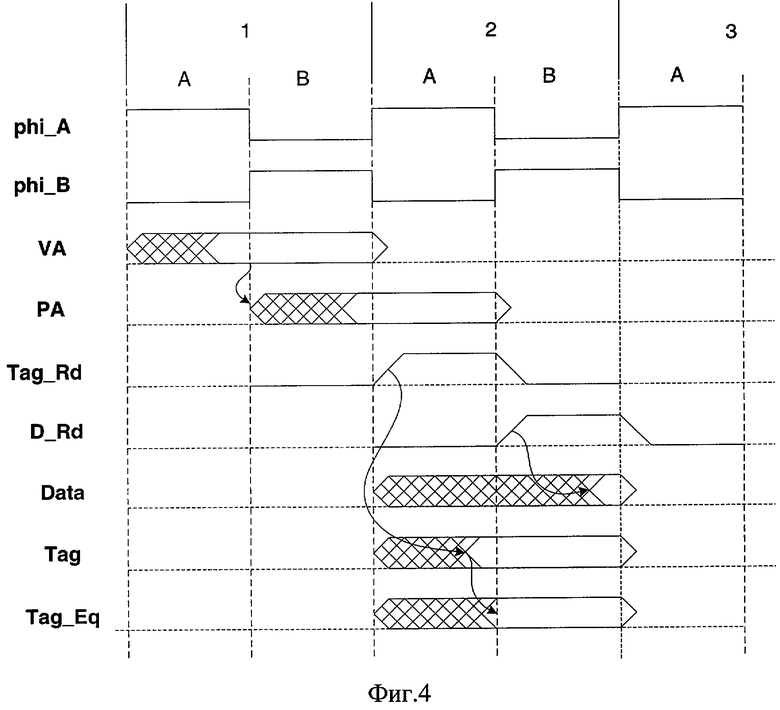

На фиг.4 - временная диаграмма работы считывания кэш-памяти патентуемым устройством.

Устройство чтения из кэш-памяти содержит следующие узлы:

1 - блок формирования адреса,

2 - конвейерный регистр-защелка 1А,

3 - блок преобразования адреса,

4 - конвейерный регистр-защелка 1 В,

5 - блок сравнения,

6 - конвейерный регистр-защелка 2А,

7 - память тэгов,

8 - генератор тактовых импульсов,

9 - блок управления,

10 - память данных,

11 - конвейерный регистр-защелка 2 В,

причем выход 12 блока формирования адреса 1 подключен к входу 13 конвейерного регистра-защелки 1А позиция 2, выход 14 которого подключен к входу 15 блока преобразования адреса 3 и к адресным входам 16 и 17 памяти данных 10 и памяти тэгов 7 соответственно, выход 18 блока преобразования адреса 3 подключен к входу 19 конвейерного регистра-защелки 1 В позиция 4, выход 20 которого подключен к входу 21 блока сравнения 5, к другому входу 22 которого подключен выход 23 памяти тэгов 7, выход 24 памяти данных 10 подключен к входу 25 конвейерного регистра защелки 2 В позиция 11, синхронизация схемы задается генератором тактовых импульсов 8, который имеет два выхода 26 и 27, соединенных с входами 28 и 29, соответственно, блока управления 9, а также с входами 30 и 31 регистров 1А и 2А позиции 2 и 6, и с входами 32 и 33 регистров 1В и 2В позиции 4 и 11, соответственно, управляющие входы 34 и 35 памяти данных 10 и памяти тэгов 7 подключены к раздельным выходам 36 и 37 блока управления 9 соответственно, а выход 38 блока сравнения 5 подключен к входу 39 конвейерного регистра-защелки 2А позиция 6.

Блок формирования адреса 1, предназначен для формирования виртуального адреса, по которому необходимо считать содержимое кэш-памяти, и состоит из 32-разрядного счетчика. Выходом блока формирования адреса является 32-разрядный адрес из виртуального адресного пространства микропроцессора.

Конвейерный регистр-защелка 2 предназначен для сохранения 32-разрядного виртуального адреса в стабильном состоянии в течение фазы 1В путем защелкивания входного сигнала по заднему фронту сигнала phi_A в такте 1, и состоит из 32-разрядного регистра типа latch.

Блок преобразования адреса 3 предназначен для формирования 32-разрядного физического адреса на основе 32-х разрядного виртуального адреса. Блок состоит из полностью ассоциативной памяти на 64 строки. Схема и принцип работы блока преобразования адреса описана в J.Hennesy and D.Patterson. Computer Architecture: A Quantitative Approach. Morgan Kaufmann Publisher, Inc., San Francisco, CA, Second edition, 2001, глава 5.

Выходом блока преобразования адреса является 32-разрядный физический адрес.

Конвейерный регистр-защелка 4 предназначен для сохранения 32-разрядного физического адреса в стабильном состоянии в течение фазы 2А, путем защелкивания входного сигнала по заднему фронту сигнала phi_B в такте 1, и состоит из 32-разрядного регистра типа latch.

Блок сравнения 5 предназначен для сравнения старших 20-ти разрядов физического адреса с содержимым памяти тэгов и состоит из 20-разрядного компаратора. В случае совпадения блок сравнения формирует активный уровень сигнала TagEq.

Конвейерный регистр защелка 6 предназначен для сохранения сигнала совпадения адреса TagEq в стабильном состоянии в течения фазы 2 В, путем защелкивания входного сигнала по заднему фронту сигнала phi_A в такте 2, и состоит из 1-разрядного регистра типа latch.

Память тэгов 7 представляет собой стандартную асинхронную память емкостью 4 КБ и с шириной слова в 20 разрядов. Память предназначена для хранения тэгов. В данной схеме к памяти предъявляются повышенные требования по быстродействию. Выходом памяти тэгов является 20-разрядная шина Tag.

Генератор тактовых импульсов 8 предназначен для формирования тактовых сигналов phi_А и phi_B. Форма данных сигналов показана на фиг.3. Необходимо отметить требование наличия временного интервала между активными высокими уровнями сигналов phi_A и phi_В не менее 1 нс.

Блок управления 9 предназначен для формирования управляющих сигналов считыванию памяти тэгов и памяти данных. Алгоритм формирования справляющих сигналов обеспечивает считывание содержимого тэгов раньше, чем содержимого памяти данных. Блок построен на базе программируемой логической матрицы (PLM). Выходом блока являются сигналы чтения памяти данных D_Rd и чтения памяти тэгов Tag_Rd.

Память данных 10 представляет собой стандартную асинхронную память емкостью 4 КБ и с шириной слова в 32 разряда. Память предназначена для хранения данных. В данной схеме к памяти не предъявляются требования по быстродействию, что позволяет снизить энергопотребление и занимаемую площадь. Выходом памяти тэгов является 32-разрядная шина данных Data.

Конвейерный регистр-защелка 11 предназначен для сохранения шины данных Data в стабильном состоянии в течение фазы 3А, путем защелкивания входного сигнала по заднему фронту сигнала phi_В в такте 2, и состоит из 32-разрядного регистра типа latch.

Устройство считывания из кэш-памяти работает следующим образом. В течение фазы 1А блок формирования адреса 1 формирует адрес на основе предыдущего значения путем увеличения его на 4. Выход 12 блока формирования адреса 1 поступает на вход 13 регистра защелки 1А, позиция 2, который обеспечивает стабильность виртуального адреса VA в течение фазы 1В. Далее старшие разряды [31:12] виртуального адреса VA поступают на вход 15 блока преобразования адреса 3, где происходит их преобразование в физические адреса РА в соответствии со схемой, изображенной на фиг.2. Младшие 12 разрядов [11:0] виртуального адреса VA подаются на адресные входы 16 и 17 памяти данных 10 и памяти тэгов 7 соответственно. В течение фазы 1 В происходит преобразование виртуального адреса VA в физический РА в блоке преобразования адреса 3, а также начинается цикл чтения памяти тэгов 7 и памяти данных 10. К концу фазы 1 В на выходе 18 блока преобразования адреса 3 формируется физический адрес, который поступает на вход 19 и защелкивается в регистре-защелке 1В, позиция 4, который обеспечивает стабильность физического адреса в течение фазы 2А. В этой же фазе блок управления 9 на выходе 37 формирует активное состояние сигнала Tag_Rd, который разрешает выдачу содержимого памяти тэгов 7 на 20-разрядную шину Tag, которая соединяет выход 23 памяти тэгов с входом 22 блока сравнения 5, на другой вход 21 которого поступают старшие разряды физического адреса РА. Блок сравнения 5 формирует активный сигнал Tag_Eq, в случае, если содержимое памяти тэгов 7, считанное в данном цикле, совпадает со старшими разрядами физического адреса. Сигнал Tag_Eq должен поступить на вход 39 регистра защелки 2А, позиция 6 до окончания фазы 1А с тем, чтобы быть доступным для дальнейшей обработки в фазе 2В. Также в течение фазы 2В блок управления 9 формирует сигнал D_Rd, который разрешает выдачу содержимого памяти данных 10 на 32-разрядную шину Data, которая соединяет выход 24 памяти данных с входом 25 регистра-защелки 2В, позиция 11, к моменту окончания фазы 2В с тем, чтобы быть доступной для дальнейшей обработки в фазе 3А.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ ПОТОКОВ ДАННЫХ, СЧИТЫВАЕМЫХ ИЗ ОЗУ | 2011 |

|

RU2475817C1 |

| Запоминающее устройство с динамической адресацией | 1987 |

|

SU1472909A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| ГИБРИДНЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2556364C1 |

| МУЛЬТИПРОЦЕССОРНАЯ АРХИТЕКТУРА, ОПТИМИЗИРОВАННАЯ ДЛЯ ПОТОКОВ | 2008 |

|

RU2450339C2 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| СРЕДСТВО РАЗДЕЛЕННОЙ ЗАГРУЗКИ/СОХРАНЕНИЯ И КОМАНДА ДЛЯ НЕГО | 2010 |

|

RU2554546C2 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

Изобретение относится к вычислительной технике, в частности к устройствам обработки данных, и может применяться в микропроцессорных системах с сокращенным набором команд. Техническим результатом является повышение быстродействия конвейерной системы микропроцессора с сокращенным набором команд, сокращение времени формирования признака попадания в кэш-память и снижение энергопотребления. Устройство чтения из кэш-памяти содержит блок формирования адреса, конвейерные регистры-защелки 1А, 1В, 2А, 2В, блок преобразования адреса, память данных, память тэгов, блок сравнения, блок управления с двумя выходами и генератор тактовых импульсов с двумя выходами. 4 ил.

Устройство чтения из кэш-памяти, содержащее блок формирования адреса, конвейерные регистры-защелки 1А, 1В, 2А, 2В, блок преобразования адреса, память данных, память тэгов, блок сравнения, блок управления и генератор тактовых импульсов с двумя выходами, причем выход блока формирования адреса подключен к входу конвейерного регистра-защелки 1А, выход которого подключен к входу блока преобразования адреса и к адресным входам памяти данных и памяти тэгов соответственно, выход блока преобразования адреса подключен к входу конвейерного регистра-защелки 1В, выход которого подключен к входу блока сравнения, к другому входу которого подключен выход памяти тэгов, выход памяти данных подключен к входу конвейерного регистра защелки 2В, один выход генератора тактовых импульсов соединен с одним из входов блока управления и входами регистров 1А и 2А, а другой выход генератора тактовых импульсов соединен с другим входом блока управления и входами регистров 1В и 2В, отличающееся тем, что блок управления имеет два выхода, один из которых подключен к входу памяти данных, а другой к входу памяти тэгов, а выход блока сравнения подключен к входу конвейерного регистра-защелки 2А.

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МНОГОПРОЦЕССОРНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА С КОГЕРЕНТНОЙ КЭШ С УМЕНЬШЕННЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ | 1995 |

|

RU2171490C2 |

| Штемпель для нанесения оттиска на бумагу | 1987 |

|

SU1444171A1 |

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Controller Hardware User's Manual | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ГУК М | |||

| Аппаратные средства IBM PC | |||

| - С-Пб.: Питер Ком, 1999, с.214-218, 320-327. | |||

Авторы

Даты

2006-12-27—Публикация

2005-05-14—Подача