Изобретение относится к вычислительной технике и может быть использовано для контроля правильности соединений электрического монтажа различных радиоэлектронных устройств.

Известно устройство для контроля монтажных схем [1], содержащее генератор импульсов, схему сравнения, счетчик входного адреса, блок вывода, коммутатор входного адреса, блок хранения эталонов, первый и второй коммутаторы опроса, счетчик выходного адреса, вход и выход устройства, к которым подключен проверяемый объект.

Недостатком устройства является большой объем оборудования, обусловленный необходимостью наличия физического эталона и соответствующих коммутаторов, и длительное время проверки из-за необходимости последовательного сравнения логических состояний на выходах коммутаторов опроса проверяемого объекта и блока хранения эталонов для каждого входного и выходного адреса, что требует большого числа операций сравнения в схеме сравнения и многократных коммутаций в блоке хранения эталона.

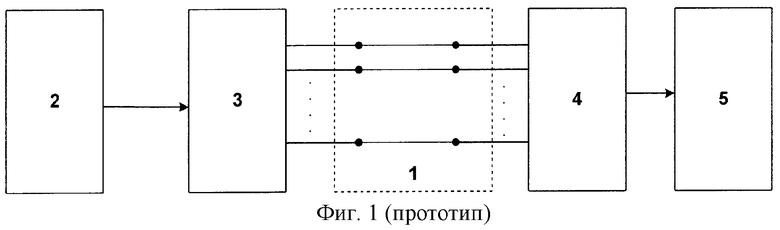

Наиболее близким техническим решением, принятым за прототип, является устройство для контроля монтажа жгутов [2], содержащее последовательно соединенные генератор импульсов и последовательный регистр сдвига, выходы которого соединены с объектом контроля, логические вентили И, входы которых соединены с объектом контроля, и блок индикации (светоизлучающие диоды).

Недостатком данной схемы является то, что она имеет низкую производительность и достоверность контроля. При росте числа проверяемых цепей и увеличении числа одновременно замкнутых контактов (более двух) происходит усложнение анализа полученных результатов контроля.

Технический результат предлагаемого изобретения - увеличение производительности и достоверности контроля, расширение функциональных возможностей, связанных с упрощением анализа полученных результатов контроля независимо от числа проверяемых цепей и числа одновременно замкнутых контактов.

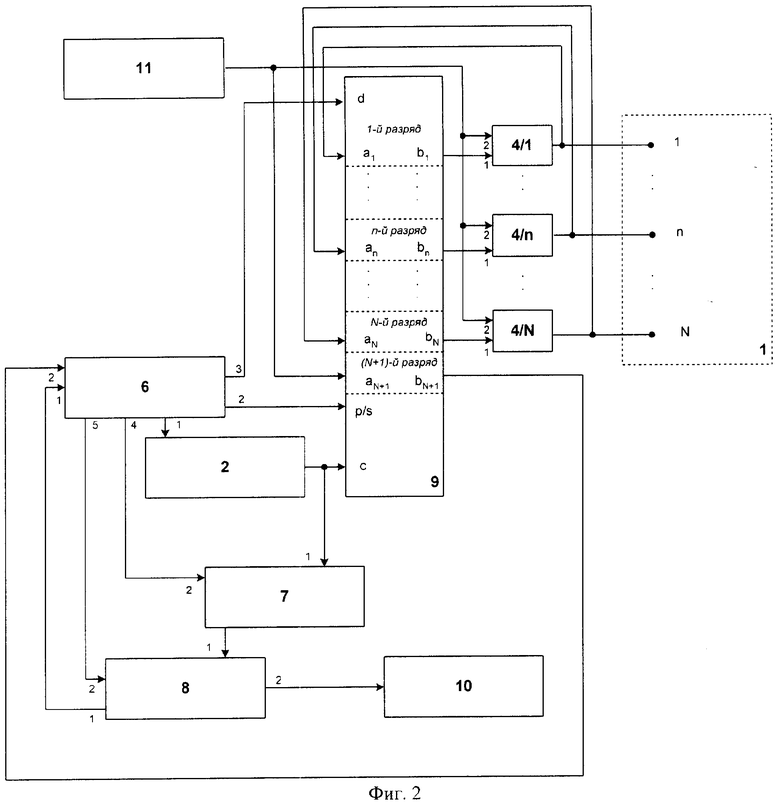

Это достигается тем, что в структурную схему устройства для контроля монтажа, взятого в качестве прототипа, состоящего из генератора импульсов, логических вентилей И, введены блок управления, счетчик, контроллер, регистр параллельно-последовательный, блок вывода и формирователь логической единицы с соответствующими связями.

На фиг.1 изображена упрощенная структурная схема прототипа,

на фиг.2 структурная схема предлагаемого устройства, где на фигурах приняты следующие обозначения:

1 - объект контроля;

2 - генератор импульсов;

3 - регистр последовательный;

4 - N логических вентилей И;

5 - блок индикации;

6 - блок управления;

7 - счетчик;

8 - контроллер;

9 - регистр параллельно-последовательный;

10 - блок вывода;

11 - формирователь логической единицы.

Устройство для контроля монтажных схем содержит объект контроля 1, генератор импульсов 2, N логических вентилей И 4, блок управления 6, счетчик 7, контроллер 8, регистр параллельно-последовательный 9, блок вывода 10, формирователь логической единицы 11, причем первый выход блока управления 6 соединен с входом генератора импульсов 2, выход которого соединен с первым входом счетчика 7 и управляющим входом "с" регистра 9, второй выход блока управления 6 соединен с управляющим входом "p/s" регистра 9, третий выход блока управления 6 соединен с последовательным входом "d" регистра 9, четвертый выход блока управления 6 соединен со вторым входом счетчика 7, выход которого соединен с первым входом контроллера 8, пятый выход блока управления 6 соединен со вторым входом контроллера 8, первый выход которого соединен с первым входом блока управления 6, а второй выход - с входом блока вывода 10, выходы "bn" (n=1, 2, ...N) регистра 9 соединены с первыми входами вентилей И 4, выход формирователя логической единицы 11 соединен с входом "аN+1" регистра 9 и вторыми входами вентилей И 4, выходы вентилей И 4 соединены с входами "an" (n=1, 2, ...N) регистра 9 и N контактами объекта контроля 1, выход "bN+1" регистра 9 соединен со вторым входом блока управления 6.

Устройство для контроля монтажных схем работает следующим образом.

Регистр параллельно-последовательный 9 работает в соответствии с логикой, описанной в таблице №1.

Где tk - дискретные моменты времени (к=1, 2, ...), соответствующие моментам появления импульсов на входе "с" регистра 9.

Примеры конкретных реализацией регистра параллельно-последовательного приведены в литературе [3], [4].

В исходном состоянии во все разряды регистра 9 записывается логический высокий уровень ("1"), задаваемый формирователем логической единицы 11. На выходах "bn" всех разрядов регистра 9, а следовательно, и на каждом из входов "an" будет "1".

Затем происходит операция записи "0" в первый разряд регистра 9. Для этого в соответствии с таблицей №1 на вход "p/s" регистра 9 из блока управления 6 подается логический нуль "0", а на вход "d" регистра 9 из блока управления 6 поступает сигнал логического нуля ("0") длительностью, равной одному периоду следования импульсов, поступающих на вход "с" регистра 9 с генератора импульсов 2. При этом логический нуль ("0") записывается в первый разряд регистра 9 в режиме синхронного последовательного ввода данных. Синхронизация записи в разряды регистра 9 осуществляется сигналом на входе "с" регистра 9, поступающим с выхода генератора тактовых импульсов 2. Число импульсов, поданных на вход "с" регистра 9 равно одному. (При поступлении n тактовых импульсов логический нуль "0" будет записан в n-й разряд регистра 9).

Затем регистр 9 переводится в режим параллельной загрузки для чего на вход "p/s" регистра 9 из блока управления 6 подается "1", и на вход "с" регистра 9 подается один тактовый импульс. При этом в каждый из "n" разрядов регистра 9 запишется то состояние, в котором находится соответствующий вход "an" регистра 9. Так как на выходе "b1" первого разряда регистра 9 был задан "0", а на остальных выходах "bn" (n≠1) - "1", то все разряды регистра 9, в которые при параллельной загрузке запишутся "0", будут соответствовать входам регистра 9, имеющим связь (замыкание) с первым входом "a1" регистра 9. При этом вентили И 4 обеспечивают развязку между входами "an" и выходами "bn" регистра 9.

После этого регистр 9 переводится в режим последовательного ввода данных для чего на вход "p/s" регистра 9 из блока управления 6 подается "0", при этом на вход "d" регистра 9 подается "1", а на вход "с" последовательность (N+1) тактовых импульсов. Одновременно тактовые импульсы поступают на вход счетчика 7, который считает число поступающих импульсов при наличии разрешения с блока управления 6. С выхода "bN+1" регистра 9 (разряда N+1) информация в виде последовательного кода поступает в блок управления 6. При поступлении на второй вход блока управления 6 значения, равного "0", в нем формируется сигнал прерывания счета, и в контроллер 8 считывается текущее состояние счетчика 7, затем счет продолжается дальше до тех пор, пока с выхода "bN+1" регистра 9 не поступит очередной "0" или не поступит последний (N+1) тактовый импульс.

Таким образом, в памяти контроллера 8 окажутся записанными все номера разрядов регистра 9, в которых после параллельной загрузки оказались "0". Эти номера соответствуют входным контактам проверяемого объекта контроля 1 (входам регистра 9), имеющим замыкание с первым входом "a1" регистра 9.

Аналогичным образом, поочередно записывается "0" во второй разряд регистра 9, в третий разряд регистра 9 и т.д., каждый раз проверяется наличие связей "активируемого" входа регистра 9 (контакта объекта контроля 1) с последующими входами регистра 9. При этом для сокращения времени проверки из перечня "активируемых" входов исключаются входы, уже попавшие на предыдущих шагах в списки входов, имеющих замыкание.

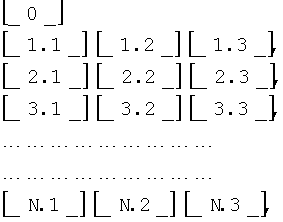

Графически вся описанная процедура может быть представлена следующим образом:

где:

[0] - установка исходного состояния регистра 9 (запись "1" во все разряды регистра 9);

[1.1]- запись "0" в первый разряд регистра 9;

[1.2] - параллельная загрузка;

[1.3] - последовательное считывание информации, записанной во всех разрядах регистра 9, с выхода "bN+1" последнего (N+1) разряда регистра 9 и запоминание номеров входов, имеющих замыкание с входом "a1";

[2.1] - запись "0" во второй разряд регистра 9;

[2.2] - параллельная загрузка;

[2.3] - последовательное считывание информации, записанной во всех разрядах регистра 9, с выхода "bN+1" последнего (N+1) разряда регистра 9 и запоминание номеров входов, имеющих замыкание с входом "a2";

[3.1] - запись "0" в третий разряд регистра 9;

[3.2] - параллельная загрузка;

[3.3] - последовательное считывание информации, записанной во всех разрядах регистра 9, с выхода "bN+1" последнего (N+1) разряда регистра 9 и запоминание номеров входов, имеющих замыкание с входом "а3";

[N.1] - запись "0" в N-й разряд регистра 9;

[N.2] - параллельная загрузка;

[N.3] - последовательное считывание информации, записанной во всех разрядах регистра 9, с выхода "bN+1" последнего (N+1) разряда регистра 9 и запоминание номеров входов, имеющих замыкание с входом "аN".

Таким образом после проведения проверки по всем входам в памяти контроллера 8 окажется полная информация о всех соединениях между входными контактами объекта, имеющихся в проверяемом объекте 1, которая через блок вывода 10 может быть выведена пользователю.

При эксплуатации предлагаемое устройство для контроля монтажных схем может работать в двух режимах:

- режим снятия эталонного образа ("маски"),

- режим контроля соединений.

В режиме снятия "маски" к устройству подключается в качестве объекта контроля 1 заведомо исправное изделие. После процедуры снятия маски в памяти контроллера 8 записывается эталонный образ ("маска"), с которым при последующих проверках сравниваются данные, получаемые при проведении проверки объекта контроля 1, и который при необходимости может быть выведен пользователю через блок вывода 10.

В результате сравнения данных, полученных при проверке объекта контроля 1, с эталонным образом ("маской"), хранящимся в памяти контроллера 8, который выполняет и сравнение, на блок вывода 10 поступает полная информация обо всех отклонениях проверяемого объекта 1 от эталона (как об отсутствующих соединениях, так и о лишних соединениях).

Таким образом, технический эффект, получаемый в результате включения в состав устройства для контроля монтажных схем, блока управления 6, счетчика 7, контроллера 8, регистра параллельно-последовательного 9, блока вывода 10, формирователя логической единицы 11, соединенных описанным образом, заключается в увеличении производительности и достоверности контроля монтажных схем за счет достижения полной автоматизации, как процесса контроля, так и процесса получения эталонного образа ("маски"). Кроме того, применение данного устройства требует наличия "физического" эталона однократно, только при создании эталонного образа конкретного объекта.

Предлагаемое устройство позволяет проверять правильность монтажных схем широкого класса объектов.

Результаты контроля, получаемые в блоке вывода 10, содержат полную информацию как о лишних, так и об отсутствующих связях в проверяемом объекте и не требуют дополнительной интерпретации.

Перечень используемой информации

1. Журнал "Электроника" №26, 1975, М.: Мир.

2. Авторское свидетельство СССР №593217, опубликовано 15.02.78 г. МПК G 06 F 15/467.

3. Шило В.Л. "Популярные цифровые микросхемы". Справочник. - М.: Радио и связь, 1987.

4. Гутников В.С. "Интегральная электроника в измерительных устройствах" 2 изд. - Л.: Энергоатомиздат, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля монтажных соединений | 1988 |

|

SU1608696A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля правильности соединений электрического монтажа различных радиоэлектронных устройств. Устройство содержит генератор импульсов и N логических вентилей И. В устройство также введены блок управления, счетчик, контроллер, регистр параллельно-последовательный, блок вывода и формирователь логической единицы. Элементы соединены между собой соответствующим образом. Технический результат - увеличение производительности и достоверности контроля, расширение функциональных возможностей, связанных с упрощением анализа полученных результатов контроля независимо от числа проверяемых цепей и числа одновременно замкнутых контактов. 2 ил.

Устройство для контроля монтажных схем, состоящее из генератора импульсов, N логических вентилей И, отличающееся тем, что вновь введены блок управления, счетчик, контроллер, регистр параллельно-последовательный, блок вывода и формирователь логической единицы, причем первый выход блока управления соединен с входом генератора импульсов, выход которого соединен с первым входом счетчика и управляющим входом "с" регистра параллельно-последовательного, второй выход блока управления соединен с управляющим входом "р/s" регистра параллельно-последовательного, третий выход блока управления соединен с последовательным входом "d" регистра параллельно-последовательного, четвертый выход блока управления соединен со вторым входом счетчика, выход которого соединен с первым входом контроллера, пятый выход блока управления соединен со вторым входом контроллера, первый выход которого соединен с первым входом блока управления, а второй выход контроллера - с входом блока вывода, выходы "bn" (n=1, 2, ...N) регистра параллельно-последовательного соединены с первыми входами N логических вентилей "И", выход формирователя логической единицы соединен со вторыми входами N логических вентилей "И" и с входом "aN+1" регистра параллельно-последовательного, а выходы N логических вентилей "И" соединены с входами "an" (n=1, 2, ...N) регистра параллельно-последовательного и N контактами проверяемого объекта контроля, а выход "dN+1" регистра параллельно-последовательного соединен со вторым входом блока управления.

| Устройство для контроля монтажных схем | 1976 |

|

SU593217A1 |

| Устройство для контроля соединений в электрическом монтаже | 1990 |

|

SU1758606A1 |

| Устройство для контроля монтажных схем | 1980 |

|

SU888136A1 |

| US 2003167932 13.06.2003 | |||

| US 2002194547 19.12.2002. | |||

Авторы

Даты

2007-01-10—Публикация

2005-06-02—Подача