Изобретение относится к вычисли- , тельной технике, электронике и может быть использовано при построении различных узлов и устройств цифровых ЭВМ и БИС.

Цель изобретения - упрощение модуля за счет сокращения числа внешних входов.

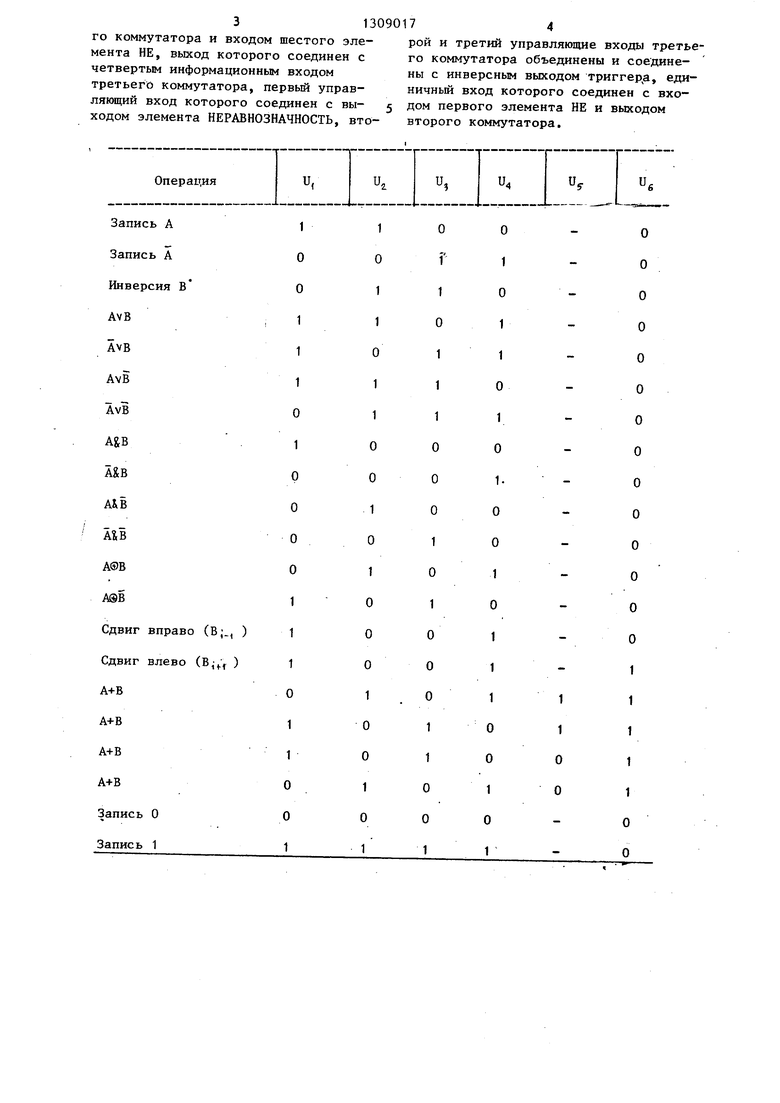

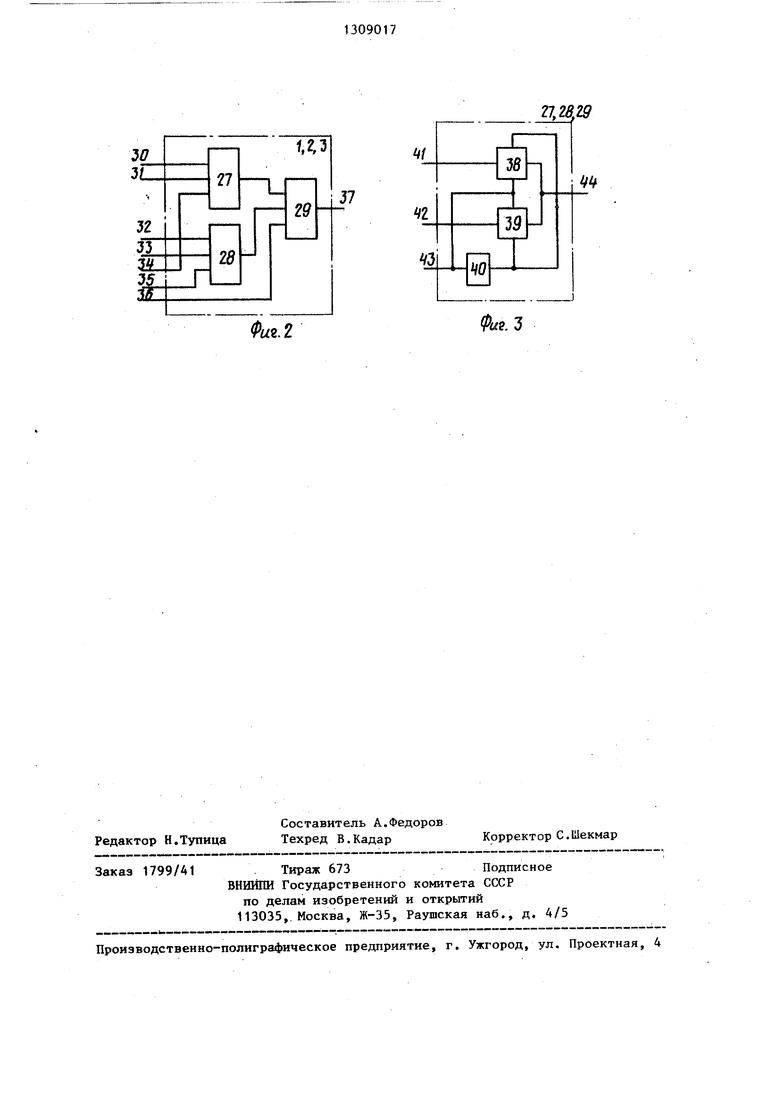

На фиг. 1 показана схема управляемого арифметического модуля; на фиг. 2 - схема коммутатора; на фиг. 3 - схема мультиплексора.

Управляемый арифметический модуль содержит коммутаторы 1-3, элементы НЕ 4-9, триггер 10, элемент И 11, элемент НЕРАВНОЗНАЧНОСТЬ 12, эле- мент И-НЕ 13, управляющие входы 14- 19, информационные входы 20-22, вход 23 переноса, синхровход 24, выход 25 результата и выход 26 переноса.

Коммутатор содержит мультиплексоры на двунаправленных ключах 27-29, информационные входы 30-33, управляющие входы 34-36, выход 37.

Мультиплексор содержит двунаправленные ключи 38 и 39, элемент НЕ 40, информационные входы 41 и 42, управляющий вход 43, выход 44.

Модуль работает следующим образом.

Ю

15

20

25

торы, триггер, элементы И и НЕ, причем 1-й (i 1,4) управляющий вход модуля соединен с i-м информационным входом первого коммутатора, первый управляющий вход которого соединен с прямым выходом триггера и выходом результата модуля, синхровход модуля соединен с синхровходом триггера, нулевой вход которого соединен с выходом первого элемента НЕ, первый и второй информационные входы модуля соединены с первым и вторым информационным входами второго коммутатора соответственно, отличающийся тем, что, с целью упрощения модуля за счет сокращения числа внешних входов, в него введены третий коммутатор, элемент НЕРАВНОЗНАЧНОСТЬ, элемент И-НЕ и элементы НЕ, причем второй управляющий вход первого коммутатора соединен с прямым выходом триггера, третий управляющий вход первого коммутатора соединен с третьим информационным входом модуля и первым входом элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с вторым управляющим входом модуля и входом второго элемента НЕ, выход которого соединен с первым входом элеНа информационные входы 20-22 моду-30 „ента И-НЕ, второй вход которого сое- ля подаются значения сигналов: на динен с выходом третьего элемента НЕ, вход 20 - сигнал А; значения i-ro вход которого соединен с третьим уп- разряда операнда А, на вход 21 - сигравляющим входом модуля, первый и четвертый управляющие входы которого сое;динены соответственно с третьим и четвертым входами элемента И-НЕ, выход которого соединен с первым управляющим входом второго коммутатора, третий информационный вход которого соединен с выходом четвертого элемента НЕ, вход которого соединен с четвертым информационным входом второго коммутатора и выходом пятого элемента НЕ, вход которого соединен с выходом первого коммутатора, второй управляющий вход второго коммутатора соединен с пятым управляющим входом модуля и первым входом элемента И, выход которого соединен с выходом переноса модуля, второй вход элемента И соединен с выходом третьего коммутатора, первый и второй информационные входы которого объединены и соединены с третьим управляющим входом второго коммутатора и входом переноса модуля, шестой управляющий вход которого соединен с третьим информационным входом третьенал В,

с выхода старшего разряда

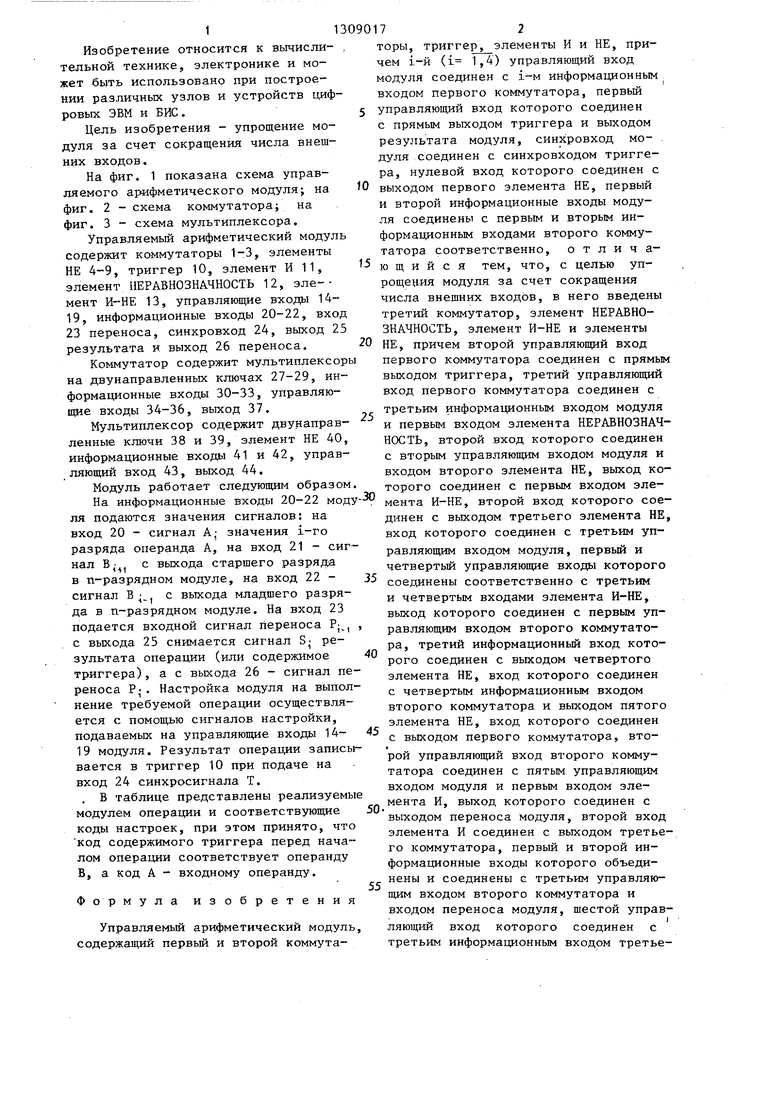

в п-разрядном модуле, на вход 22 - сигнал В с выхода младшего разряда в п-разрядном модуле. На вход 23 подается входной сигнал переноса Pj, с выхода 25 снимается сигнал S результата операции (или содержимое триггера), а с выхода 26 - сигнал переноса . Настройка модуля на выполнение требуемой операции осуществляется с помощью сигналов настройки, подаваемых на управляющие входы 14- 19 модуля. Результат операид1и записывается в триггер 10 при подаче на вход 24 синхросигнала Т. . В таблице представлены реализуемы модулем операции и соответствующие коды настроек, при этом принято, что код содержимого триггера перед началом операции соответствует операнду В, а код А - входному операнду.

Ф о р мула изобретения

Управляемый арифметический модуль, содержащий первьй и второй коммута

5

0

5

торы, триггер, элементы И и НЕ, причем 1-й (i 1,4) управляющий вход модуля соединен с i-м информационным входом первого коммутатора, первый управляющий вход которого соединен с прямым выходом триггера и выходом результата модуля, синхровход модуля соединен с синхровходом триггера, нулевой вход которого соединен с выходом первого элемента НЕ, первый и второй информационные входы модуля соединены с первым и вторым информационным входами второго коммутатора соответственно, отличающийся тем, что, с целью упрощения модуля за счет сокращения числа внешних входов, в него введены третий коммутатор, элемент НЕРАВНОЗНАЧНОСТЬ, элемент И-НЕ и элементы НЕ, причем второй управляющий вход первого коммутатора соединен с прямым выходом триггера, третий управляющий вход первого коммутатора соединен с третьим информационным входом модуля и первым входом элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с вторым управляющим входом модуля и входом второго элемента НЕ, выход которого соединен с первым входом эле0 „ента И-НЕ, второй вход которого сое- динен с выходом третьего элемента НЕ, вход которого соединен с третьим уп-

„ента И-НЕ, второй вход которого сое- динен с выходом третьего элемента НЕ, вход которого соединен с третьим уп-

равляющим входом модуля, первый и четвертый управляющие входы которого сое;динены соответственно с третьим и четвертым входами элемента И-НЕ, выход которого соединен с первым управляющим входом второго коммутатора, третий информационный вход которого соединен с выходом четвертого элемента НЕ, вход которого соединен с четвертым информационным входом второго коммутатора и выходом пятого элемента НЕ, вход которого соединен с выходом первого коммутатора, второй управляющий вход второго коммутатора соединен с пятым управляющим входом модуля и первым входом элемента И, выход которого соединен с выходом переноса модуля, второй вход элемента И соединен с выходом третьего коммутатора, первый и второй информационные входы которого объединены и соединены с третьим управляющим входом второго коммутатора и входом переноса модуля, шестой управляющий вход которого соединен с третьим информационным входом третье313090174

го коммутатора и входом шестого эле-рой и третий управляющие входы третье- мента НЕ, выход которого соединен сго коммутатора объединены и соедине- четвертым информационным входомны с инверсным выходом триггеда, едн- третьего коммутатора, первый управ-ничньй вход которого соединен с вхо- ляющий вход которого соединен с вы- Дом первого элемента НЕ и выходом ходом элемента НЕРАВНОЗНАЧНОСТЬ, вто-второго коммутатора.

27,252

L

3L.

27

t.2,3

32

29

37

33

I

i

25

«e.2

Редактор H.Тупица

Составитель А.Федоров Техред В.Кадар

Заказ 1799/А1

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

fe3

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1980 |

|

SU903865A1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Управляемый арифметический модуль | 1979 |

|

SU855654A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

Изобретение относится к области автоматики и вычислительной техники и предназначено для построения различных блоков и устройств цифровой обработки данных. Цель изобретения - повышение надежности модуля за счет сокращения числа внешних входов. Модуль содержит информационные и управляющие входы 20-23, 14-19, коммутаторы 1, 2, 3, элементы И 11, НЕ 4-9, И-НЕ 13, НЕРАВНОЗНАЧНОСТЬ 12, триггер 10, выход 25 результата и выход 26 переноса. Модуль реализует логические и арифметические операции над однобитовьми операндами, а также операции сдвиг и запись операнда. Настройка модуля на реализацию требуемой операции осуществляется подачей сигналов настройки на управляющие входы модуля. Результат операции записывается в триггер и снимается с его прямого выхода. Соединение п модулей по входам и выходам результата и переноса позволяет обра- батьшать п-разрядные операнды. 1 табл., 3 ил. § (/) А- at.f Ue

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляемый арифметический модуль | 1980 |

|

SU903865A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-09-30—Подача