Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к электронике и более конкретно - к цифровым сигнальным процессорам (ЦСП, DSP) с конфигурируемыми блоками умножения-накопления (УН, MAC) и арифметико-логическими устройствами (АЛУ, ALU).

Предшествующий уровень техники

DSP - это специализированные микропроцессоры, которые специально разработаны для того, чтобы очень быстро выполнять математические вычисления. DSP широко используются во множестве электронных модулей, таких как проигрыватели компакт-дисков, накопители на магнитных дисках персональных компьютеров (PC), модемные банки, аудиоустройства, сотовые телефоны и т.д. В сотовых телефонах потребности в возможностях выполнения вычислений посредством DSP продолжают расти, подкрепляемые увеличивающимися потребностями прикладных программ, таких как модемной обработки 3G (3-го поколения), определение положения, обработка изображений и видео, 3-мерные игры и так далее. Эти прикладные программы требуют DSP, которые могут исполнять вычисления быстро и эффективно.

DSP обычно содержит блок УН (умножения-накопления) и АЛУ (арифметико-логическое устройство). Блок УН используется для операций умножения с накоплением, которые обычно используются в фильтрации и обработке сигналов. АЛУ используется для сложения, вычитания, логических операций, сдвига и операций манипулирования битами. DSP может также содержать множество блоков УН для повышения вычислительной производительности. Примерная архитектура DSP с двумя блоками УН описана в заявке № 6557022 на патент США "Digital Signal Processor with Coupled Multiply-Accumulate Units", поданной 29 апреля 2003.

Целями любой структуры DSP являются (1) достижение самого высокого количества операций в единицу времени и (2) обеспечение гибкости для выполнения операций различных типов одновременно, чтобы лучше использовать доступное оборудование. Архитектуры DSP, которые могут удовлетворять этим целям, особенно желательны для удовлетворения запросов на обработку современных прикладных программ.

Сущность изобретения

Архитектуры DSP, имеющие улучшенную эффективность, описаны ниже. В одном варианте осуществления DSP включает в себя два блока УН и два АЛУ, где одно из АЛУ заменяет сумматор для одного из двух блоков УН (БУН). Этот DSP может быть конфигурирован, возможно, на основании "команда за командой", чтобы работать в конфигурации двойной БУН/одинарное АЛУ, конфигурации одинарный БУН/двойное АЛУ или конфигурации двойной БУН/двойное АЛУ. Гибкость конфигурации позволяет DSP обрабатывать различные типы операций по обработке сигналов и улучшает использование доступного оборудования. DSP дополнительно включает в себя регистры конвейера, которые прерывают критические пути (тракты) и позволяют DSP работать с более высокой тактовой частотой для большей производительности. Другие варианты осуществления архитектуры DSP также описаны ниже.

Различные аспекты и варианты осуществления изобретения описаны более подробно ниже.

В одном аспекте представлен процессор, содержащий: первый блок умножения-накопления (УН), выполненный с возможностью принимать и перемножать первый и второй операнды, чтобы получить первый промежуточный результат, сохранять первый промежуточный результат в первом регистре, суммировать сохраненный первый промежуточный результат с третьим операндом и обеспечивать первый выходной результат; и второй блок УН, выполненный с возможностью принимать и перемножать четвертый и пятый операнды, чтобы получить второй промежуточный результат, сохранять второй промежуточный результат во втором регистре, суммировать шестой операнд или с сохраненным вторым промежуточным результатом или суммой сохраненных первого и второго промежуточных результатов и обеспечивать второй выходной результат.

В другом аспекте представлен процессор, содержащий: первый блок умножения-накопления (УН), включающий в себя первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды и обеспечивать первый промежуточный результат, и первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать первый промежуточный результат, третий операнд, и по меньшей мере один дополнительный операнд, выполнять операции над принятыми операндами и обеспечивать первый выходной результат; и второй блок УН, включающий в себя второй умножитель, выполненный с возможностью принимать и умножать четвертый и пятый операнды и обеспечивать второй промежуточный результат, первый сумматор, выполненный с возможностью суммировать второй промежуточный результат или с нулем или с первым промежуточным результатом из первого блока УН, и второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом и обеспечивать второй выходной результат.

В другом аспекте представлен процессор, содержащий: первый блок умножения-накопления (УН), включающий в себя первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды и обеспечивать первый промежуточный результат, первый регистр, выполненный с возможностью хранить первый промежуточный результат и обеспечивать сохраненный первый промежуточный результат, и первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать и выполнять операции над сохраненным первым промежуточным результатом, третьим операндом, по меньшей мере, одним другим операндом или их комбинацией и обеспечивать первый выходной результат; и второй блок УН, включающий в себя второй умножитель, выполненный с возможностью принимать и перемножать четвертый и пятый операнды и обеспечивать второй промежуточный результат, второй регистр, выполненный с возможностью хранить второй промежуточный результат и выдавать сохраненный второй промежуточный результат, первый сумматор, выполненный с возможностью суммировать сохраненный второй промежуточный результат или с нулем, или с сохраненным первым промежуточным результатом из первого блока УН, и второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом и выдавать второй выходной результат.

В другом аспекте представлено беспроводное устройство, содержащее: первый блок умножения-накопления (УН), включающий в себя первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды и обеспечивать первый промежуточный результат, и первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать первый промежуточный результат, третий операнд и по меньшей мере один дополнительный операнд, выполнять операции над принятыми операндами и выдавать первый выходной результат; второй блок УН, включающий в себя второй умножитель, выполненный с возможностью принимать и перемножать четвертый и пятый операнды и выдавать второй промежуточный результат, первый сумматор, выполненный с возможностью суммировать второй промежуточный результат или с нулем, или первым промежуточным результатом из первого блока УН, и второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом и выдавать второй выходной результат; тракт АЛУ, включающий в себя блок сдвига, выполненный с возможностью принимать и сдвигать седьмой операнд или восьмой операнд и обеспечивать третий промежуточный результат, и второе АЛУ, выполненное с возможностью выполнять операции над третьим промежуточным результатом, седьмым операндом, восьмым операндом или их комбинацией и выдавать третий выходной результат; и файл регистров, выполненный с возможностью выдавать с первого по восьмой операнды для первого и второго блоков УН и тракта АЛУ и сохранять с первого по третий выходные результаты от первого и второго блоков УН и тракта АЛУ.

Краткое описание чертежей

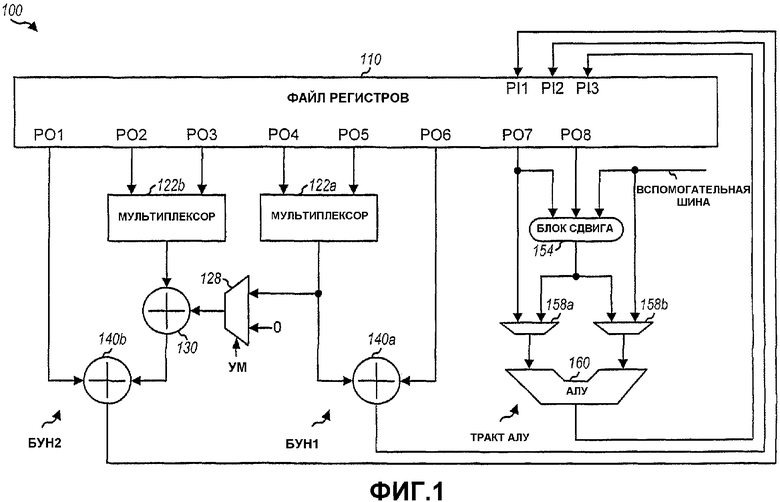

Фиг. 1 иллюстрирует DSP с двумя блоками УН и одним АЛУ.

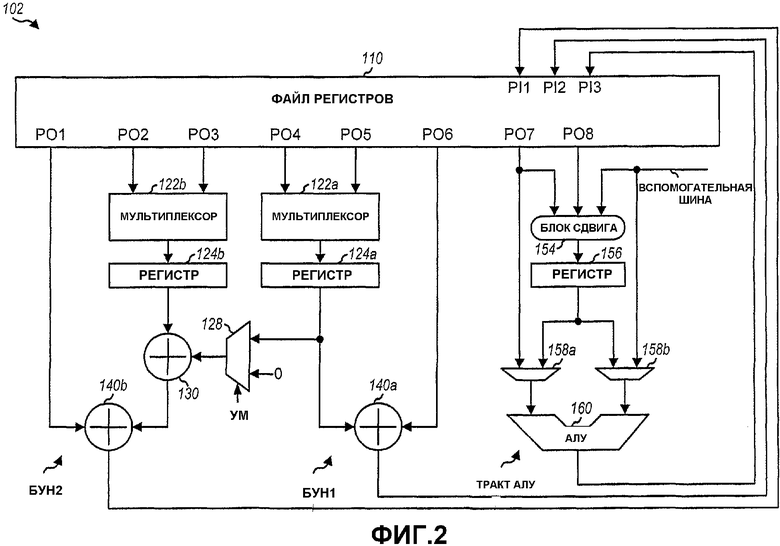

Фиг. 2 иллюстрирует конвейерный DSP с двумя блоками УН и одним АЛУ.

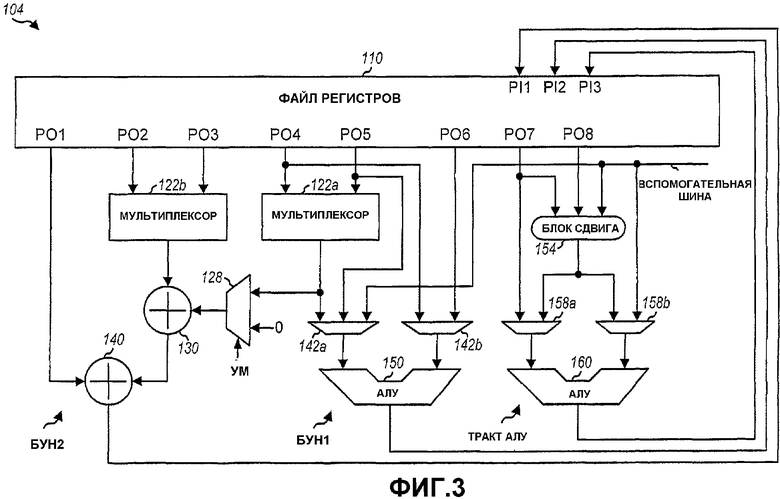

Фиг. 3 иллюстрирует DSP с конфигурируемыми с двумя блоками УН и двумя АЛУ.

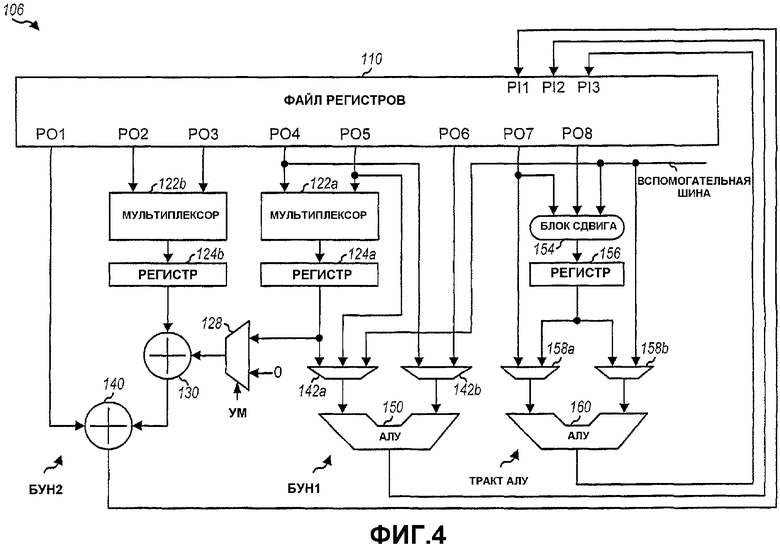

Фиг. 4 иллюстрирует конфигурируемый конвейерный DSP с двумя блоками УН и двумя АЛУ.

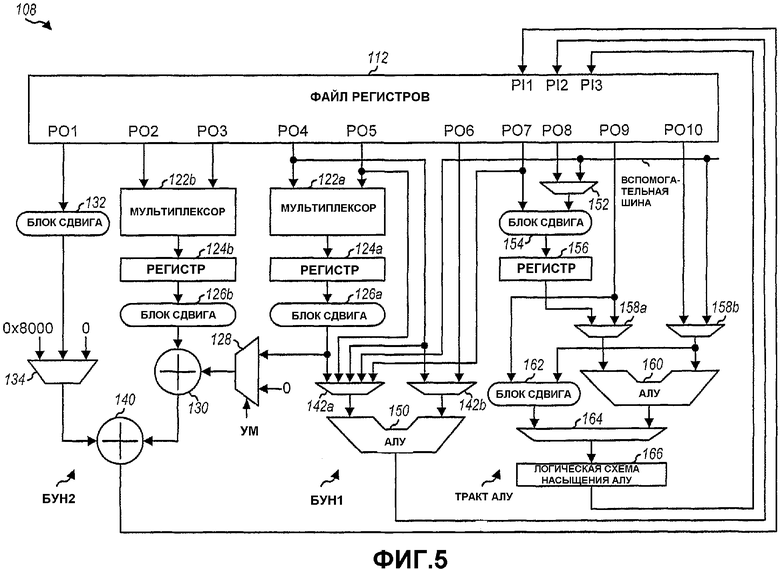

Фиг. 5 иллюстрирует другой конфигурируемый конвейерный DSP с двумя блоками УН и двумя АЛУ.

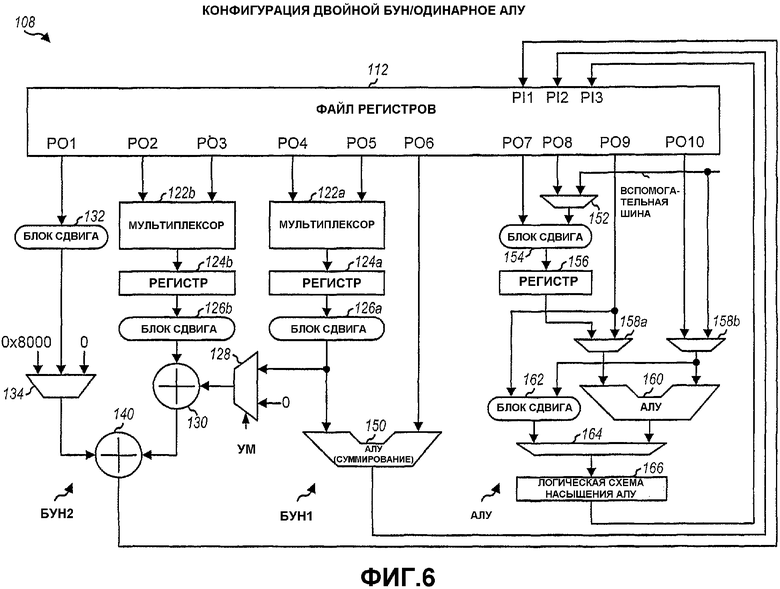

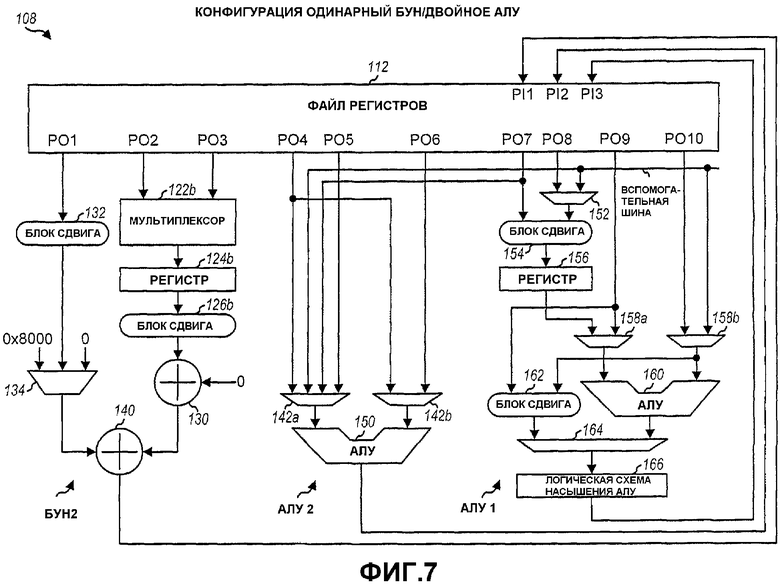

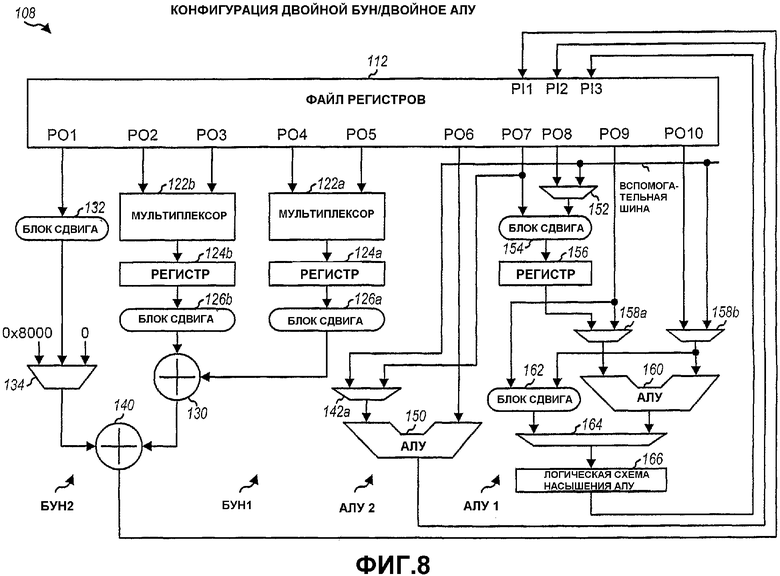

Фиг. 6, 7 и 8 иллюстрируют DSP согласно фиг. 5, работающий в конфигурациях двойной БУН/одинарное АЛУ, одинарный БУН/двойное АЛУ и двойной БУН/двойное АЛУ, соответственно.

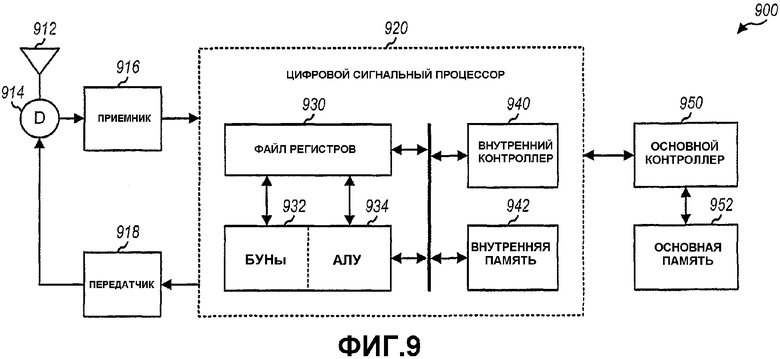

Фиг. 9 иллюстрирует беспроводное устройство в системе радиосвязи.

Подробное описание

Слово "примерный" используется здесь для обозначения "служащий в качестве примера, случая или иллюстрации". Любой вариант осуществления или конструкция, описанные ниже в качестве "примерных", не обязательно должны быть рассмотрены как предпочтительные или выгодные по сравнению с другими вариантами осуществления или конструкциями.

Фиг. 1 показывает блок-схему DSP 100 с два блоками УН и одним АЛУ. Файл 110 регистров содержит банк регистров общего назначения, которые могут использоваться для хранения операндов и результатов для блоков УН и АЛУ. Файл 110 регистров подсоединен к и обменивается данными с блоком памяти (не показан на фиг. 1). Для варианта осуществления, показанного на фиг. 1, файл 110 регистров имеет три входных порта, обозначенных как PI1-PI3 и восемь выходных портов, обозначенных как PO1-PO8. В общем случае файл регистров может иметь любое количество входных и выходных портов.

Для первого блока УН (БУН1) умножитель 122a принимает и перемножает два операнда с выходных портов PO4 и PO5 файла 110 регистров и подает результат на один вход сумматора 140a. Сумматор 140a принимает другой операнд от выходного порта PO6, суммирует два входных операнда и выдает выходной результат на входной порт PI2 файла 110 регистров. Мультиплексор 128 принимает выходной результат умножителя 122a и значение нуля на два входа и выдает или выходной результат умножителя, или ноль в зависимости от сигнала управления мультиплексором (УМ, МС).

Для второго блока УН (БУН2), умножитель 122b принимает и перемножает два операнда от выходных портов PO2 и PO3 файла 110 регистров и выдает свой результат на один вход сумматора 130. Сумматор 130 также принимает выходной результат мультиплексора 128, суммирует два входных операнда и выдает выходной результат на один вход сумматора 140b. Сумматор 140b принимает другой операнд с выходного порта PO1, суммирует два входных операнда и подает выходной результат на входной порт PI1 файла 110 регистров.

Для тракта АЛУ блок 154 сдвига принимает два входа с выходных портов PO7 и PO8 файла 110 регистров и третий вход с вспомогательной шины. Вспомогательная шина передает непосредственные значения, внедренные в команду, в АЛУ. Блок 154 сдвига выбирает одни из этих трех входных данных, сдвигает операнд от выбранного входа на заданное количество битов (например, 0, 1, 2 или 3 бита влево) и подает выходной результат на один вход мультиплексоров 158a и 158b. Мультиплексор 158a также принимает операнд с выходного порта PO7 и подает один из двух входов (входных данных) на один вход АЛУ 160. Мультиплексор 158b также принимает непосредственные значения с вспомогательной шины и выдает один из двух входов на другой вход АЛУ 160. АЛУ 160 выполняет операции над своими входными операндами и выдает выходной результат на вход PI3 файла 110 регистров.

Модули в DSP 110 могут быть созданы с любым числом битов. В качестве примера, умножители 122a и 122b могут быть умножителями 16x16 битов, сумматор 130 может быть 32-битовым сумматором, сумматоры 140a и 140b могут быть 40-битовыми сумматорами, и блок 154 сдвига и АЛУ 160 могут быть 40-битовыми модулями. Аналогично, файл 110 регистров может быть разработан с любым количеством битов для его входных и выходных портов. В качестве примера, выходные порты PO1, PO6 и PO7 могут выдавать 40-битовые операнды, выходные порты PO2, PO3, PO4 и PO5 могут выдавать 16-битовые операнды, выходной порт PO8 может выдавать 16-битовые или 40-битовые операнды, и входные порты PI1, PI2 и PI3 могут принимать 40-битовые результаты. Выше приведены примерные значения, и другие количества битов также могут быть использованы.

DSP 100 может быть сконфигурирован так, чтобы работать или как два независимых блока УН, или как два соединенных блока УН. Для конфигурации с независимыми двумя БУН мультиплексор 128 управляется так, чтобы передавать нулевое значение к сумматору 130, и БУН1 и БУН2 работают независимо и могут выполнять две операции УН одновременно над различными наборами операндов. Для конфигурации с соединенными двумя БУН мультиплексор 128 управляется так, чтобы передавать выходной результат умножителя 122a, и БУН1 и БУН2 вместе выполняют вычисление: (B*C)±(D*E) или А±(B*C)±(D*E), где А-E являются операндами с выходных портов PO1-PO5 соответственно. Эти два вычисления очень полезны для операций комплексного умножения и накопления.

Крайне желательно увеличить тактовую частоту для DSP, чтобы увеличить объем обработки в единицу времени (т.е. чтобы выполнить большее количество операций в секунду). Например, если тактовая частота может быть увеличена на 50%, то на 50% операций в секунду больше может быть выполнено одним и тем же оборудованием. Однако так как тракт с соединенными двумя БУН и тракт АЛУ каждый имеет множество операций последовательно на своем критическом пути, архитектура DSP, показанная на фиг. 1, хорошо не масштабируется, когда тактовая частота увеличивается. Тракт с соединенными двумя БУН имеет операции умножения и две - суммирования на его критическом пути через умножитель 122a или 122b и сумматоры 130 и 140b. Тракт АЛУ имеет сдвиг и операцию суммирования в своем критическом пути. Эти операции требуют некоторого времени для завершения и, таким образом, будут ограничивать тактовую частоту, которая может быть использована для DSP.

Фиг. 2 иллюстрирует блок-схему конвейерного DSP 102 с двумя блоками УН и одним АЛУ. DSP 102 включает в себя все элементы DSP 100, показанного на фиг. 1. DSP 102 дополнительно включает в себя (1) регистр 124a, включенный между умножителем 122a и сумматором 140a, (2) регистр 124b, включенный между умножителем 122b и сумматором 130, и (3) регистр 156, включенный между блоком 154 сдвига и мультиплексорами 158a и 158b.

Регистры 124a, 124b и 156 являются регистрами конвейера, вставленными в критические тракты БУН1, БУН2 и тракта АЛУ соответственно. Эти регистры разбивают (прерывают) критические пути и позволяют тактировать DSP 102 с более высокой частотой. Цикл выполнения для DSP 102 разбивается на два каскада конвейера. На первом каскаде конвейера умножители 122a и 122b выбирают операнды из файла 110 регистров, выполняют операции умножения и сохраняют свои результаты в регистрах 124a и 124b соответственно. Аналогично для тракта АЛУ блок 154 сдвига принимает входные данные из файла 110 регистров и/или непосредственной шины, выполняет сдвиги как задано и сохраняет результаты в регистре 156. На втором каскаде конвейера сумматоры в БУН1 и БУН2 и АЛУ 160 в тракте АЛУ являются активными. Для конфигурации с независимыми двумя БУН сумматор 140a суммирует выходной результат регистра 124a с операндом из выходного порта PO6 и выдает выходной результат на входной порт PI2, и сумматор 140b суммирует выходной результат регистра 124b с операндом с выходного порта PО1 и выдает выходной результат на входной порт PI1. Для конфигурации с соединенными двумя БУН сумматор 130 суммирует выходные результаты регистров 124a и 124b, и сумматор 140b суммирует выходной результат сумматора 130, и операнд с выходного порта PO1 и выдает выходной результат на входной порт PI1. Для тракта АЛУ, АЛУ 160 принимает выходной результат регистра 156 и/или операнды от выходного порта PO7 и вспомогательной шины, выполняет операции над входными операндами и выдает выходной результат на входной порт PI3.

DSP 102 может обеспечивать все функциональные возможности DSP 100. Однако DSP 102 может быть тактирован с более высокой частотой, чем DSP 100 (вплоть до значения в два раза быстрее), так как критические тракты в DSP 102 разбиты конвейерными регистрами. Это также позволяет DSP 102 достигать более высокой общей производительности, чем DSP 100. Регистр конвейера может также быть вставлен между сумматорами 130 и 140b, чтобы дополнительно разбить этот тракт, если он является новым критическим путем с намного более длинной задержкой, чем все другие пути в DSP 102. В этом случае цикл выполнения для DSP 102 может быть разбит на три каскада конвейера.

Архитектура DSP, показанная на фиг. 1, имеет ограниченную возможность конфигурации и не соответствует всем типам вычислений обработки сигналов. DSP 100 может выполнять две (или независимые или объединенные) операции УН и одну операцию АЛУ параллельно. Для некоторых приложений может быть предпочтительно иметь две операции АЛУ и одну операцию УН, выполняемых параллельно, или иметь две операции УН и две операции АЛУ, все выполняемые параллельно. Приложения, для которых предпочтительны две операции АЛУ параллельно, включают в себя вычисления метрики суммы абсолютных разностей (SAD) для оценки движения при сжатии видео, сравнение шаблонов при распознавании речи и вычисления расстояния путей при декодировании по Витерби, которые все известны из уровня техники.

Фиг. 3 иллюстрирует блок-схему конфигурируемого DSP 104 с двумя блоками УН и двумя АЛУ. DSP 104 включает в себя большинство элементов DSP 100, показанного на фиг. 1. DSP 104 дополнительно включает в себя мультиплексоры 142a и 142b и АЛУ 150, которое заменяет сумматор 140a в DSP 100.

Для варианта осуществления, показанного на фиг. 3, мультиплексор 142a принимает выходной результат умножителя 122a и операнды от выходного порта PO5 и вспомогательной шины. Мультиплексор 142a выбирает один из своих трех входов и выдает операнд с выбранного входа на один вход АЛУ 150. Мультиплексор 142b принимает операнды от выходных портов PO4 и PO6, выбирает один из двух входов и выдает операнд с выбранного входа на другой вход АЛУ 150. АЛУ 150 может выполнять логические операции и манипуляции над битами наряду с операциями суммирования и вычитания над своими входными операндами и выдавать выходной результат на входной порт PI2.

Фиг. 3 иллюстрирует использование конфигурируемых выходных портов PO4, PO5 и PO6 файла 110 регистров для подачи данных (поддержки) на БУН1 и АЛУ 150. Это уменьшает количество выходных портов, необходимых для подачи данных на БУН и АЛУ, что может упростить конструкцию файла регистров. Фиг. 3 также иллюстрирует конкретный пример подсоединения АЛУ 150 к выходным портам файла 110 регистров и к другим модулям в DSP 104. Другие подключения также возможны. Например, мультиплексоры 142a и 142b могут иметь большее количество входов, чтобы принять большее количество операндов, и/или могут принимать операнды от других выходных портов файла 110 регистров.

DSP 104 может использоваться в различных конфигурациях, которые перечислены в Таблице 1. Эти различные конфигурации могут быть выбраны, подходящим образом устанавливая подключения для различных модулей в DSP 104, например, используя команды DSP. Конфигурация для DSP 104 может быть изменена динамически, например, на основании команда-за-командой.

Для DSP 104 некоторые из операндов совместно используются в некоторых из конфигураций из-за ограниченного количества выходных портов и соединений.

Гибкость использования DSP в различных конфигурациях позволяет DSP лучше адаптироваться и приспосабливаться к различным типам операций по обработке сигналов. Это также позволяет лучше использовать доступное оборудование и повысить общую производительность. Различные конфигурации для DSP иллюстрируются ниже.

Фиг. 4 иллюстрирует блок-схему конфигурируемого конвейерного DSP 106 с два блоками УН и двумя АЛУ. DSP 106 включает в себя большинство элементов DSP 104, показанного на фиг. 3. DSP 106 дополнительно включает в себя регистры 124a, 124b и 156 конвейера, которые имеются на выходе умножителей 122a и 122b и блока 154 сдвига соответственно. DSP 106 может поддерживать все конфигурации, показанные в Таблице 1 для DSP 104. Однако DSP 106 может работать на более высокой тактовой частоте, чем DSP 104, так как регистры 124a, 124b и 156 конвейера прерывают критические пути для БУН1, БУН2 и тракта АЛУ соответственно.

Путь передачи данных DSP может быть разработан с большим количеством модулей и/или соединений, чем тот, что показан на фиг. 3 и 4, чтобы достичь еще большей гибкости и функциональных возможностей. Кроме того, файл регистров может быть снабжен дополнительными выходным портами, чтобы поддерживать большую гибкость при выборе операндов.

Фиг. 5 иллюстрирует блок-схему другого конфигурируемого конвейерного DSP 108 с двумя блоками УН и двумя АЛУ. DSP 108 включает в себя большинство элементов DSP 106, показанного на фиг. 4. Однако DSP 108 включает в себя файл 112 регистров, имеющий десять выходных портов, который заменяет файл 110 регистров, имеющий восемь выходных портов. DSP 108 дополнительно включает в себя дополнительные модули и соединения для БУН1 и БУН2 и тракта АЛУ, как описано ниже.

Для БУН1 блок 126a сдвига принимает выходной результат регистра 124a, сдвигает свой входной операнд на заданное количество битов и выдает выходной результат на один вход мультиплексоров 128 и 142a. Мультиплексор 142a также принимает операнды от выходных портов PO4, PO5 и PO7 и вспомогательной шины. Мультиплексор 142a выдает один из своих пяти входов на один вход АЛУ 150.

Для БУН2 блок 126b сдвига принимает выходной результат регистра 124b, сдвигает свой входной операнд на заданное количество битов и выдает выходной результат на сумматор 130. Блок 132 сдвига принимает операнд от выходного порта PО1, сдвигает свой входной операнд на заданное количество битов и выдает выходной результат на один вход мультиплексора 134. Мультиплексор 134 также принимает значения '0' и '0×8000' и выдает одни из своих трех входных данных на сумматор 140. В частности, мультиплексор 134 выдает это значение '0', когда никакое суммирование не требуется для сумматора 140, значение '0×8000' для округления и операнд с выходного порта PO1, когда выполняется накопление.

Для тракта АЛУ мультиплексор 152 принимает операнды от выходного порта PO8 и вспомогательной шины и выдает выходной результат на блок 154 сдвига. Блок 154 сдвига также принимает операнд от выходного порта PO7, выбирает один из двух входов, сдвигает операнд с выбранного входа на заданное количество битов и выдает выходной результат на регистр 156. Мультиплексор 158a принимает выходной результат регистра 156 и операнд от выходного порта PO9, выбирает один из двух входов и выдает операнд с выбранного входа на один вход АЛУ 160. Мультиплексор 158b принимает операнды от выходного порта PO10 и вспомогательной шины, выбирает один из двух входов и выдает операнд с выбранного входа на другой вход АЛУ 160. АЛУ 160 выполняет операции над своими входными операндами и выдает выходной результат на мультиплексор 164. Блок 162 сдвига принимает операнды от выходного порта PO9 и мультиплексора 158b на двух входах, выбирает один из этих двух входов, сдвигает операнд с выбранного входа на заданное количество битов и выдает выходной результат на мультиплексор 164. Мультиплексор 164 выдает один из двух входов к модулю 166 насыщения АЛУ, который выполняет операцию «насыщения» полученного значения и выдает значение с насыщением на вход PI3.

Блоки 126a, 126b и 132 сдвига обеспечиваются в БУН1 и БУН2, чтобы обработать ряд различных упорядочений величины. Блоки 154 и 162 сдвига обеспечиваются в тракте АЛУ для операций сдвига. Каждый из этих блоков сдвига может быть индивидуально конфигурирован, чтобы сдвинуть свой входной операнд, например, на 0, 1, 2 или 3 бита влево или на некоторое другое количество битов сдвига. Мультиплексор 134 обеспечивает дополнительную точность посредством подачи '0×8000' для округления, которое обеспечивает дополнительно полбита точности.

DSP 108 имеет следующие отличия от DSP 100, изображенного на фиг. 1. Во-первых, регистры 124a и 124b конвейера расположены на выходе умножителей 122a и 122b в БУН1 и БУН2 соответственно и регистр 156 конвейера расположен на выходе блока 154 сдвига в тракте АЛУ. Во-вторых, сумматор 140a в БУН1 был заменен АЛУ 150, которое может выполнять логические операции и манипуляции над битами наряду с суммированием и вычитанием. В-третьих, блок 162 сдвига и два дополнительных выходных порта PO9 и PO10 в файле 112 регистров были добавлены для тракта АЛУ. В-четвертых, различные новые соединения теперь обеспечиваются в АЛУ 150 для БУН1.

DSP 108 может поддерживать все конфигурации, показанные в Таблице 1 для DSP 104 на фиг. 3. DSP 108 может поддерживать различные типы и комбинации операций из-за дополнительных блоков сдвига, мультиплексоров, выходных портов и соединений. DSP 108 может также поддерживать более высокую тактовую частоту, так как регистры 124a, 124b и 156 конвейера прерывают критические тракты для БУН1, БУН2 и тракта АЛУ соответственно.

Фиг. 6 иллюстрирует DSP 108, работающий в конфигурации двойной БУН/одинарное АЛУ. В этой конфигурации БУН1 и БУН2 могут быть использованы независимо или в комбинации с помощью соответствующего управления мультиплексором 128. АЛУ 150 принимает выходной результат блока 126a сдвига (через мультиплексор 142a, который не показан на фиг. 6 для ясности) и операнд от выходного порта PO6 (через мультиплексор 142b, который также не показан). Для этой конфигурации АЛУ 150 функционирует как сумматор и выполняет суммирование над двумя входными операндами.

Фиг. 7 иллюстрирует DSP 108, работающий в конфигурации одинарный БУН/двойное АЛУ. В этой конфигурации БУН1 обходится, а БУН2 выполняет операции. Мультиплексор 142a может принимать операнды с выходных портов PO4, PO5 и PO7 и вспомогательной шины, выбирать один из этих четырех входов и выдавать операнд с выбранного входа на один вход АЛУ 150. Мультиплексор 142b может принимать операнды от выходных портов PO4 и PO6, выбирать один из этих двух входов и выдавать операнд с выбранного входа на другой вход АЛУ 150. АЛУ 150 может выполнять любую операцию АЛУ над своими входными операндами.

Фиг. 8 иллюстрирует DSP 108, работающий в конфигурации двойной БУН/двойное АЛУ. В этой конфигурации БУН1 и БУН2 используются в конфигурации с объединенными двумя БУН, а мультиплексор 128 опущен для ясности. Мультиплексор 142a может принимать операнды от выходного порта PO7 и вспомогательной шины, выбирать один из этих двух входов и выдавать операнд с выбранного входа на один вход АЛУ 150. АЛУ 150 может также принимать операнд с выходного порта PO6 на своем другом входе и выполнять любую операцию АЛУ над своими входными операндами.

DSP 104 и 106 могут также использоваться в конфигурациях двойной БУН/одинарное АЛУ, одинарный БУН/двойное АЛУ и двойной БУН/двойное АЛУ способом, подобным показанному на фиг. 6, 7 и 8 для DSP 108. Однако соединения для DSP 104 и 106 для этих различных конфигураций могут отличаться от соединений для DSP 108, так как DSP 104 и 106 имеют меньшее количество соединений, выходных портов и мультиплексоров, чем DSP 108.

Конфигурируемые архитектуры для DSP 104, 106 и 108 позволяют этим DSP выполнять различные типы и комбинации вычислений в одиночной команде. Например, следующие типы вычисления и комбинации могут быть выполнены этими DSP в одной команде:

A=B+C; D=E+F; G=H+(I*J).

A=B+C; D=E-F; G=H+(I*J)+(K*L).

A=(B<<3)+C; D=E&F; G=H-(I*J).

Входные операнды для вычислений, показанных выше, могут приходить с выходных портов файла регистров и вспомогательной шины. Три результата A, D и G для этих вычислений можно подавать на три входных порта файла регистров. Множество других типов и комбинаций вычислений также могут быть выполнены DSP 104, 106 и 108.

Конфигурируемые архитектуры для DSP 104, 106 и 108 являются более подходящими для всех типов операций обработки сигналов, чем архитектура для DSP 100, так как они поддерживают все параллельные комбинации, показанные в Таблице 1.

Конфигурируемые и/или конвейерные DSP, описанные выше, могут использоваться для различных применений, включая радиосвязь, вычисление, работу в сети, персональную электронику и так далее. Примерное использование DSP для радиосвязи описано ниже.

Фиг. 9 иллюстрирует блок-схему беспроводного устройства 900 в системе беспроводной связи. Беспроводное устройство 900 может быть сотовым телефоном, микротелефоном, терминалом, мобильной станцией или некоторым другим устройством или конструкцией. Системой беспроводной связи может быть система множественного доступа с кодовым разделением каналов (CDMA), глобальной системой для системы с мобильными объектами (GSM), системой множество входов - множество выходов (MIMO), системой мультиплексирования с ортогональным делением частот (OFDM), системой доступа с мультиплексированием с ортогональным делением частот (OFDMA) и так далее. Беспроводное устройство 900 способно обеспечить двунаправленную связь через тракт приема и тракт передачи.

Для тракта приема сигналы, переданные базовыми станциями в системе, принимаются антенной 912, направляются через антенный переключатель (D) 914 и подают к модулю приемника (RCVR) 916. Модуль 916 приемника обрабатывает (например, фильтрует, усиливает и преобразовывает частоту с понижением частоты) принятый сигнал, оцифровывает обработанный сигнал и выдает выборки данных на DSP 920 для дальнейшей обработки. Для тракта передачи данные, которые должны быть переданы из беспроводного устройства 900, выдаются посредством DSP 920 к модулю передатчика (TMTR) 918. Модуль 918 передатчика обрабатывает (например, фильтрует, усиливает и преобразовывает частоту с повышением частоты) данные и генерирует модулированный сигнал, который направляют через антенный переключатель 914 и передают с помощью антенны 912 базовым станциям.

DSP 920 включает в себя различные модули, такие как, например, файл 930 регистров, блоки 932 УН, АЛУ 934, внутренний контроллер 940 и внутренний блок 942 памяти, которые все подсоединены через внутреннюю шину. Внутренний контроллер 940 выполняет команды, которые выдают команды на блоки 932 УН и АЛУ 934 для выполнения различных вычислений. Например, DSP 920 может выполнять кодирование, перемежение, модуляцию, формирование канала, расширение по спектру, фильтрование и так далее для тракта передачи. DSP 920 может выполнять фильтрование, сжатие, формирование канала, демодулирование, осуществление обращенного перемежения, декодирование и так далее для тракта приема. Эти различные операции известны в технике. Конкретная обработка, которая должна быть выполнена DSP 920, зависит от системы связи. Файл 930 регистров, блоки 932 УН и АЛУ 934 могут быть осуществлены любой из архитектур DSP, показанных на фиг. 2, 3, 4 и 5.

Контроллер 950 управляет работой DSP 920 и других модулей в беспроводном устройстве 900. Другие модули не показаны на фиг. 9, так как они не способствуют пониманию различных вариантов осуществления. Блоки 942 и 952 памяти хранят программные коды и данные, используемые контроллерами 940 и 950 соответственно.

Фиг. 9 иллюстрирует примерную конструкцию беспроводного устройства, в который конфигурируемые и/или конвейерные DSP, описанные выше, могут использоваться. Эти DSP также могут использоваться в других электронных устройствах.

Описанные конфигурируемые и/или конвейерные архитектуры DSP могут быть осуществлены в различных аппаратных модулях. Например, эти архитектуры DSP могут быть осуществлены в интегральной схеме для специального применения (ASIC), устройстве обработки цифрового сигнала (DSPD), программируемом логическом устройстве (PLD), программируемой пользователем матрице логических элементов (FPGA), процессоре, контроллере, микроконтроллере, микропроцессоре и других электронных модулях.

Предыдущее описание раскрытых вариантов осуществления обеспечивается для того, чтобы дать возможность любому специалисту изготовить или использовать настоящее изобретение. Различные модификации этих вариантов осуществления будут очевидны специалистам, и родовые принципы, определенные здесь, могут применяться к другим вариантам осуществления без отрыва от объема или формы изобретения. Таким образом, настоящее изобретение не ограничено вариантами осуществления, показанными выше, но должны предоставить наибольший объем, совместимый с раскрытыми принципами и новыми признаками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНСТРУКЦИЯ И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СКАЛЯРНОГО ПРОИЗВЕДЕНИЯ | 2007 |

|

RU2421796C2 |

| ЦИФРОВОЙ СИГНАЛЬНЫЙ ПРОЦЕССОР И СПОСОБ РАБОТЫ | 2019 |

|

RU2769964C1 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

| Конвейерный умножитель | 2024 |

|

RU2827680C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ УМНОЖЕНИЯ-СЛОЖЕНИЯ С УПАКОВАННЫМИ ДАННЫМИ | 1996 |

|

RU2139564C1 |

| СТЕКОВАЯ ЭВМ С ПРЕФИКСНЫМИ КОМАНДАМИ | 2014 |

|

RU2581548C1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| ВЕКТОРНЫЙ МУЛЬТИФОРМАТНЫЙ УМНОЖИТЕЛЬ | 2018 |

|

RU2689819C1 |

| МАТРИЧНО-ВЕКТОРНЫЙ УМНОЖИТЕЛЬ С НАБОРОМ РЕГИСТРОВ ДЛЯ ХРАНЕНИЯ ВЕКТОРОВ, СОДЕРЖАЩИМ МНОГОПОРТОВУЮ ПАМЯТЬ | 2019 |

|

RU2795887C2 |

Изобретение относится к цифровым сигнальным процессорам с конфигурируемыми блоками умножения-накопления (БУН) и арифметико-логическими устройствами (АЛУ). Техническим результатом является увеличение быстродействия устройства и обеспечение гибкости для одновременного выполнения операций различных типов. Устройство содержит первый БУН, для приема и перемножения первого и второго операндов, сохранения полученного результата в первом промежуточном регистре, суммирования его с третьим операндом, второй БУН, для приема и перемножения четвертого и пятого операндов, сохранения полученного результата во втором промежуточном регистре, суммирования шестого операнда или с сохраненным вторым промежуточным результатом, или с суммой сохраненных первого и второго промежуточных результатов, причем БУНы реагируют на процессорные инструкции для динамической реконфигурации между первой конфигурацией, в которой работают первый и второй БУНы в качестве двух независимых, и второй конфигурацией, в которой работают первый и второй БУНы в качестве соединенных БУНов. 4 н. и 17 з.п. ф-лы, 9 ил., 1 табл.

первый блок умножения-накопления (УН), выполненный с возможностью принимать и перемножать первый и второй операнды из файла регистров и получать первый промежуточный результат, сохранять первый промежуточный результат в первом промежуточном регистре, суммировать сохраненный первый промежуточный результат с третьим операндом и выдавать первый выходной результат к файлу регистров; и

второй блок УН, выполненный с возможностью принимать и перемножать четвертый и пятый операнды из файла регистров, чтобы получить второй промежуточный результат, сохранять второй промежуточный результат во втором промежуточном регистре, суммировать шестой операнд или с сохраненным вторым промежуточным результатом, или с суммой сохраненных первого и второго промежуточных результатов и обеспечивать второй выходной результат в файл регистров,

причем первый блок УН и второй блок УН реагируют на процессорные инструкции для динамической реконфигурации между первой конфигурацией, в которой работают первый блок УН и второй блок УН в качестве двух независимых блоков УН, и второй конфигурацией, в которой работают первый блок УН и второй блок УН в качестве соединенных блоков УН, и

причем упомянутая первая конфигурация или упомянутая вторая конфигурация включает в себя блок УН и арифметико-логическое устройство (АЛУ).

тракт арифметико-логического устройства (АЛУ), выполненный с возможностью принимать и выполнять первую операцию над седьмым операндом или восьмым операндом, чтобы получить третий промежуточный результат, сохранять третий промежуточный результат в третьем регистре, выполнять вторую операцию над третьим промежуточным результатом, седьмым операндом, восьмым операндом или их комбинацией и обеспечивать третий выходной результат.

первый блок УН включает в себя

первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды и обеспечивать первый промежуточный результат, после чего первый регистр способен сохранять первый промежуточный результат, и

первый сумматор, выполненный с возможностью суммировать сохраненный первый промежуточный результат из первого регистра с третьим операндом и обеспечивать первый выходной результат, и

второй блок УН включает в себя

второй умножитель, выполненный с возможностью принимать и перемножать четвертый и пятый операнды и выдавать второй промежуточный результат, после чего второй регистр способен сохранять второй промежуточный результат,

второй сумматор, выполненный с возможностью суммировать сохраненный второй промежуточный результат из второго регистра или с нулем, или с первым промежуточным результатом из первого регистра, и

третий сумматор, выполненный с возможностью суммировать выходной результат второго сумматора с шестым операндом и выдавать второй выходной результат.

блок сдвига, выполненный с возможностью принимать и сдвигать седьмой или восьмой операнд и выдавать третий промежуточный результат, после чего третий регистр способен сохранять третий промежуточный результат, и

АЛУ, выполненное с возможностью выполнять вторую операцию над третьим промежуточным результатом из третьего регистра, седьмым операндом, восьмым операндом или их комбинацией и выдавать третий выходной результат.

первый тракт обработки, соединенный с файлом регистров, причем первый тракт обработки включает в себя

первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды из файла регистров и обеспечивать первый промежуточный результат, и

первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать первый промежуточный результат, третий операнд и, по меньшей мере, один дополнительный операнд, выполнять операции над принятыми операндами и выдавать первый выходной результат; и

второй тракт обработки, соединенный с файлом регистров, причем второй тракт обработки включает в себя

второй умножитель, выполненный с возможностью принимать и перемножать четвертый и пятый операнды из файла регистров и выдавать второй промежуточный результат,

первый сумматор, выполненный с возможностью суммировать второй промежуточный результат или с нулем или с первым промежуточным результатом из первого тракта обработки, и

второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом из файла регистров и выдавать второй выходной результат,

при этом первый тракт обработки выборочно конфигурируется для обеспечения первой возможности использовать тракт обработки умножения-накопления и второй возможности использовать тракт обработки АЛУ.

тракт АЛУ, включающий в себя

блок сдвига, выполненный с возможностью принимать и сдвигать седьмой операнд или восьмой операнд и выдавать третий промежуточный результат, и

второе АЛУ, выполненное с возможностью выполнять операции над третьим промежуточным результатом, седьмым операндом, восьмым операндом или их комбинацией и выдавать третий выходной результат.

файл регистров, выполненный с возможностью выдавать с первого по восьмой операнды для первого и второго блоков УН и тракта АЛУ и сохранять с первого по третий выходные результаты от первого и второго блоков УН и тракта АЛУ.

первый регистр, выполненный с возможностью сохранять первый промежуточный результат и выдавать сохраненный первый промежуточный результат к первому АЛУ и первому сумматору; и

второй регистр, выполненный с возможностью сохранять второй промежуточный результат и выдавать сохраненный второй промежуточный результат к первому сумматору.

первый регистр, выполненный с возможностью сохранять первый промежуточный результат и выдавать сохраненный первый промежуточный результат к первому АЛУ и первому сумматору;

второй регистр, выполненный с возможностью сохранять второй промежуточный результат и выдавать сохраненный второй промежуточный результат к первому сумматору; и третий регистр, выполненный с возможностью сохранять третий промежуточный результат и выдавать сохраненный третий промежуточный результат ко второму АЛУ.

файл регистров,

первый тракт обработки, соединенный с файлом регистров, при этом первый тракт обработки включает в себя

первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды из файла регистров и выдавать первый промежуточный результат,

первый промежуточный регистр, выполненный с возможностью сохранять первый промежуточный результат и выдавать сохраненный первый промежуточный результат, и

первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать и выполнять операции над сохраненным первым промежуточным результатом, третьим операндом из файла регистров, по меньшей мере, одним другим операндом или их комбинацией и выдавать первый выходной результат; и

второй тракт обработки, соединенный с файлом регистров, при этом второй тракт обработки включает в себя

второй умножитель, выполненный с возможностью принимать и умножать четвертый и пятый операнды из файла регистров и выдавать второй промежуточный результат,

второй промежуточный регистр, выполненный с возможностью сохранять второй промежуточный результат и выдавать сохраненный второй промежуточный результат,

первый сумматор, выполненный с возможностью суммировать сохраненный второй промежуточный результат или с нулем, или сохраненным первым промежуточным результатом из первого тракта обработки, и

второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом из файла регистров и выдавать второй выходной результат,

причем первый тракт обработки является выборочно конфигурируемым для обеспечения тракта обработки с блоком УН и тракта обработки с АЛУ.

третий тракт обработки, соединенный с файлом регистров, причем третий тракт обработки включает в себя

первый блок сдвига, выполненный с возможностью принимать и сдвигать седьмой операнд или восьмой операнд из файла регистров и выдавать третий промежуточный результат,

третий промежуточный регистр, выполненный с возможностью сохранять третий промежуточный результат и выдавать сохраненный третий промежуточный результат, и

второе АЛУ, выполненное с возможностью выполнять операции над сохраненным третьим промежуточным результатом, седьмым операндом, восьмым операндом или их комбинацией и выдавать третий выходной результат,

при этом третий тракт обработки является конфигурируемым в качестве тракта обработки АЛУ, работающего параллельно с первым и вторым трактами обработки.

второй блок сдвига, выполненный с возможностью принимать девятый и десятый операнды и выдавать четвертый выходной результат, и мультиплексор, выполненный с возможностью принимать третий и четвертый выходные результаты и выдавать или третий, или четвертый выходной результат.

первый тракт обработки дополнительно включает в себя первый блок сдвига, выполненный с возможностью принимать сохраненный первый промежуточный результат и выдавать первый сдвинутый результат на первый АЛУ и первый сумматор, и

второй тракт обработки дополнительно включает в себя второй блок сдвига, выполненный с возможностью принимать сохраненный второй промежуточный результат и выдавать второй сдвинутый результат к первому сумматору.

файл регистров для хранения и передачи множества операндов, принятых от антенны,

первый тракт обработки, включающий в себя

первый умножитель, выполненный с возможностью принимать и перемножать первый и второй операнды из файла регистров и выдавать первый промежуточный результат, и

первое арифметико-логическое устройство (АЛУ), выполненное с возможностью принимать первый промежуточный результат, третий операнд из файла регистров и, по меньшей мере, один дополнительный операнд, выполнять операции над принятыми операндами и выдавать первый выходной результат;

второй тракт обработки, включающий в себя

второй умножитель, выполненный с возможностью принимать и умножать четвертый и пятый операнды из файла регистров и выдавать второй промежуточный результат,

первый сумматор, выполненный с возможностью суммировать второй промежуточный результат или с нулем, или первым промежуточным результатом из первого тракта обработки, и

второй сумматор, выполненный с возможностью суммировать выходной результат первого сумматора с шестым операндом из файла регистров и выдавать второй выходной результат;

третий тракт обработки, включающий в себя

блок сдвига, выполненный с возможностью принимать и сдвигать седьмой операнд или восьмой операнд из файла регистров и выдавать третий промежуточный результат, и

второе АЛУ, выполненное с возможностью выполнять операции над третьим промежуточным результатом, седьмым операндом, восьмым операндом или их комбинацией и выдавать третий выходной результат; и

причем файл регистров выполнен с возможностью выдавать с первого по восьмой операнды для первого, второго и третьего трактов обработки и сохранять в нем с первого по третий выходные результаты, и

при этом первый тракт обработки является динамически реконфигурируемым между конфигурацией тракта обработки с блоком умножения-накопления и конфигурацией тракта обработки с АЛУ.

| US 6530014 В2, 04.03.2003 | |||

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ УМНОЖЕНИЯ-СЛОЖЕНИЯ С УПАКОВАННЫМИ ДАННЫМИ | 1996 |

|

RU2139564C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ПОДАЧИ БУРОВОГО СТАВА | 0 |

|

SU332215A1 |

Авторы

Даты

2008-12-27—Публикация

2005-03-02—Подача