Изобретение относится к области компьютерных устройств, основанных на специфических вычислительных моделях, может быть использовано при проектировании нейроморфных процессорных устройств, а также может быть использовано в центральных и графических процессорных устройствах и иных областях. Конвейерный умножитель может являться частью арифметического сопроцессора процессорного ядра нейроморфной СБИС (сверхбольшой интегральной микросхемы) и предназначен для проведения операции умножения над двумя бинарными операндами или операции комбинированного умножения-сложения (МАС-операции) над тремя операндами. Два основных операнда являются целыми числами в диапазоне от –32768 до 32767, длинной 16 бит, представленные в дополнительном коде. Третьим дополнительным операндом для MAC-операции и операндом результата выполнения операции являются 32-битное целое число, представленное в дополнительном коде.

Известен конвейерный арифметический умножитель (см. патент РФ №2546072, опубл. 2015 г., G06F 7/527). Устройство содержит два блока, которые имеют ячеистую структуру и разбиты на колонки и ряды, элемент памяти, элементы управления записью информации и чтением информации из памяти. Первый блок является входным с числом колонок, равным сумме разрядов множимого и множителя и с числом рядов на один больше числа разрядов множимого. У второго блока число колонок и число рядов равно числу разрядов соответственно множимого и множителя. При этом используются ячейки четырех типов (ИЛИ, И, полусумматор, сумматор) с регистрами.

Основным недостатком данного решения является отсутствие имплементации операции сложения для реализации операции умножения-сложения в конвейер умножителя. Также недостатком является систолическая архитектура умножителя, являющаяся более медленной, по сравнению с архитектурой на основе алгоритма Бута.

Известно устройство выполнения операций умножения-сложения (см. US 20190012143, опубл.2019 г), включающее умножитель, сумматор, первый регистр результатов и второй регистр результатов, соединенные с выходами умножителя и сумматора, соответственно. Включает четыре блока выбора. Первый блок выбора, выполненный с возможностью выборочной подачи на умножитель, и в ответ на первый управляющий сигнал первого значения из первого множества значений. Второй блок выбора, выполненный с возможностью выборочной подачи на умножитель и в ответ на второй управляющий сигнал второго значения из второго множества значений. Третий блок выбора, сконфигурированный для выборочной подачи в сумматор и в ответ на третий управляющий сигнал третьего значения из третьего множества значений. Четвертый блок выбора, сконфигурированный для выборочной подачи в сумматор и в ответ на четвертый управляющий сигнал четвертого значения из четвертого множества значений.

Основным недостатком данного решения является последовательная реализация MAC-операции, то есть умножение двух операндов, и последующее суммирование результата умножения с третьим операндом. Подобное решение приводит к разнице в скорости выполнения операции умножения и умножения-сложения, что усложняет работу контроллера очереди операций процессора, а также уменьшает общую скорость выполнения операции умножения-сложения.

Наиболее близким по технической сущности заявляемому устройству является устройство умножения-сложения и способ его работы (патент США №7730118, опубл.2006 г., МПК G06F 7/38), содержащее арифметический блок для выборочной реализации одной из команд умножения или умножения-сложения, включающий умножитель, конвейер свертки, регистр результата и схему аккумулятора. Умножитель выполнен с возможностью приема первого и второго операндов и способен генерировать члены умножения. Схема сложения для получения членов умножения от умножителя и возможность их объединения для получения результата умножения. Регистр результата для получения результата умножения от сумматора. Схема мультиплексора выбора операции подключена для приема значения, хранящегося в регистре результатов, и сигнала управления накоплением, который определяет, выполняет ли арифметический блок умножение, либо MAC-операцию. В известном устройстве использован генератор промежуточных значений на основе алгоритма Бута, шестистадийный конвейер свертки типа «древо Уоллеса» для

17 промежуточных значений и мультиплексор выбора операции умножения/комбинированного умножения-сложения.

Недостатком прототипа является применение стандартного алгоритма Бута, порождающего большее количество промежуточных значений, что увеличивает размеры конвейера. Для актуальных задач нейроморфных вычислений вариант вычислителя с разрядностью 32 бит не позволяет реализовать более компактное, производительное и энергоэффективное решение.

Задачами изобретения являются увеличение быстродействия, уменьшение площади устройства и энергопотребления при исполнении операции умножения или комбинированного умножения-сложения.

Техническим результатом является уменьшение количества генерируемых промежуточных значений, благодаря чему увеличивается быстродействие, уменьшается площадь и энергопотребление.

Технический результат достигается тем, что конвейерный умножитель содержит генератор промежуточных значений, выполненный с возможностью приема первого и второго операндов, а также генерации промежуточных результатов умножения, выходы которого соединены со входами конвейера свертки промежуточных значений, вход которого связан с выходом мультиплексора выбора операции умножения или комбинированного умножения-сложения с третьим операндом, отличающийся тем, что конвейерный умножитель выполнен с возможностью обработки входных операндов разрядностью 16 бит, получения результата выполнения операции разрядностью 32 бита, работы каждого следующего блока по инверсному, относительно предыдущего блока, фронту синхросигнала; генератор промежуточных значений выполнен с возможностью реализации модифицированного алгоритма Бута Radix-8, а также ускоренной генерации промежуточных значений с неединичными коэффициентами за полтакта и параллельной генерации всех вариантов промежуточных значений; конвейер свёртки выполнен трёхслойным по типу «древо Уоллеса» с возможностью сложения шести промежуточных значений.

Блоки генератора промежуточных значений выполнены с возможностью генерации вариантов промежуточных значений из операнда-множимого.

Мультиплексор генератора промежуточных значений состоит из шести параллельных мультиплексоров.

Конвейер свертки выполнен с возможностью проведения трёх этапов сложения, каждый из которых осуществляется отдельной группой сумматоров.

Мультиплексор выбора операции выполнен с возможностью записи на основе значения флага выбора операции значения 32-битного операнда в случае исполнения операции комбинированного умножения-сложения либо записи логического ноля в случае исполнения операции умножения в 32-битный регистр при параллельной генерации промежуточных значений и их загрузке в конвейер свертки промежуточных значений посредством коммутации через мультиплексор, передающий полученное значение в конвейер свертки промежуточных значений.

Признак «разрядность входных операндов умножителя 16 бит» влияет на технический результат следующим образом: из-за более короткого операнда генерируется меньше промежуточных значений, что уменьшает количество сумматоров в первом слое конвейера свертки промежуточных значений, что в свою очередь приводит к уменьшению количества слоев в конвейере свертки промежуточных значений, что приводит к увеличению быстродействия, уменьшению площади и энергопотребления устройства.

Разрядность результата выполнения операции 32 бита влияет на технический результат, так как уменьшение разрядности выходного операнда уменьшает разрядность сумматоров, регистров, мультиплексоров и прочих элементов устройства, что в свою очередь приводит к снижению энергопотребления и уменьшению площади устройства.

Выполнение блоков по синхросигналу таким образом, что каждый следующий блок работает по инверсному фронту синхросигнала, относительно предыдущего, приводит к увеличению частоты работы блоков, за счет этого достигается увеличение быстродействия устройства.

Параллельная генерация промежуточных значений за пол такта позволяет конвейеризовать обработку входных операндов, что приводит к увеличению быстродействия устройства.

Выполнение трехслойного конвейера, складывающего 6 промежуточных значений, позволяет оптимизировать структуру конвейера свертки промежуточных значений, что приводит к увеличению быстродействия, уменьшению площади и энергопотребления устройства.

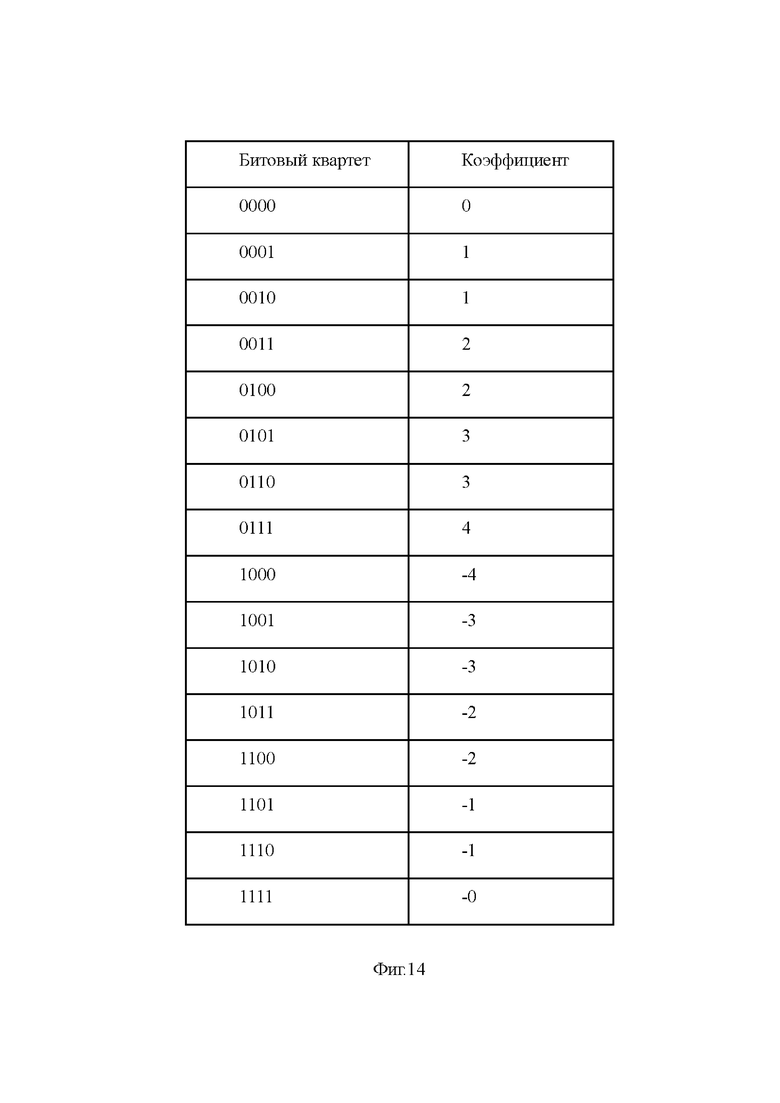

Уменьшение количества генерируемых промежуточных значений достигается за счет генерации промежуточных значений на основе сразу нескольких элементов операнда-множителя. В случае вариации Radix-8 множитель разбивается на битовые «квартеты», на основе которых определяются коэффициенты, на которые умножается множитель для получения набора промежуточных значений.

Применение алгоритма Radix-8 увеличивает размер применяемой избыточной кодировки множителя, что приводит к уменьшению количества промежуточных значений. В свою очередь, уменьшение разрядности входных операндов с 32 (см. прототип) до 16 бит также приводит к уменьшению количества промежуточных значений. Кумулятивный эффект применения данных решений позволяет уменьшить ширину и глубину конвейера свертки, так как конвейер складывает только 6 промежуточных значений, вместо 17 у прототипа, что в свою очередь приводит к оптимизации заявленных характеристик.

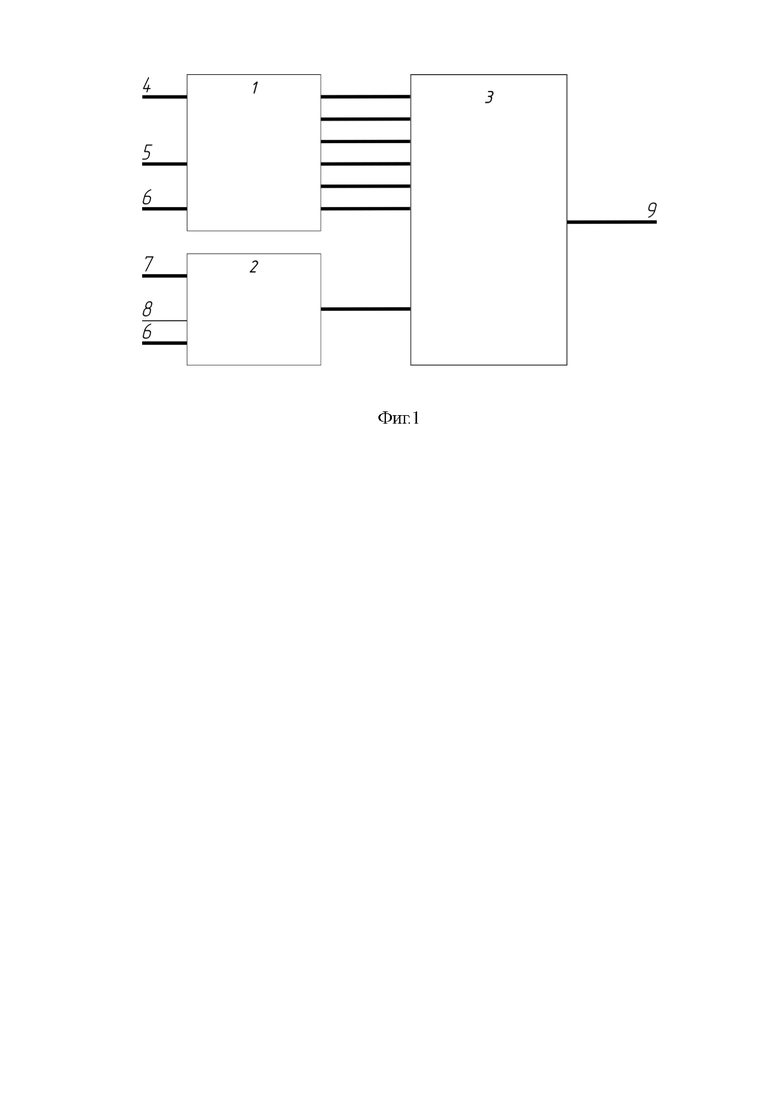

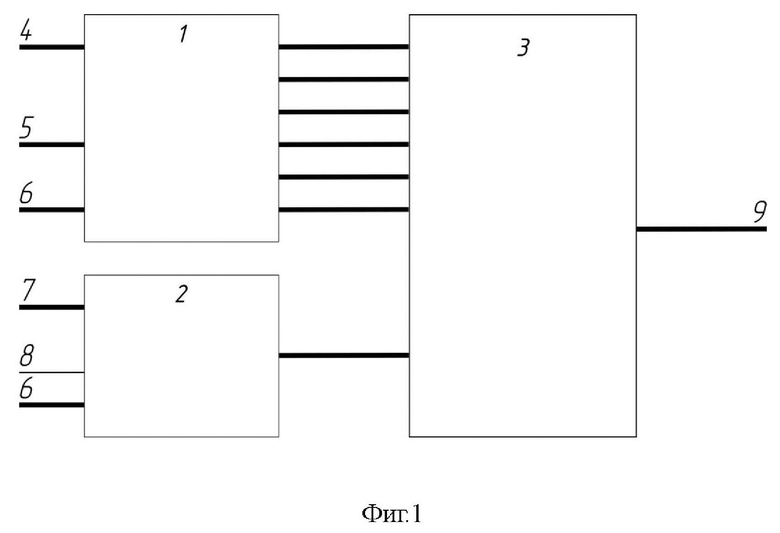

На фиг. 1 представлена принципиальная схема устройства, где блок 1 – генератор промежуточных значений, блок 2 – мультиплексор выбора операции, блок 3 – конвейер свертки промежуточных значений, вход 4 – 16-ти битный операнд-множимое, вход 5 – 16-ти битный операнд-множитель, вход 6 – логический 0, вход 7 – 32-битный операнд для МАС-операции, вход 8 – флаг выбора операции МАС-операции, выход 9 – результат работы устройства.

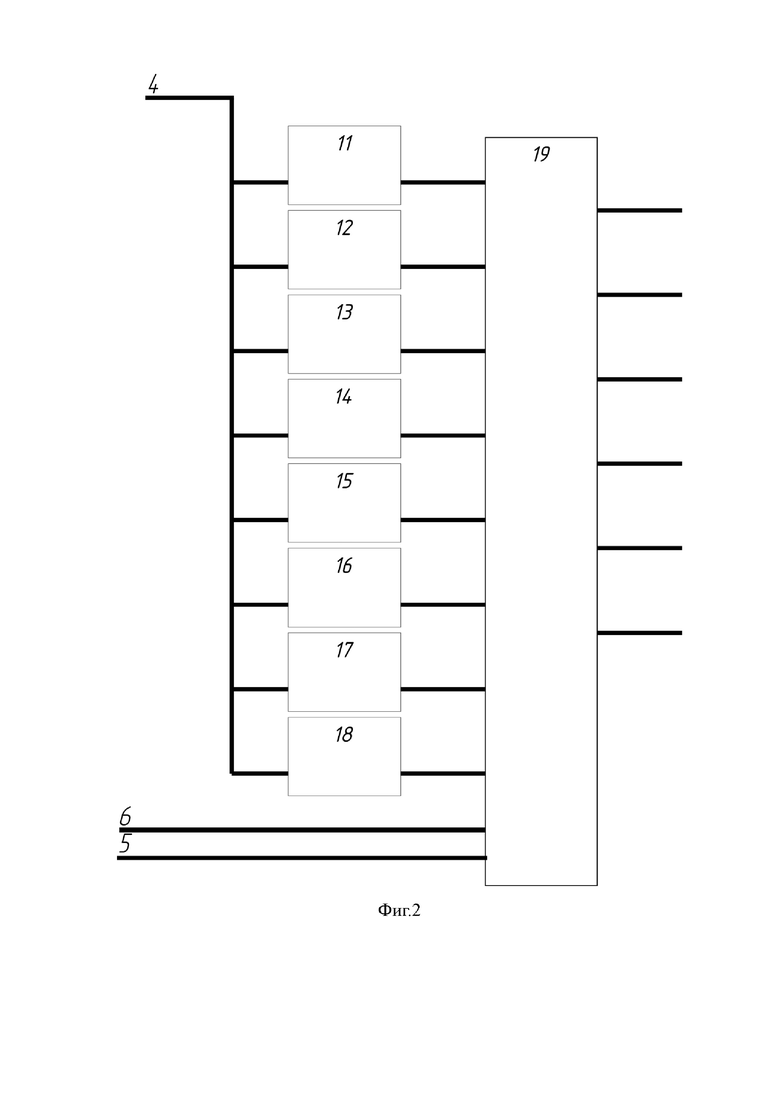

На фиг. 2 представлен генератор промежуточных значений, где 11 – блок генератора промежуточных значений с коэффициентом 4, 12 – блок генератора промежуточных значений с коэффициентом 3, 13 – блок генератора промежуточных значений с коэффициентом 2, 14 – блок генератора промежуточных значений с коэффициентом 1, 15 – блок генератора промежуточных значений с коэффициентом минус 1, 16 – блок генератора промежуточных значений с коэффициентом минус 2, 17 – блок генератора промежуточных значений с коэффициентом минус 3, 18 – блок генератора промежуточных значений с коэффициентом минус 4, блок 19 – мультиплексор генератора промежуточных значений.

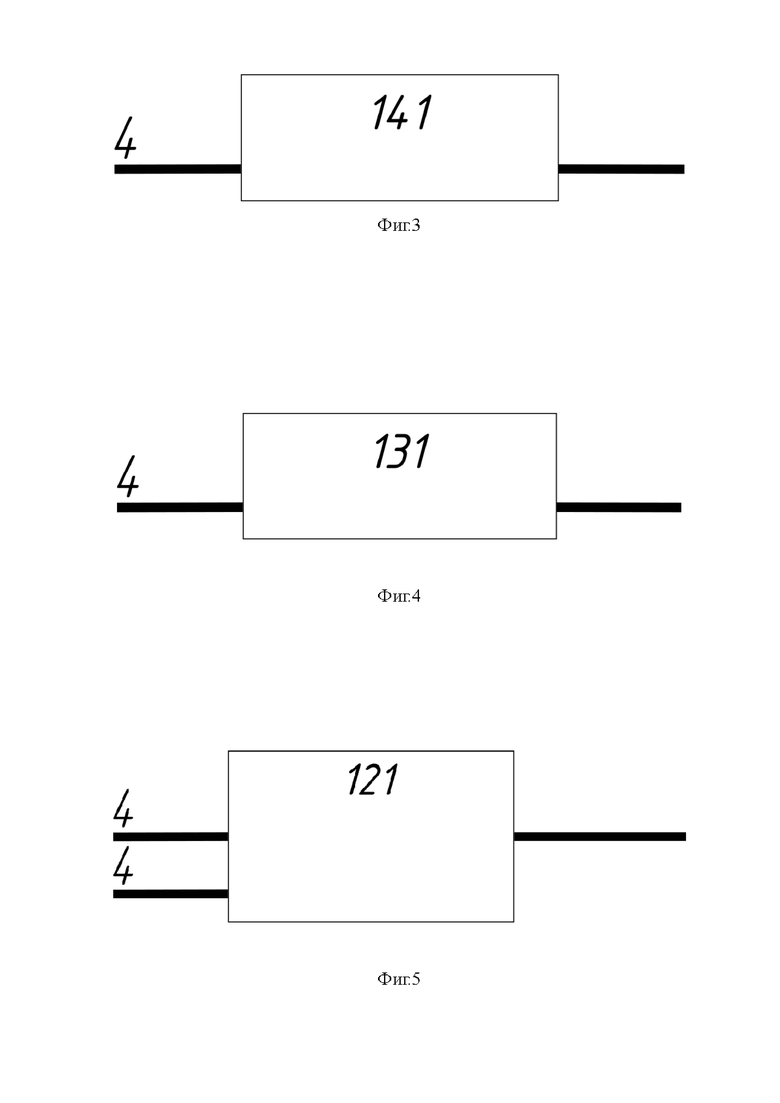

На фиг. 3 представлен блок генератора промежуточных значений с коэффициентом 1, где блок 141 – 18-битный регистр.

На фиг. 4 представлен блок генератора промежуточных значений с коэффициентом 2, где блок 131 – 18-битный регистр.

На фиг. 5 представлен блок генератора промежуточных значений с коэффициентом 3, где блок 121 – 18-битный полный двоичный сумматор.

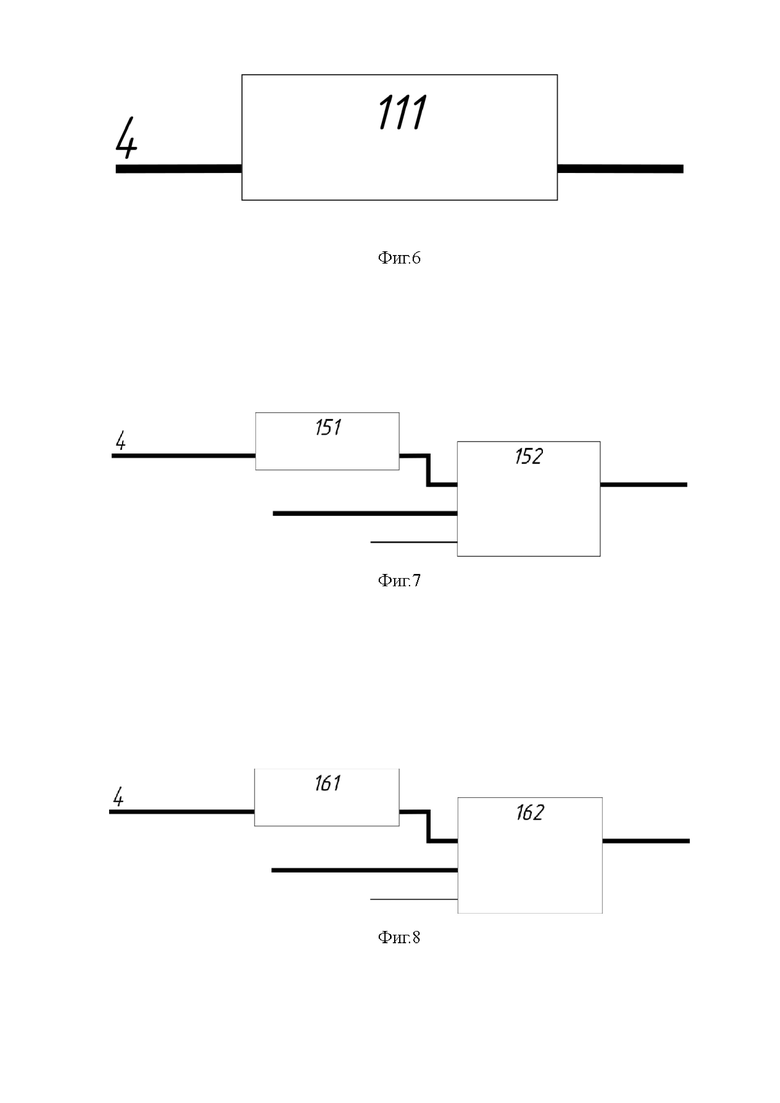

На фиг. 6 представлен блок генератора промежуточных значений с коэффициентом 4, где блок 111 –18-битный регистр.

На фиг. 7 представлен блок генератора промежуточных значений с коэффициентом минус 1, где блок 151 – 18-битный логический инвертор, блок 152 – 18-битный полный двоичный сумматор.

На фиг. 8 представлен блок генератора промежуточных значений с коэффициентом минус 2, где блок 161 – 18-битный логический инвертор, блок 162 – 18-битный полный двоичный сумматор.

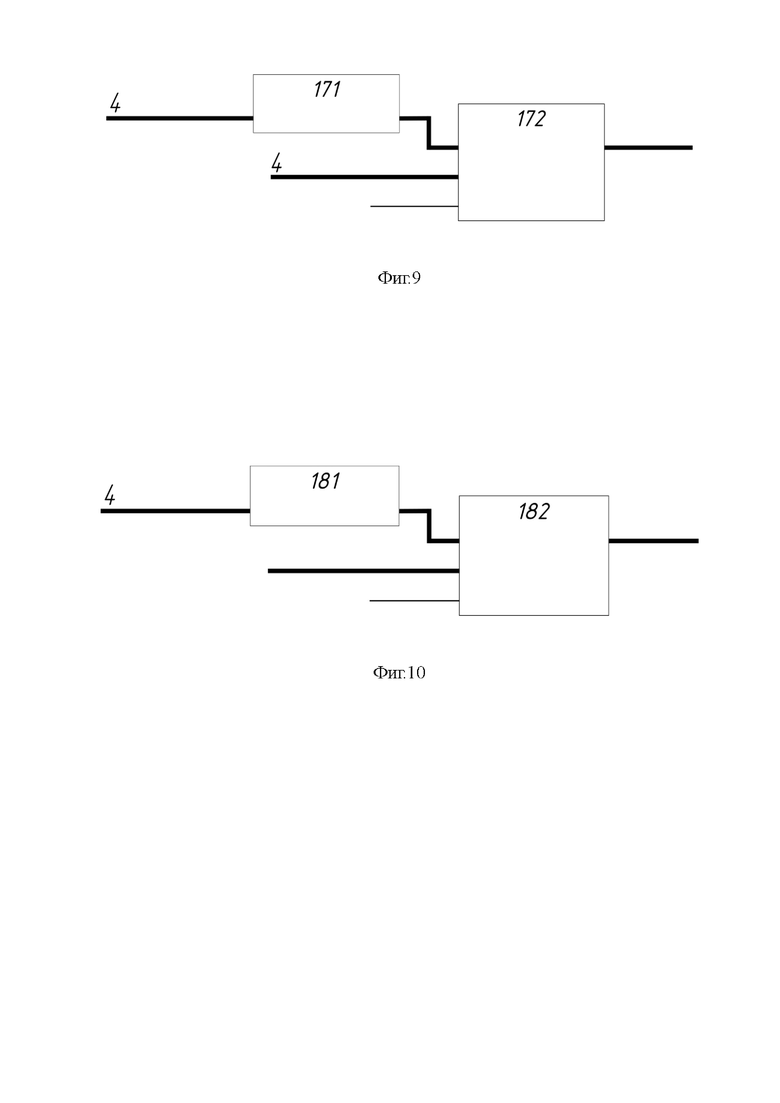

На фиг. 9 представлен блок генератора промежуточных значений с коэффициентом минус 3, где блок 171 – 18-битный логический инвертор, блок 172 – 18-битный полный двоичный сумматор.

На фиг. 10 представлен блок генератора промежуточных значений с коэффициентом минус 4, где блок 181 – 18-битный логический инвертор, блок 182 – 18-битный полный двоичный сумматор.

На фиг. 11 представлена схема мультиплексора генератора промежуточных значений, где блоки 191, 192, 193, 194, 195, 196 – мультиплексоры.

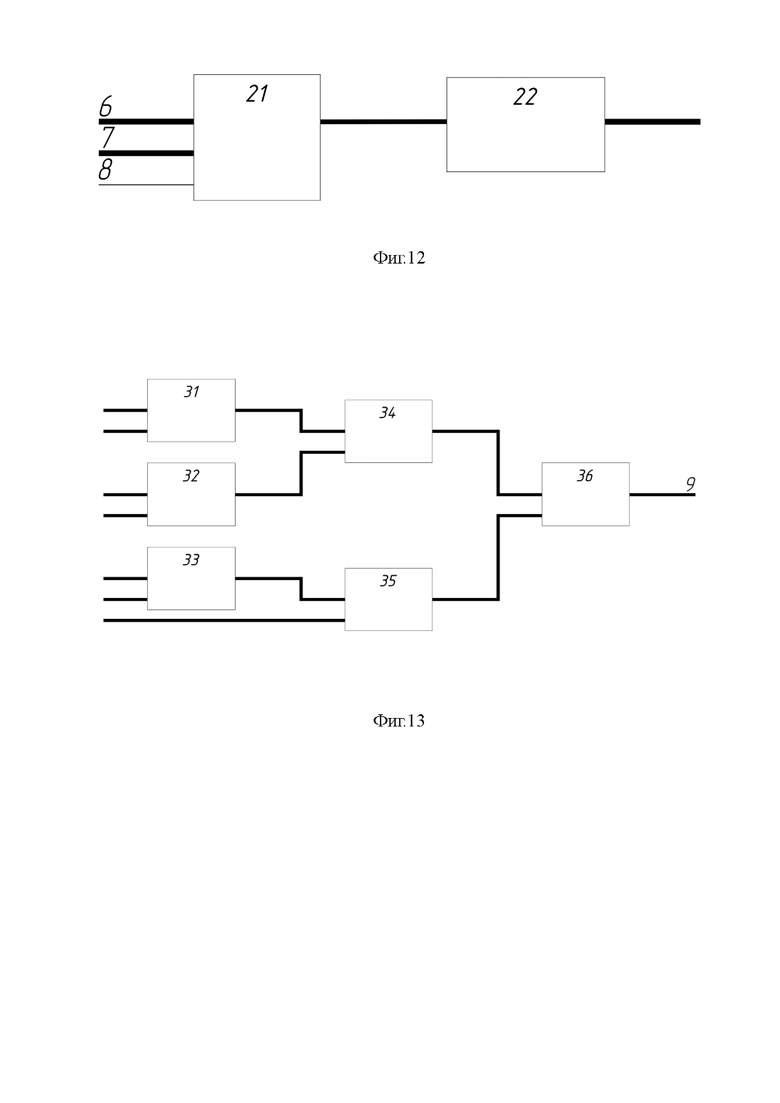

На фиг. 12 представлен мультиплексор выбора операции, где блок 21 – мультиплексор, блок 22 – 32-битный регистр.

На фиг. 13 представлен конвейер свертки промежуточных значений, где блоки 31, 32, 33, 34, 35, 36 – 32-битные полные двоичные сумматоры.

На фиг.14, в таблице приведены вариации битовых квартетов и соответствующие им коэффициенты.

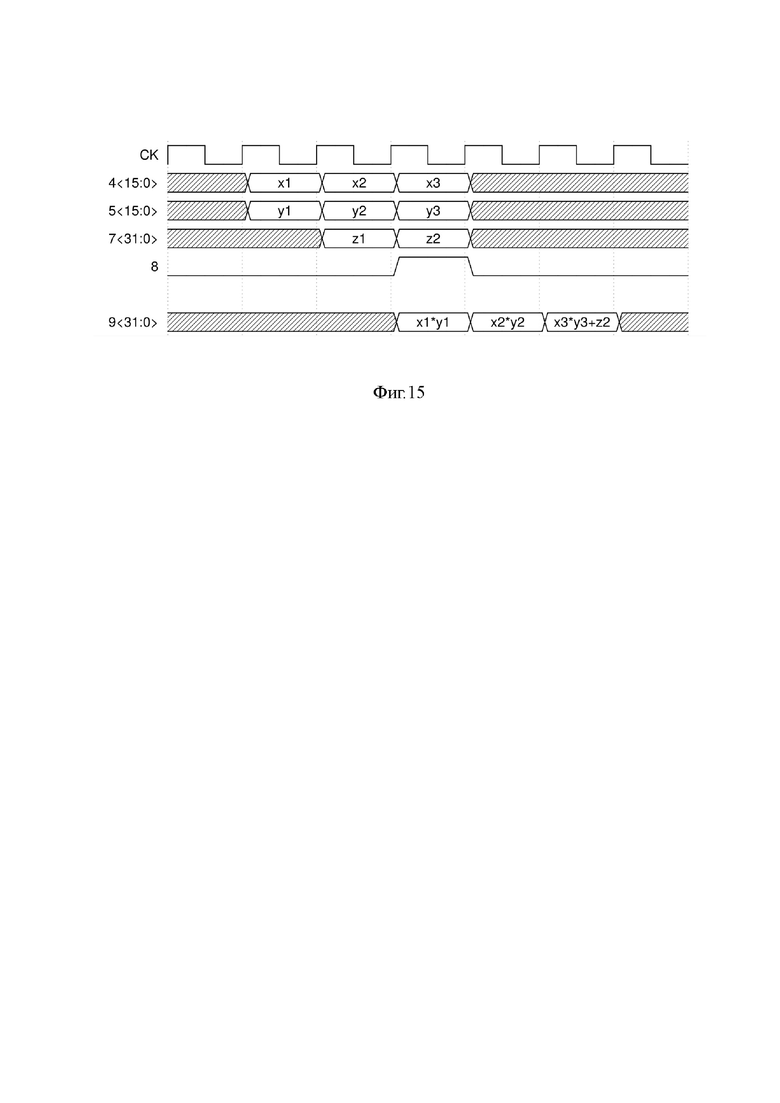

На фиг. 15 на временной диаграмме представлен общий принцип работы изобретения.

Устройство состоит из трех функциональный блоков: генератора промежуточных значений (блок 1, см.фиг.2), мультиплексора выбора операции (блок 2, см.фиг.12) и блока свертки (блок 3, см.фиг.13).

Генерация вариантов промежуточных значений из операнда-множимого (вход 4) происходит в блоках генератора промежуточных значений (блоки 11-18, см. фиг. 3-10).

Блок генератора промежуточных значений с коэффициентом «4» (блок 11), записывает значение операнда-множимого (вход 4) в 18-битный регистр, со сдвигом влево на 2, тем самым генерируя и сохраняя 18-битное значение (блок 111), которое в дальнейшем передается на вход блока 19 (см. фиг.6).

Блок генератора промежуточных значений с коэффициентом «3» (блок 12), подает значение операнда-множимого (вход 4), со сдвигом влево на 1 и расширением старшего бита на 1, и значение операнда-множимого (вход 4) с расширением старшего бита на 2, в 18-битный сумматор (121), где путем сложения создается и сохраняется 18-битное значение, которое в дальнейшем передается на вход блока 19 (см. фиг.5).

Блок генератора промежуточных значений с коэффициентом «2» (блок 13), записывает значение операнда-множимого (вход 4) в 18-битный регистр со сдвигом влево на 1 и расширением старшего бита на 1, тем самым генерируя и сохраняя 18-битное значение (блок 131), которое в дальнейшем передается на вход блока 19 (см.фиг.4).

Блок генератора промежуточных значений с коэффициентом «1» (блок 14), записывает значение операнда-множимого (вход 4) в 18-битный регистр, с расширением старшего бита на 2, тем самым генерируя и сохраняя 18-битное значение (блок 141), которое в дальнейшем передается на вход блока 19 (см.фиг.3).

Блок генератора промежуточных значений с коэффициентом «минус 1» (блок 15), подает значение операнда-множимого (вход 4) с расширением старшего бита на 2, в 18-битный инвертор (блок 151), получая значение равное отрицательному множимому минус один, затем подавая его в сумматор (блок 152), где к нему прибавляется 1, получая и сохраняя 18-битное значение равное отрицательному множимому, которое в дальнейшем передается на вход блока 19 (см.фиг.7).

Блок генератора промежуточных значений с коэффициентом «минус 2» (блок 16), подает значение операнда-множимого (вход 4), со сдвигом влево на 1 и расширением старшего бита на 1, в 18-битный инвертор (блок 161), получая значение равное удвоенному отрицательному множимому минус один, затем подавая его в сумматор (блок 162), где к нему прибавляется 1, получая и сохраняя значение удвоенного отрицательного множимого, которое в дальнейшем передается на вход блока 19 (см.фиг.8).

Блок генератора промежуточных значений с коэффициентом «минус 3» (блок 17), подает значение операнда-множимого (вход 4) со сдвигом влево на 2, в 18-битный инвертор (блок 171), получая значение учетверенного отрицательного множимого минус один, затем подавая его в сумматор (блок 182), где к нему прибавляется значение операнда-множимого (вход 4) с расширением старшего бита на 2, и 1, получая и сохраняя значение отрицательного утроенного множимого, которое в дальнейшем передается на вход блока 19 (см.фиг.9).

Блок генератора промежуточных значений с коэффициентом «минус 4» (блок 18), подает значение операнда-множимого (вход 4), со сдвигом влево на 2, в 18-битный инвертор (блок 181), получая значение учетверенного отрицательного множимого минус один, затем подавая его в сумматор (блок 182), где к нему прибавляется 1, получая и сохраняя значение учетверенного отрицательного множимого, которое в дальнейшем передается на вход блока 19 (см.фиг.10).

Мультиплексор генератора промежуточных значений (блок 19, см.фиг.11) загружает промежуточные значения полученные из блоков 11-18 и линии логического 0 (вход 6), которая равна результату умножения множимого на нулевой коэффициент, соответствующие квартетам (см. фиг.14), полученным из операнда-множителя (вход 5) в конвейер свертки промежуточных значений (блок 3). Мультиплексор генератора промежуточных значений состоит из 6 параллельных мультиплексоров (блоки 191-196). При передаче промежуточного значения в древо свертки мультиплексоры нормализуют их до 32-битной разрядности. Так мультиплексор (блок 191) расширяет старший бит передаваемого промежуточного значения на 14 бит, мультиплексор (блок 192) сдвигает значение влево на 3 и расширяет старший бит передаваемого промежуточного значения на 11 бит, мультиплексор (блок 193) сдвигает значение влево на 6 расширяет и старший бит передаваемого промежуточного значения на 8 бит, мультиплексор (блок 194) сдвигает значение влево на 9 и расширяет старший бит передаваемого промежуточного значения на 5 бит, мультиплексор (блок 195) сдвигает значение влево на 12 и расширяет старший бит передаваемого промежуточного значения на 2 бита, мультиплексор (блок 196) сдвигает значение влево на 15 и отбрасывает старший бит промежуточного значения.

Параллельно генерации промежуточных значений (блок 2) и их загрузке в конвейер свертки промежуточных значений (блок 3), мультиплексор выбора операции (блок 2), на основе значения флага выбора операции (вход 8), посредством коммутации через мультиплексор (блок 21), записывает либо значение 32-битного операнда (вход 7) в случае исполнения операции комбинированного умножения-сложения, либо логический 0 (вход 6) в случае исполнения операции умножения в 32-битный регистр (блок 22), который в дальнейшем передает значение в конвейер свертки промежуточных значений (блок 3).

Конвейер свертки промежуточных значений (блок 3) является трехслойным конвейером типа «древо Уолеса» (см.фиг. 13, где блоки 31-36 это 32-битные полные двоичные сумматоры), в котором промежуточные значения попарно складываются для получения результата, который затем передается на выход 9.

Выбор древовидной структуры блока свертки связан с наилучшим быстродействием данного типа структуры по сравнению с аналогами и возможностью потоковой обработки данных.

Для увеличения скорости работы устройства, работа стадий была оптимизирована относительно синхросигнала: каждая следующая стадия умножителя работает по инверсному фронту синхросигнала, относительно предыдущей. Таким образом была достигнута скорость выполнения операции, равная двум тактам. Общий принцип работы изобретения представлен на временной диаграмме на фиг.15.

В начале работы на входы генератора промежуточных значений (блок 1) поступают два 16-битных операнда — множимое (вход 4) и множитель (вход 5). На основе операнда-множимого генерируются все варианты промежуточных значений, применяемые в алгоритме, с коэффициентами от 4 до минус 4 (блоки 11-18). Параллельно, на основе операнда-множителя генерируются битовые квартеты, на основе которых в конвейер свертки промежуточных значений (блок 3) поступают промежуточные значения, получаемые путем выбора в соответствии со значением битовых квартетов и нормализации до 32-битной ширины в мультиплексорах (блоки 191-196) согласно порядковому номеру квартета. Затем, в конвейере свертки промежуточных значений (блок 3) начинается параллельное попарное арифметическое суммирование промежуточных значений. После поступления группы промежуточных значений в конвейер свертки промежуточных значений генератор промежуточных значений (блок 1) может начать генерацию новых промежуточных значений из новой пары операндов (вход 4 и вход 5). Параллельно первому этапу свертки, через мультиплексор выбора операции (блок 2) в конвейер свертки промежуточных значений может быть добавлен третий 32-битный операнд (вход 7) в случае исполнения операции комбинированного умножения-сложения, в ином случае данный операнд принимается равным нулю (вход 6), и исполняется операция умножения, управление выбором операции осуществляются флагом выбора операции (вход 8). Вне зависимости от выполняемой операции, конвейер свертки проводит три этапа сложения, каждый из которых обрабатываться отдельной группой сумматоров (блоки 31-36). После третьего этапа свертки результат умножения или комбинированного умножения-сложения передается на выход устройства 9.

Пример выполнения операции умножения.

Пусть операнд-множимое (вход 4) равен 0000000011111010 (далее – А), операнд-множитель (вход 5) равен 0000110010100010 (далее – В) и флаг выбора операции (вход 8) равен 0. В таком случае значение операнда MAC-операции (вход 7) не рассматривается, так как устройство исполняет операцию умножения, и следовательно, в регистр мультиплексора выбора операции (блок 22) записывается опорный логический 0 (вход 6).

По переднему фронту синхросигнала (далее – CK) в генераторе промежуточных значений (блок 1) блоки генерации промежуточных значений вычисляют из А промежуточные 18-битные значения. Так, блок 11 генерирует значение 4*А равное 000000001111101000, блок 12 генерирует значение 3*А равное 000000001011101110, блок 13 генерирует значение 2*А равное 000000000111110100, блок 14 генерирует значение А равное 000000000011111010, блок 15 генерирует значение минус А равное 111111111100000110, блок 16 генерирует значение минус 2*А равное 111111111000001100, блок 17 генерирует значение минус 3*А равное 111111110100010010, блок 18 генерирует значение минус 4*А, равное 111111110000011000. Промежуточное значение коэффициента 0 не генерируется, а мультиплицируется из опорного 0 (вход 6).

Параллельно этому, мультиплексор генератора промежуточных значений (блок 19) производит коммутацию конвейера свертки промежуточных операций с блоками генерации в соответствии с В (вход 5). Для этого, В (вход 5) разбивается на 6 битовых групп со взаимным перекрытием на 1 бит, и поступают на управляющие входы мультиплексоров генератора промежуточных значений (блоки 191-196), причем, на управляющем входе мультиплексора (блок 191) битовая группа смещается влево на 1, а на управляющем входе мультиплексора (блок 196) расширяется знаковый бит, тем самым получая следующий набор квартетов входа: управляющий вход блока 191 = 0100, управляющий вход блока 192 = 1000, управляющий вход блока 193 = 0101, управляющий вход блока 194 = 1100, управляющий вход блока 195 = 0001, управляющий вход блока 196 = 0000. Каждому коэффициенту промежуточных значений соответствует один или более вариантов квартетов бинарных чисел (см. фиг.14). Так же, мультиплексоры генератора промежуточных значений (блоки 191-196) приводят промежуточные значения к 32-битному виду, за счет смещения влево значения на номер квартета умноженного на 3, и заполнением оставшихся старших битов посредством расширения знакового бита, или наоборот, отбрасыванием старшего бита промежуточного значения в случае 5 квартета. Таким образом, мультиплексор генератора промежуточных значений передает в конвейер свертки промежуточных значений (блок 3) следующий набор пар промежуточных значений в сумматоры первого слоя: сумматор блок 31 00000000000000000000000111110100 и 11111111111111111110000011000000, сумматор блок 32 00000000000000001011101110000000 и 11111111111111000001100000000000, сумматор блок 33 00000000000011111010000000000000 и 00000000000000000000000000000000.

После, по заднему фронту синхросигнала CK первый слой сумматоров (блоки 31-33) в конвейере свертки промежуточных значений начинает попарно складывать значения, переданные из генератора промежуточные значения (блок 1). Таким образом, на выходе первого слоя формируется 3 промежуточных 32-битных значения, которые передаются в сумматоры второго слоя: сумматор блок 34 11111111111111111110001010110100 и 11111111111111001101001110000000, сумматор блок 35 00000000000011111010000000000000.

После, по следующему переднему фронту синхросигнала CK второй слой сумматоров (блоки 34-35) в конвейере свертки промежуточных значений начинает попарно складывать переданные из предыдущего слоя промежуточные значения. Так как исполняется операция умножения, на вход сумматора блок 35 из мультиплексора выбора операции (блок 2) подается значение вход 6, равное 00000000000000000000000000000000. Таким образом, на выходе первого слоя формируется 2 промежуточных 32-битных значения, которые подаются на сумматор блок 36: 11111111111111001011011000110100 и 00000000000011111010000000000000. Параллельно этому генератор промежуточных значений (блок 1) и мультиплексор выбора операции (блок 2) могут начать обработку следующего набора операндов.

После, по заднему фронту синхросигнала CK последний слой сумматоров в конвейере свертки промежуточных значений (блок 3) заканчивает операцию умножения сложением последних промежуточных значений, формируя результат (выход 9), равный 00000000000011000101011000110100. Затем, до следующего положительного фронта CK будет удерживаться результат на выходе конвейера свертки промежуточных значений.

Пример исполнения операции комбинированного умножения-сложения (MAC-операции).

Пусть операнд-множимое (вход 4) равно 0000000011111010 (далее – А), операнд-множитель (вход 5) равен 0000110010100010 (далее – В) и флаг выбора операции (вход 8) равен 1, операнд MAC-операции (вход 7) равен 00001010111100110000101011110011, и следовательно, в регистр мультиплексора выбора операции (блок 22) записывается значение операнда MAC-операции (вход 7).

По переднему фронту синхросигнала (далее – CK) в генераторе промежуточных значений (блок 1) блоки генерации промежуточных значений вычисляют из А промежуточные 18-битные значения. Так, блок 11 генерирует значение 4*А равное 000000001111101000, блок 12 генерирует значение 3*А равное 000000001011101110, блок 13 генерирует значение 2*А равное 000000000111110100, блок 14 генерирует значение А равное 000000000011111010, блок 15 генерирует значение минус А равное 111111111100000110, блок 16 генерирует значение минус 2*А равное 111111111000001100, блок 17 генерирует значение минус 3*А, равное 111111110100010010, блок 18 генерирует значение минус 4*А равное 111111110000011000. Промежуточное значение коэффициента 0 не генерируется, а мультиплицируется из опорного 0 (вход 6).

Параллельно этому, мультиплексор генератора промежуточных значений (блок 19) производит коммутацию конвейер свертки промежуточных значений с блоками генерации в соответствии с В (вход 5). Для этого, В (вход 5) разбивается на 6 битовых групп со взаимным перекрытием на 1 бит, и поступают на управляющие входы мультиплексоров генератора промежуточных значений (блоки 191-196), причем, на управляющем входе мультиплексора (блок 191) битовая группа смещается влево на 1, а на управляющем входе мультиплексора (блок 196) расширяется знаковый бит, тем самым получая следующий набор квартетов входа: управляющий вход блока 191 = 0100, управляющий вход блока 192 = 1000, управляющий вход блока 193 = 0101, управляющий вход блока 194 = 1100, управляющий вход блока 195 = 0001, управляющий вход блока 196 = 0000. Каждому коэффициенту промежуточных значений соответствует один или более вариантов квартетов бинарных чисел (см. фиг.14). Так же, мультиплексоры генератора промежуточных значений (блоки 191-196) приводят промежуточные значения к 32-битному виду, за счет смещения влево значения на номер квартета умноженного на 3, и заполнением оставшихся старших битов посредством расширения знакового бита, или наоборот, отбрасыванием старшего бита промежуточного значения в случае 5 квартета. Таким образом, мультиплексор генератора промежуточных значений (блок 19) передает в конвейер свертки промежуточных значений (блок 3) следующий набор пар промежуточных значений в сумматоры первого слоя: сумматор блок 31 00000000000000000000000111110100 и 11111111111111111110000011000000, сумматор блок 32 00000000000000001011101110000000 и 11111111111111000001100000000000, сумматор блок 33 00000000000011111010000000000000 и 00000000000000000000000000000000.

После, по заднему фронту синхросигнала CK первый слой сумматоров (блоки 31-33) в конвейере свертки промежуточных значений начинает попарно складывать значения, переданные из генератора промежуточных значений (блок 1). Таким образом, на выходе первого слоя формируется 3 промежуточных 32-битных значения, которые передаются в сумматоры второго слоя: сумматор блок 34 11111111111111111110001010110100 и 11111111111111001101001110000000, сумматор блок 35 00000000000011111010000000000000.

После, по следующему переднему фронту синхросигнала CK второй слой сумматоров (блоки 34-35) в конвейер свертки промежуточных значений начинает попарно складывать переданные из предыдущего слоя промежуточные значения. Так как исполняется MAC-операция, на вход сумматора блок 35 из мультиплексора выбора операции (блок 2) подается значение (вход 7), равное 00001010111100110000101011110011. Таким образом, на выходе первого слоя формируется 2 промежуточных 32-битных значения, которые подаются на сумматор блок 36: 11111111111111001011011000110100 и 00001011000000101010101011110011. Параллельно этому генератор промежуточных значений (блок 1) и мультиплексор выбора операции (блок 2) могут начать обработку следующего набора операндов.

После, по заднему фронту синхросигнала CK последний слой сумматоров в конвейере свертки промежуточных значений (блок 3) заканчивает операцию умножения сложением последних промежуточных значений, формируя результат (выход 9), равный 00001010111111110110000100100111. Затем, до следующего положительного фронта CK будет удерживаться результат на выходе конвейера свертки промежуточных значений.

Использование заявляемого изобретения позволяет быстро проводить большое количество операций умножения или комбинированного умножения-сложения в конвейерном режиме работы, то есть каждый такт работы получать на вход новый набор значений операндов и выдавать на выход новый результат, получаемый на основе старого набора значений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для контроля умножения по модулю три | 1982 |

|

SU1072049A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ УМНОЖЕНИЯ-СЛОЖЕНИЯ С УПАКОВАННЫМИ ДАННЫМИ | 1996 |

|

RU2139564C1 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| ЦИФРОВЫЕ СИГНАЛЬНЫЕ ПРОЦЕССОРЫ С КОНФИГУРИРУЕМЫМ СДВОЕННЫМ БЛОКОМ УМНОЖЕНИЯ-НАКОПЛЕНИЯ И СДВОЕННЫМ АРИФМЕТИКО-ЛОГИЧЕСКИМ УСТРОЙСТВОМ | 2005 |

|

RU2342694C2 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

Изобретение относится к области компьютерных устройств и применяется при проектировании нейроморфных процессоров. Сущность заявленного устройства заключается в следующем. Конвейерный умножитель содержит генератор промежуточных значений, выполненный с возможностью приема первого и второго операндов и способный генерировать промежуточные результаты умножения, трёхслойный конвейер свертки промежуточных значений типа «древо Уоллеса» для сложения полученных промежуточных значений и получения результата умножения, мультиплексор выбора операции умножения или комбинированного умножения-сложения с третьим операндом. При этом разрядность входных операндов умножителя составляет 16 бит, разрядность результата выполнения операции составляет 32 бита, разрядность третьего операнда для МАС-операции составляет 32 бита. При этом блоки по синхросигналу выполнены так, что каждый следующий блок работает по инверсному фронту синхросигнала относительно предыдущего; генератор промежуточных значений выполнен на основе модифицированного алгоритма Бута, в котором реализована параллельная генерация всех вариантов промежуточных значений за полтакта. Техническим результатом является увеличение быстродействия устройства. 4 з.п. ф-лы, 15 ил.

1. Конвейерный умножитель, содержащий генератор промежуточных значений, выполненный с возможностью приема первого и второго операндов, а также генерации промежуточных результатов умножения, выходы которого соединены со входами конвейера свертки промежуточных значений, вход которого связан с выходом мультиплексора выбора операции умножения или комбинированного умножения-сложения с третьим операндом, отличающийся тем, что конвейерный умножитель выполнен с возможностью обработки входных операндов разрядностью 16 бит, получения результата выполнения операции разрядностью 32 бита, работы каждого следующего блока по инверсному относительно предыдущего блока фронту синхросигнала; генератор промежуточных значений выполнен с возможностью реализации модифицированного алгоритма Бута Radix-8, а также ускоренной генерации промежуточных значений с неединичными коэффициентами за полтакта и параллельной генерации всех вариантов промежуточных значений; конвейер свёртки выполнен трёхслойным по типу «древо Уоллеса» с возможностью сложения шести промежуточных значений.

2. Конвейерный умножитель по п.1, отличающийся тем, блоки генератора промежуточных значений выполнены с возможностью генерации вариантов промежуточных значений из операнда-множимого.

3. Конвейерный умножитель по п.1, отличающийся тем, что мультиплексор генератора промежуточных значений состоит из шести параллельных мультиплексоров.

4. Конвейерный умножитель по п.1, отличающийся тем, что конвейер свертки выполнен с возможностью проведения трёх этапов сложения, каждый из которых осуществляется отдельной группой сумматоров.

5. Конвейерный умножитель по п.1, отличающийся тем, мультиплексор выбора операции выполнен с возможностью записи на основе значения флага выбора операции значения 32-битного операнда в случае исполнения операции комбинированного умножения-сложения либо записи логического ноля в случае исполнения операции умножения в 32-битный регистр при параллельной генерации промежуточных значений и их загрузке в конвейер свертки промежуточных значений посредством коммутации через мультиплексор, передающий полученное значение в конвейер свертки промежуточных значений.

| US 7730118 B2, 01.06.2010 | |||

| US 10437558 B2, 08.10.2019 | |||

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| КОНВЕЙЕРНЫЙ УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2023 |

|

RU2797164C1 |

Авторы

Даты

2024-10-01—Публикация

2024-02-27—Подача