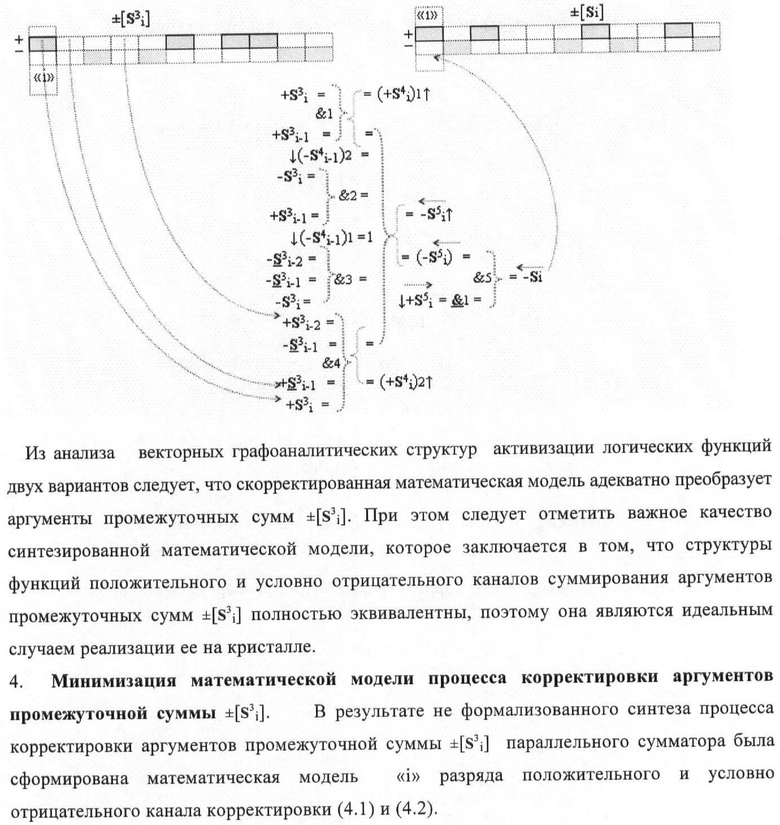

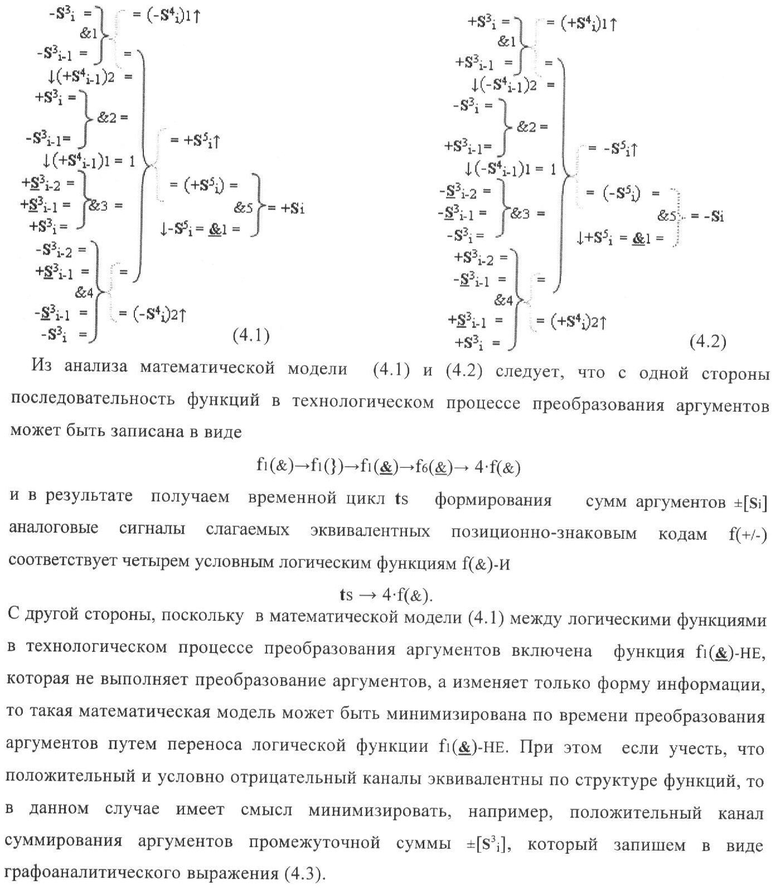

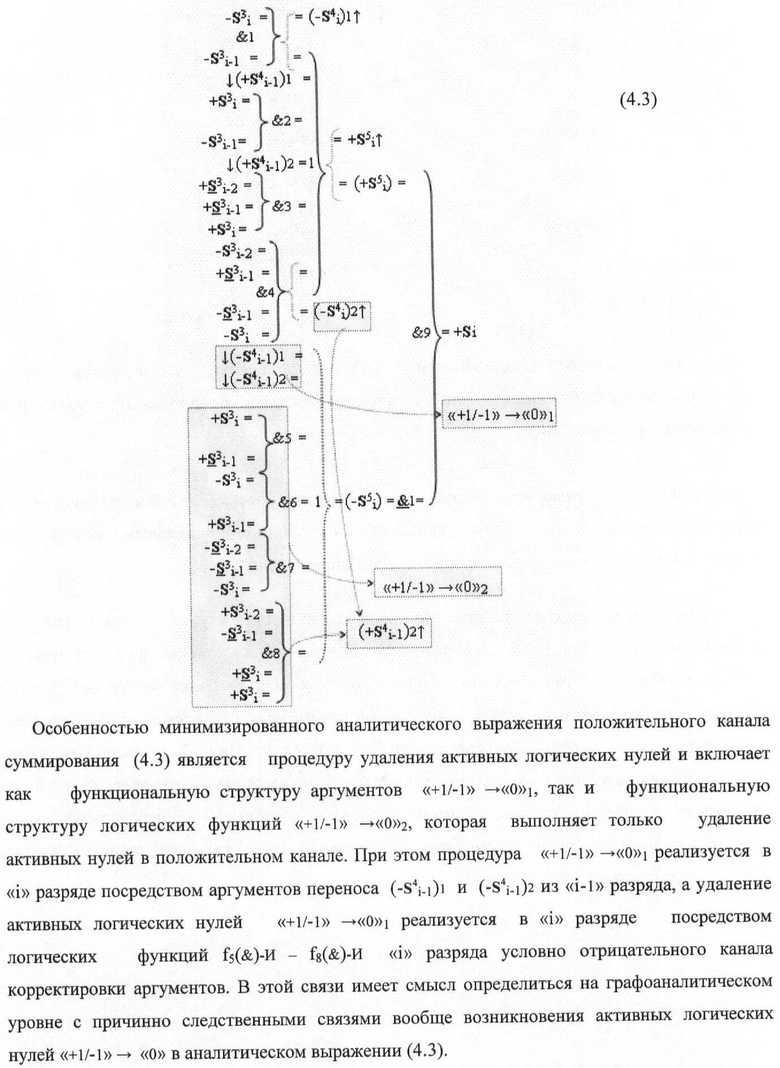

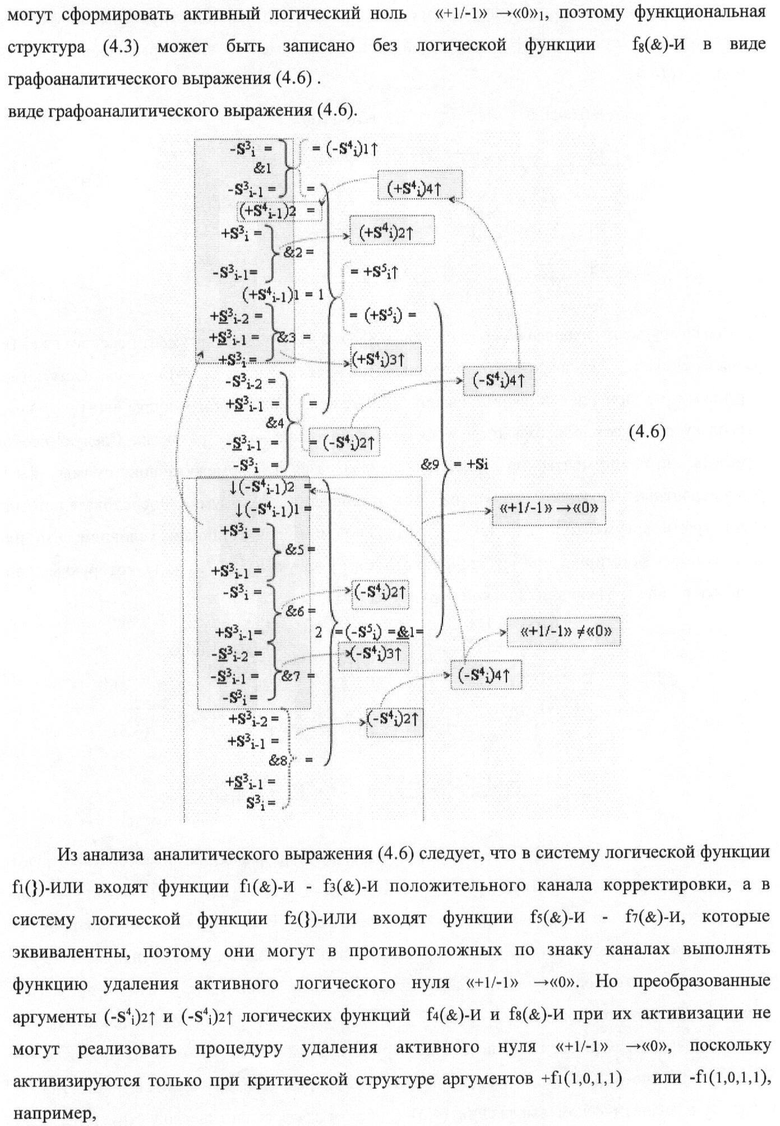

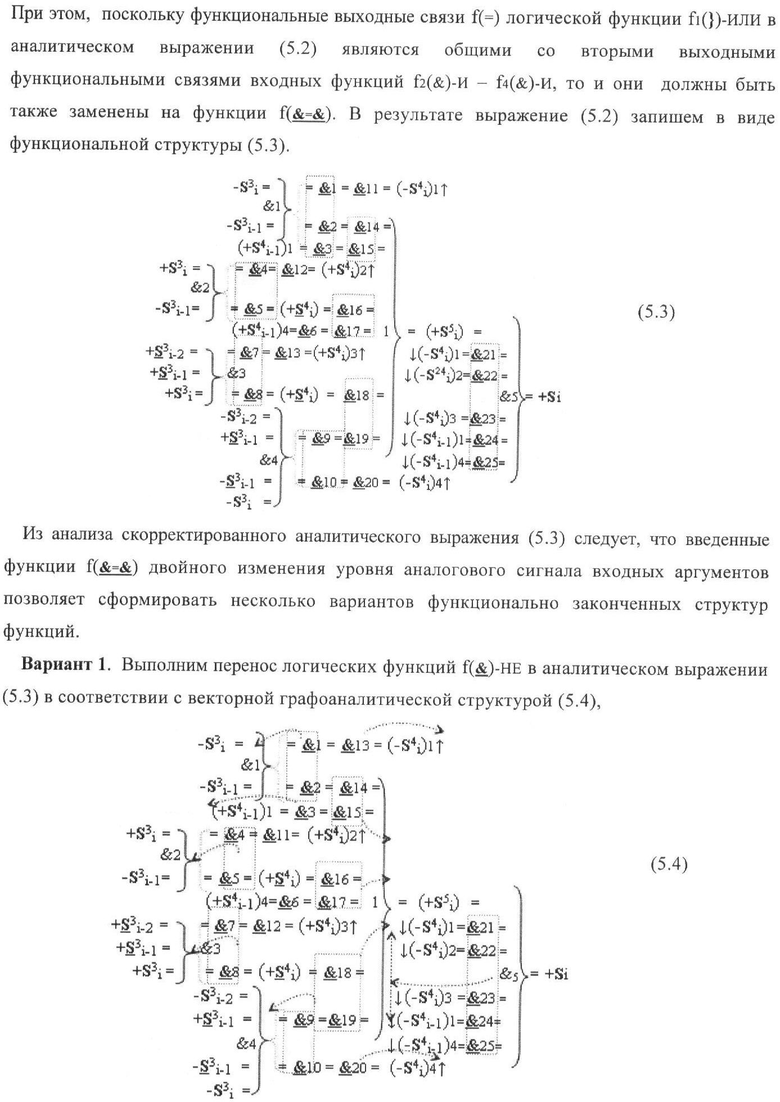

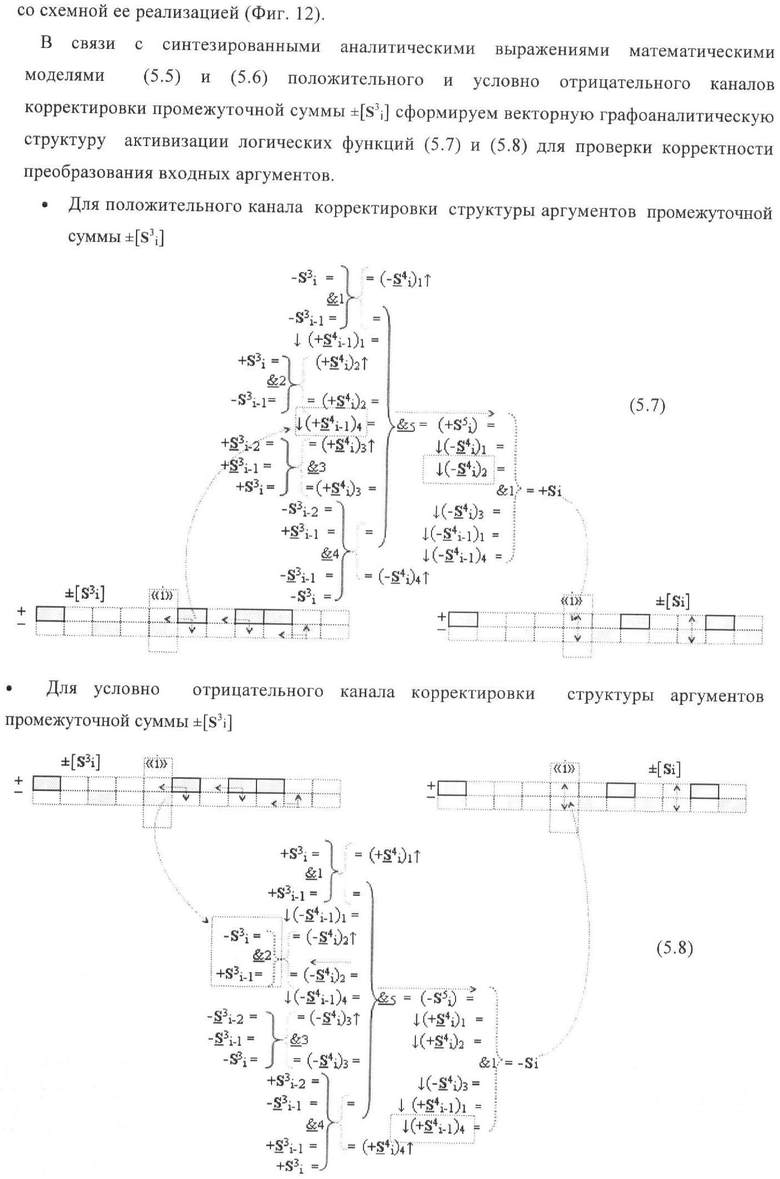

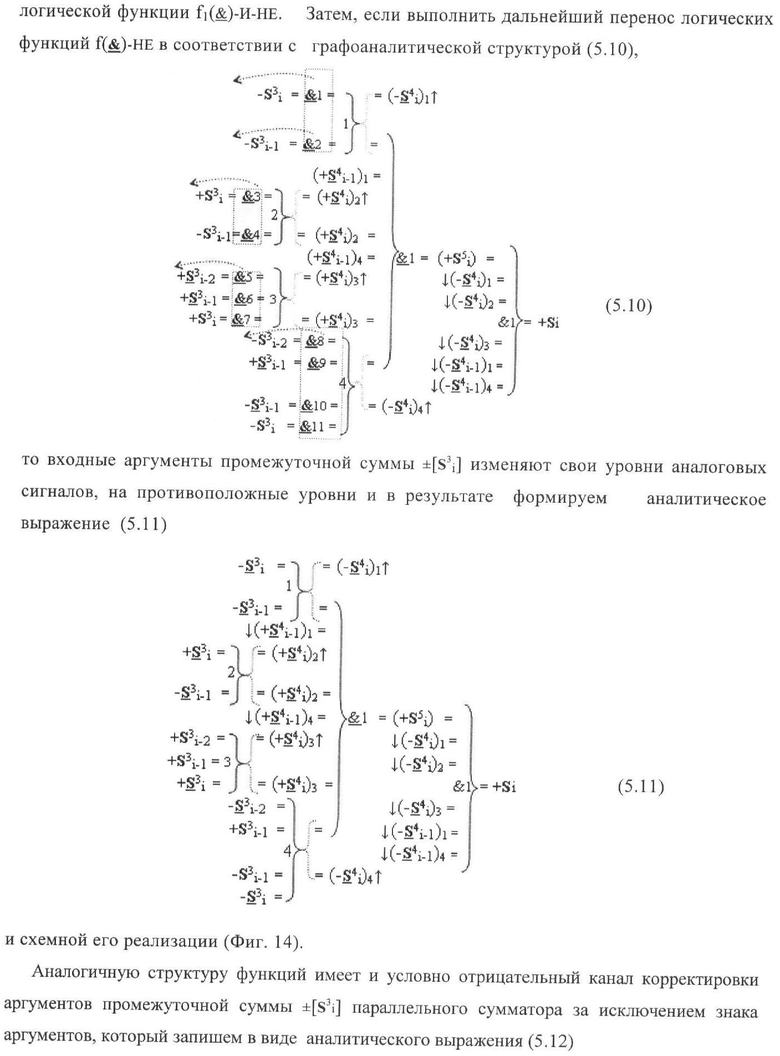

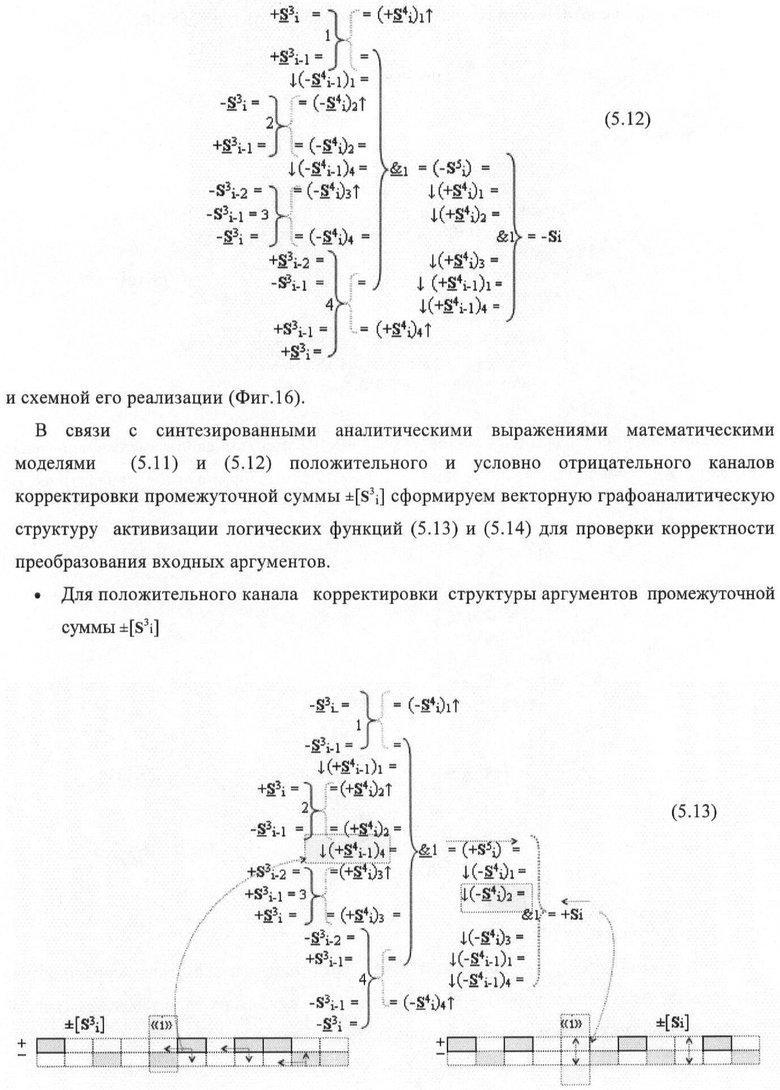

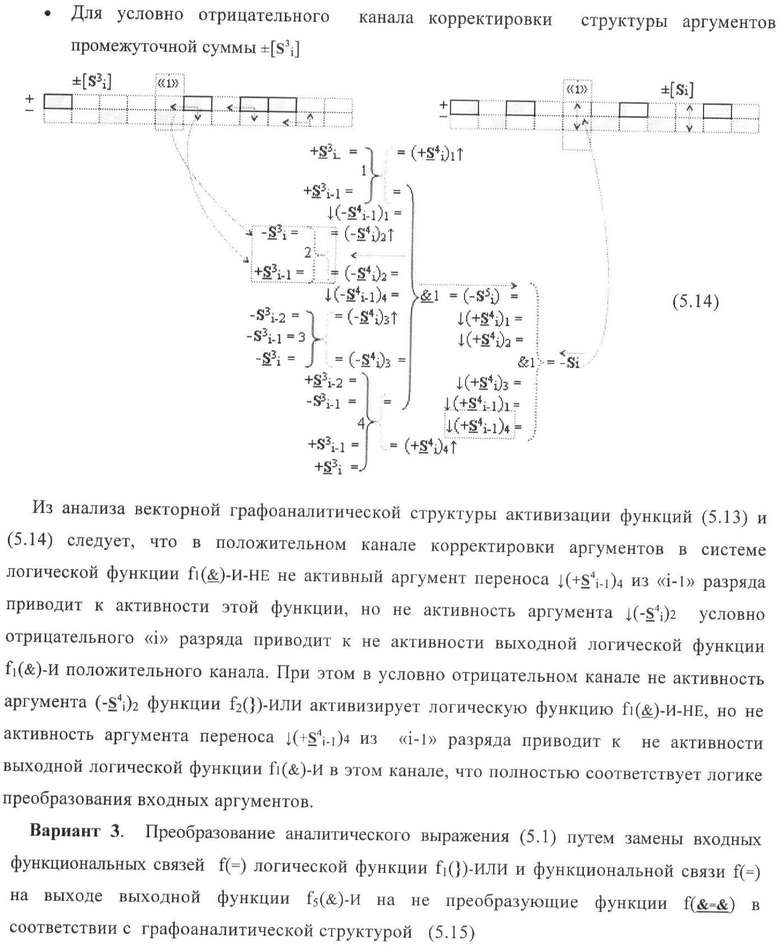

Текст описания приведен в факсимильном виде.

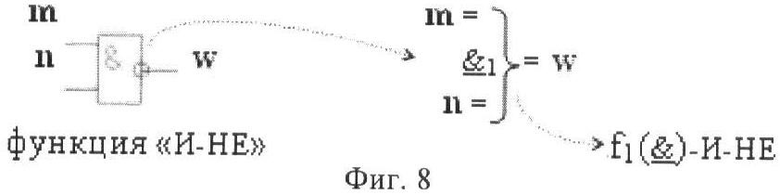

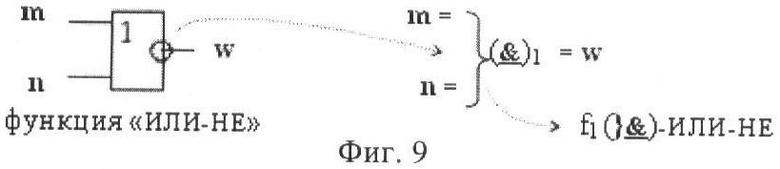

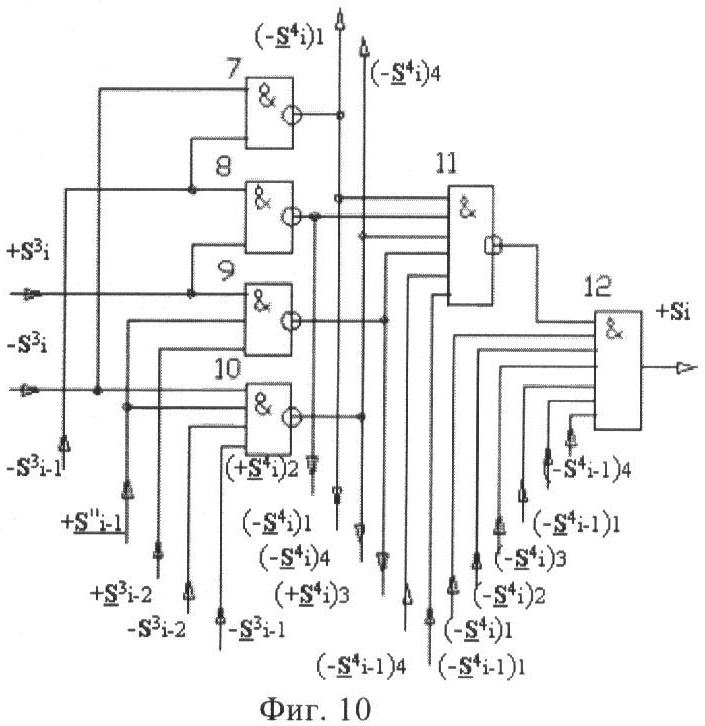

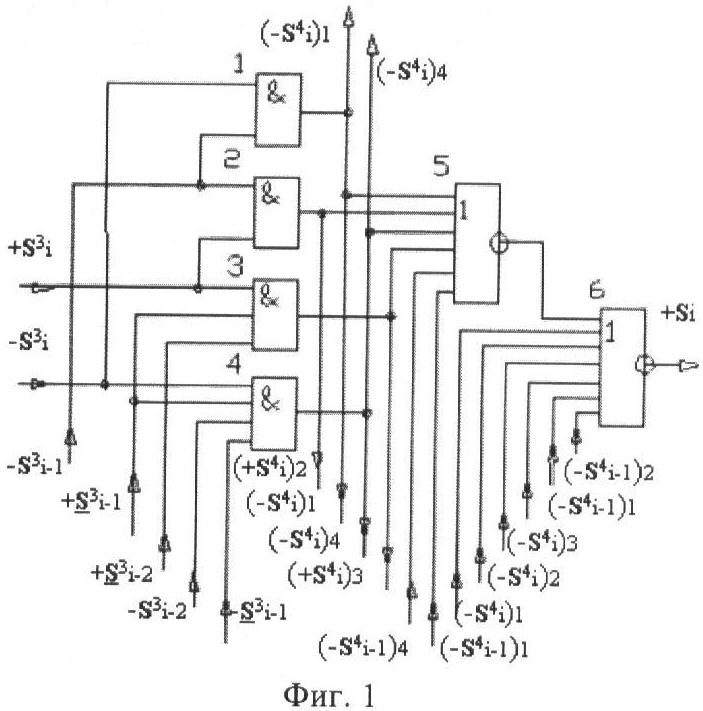

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств для выполнения арифметических операций суммирования и вычитания в позиционно-знаковых кодах. Техническим результатом является упрощение функциональной структуры сумматора. Каждый разряд сумматора выполнен в виде двух эквивалентных по структуре каналов - положительного и условно отрицательного, при этом, в одном из вариантов выполнения, i-ый разряд каждого канала содержит четыре логических элемента И и два логических элемента ИЛИ-НЕ. 4 н.п. ф-лы, 21 ил.

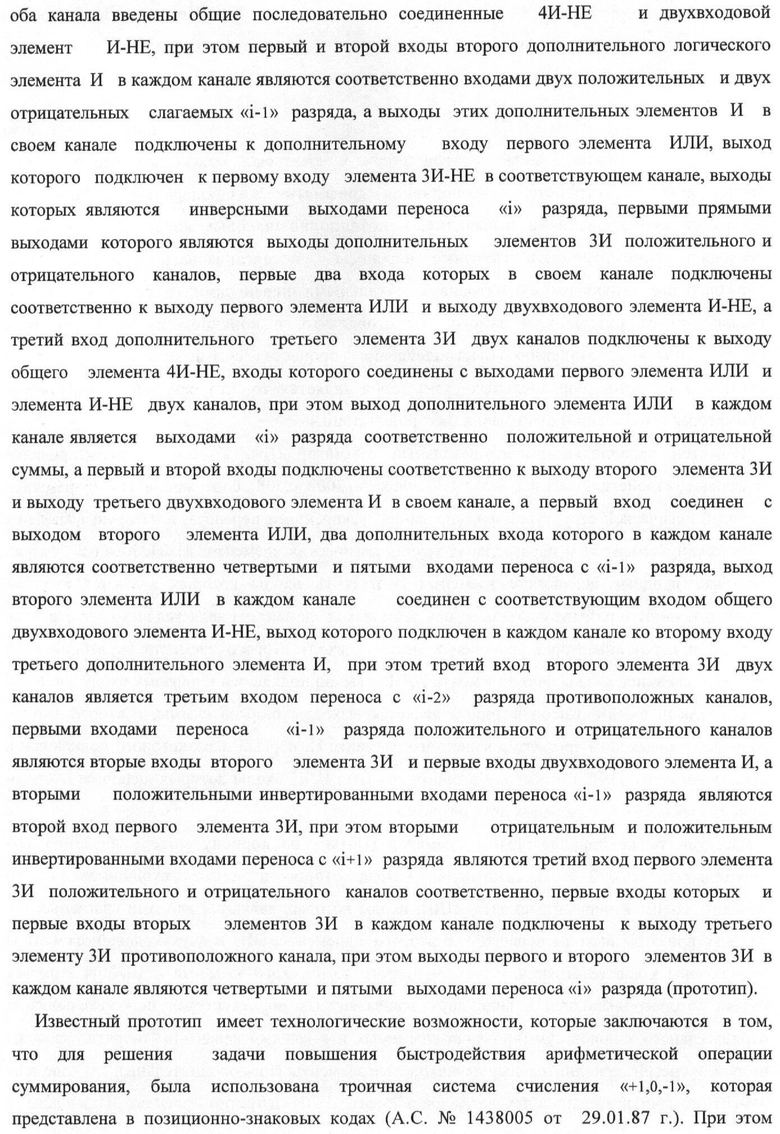

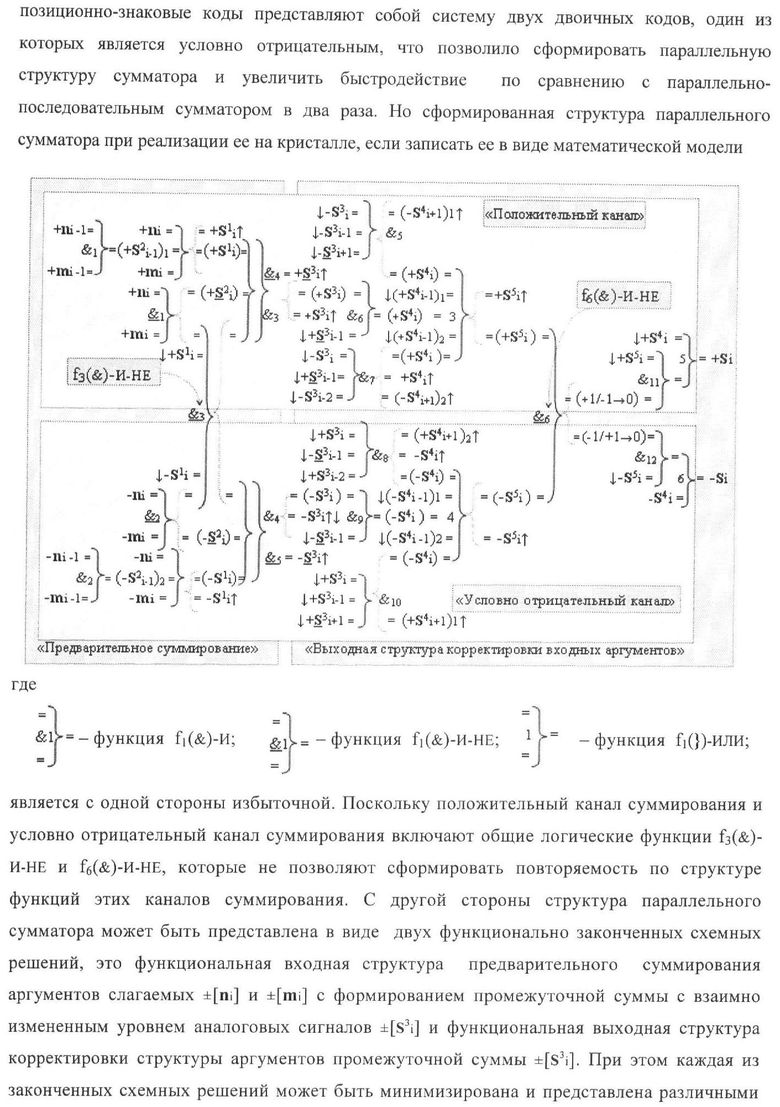

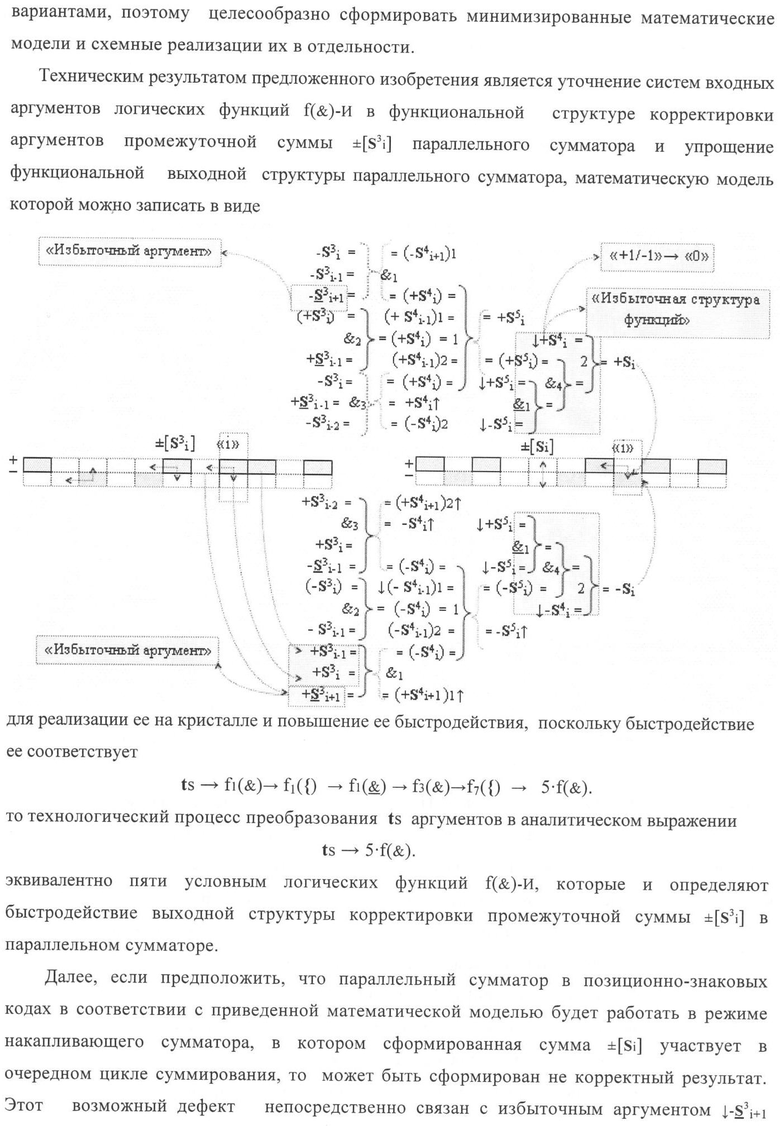

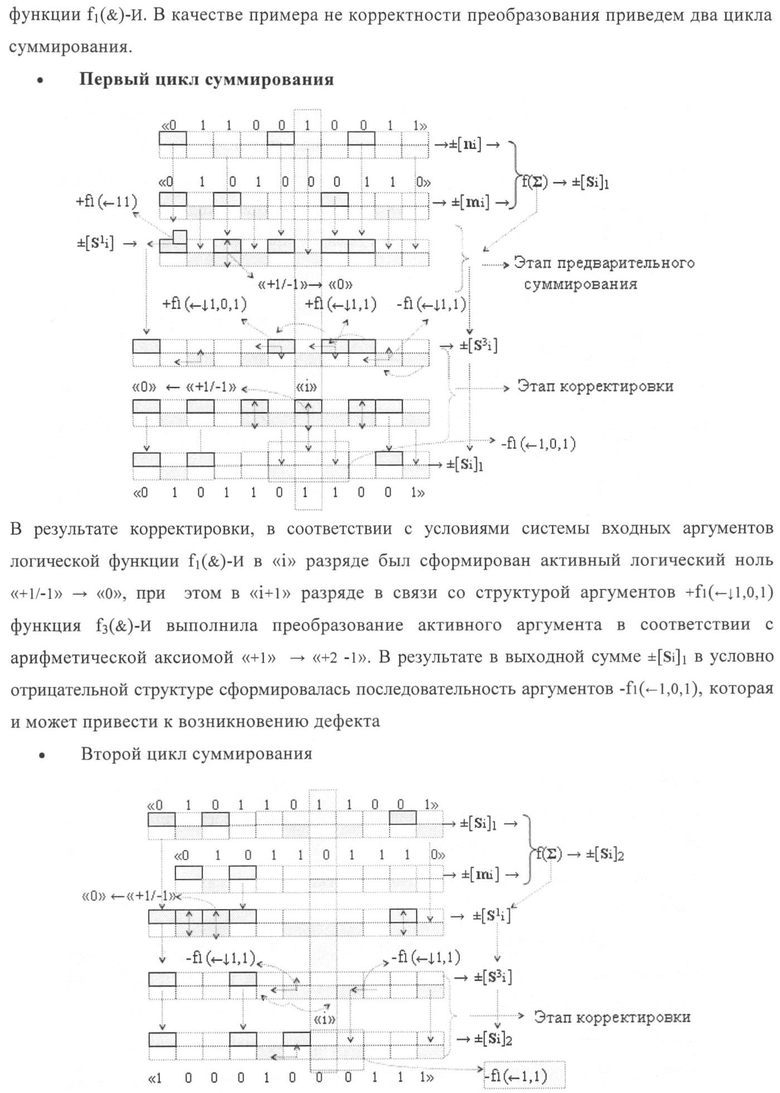

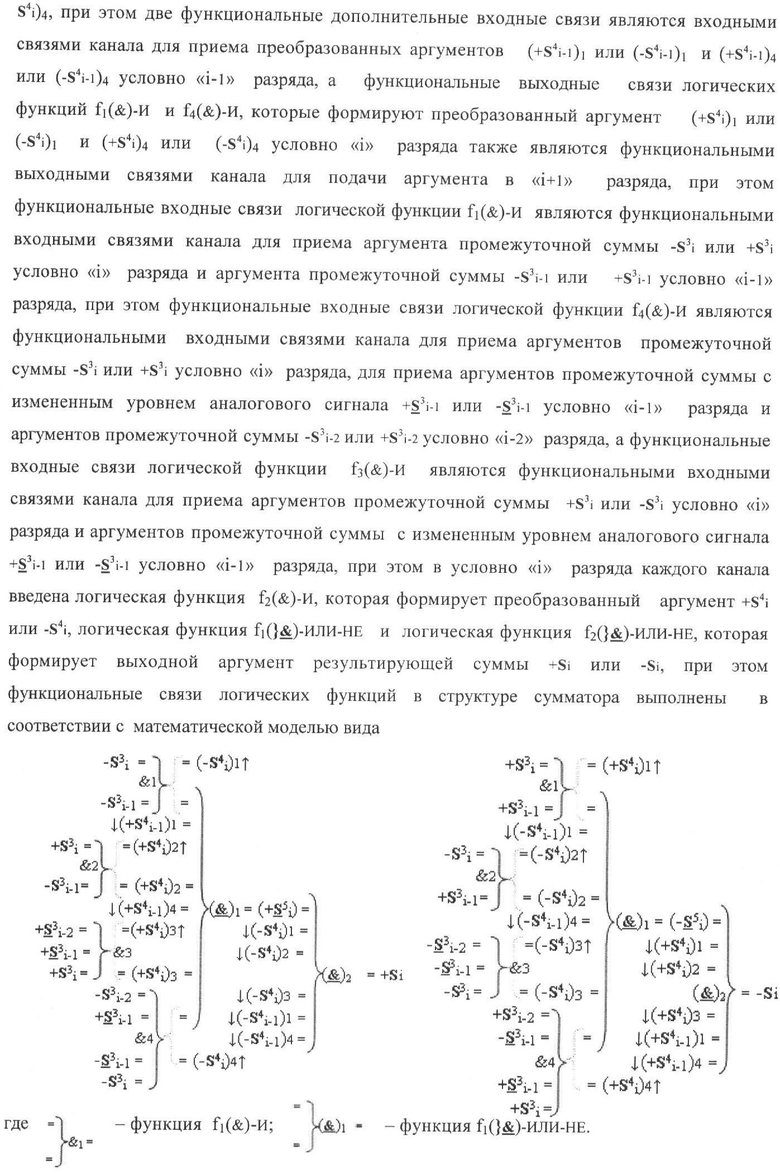

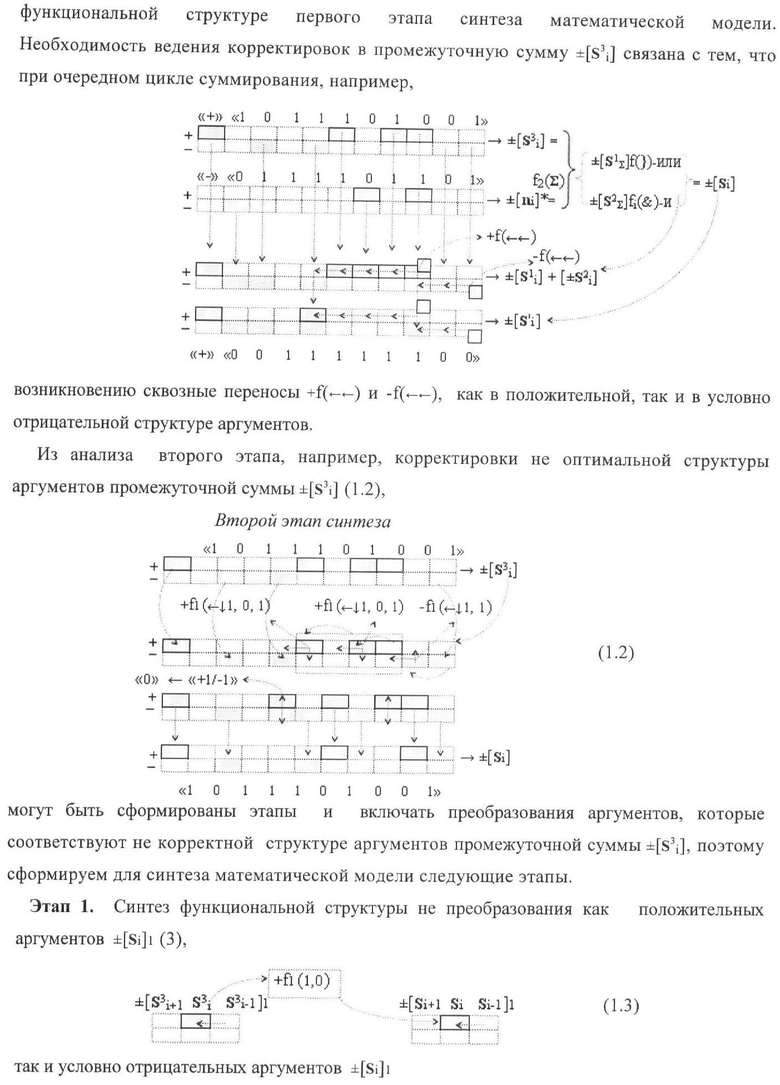

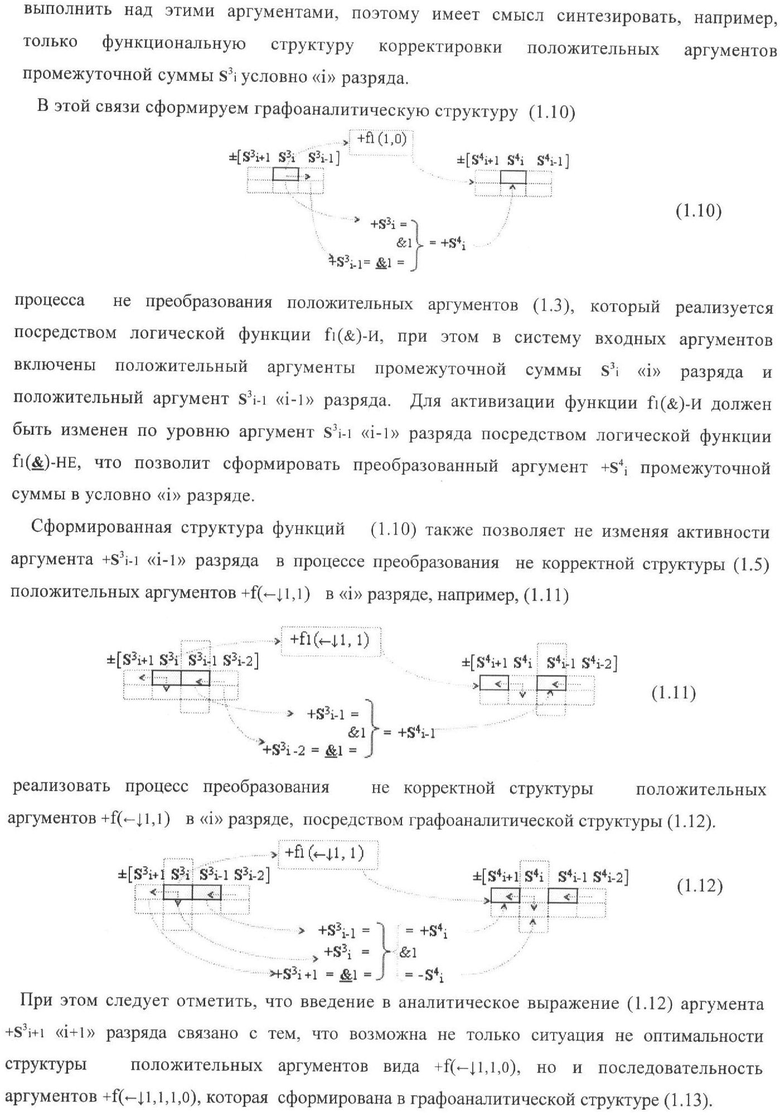

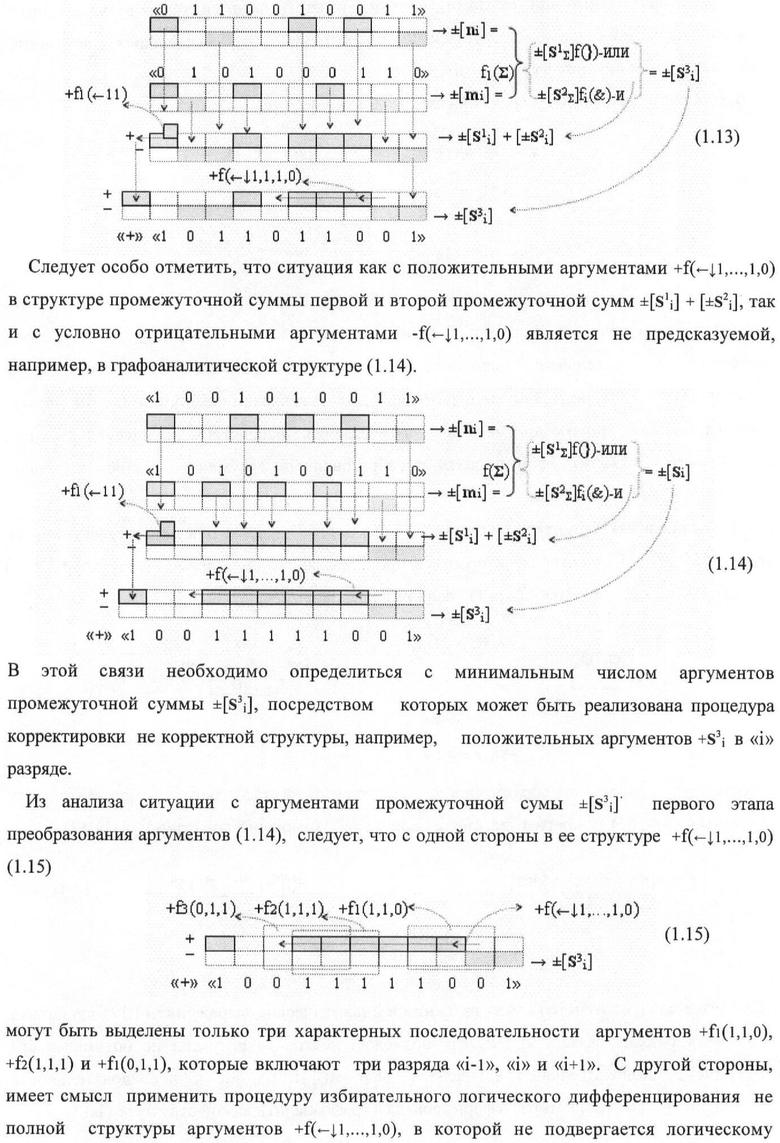

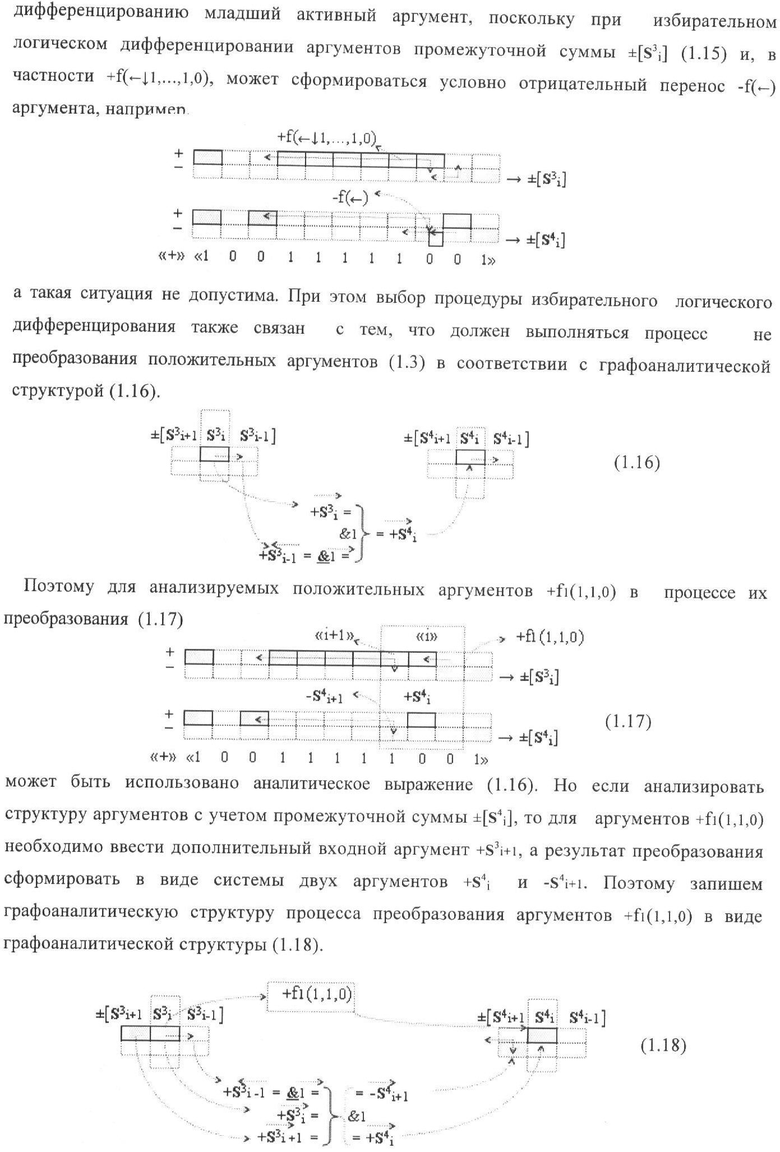

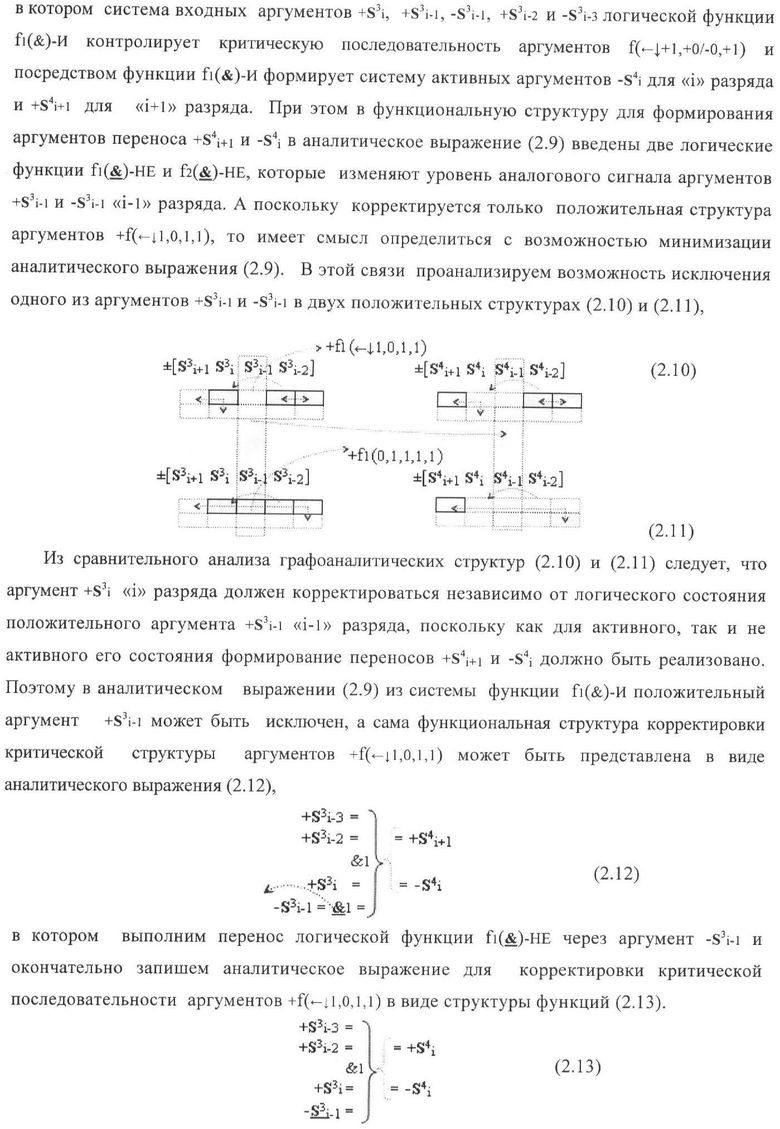

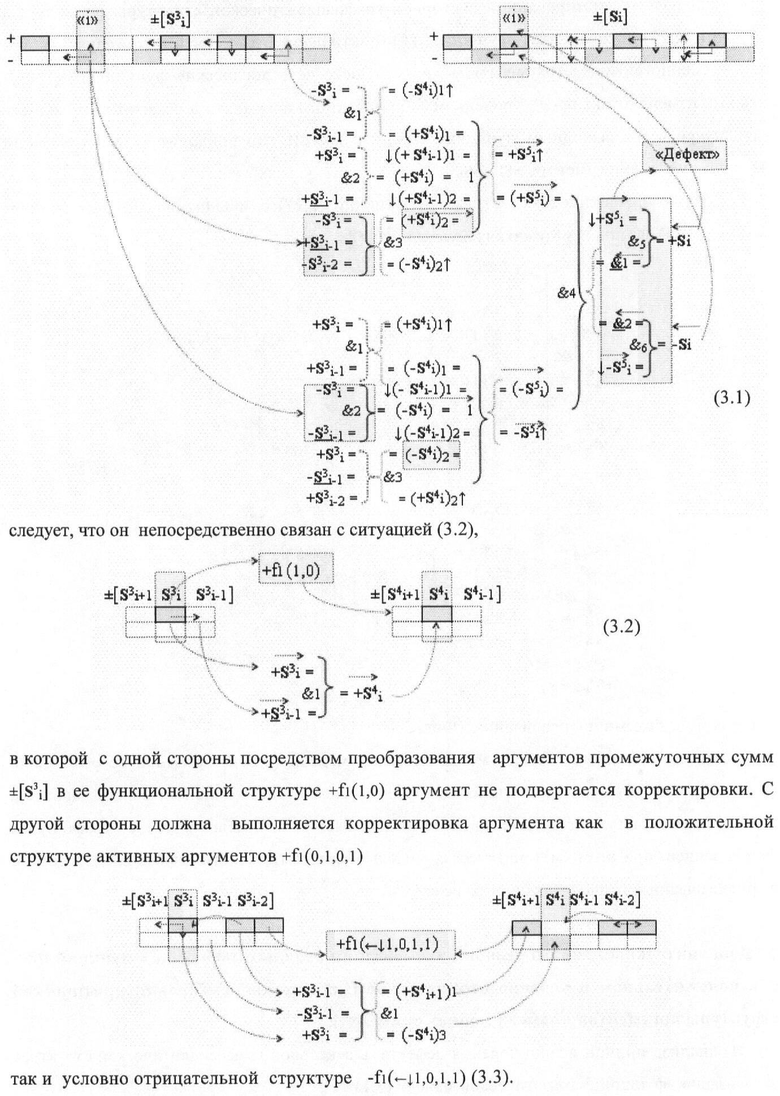

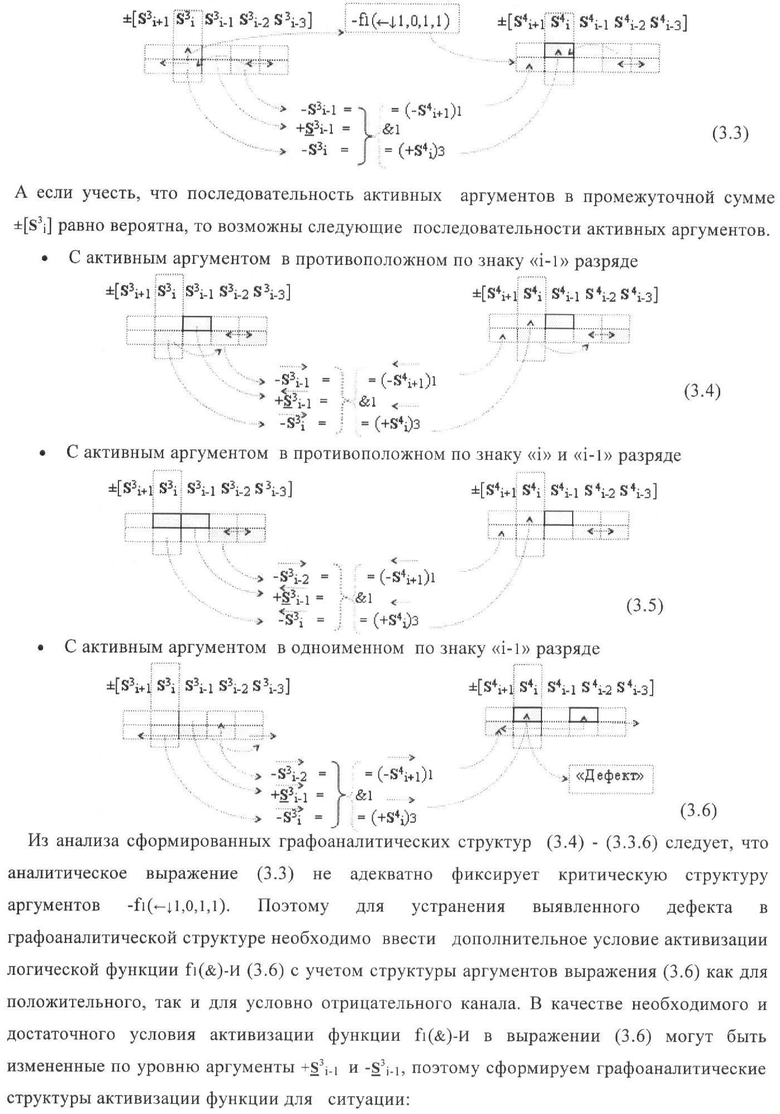

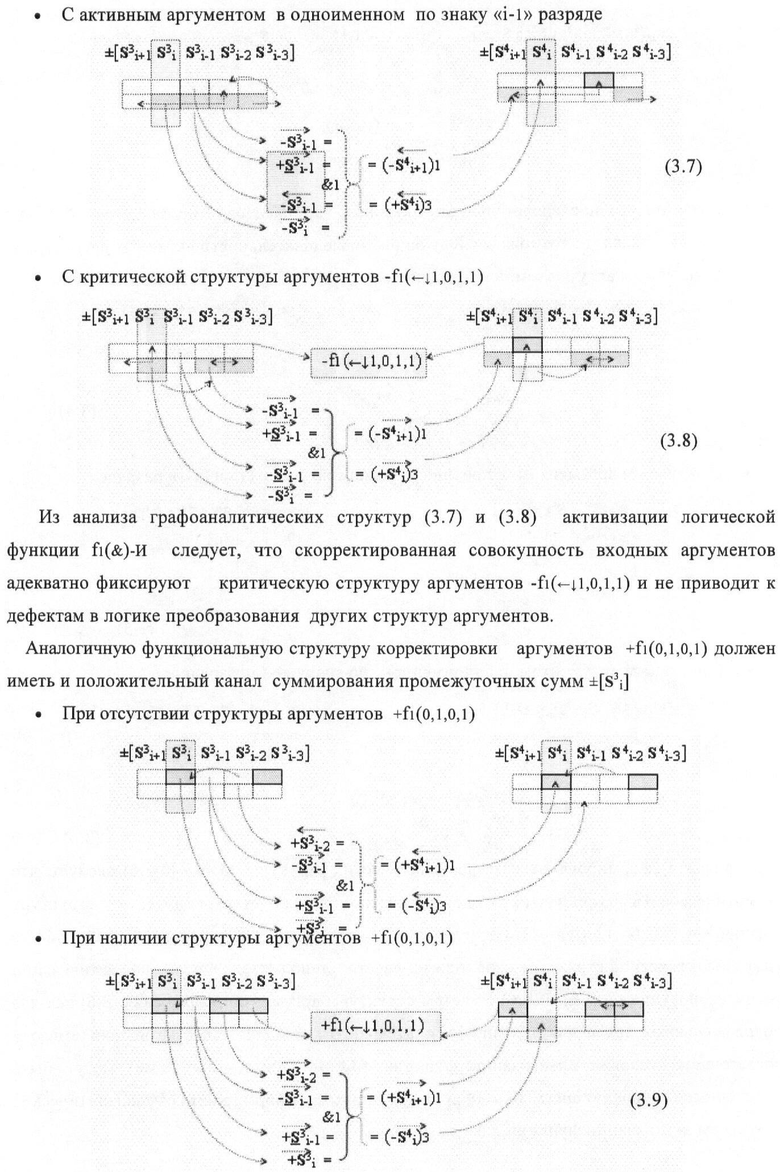

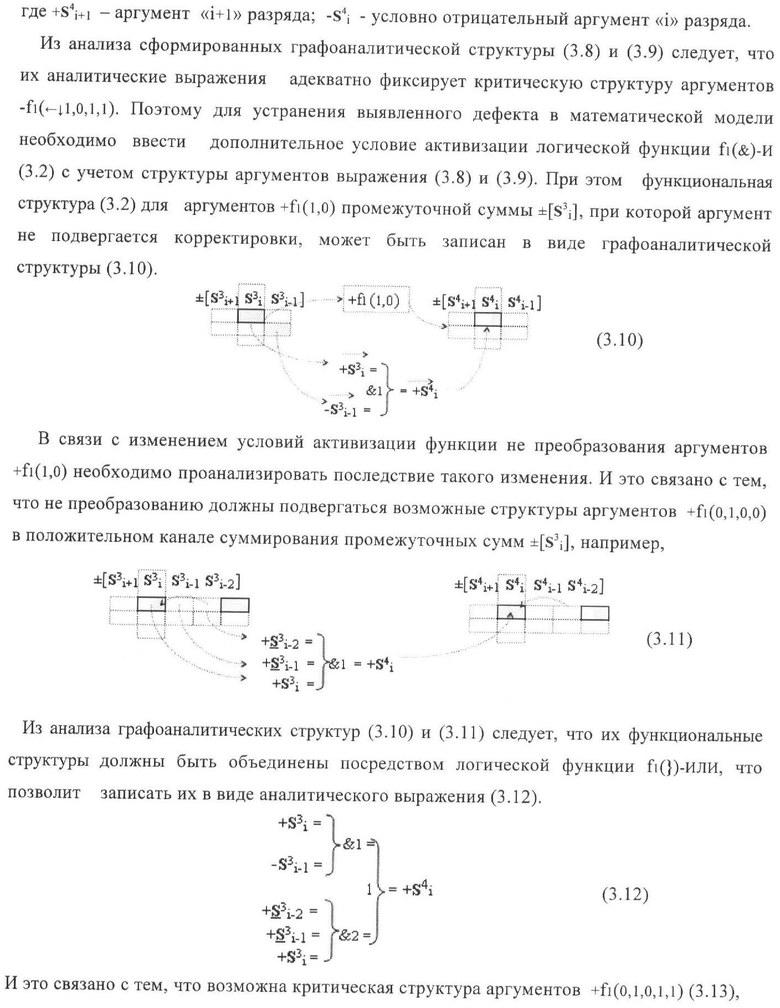

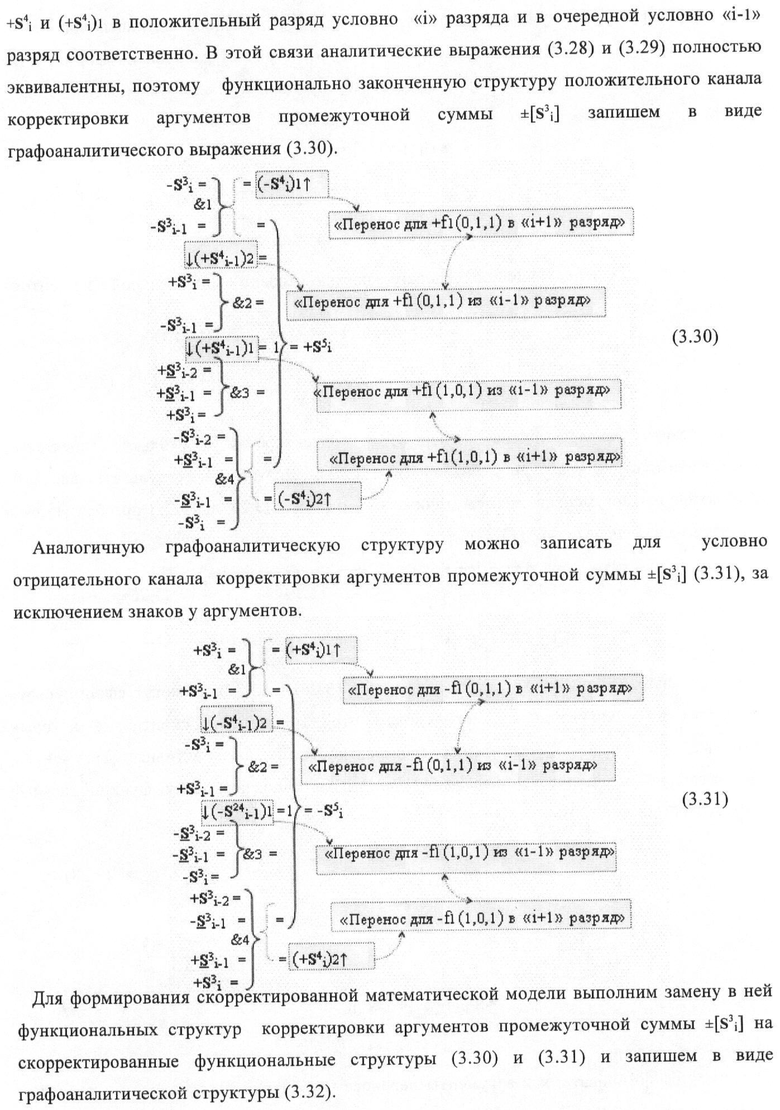

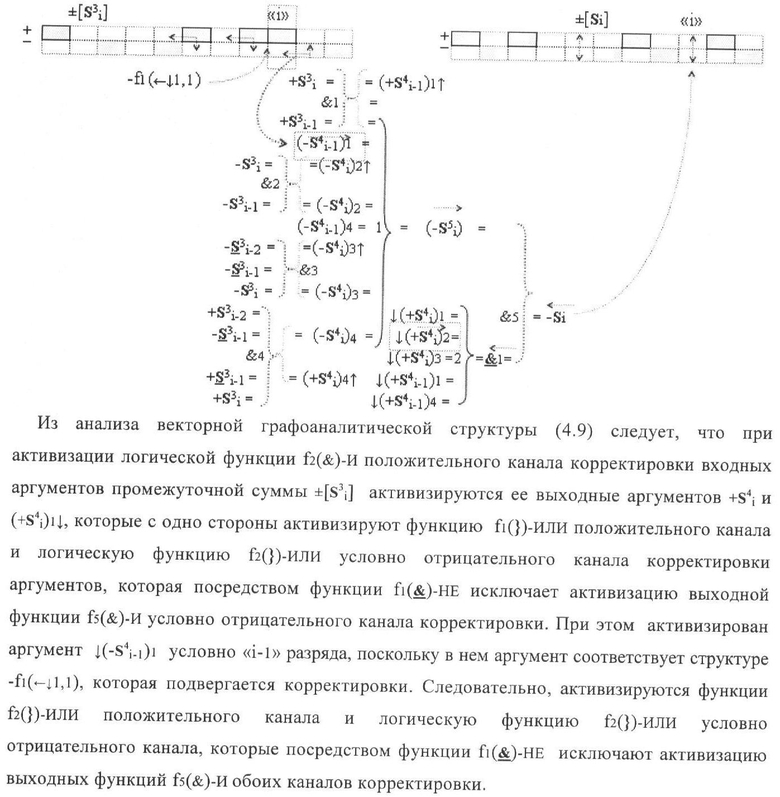

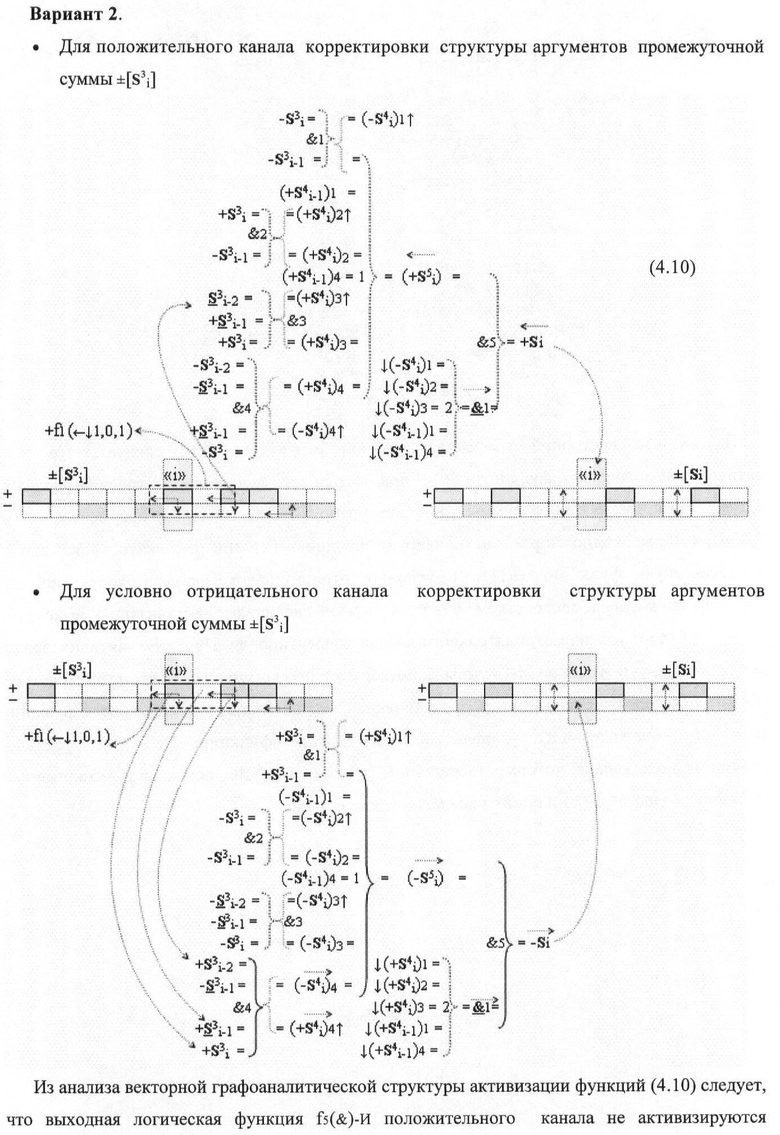

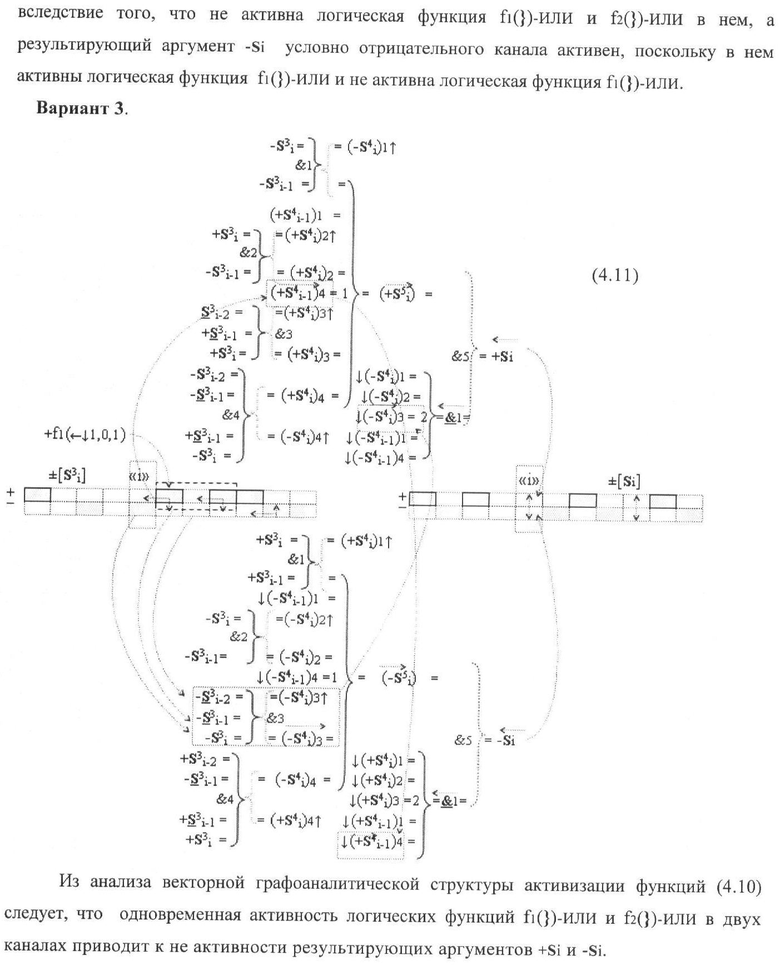

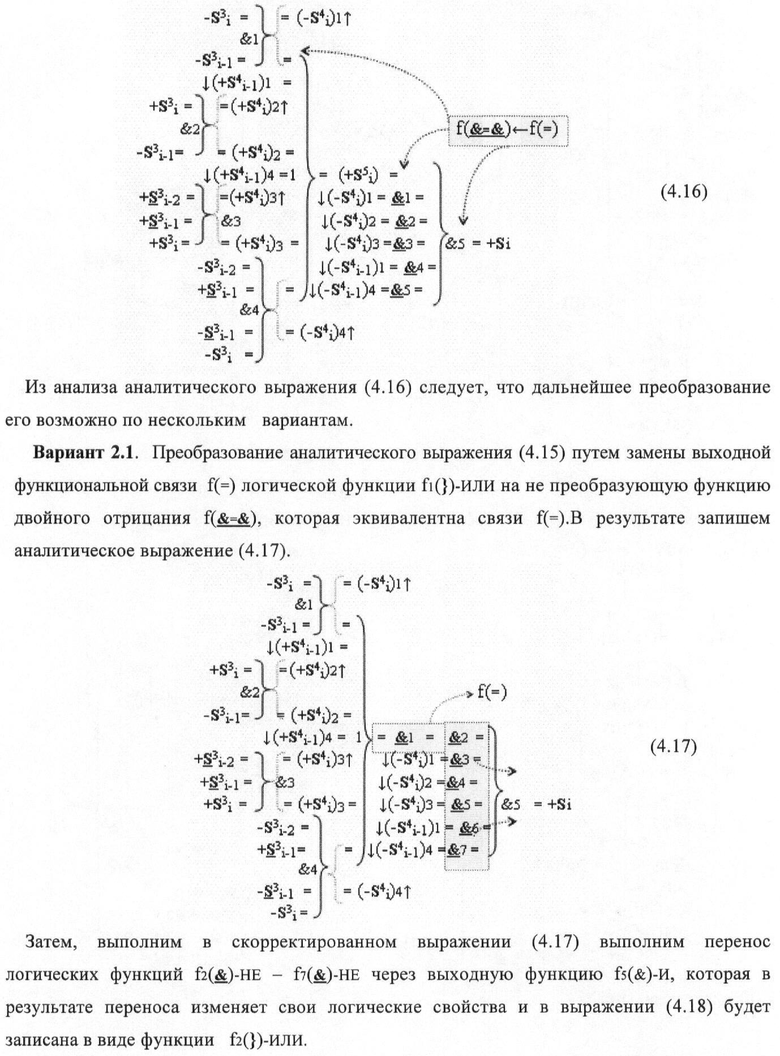

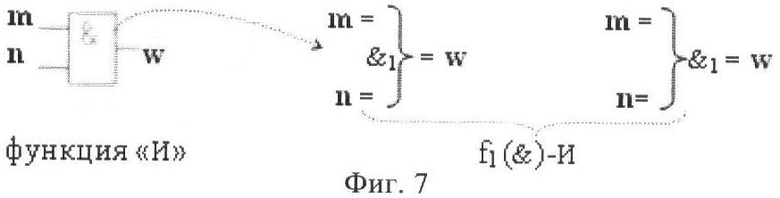

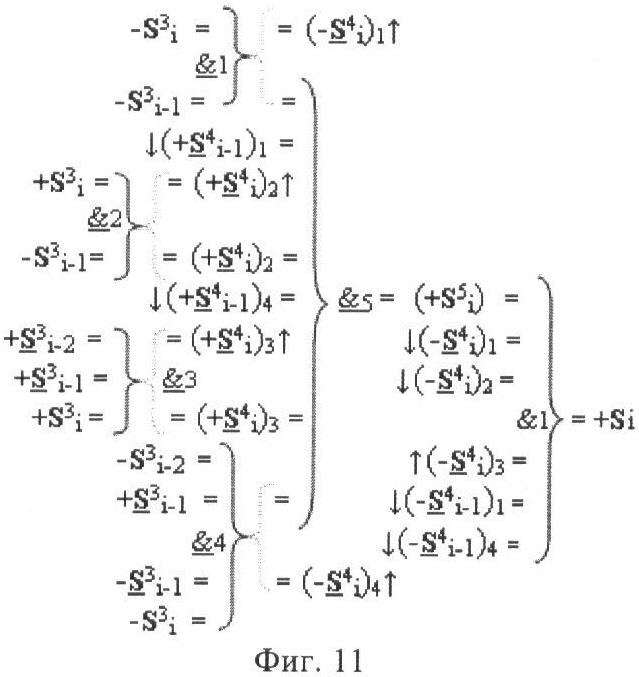

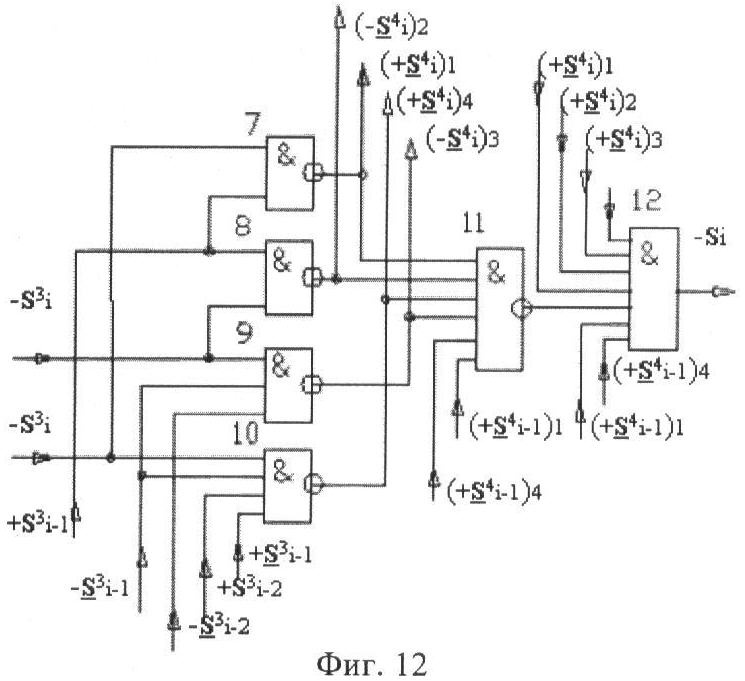

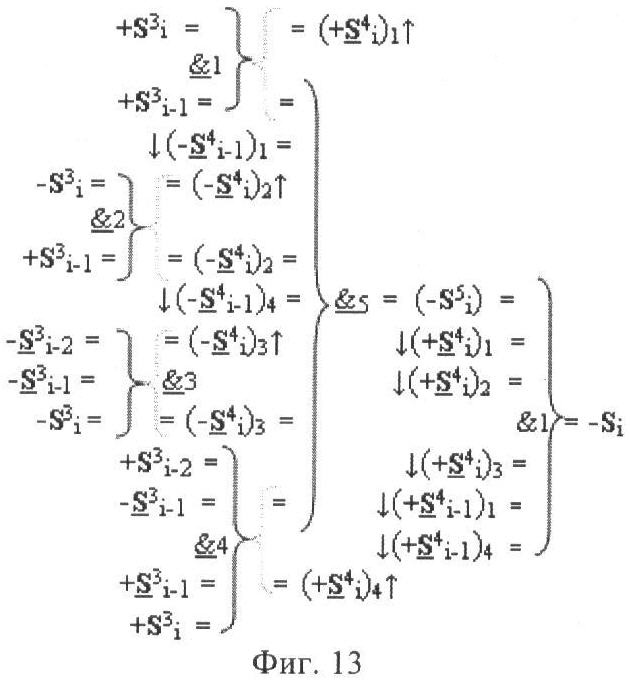

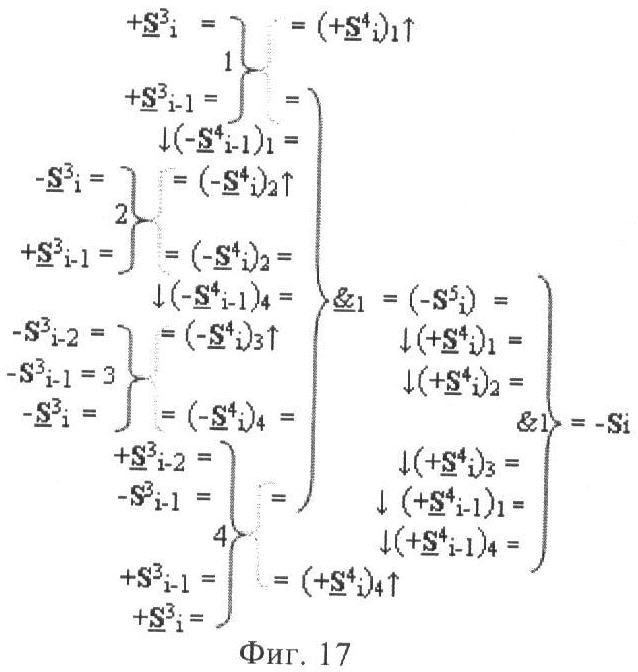

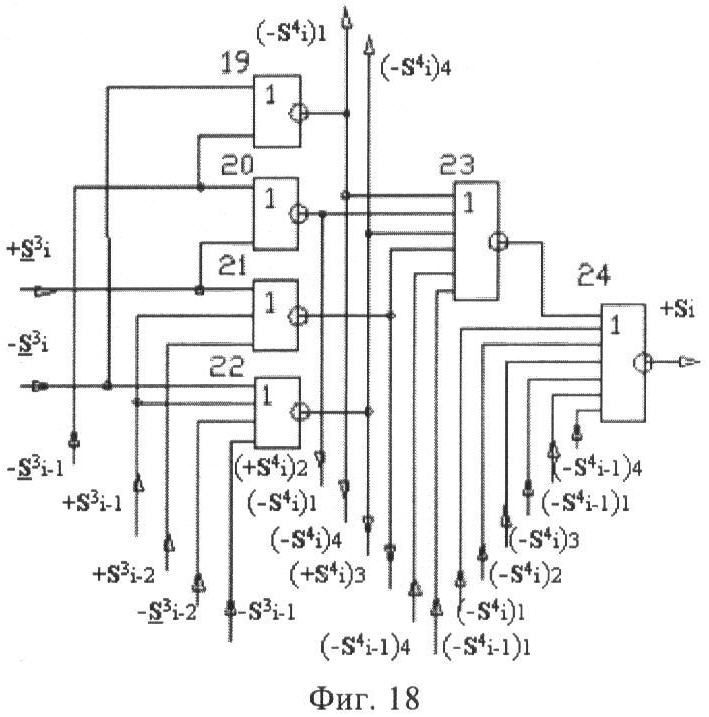

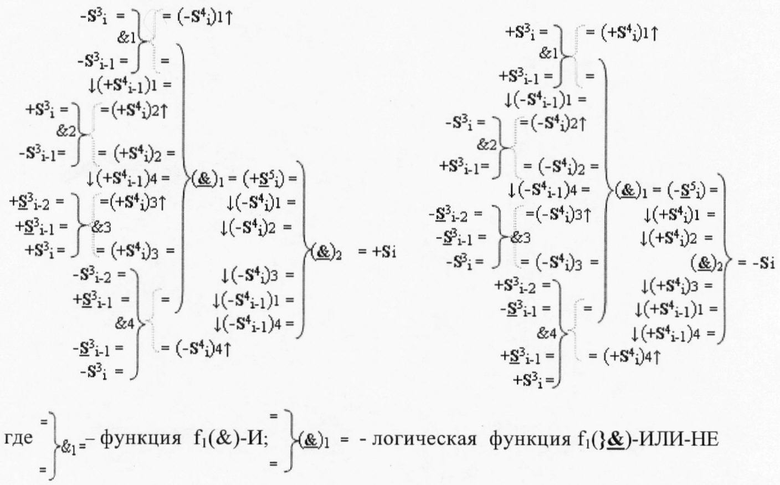

1. Функциональная структура корректировки аргументов промежуточной суммы ±[S3i] параллельного сумматора в позиционно-знаковых кодах f(+/-), условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов корректировки аргументов, и каждый канал «i» разряда включает три логические функции f1(&)-И, f3(&)-И и f4(&)-И, которые формируют преобразованные аргументы  или

или

или

или  и

и  или

или  при этом две функциональные дополнительные входные связи являются входными связями канала для приема преобразованных аргументов

при этом две функциональные дополнительные входные связи являются входными связями канала для приема преобразованных аргументов  или

или  и

и  или

или  условно «i-1» разряда, а функциональные выходные связи логических функций f1(&)-И и f4(&)-И, которые формируют преобразованный аргумент

условно «i-1» разряда, а функциональные выходные связи логических функций f1(&)-И и f4(&)-И, которые формируют преобразованный аргумент  или

или  и

и  или

или  условно «i» разряда также являются функциональными выходными связями канала для подачи аргумента в «i+1» разряда, при этом функциональные входные связи логической функции f1(&)-И являются функциональными входными связями канала для приема аргумента промежуточной суммы

условно «i» разряда также являются функциональными выходными связями канала для подачи аргумента в «i+1» разряда, при этом функциональные входные связи логической функции f1(&)-И являются функциональными входными связями канала для приема аргумента промежуточной суммы  или

или  условно «i» разряда и аргумента промежуточной суммы

условно «i» разряда и аргумента промежуточной суммы  или

или  условно «i-1» разряда, при этом функциональные входные связи логической функции f4(&)-И являются функциональными входными связями канала для приема аргументов промежуточной суммы

условно «i-1» разряда, при этом функциональные входные связи логической функции f4(&)-И являются функциональными входными связями канала для приема аргументов промежуточной суммы  или

или  условно «i» разряда, для приема аргументов промежуточной суммы с измененным уровнем аналогового сигнала

условно «i» разряда, для приема аргументов промежуточной суммы с измененным уровнем аналогового сигнала  или

или  условно «i-1» разряда и аргументов промежуточной суммы

условно «i-1» разряда и аргументов промежуточной суммы  или

или  условно «i-2» разряда, а функциональные входные связи логической функции f3(&)-И являются функциональными входными связями канала для приема аргументов промежуточной суммы

условно «i-2» разряда, а функциональные входные связи логической функции f3(&)-И являются функциональными входными связями канала для приема аргументов промежуточной суммы  или

или  условно «i» разряда и аргументов промежуточной суммы с измененным уровнем аналогового сигнала

условно «i» разряда и аргументов промежуточной суммы с измененным уровнем аналогового сигнала  или

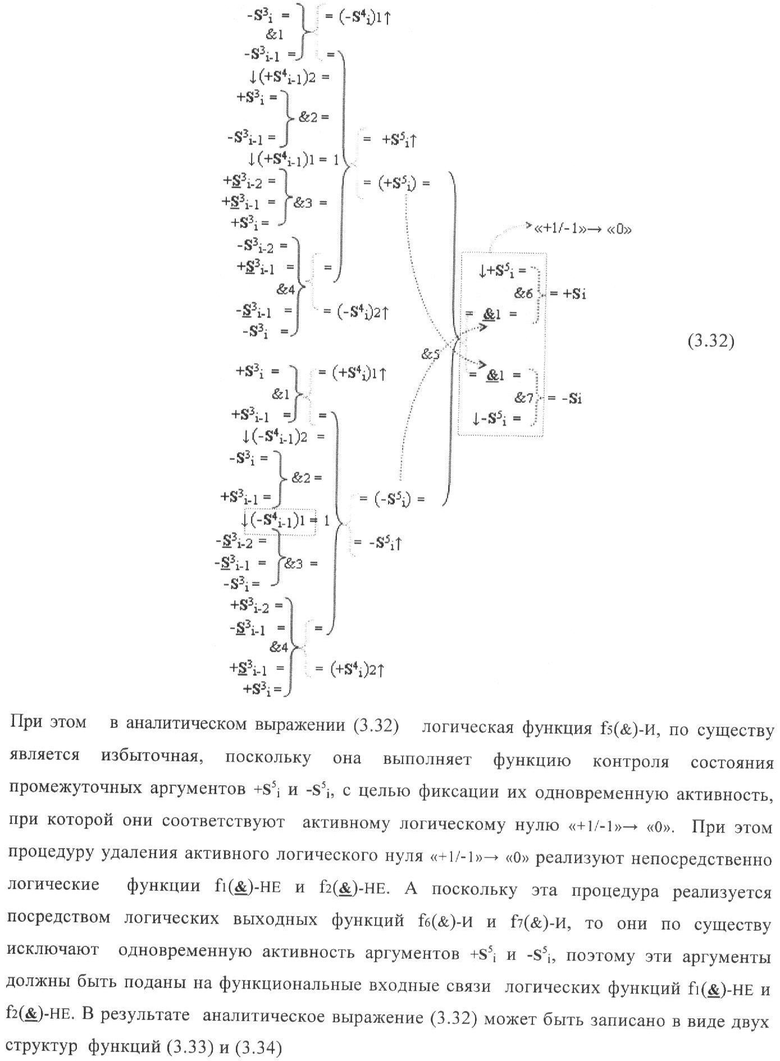

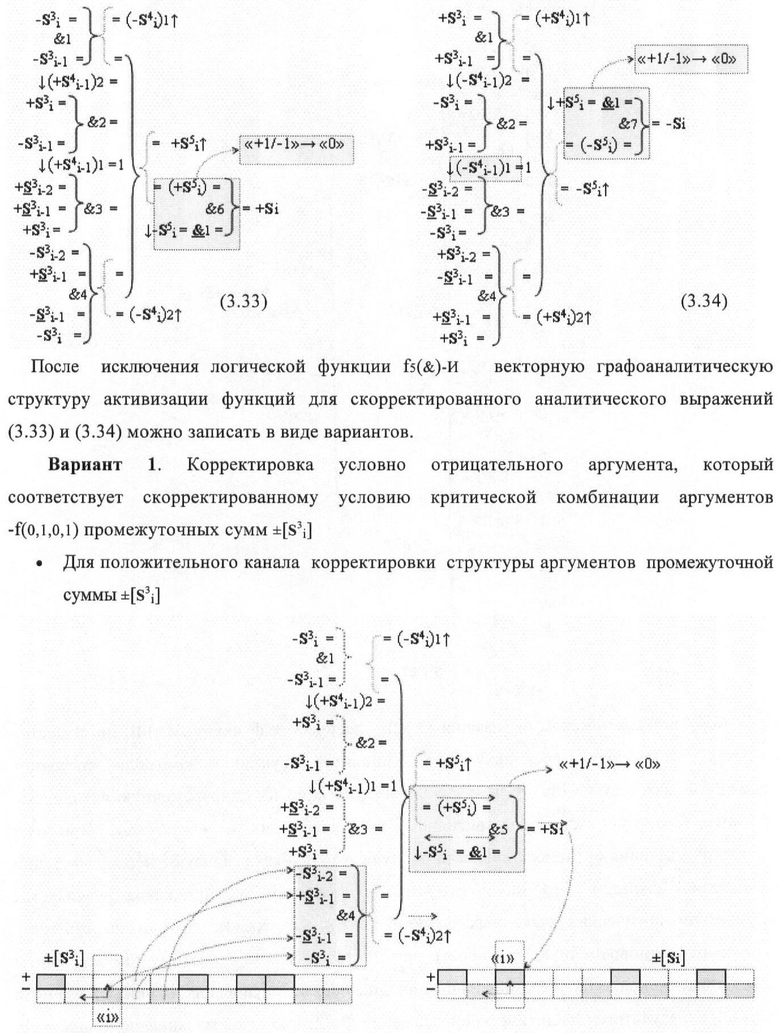

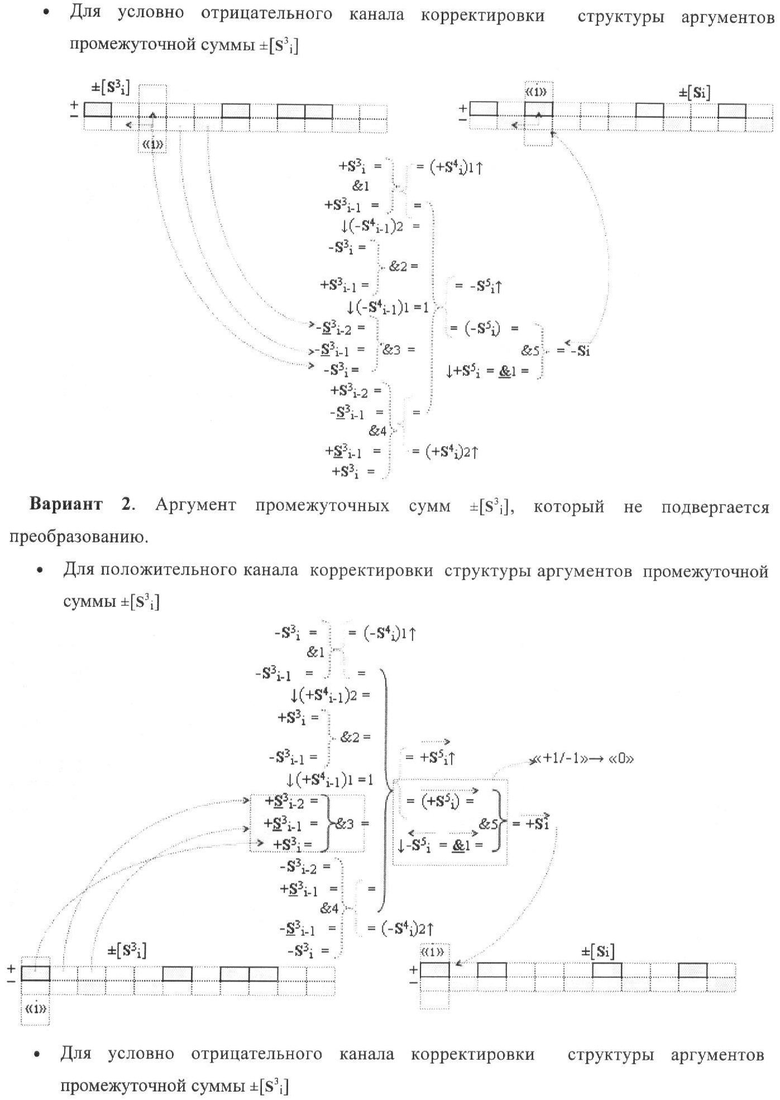

или  условно «i-1» разряда, отличающаяся тем, что в условно «i» разряда каждого канала введена логическая функция f2(&)-И, которая формирует преобразованный аргумент

условно «i-1» разряда, отличающаяся тем, что в условно «i» разряда каждого канала введена логическая функция f2(&)-И, которая формирует преобразованный аргумент  или

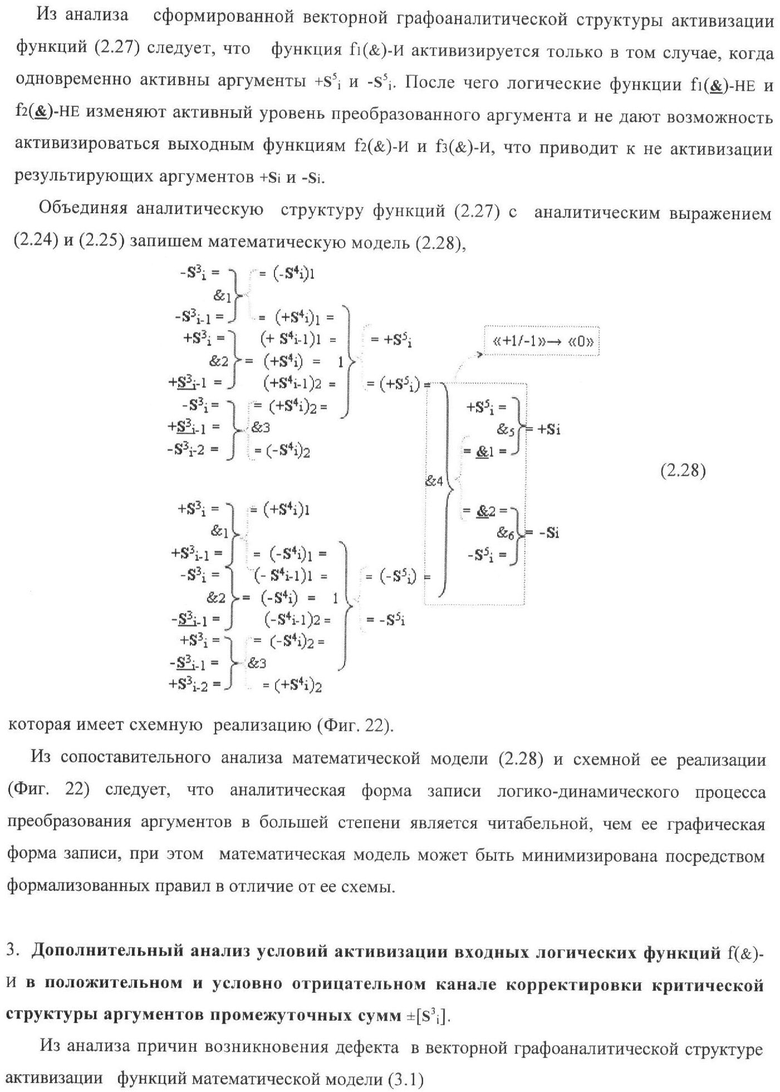

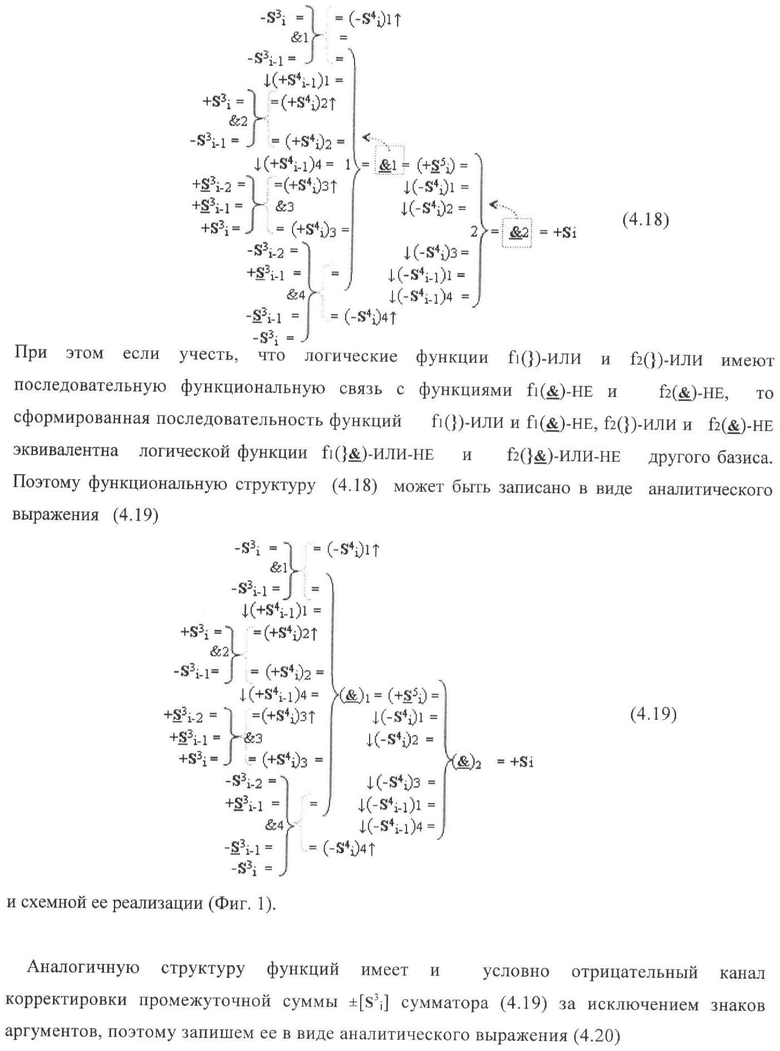

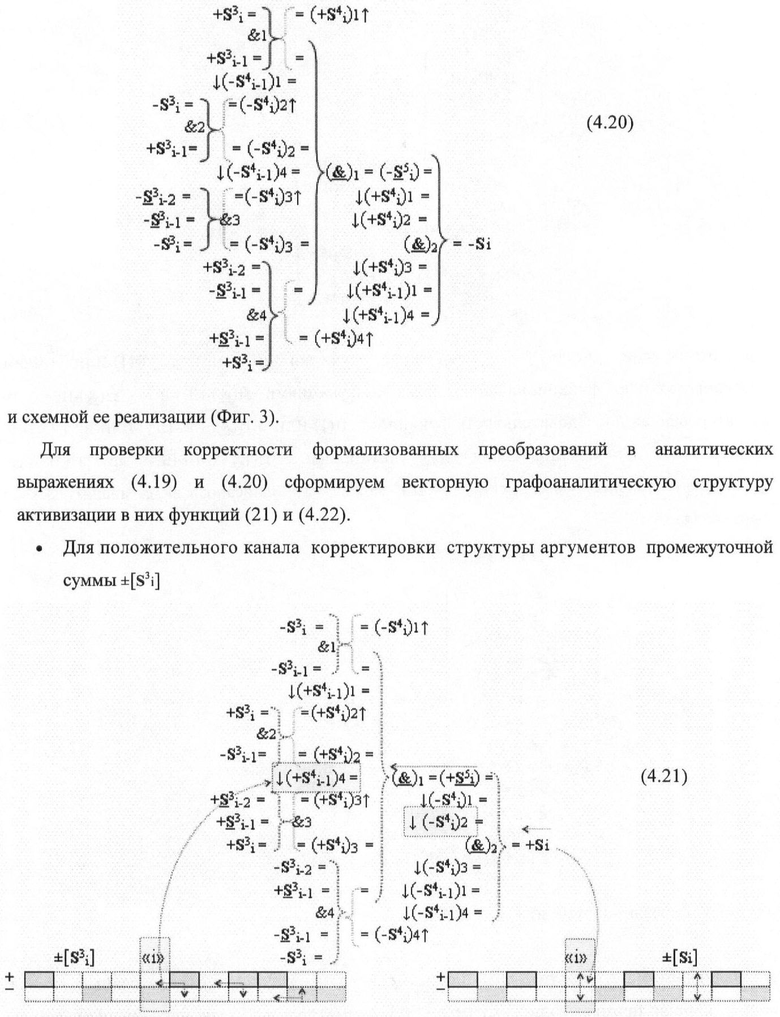

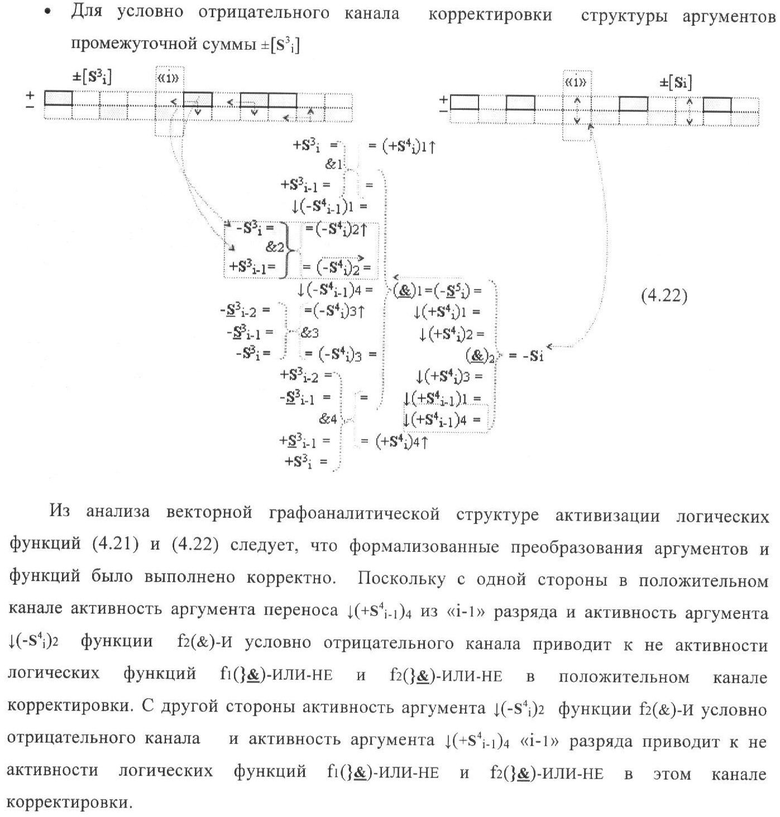

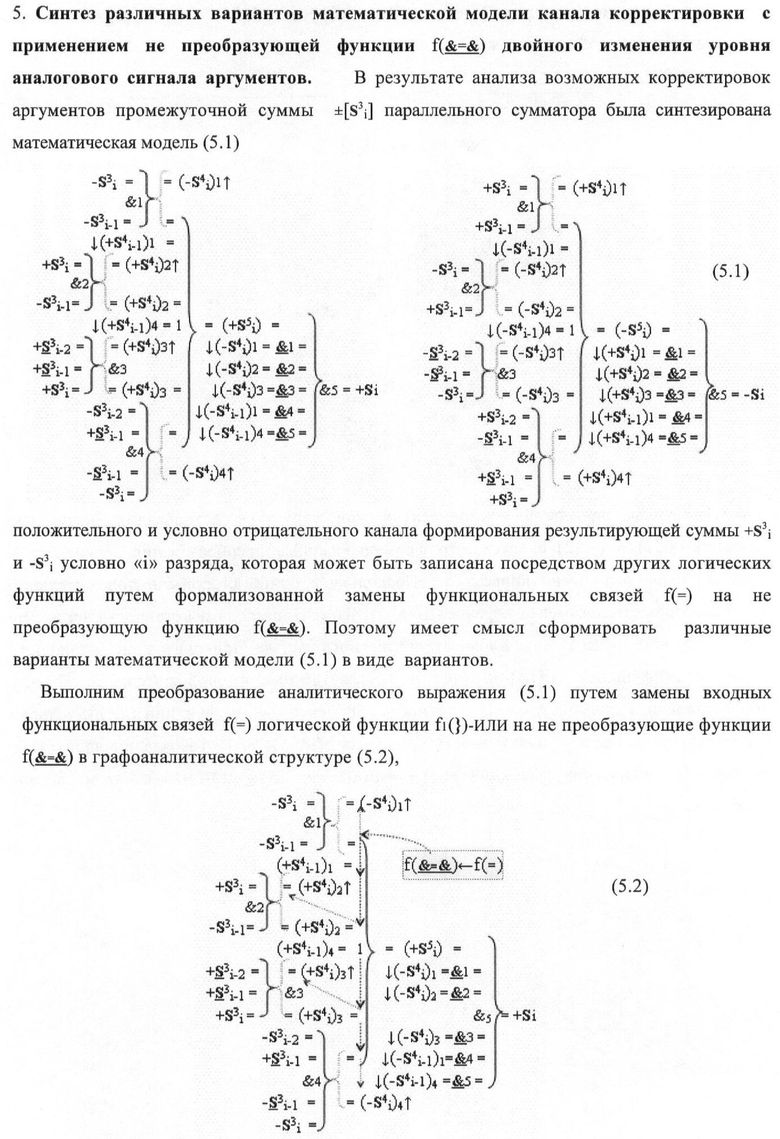

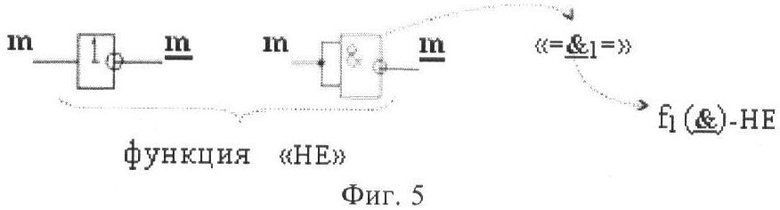

или  логическая функция f1(}&)-ИЛИ-НЕ и логическая функция f2(}&)-ИЛИ-НЕ, которая формирует выходной аргумент результирующей суммы +Si или -Si, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

логическая функция f1(}&)-ИЛИ-НЕ и логическая функция f2(}&)-ИЛИ-НЕ, которая формирует выходной аргумент результирующей суммы +Si или -Si, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

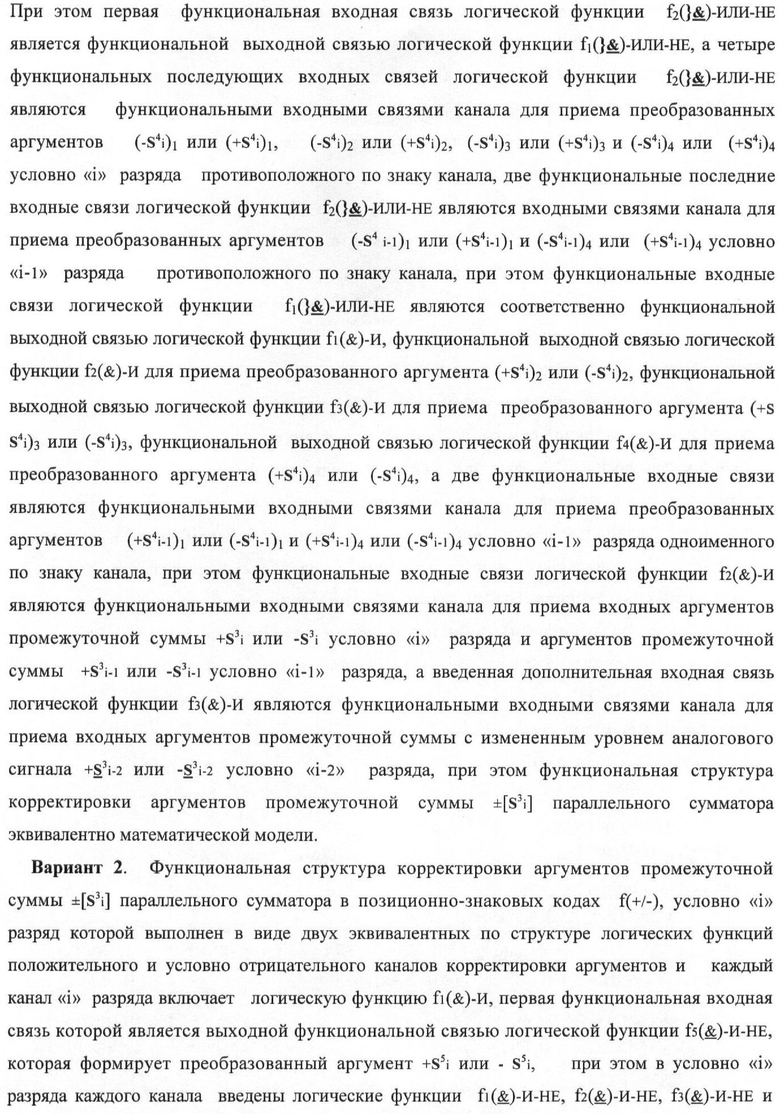

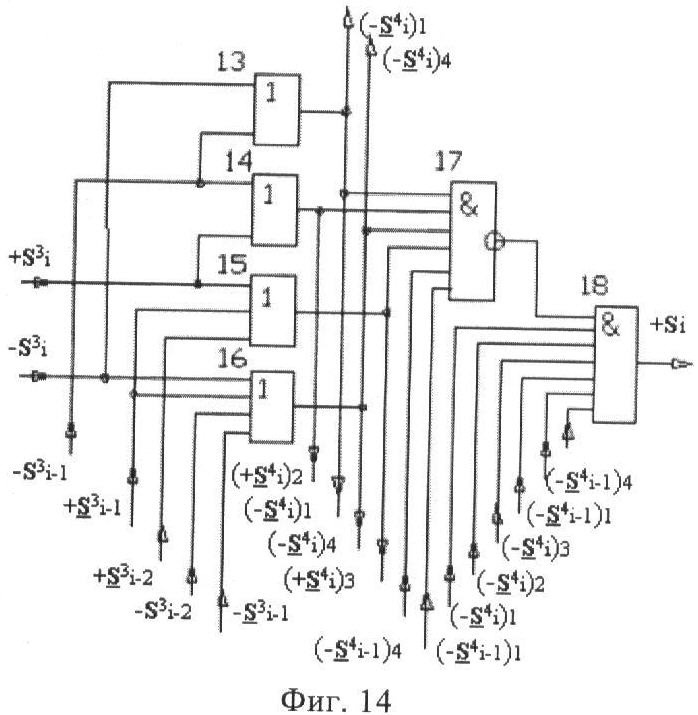

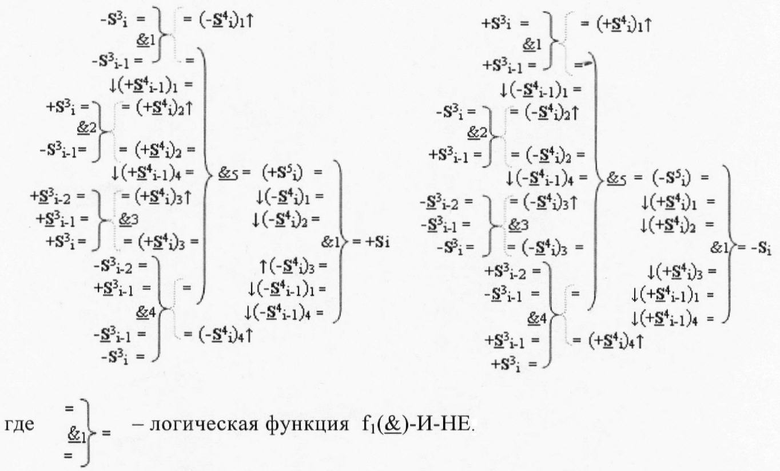

2. Функциональная структура корректировки аргументов промежуточной суммы ±[S3i] параллельного сумматора в позиционно-знаковых кодах f(+/-), условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов корректировки аргументов и каждый канал «i» разряда включает логическую функцию f1(&)-И, первая функциональная входная связь которой является выходной функциональной связью логической функции f5(&)-И-НЕ, которая формирует преобразованный аргумент  или

или  отличающаяся тем, что в условно «i» разряда каждого канала введены логические функции f1(&)-И-НЕ, f2(&)-И-НЕ, f3(&)-И-НЕ и f4(&)-И-НЕ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

отличающаяся тем, что в условно «i» разряда каждого канала введены логические функции f1(&)-И-НЕ, f2(&)-И-НЕ, f3(&)-И-НЕ и f4(&)-И-НЕ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

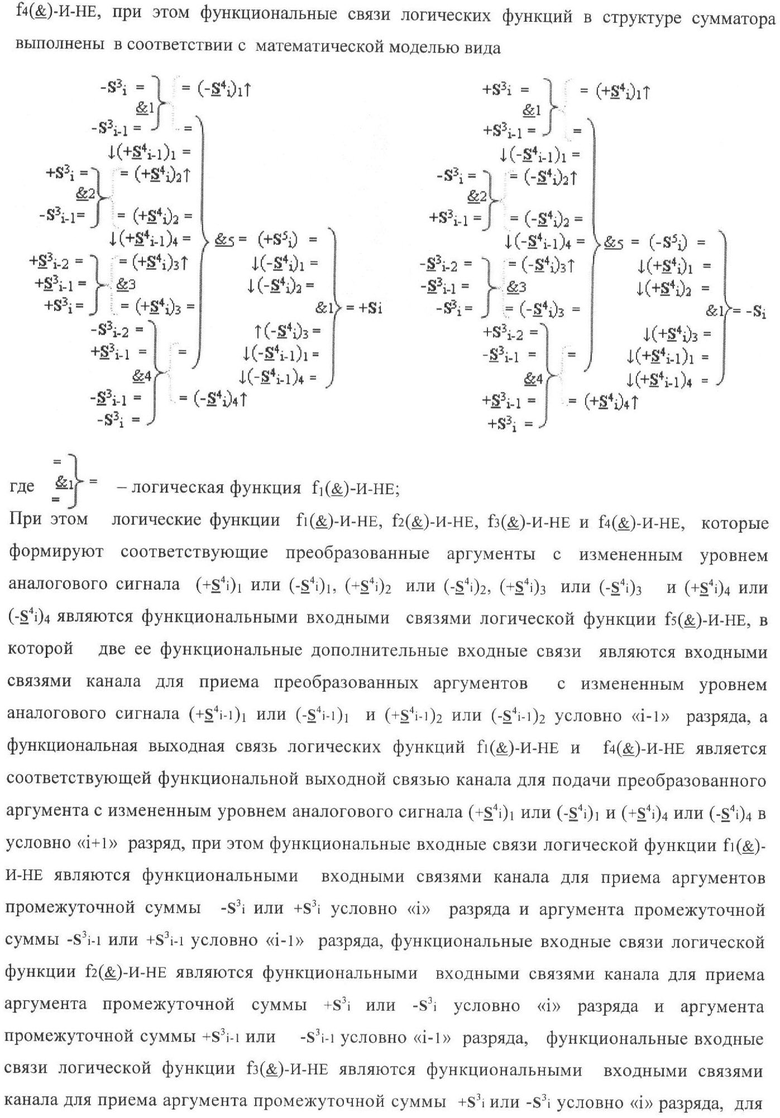

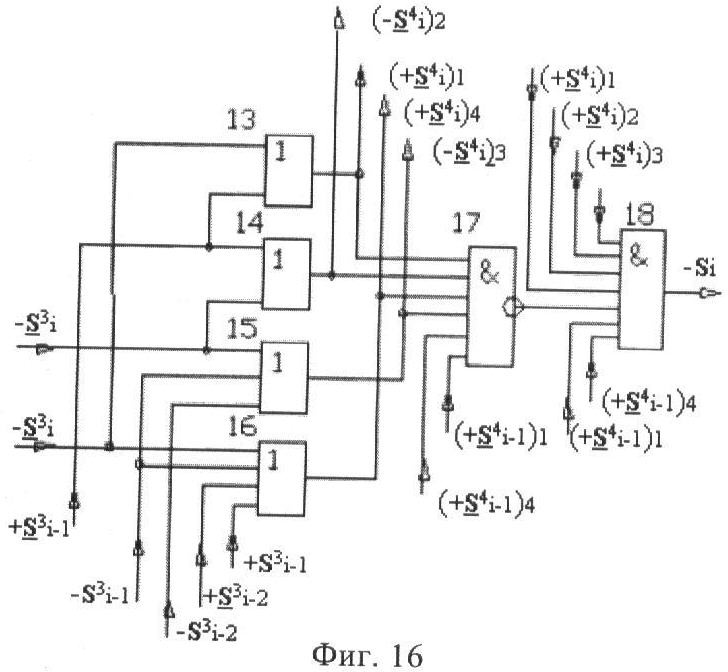

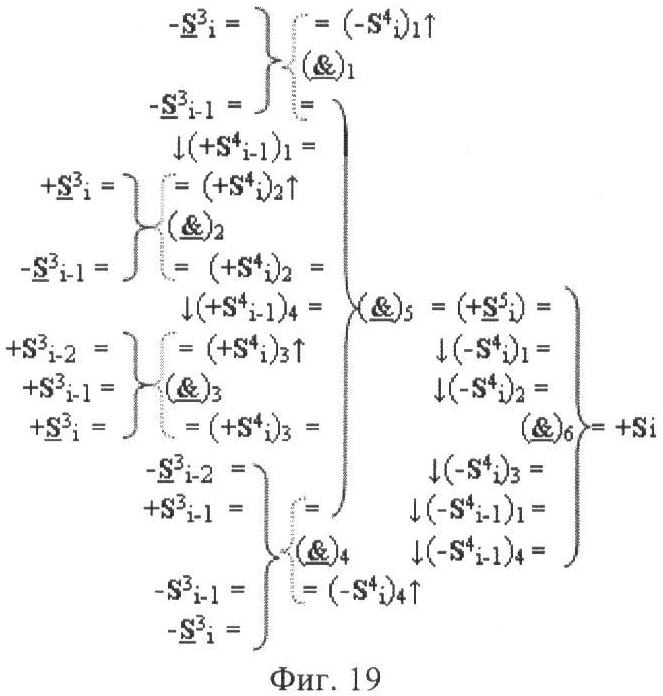

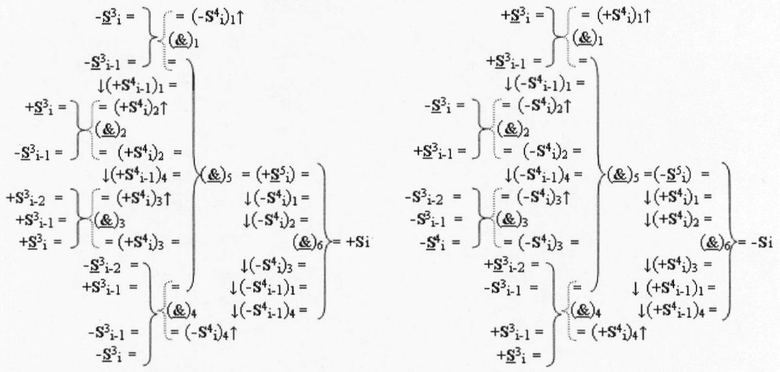

3. Функциональная структура корректировки аргументов промежуточной суммы ±[S3i] параллельного сумматора в позиционно-знаковых кодах f(+/-), условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов корректировки аргументов, и каждый канал «i» разряда включает логическую функцию f1(&)-И, первая функциональная входная связь которой является выходной функциональной связью логической функции f1(&)-И-HE, которая формирует преобразованный аргумент  или

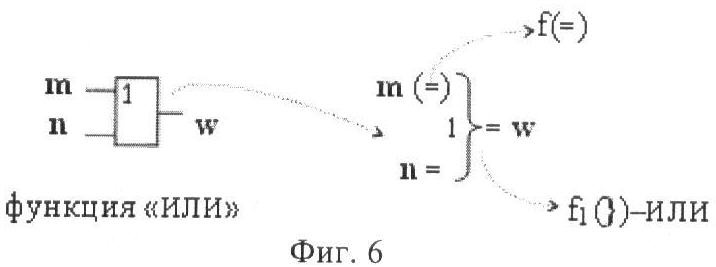

или  отличающаяся тем, что в условно «i» разряда каждого канала введены логические функции f1(})-ИЛИ, f2(})-ИЛИ, f3(})-ИЛИ и f4(})-ИЛИ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

отличающаяся тем, что в условно «i» разряда каждого канала введены логические функции f1(})-ИЛИ, f2(})-ИЛИ, f3(})-ИЛИ и f4(})-ИЛИ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

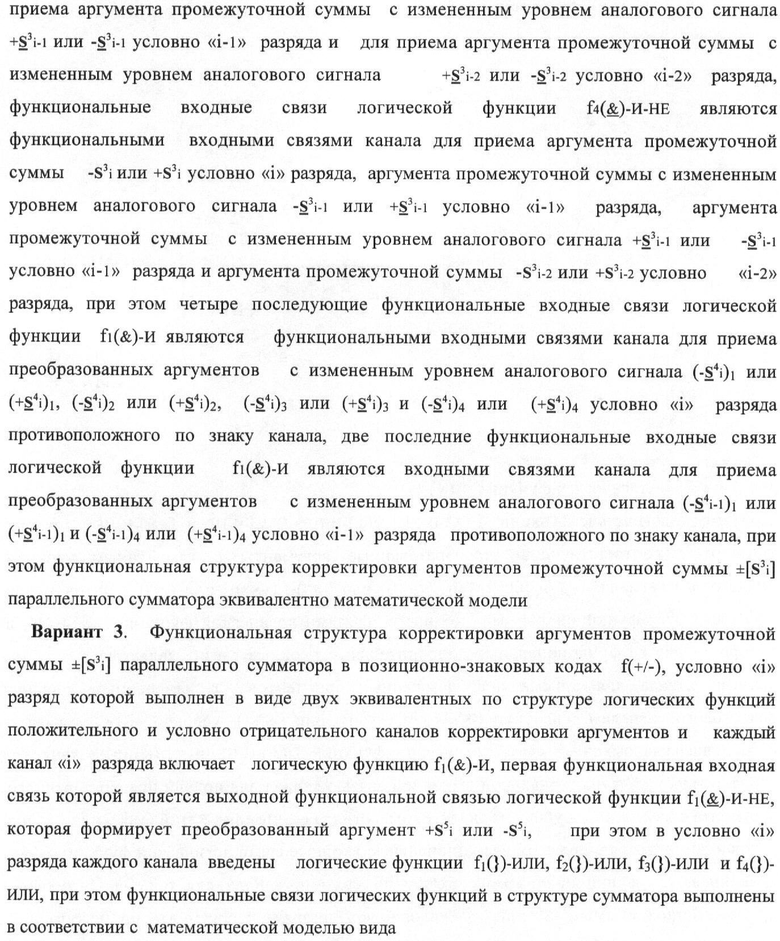

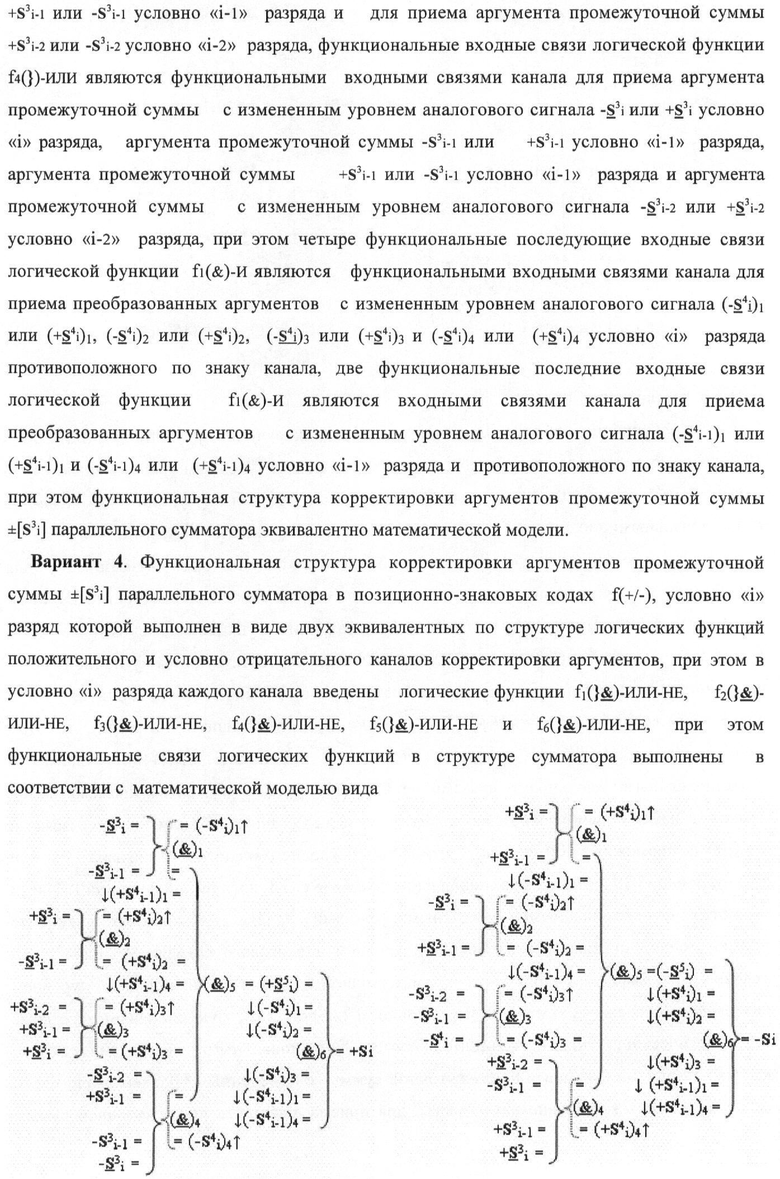

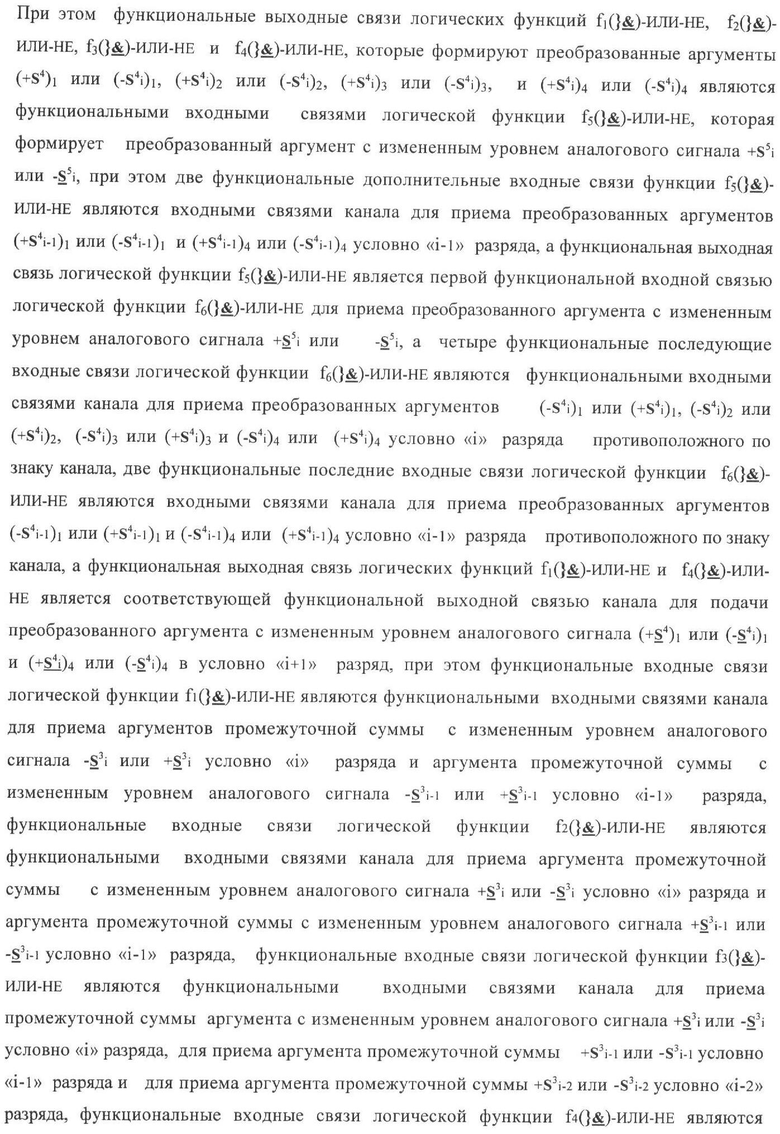

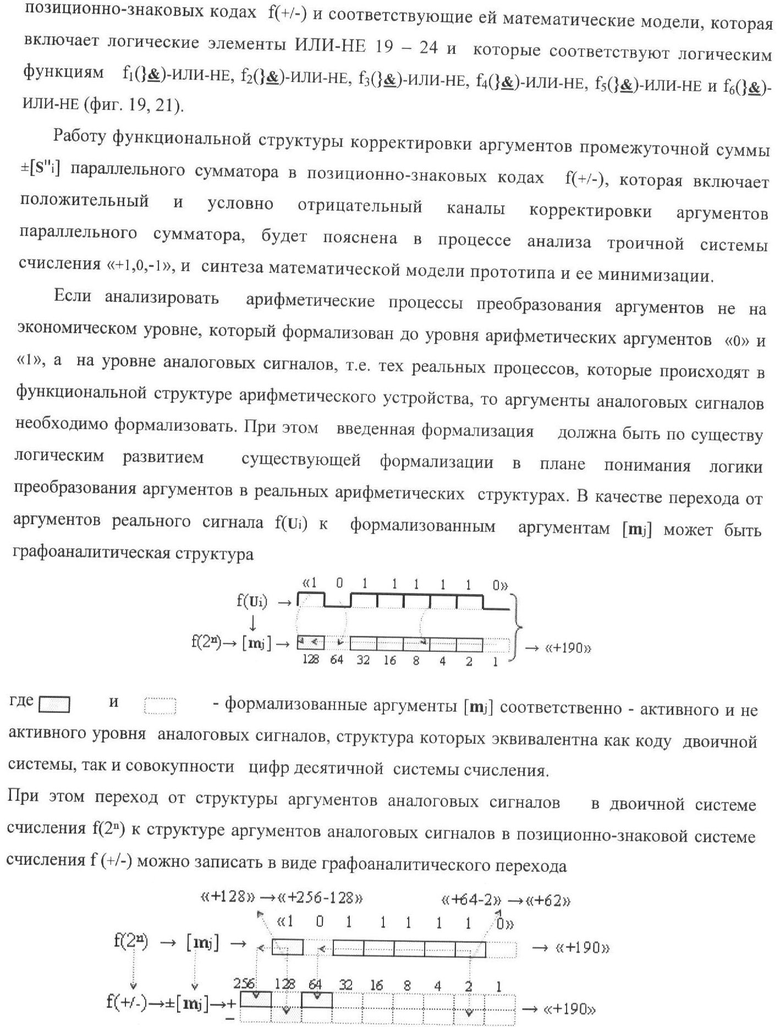

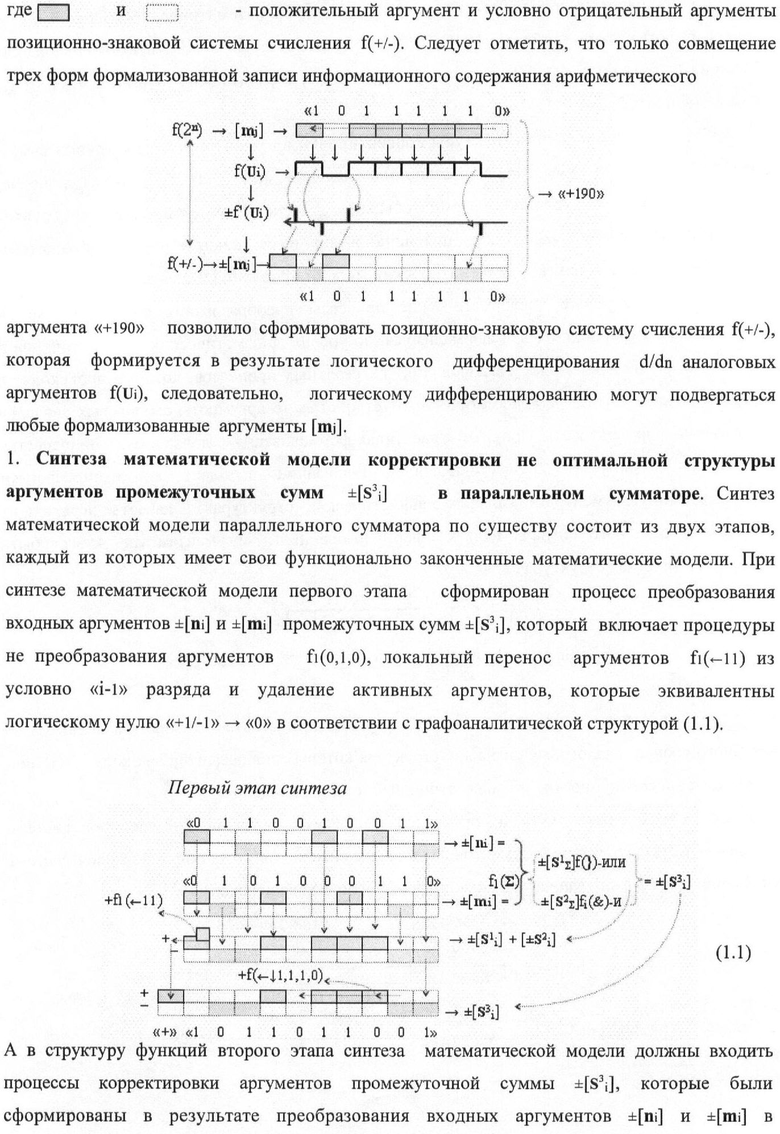

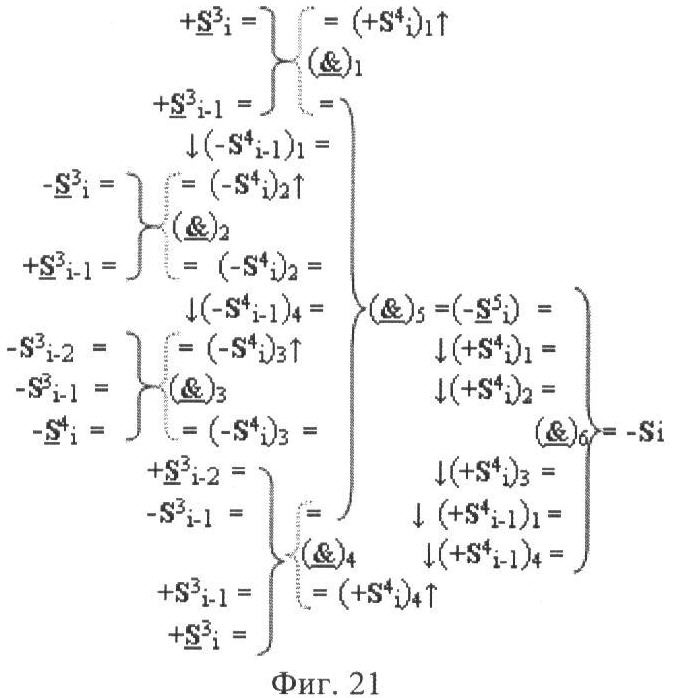

4. Функциональная структура корректировки аргументов промежуточной суммы ±[S3i] параллельного сумматора в позиционно-знаковых кодах f(+/-), условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов корректировки аргументов, отличающаяся тем, что в условно «i» разряда каждого канала введены логические функции f1(}&)-ИЛИ-НЕ, f2(}&)-ИЛИ-HE, f3(}&)-ИЛИ-HE, f4(}&)-ИЛИ-НЕ, f5(}&)-ИЛИ-НЕ и f6(}&)-ИЛИ-НЕ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

| Аппарат для отделения сатурационной грязи от сахарного сока | 1929 |

|

SU23363A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Устройство для параллельного сложения чисел, представленных в двоичной знакоразрядной системе счисления | 1989 |

|

SU1727120A1 |

| JP 62204332 A, 09.09.1987 | |||

| JP 63197227 A, 16.08.1988. | |||

Авторы

Даты

2010-01-10—Публикация

2007-12-17—Подача