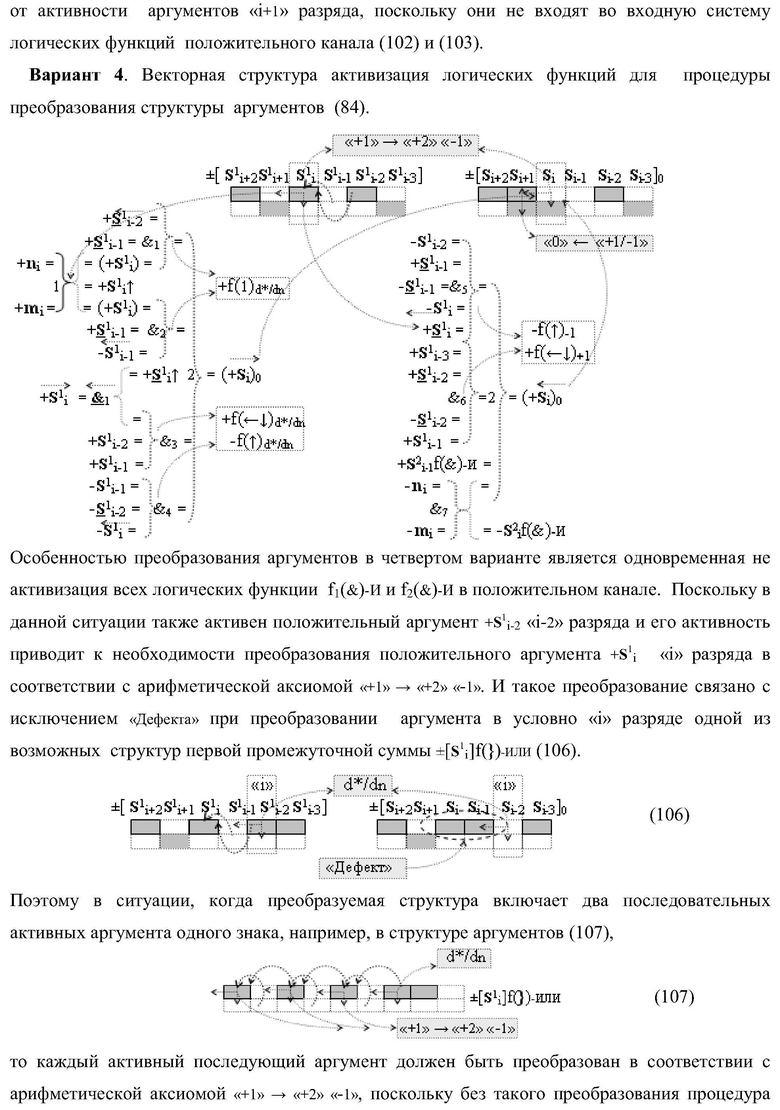

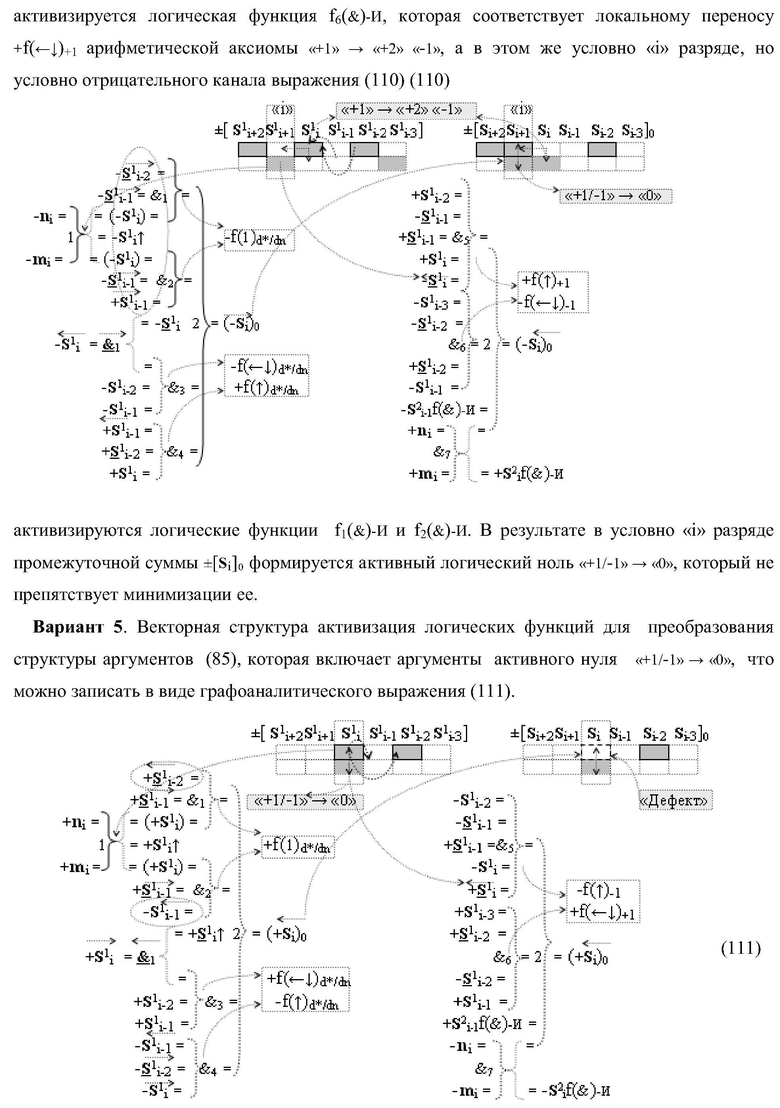

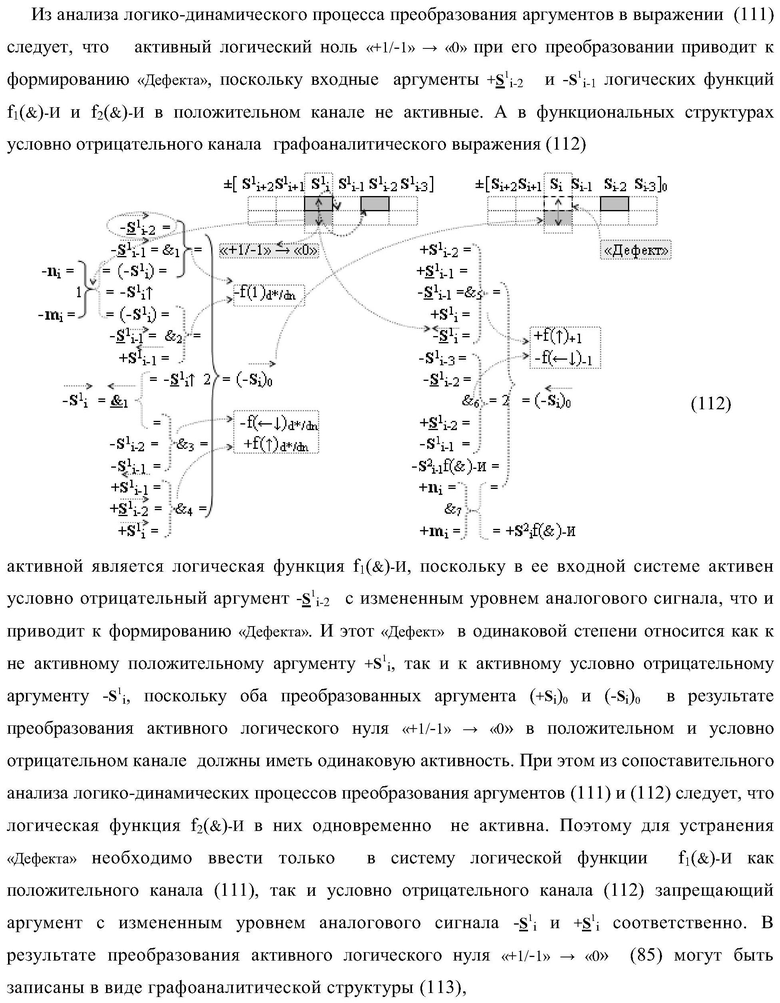

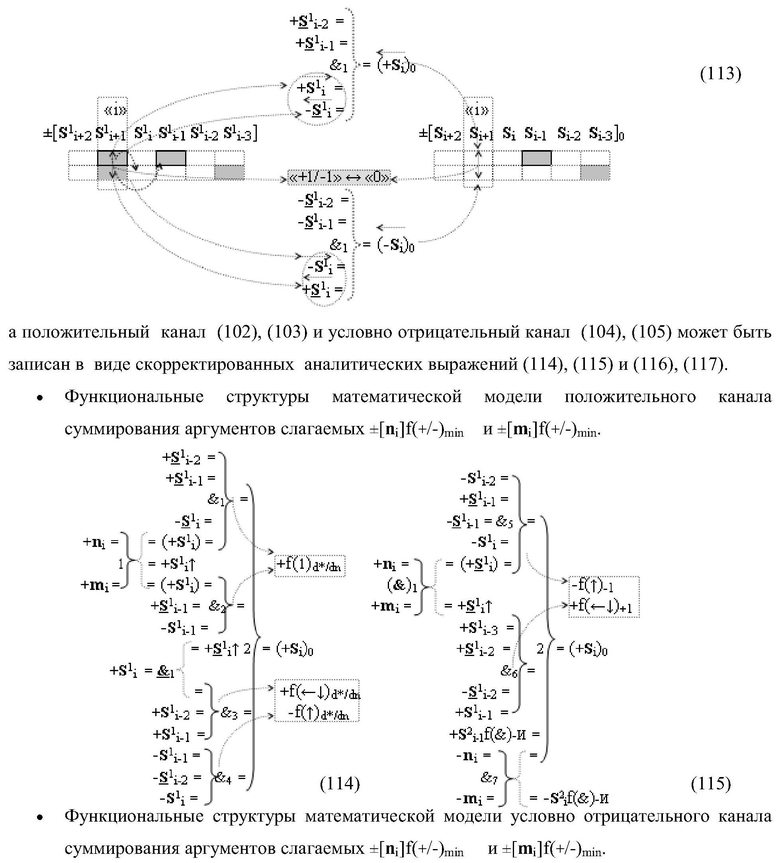

Текст описания приведен в факсимильном виде.

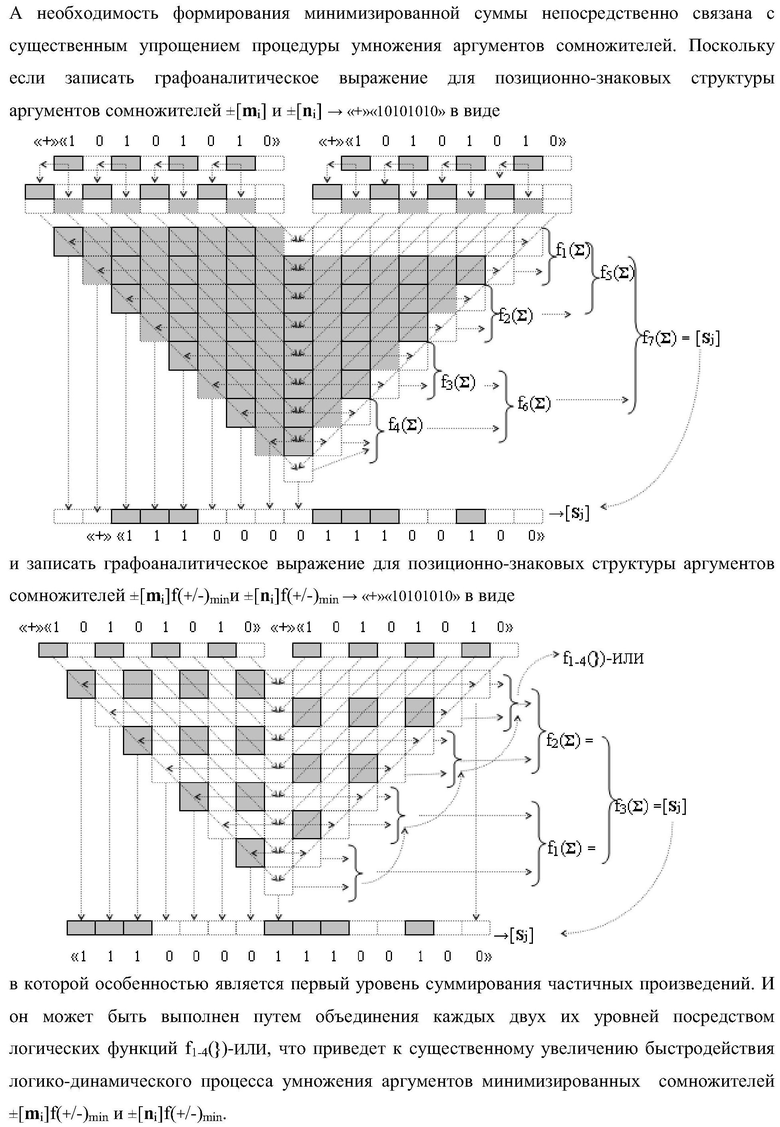

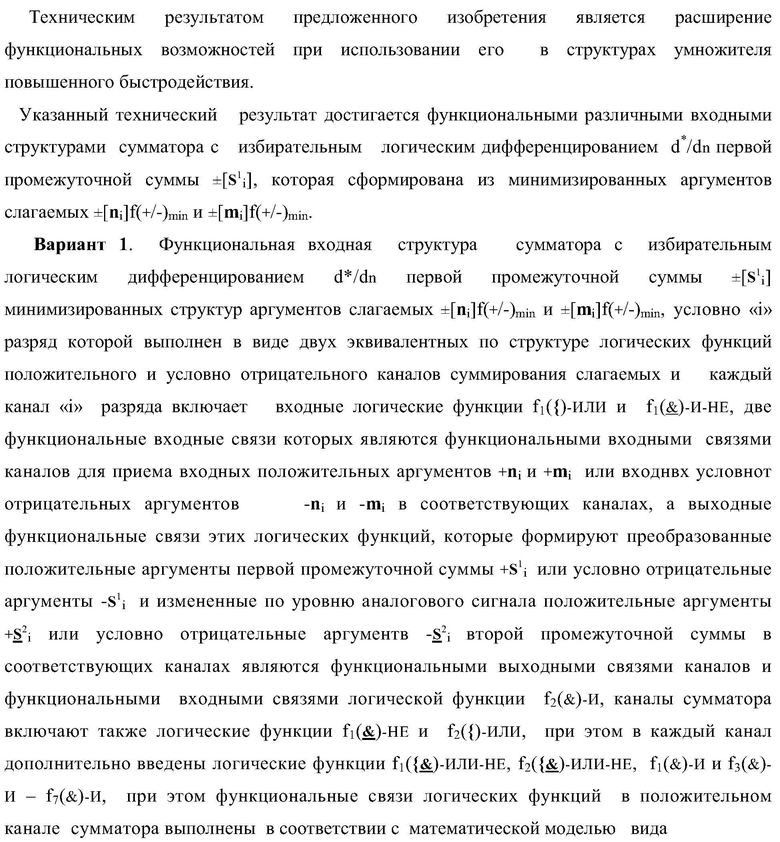

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств для выполнения арифметических операций суммирования и вычитания в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия. В одном из вариантов изобретения «i»-ый разряд функциональной структуры выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов суммирования, при этом каждый канал содержит элементы, реализующие логические функции И, ИЛИ, ИЛИ-НЕ, И-НЕ и НЕ. 4 н.п. ф-лы.

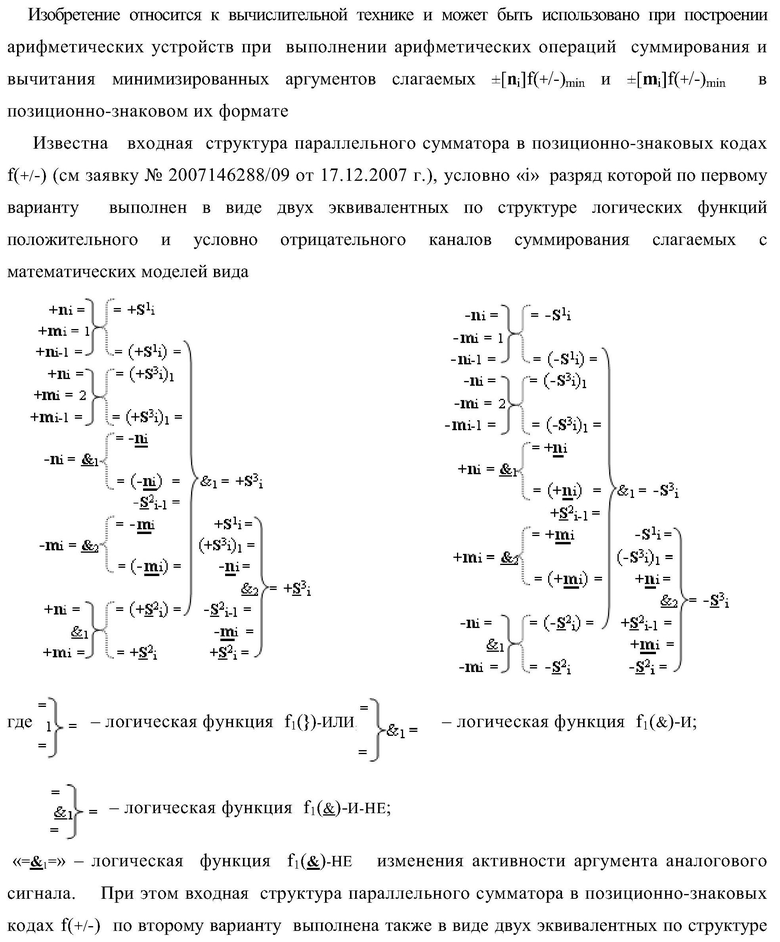

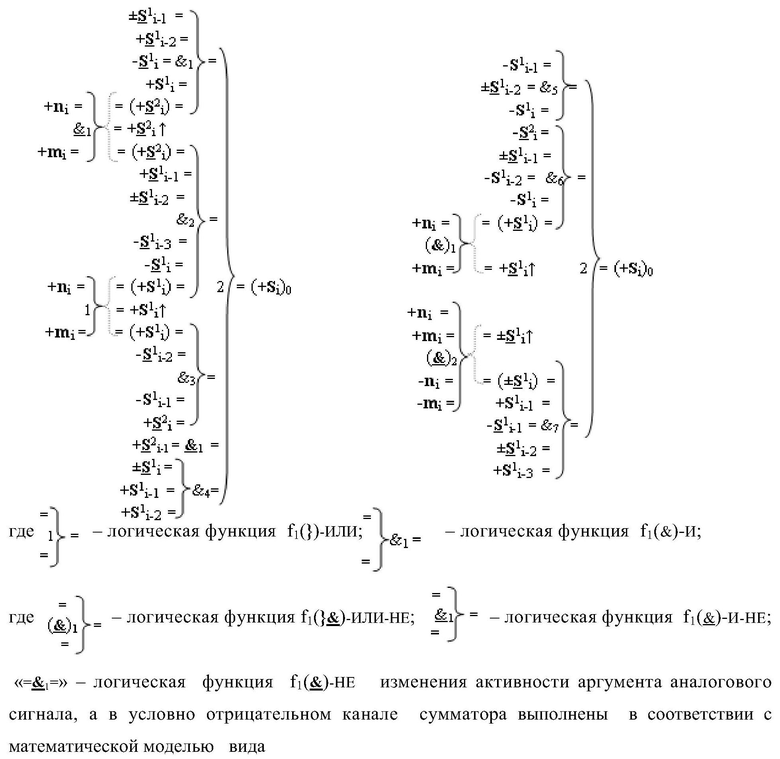

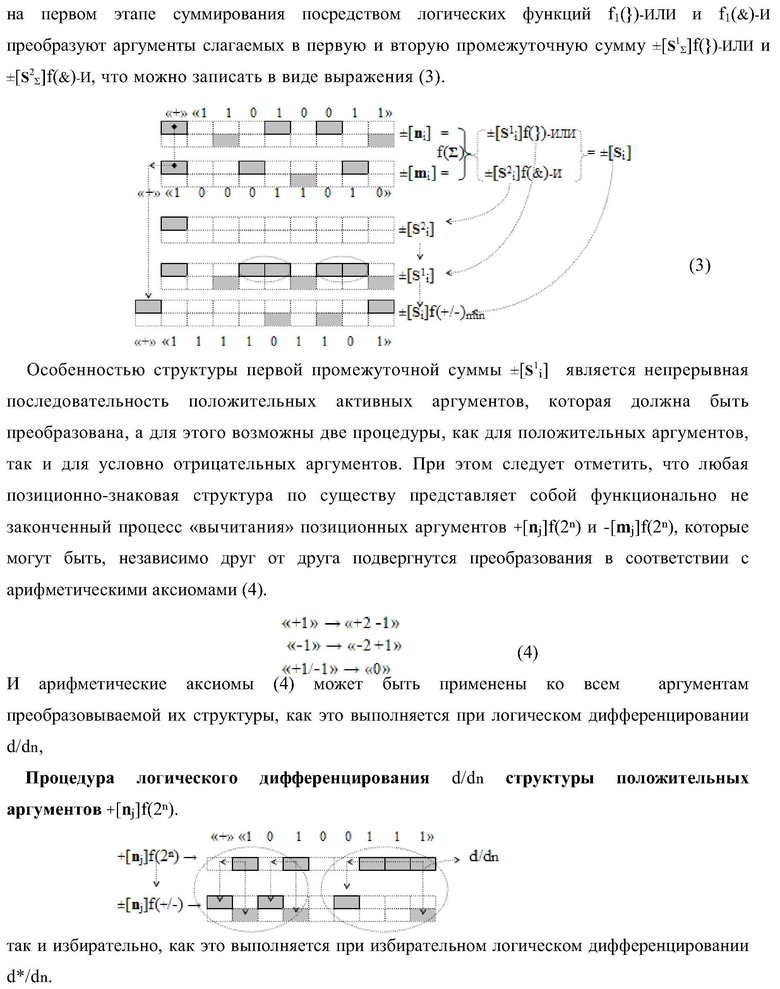

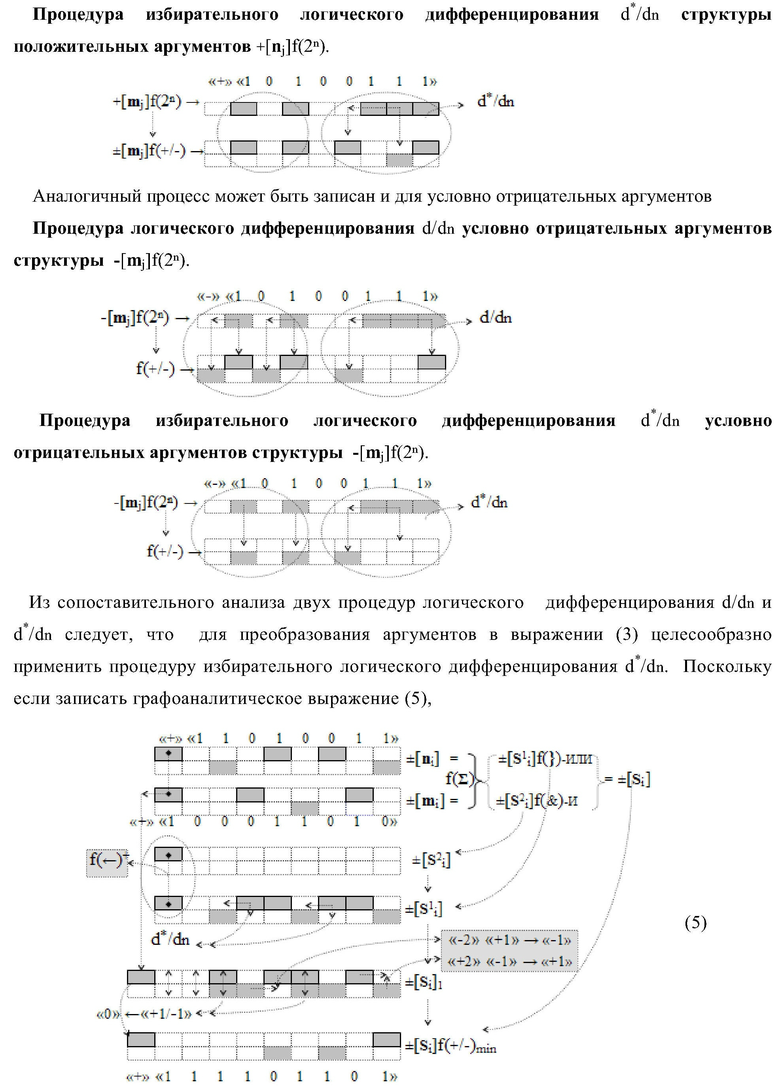

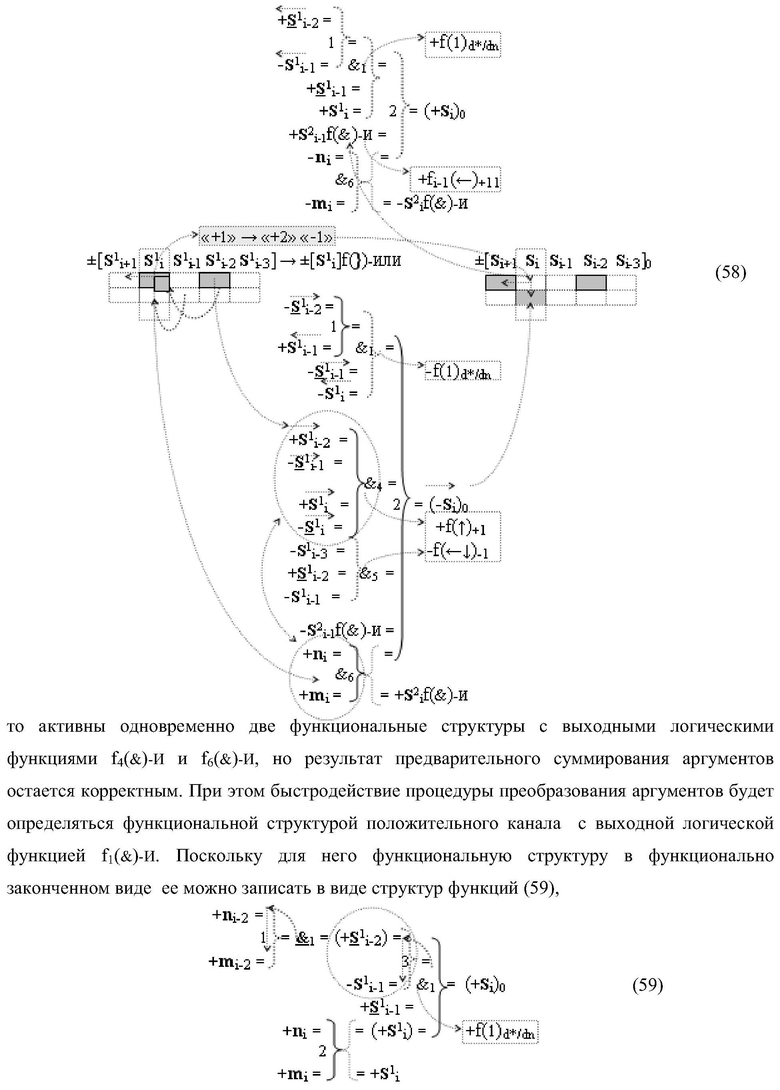

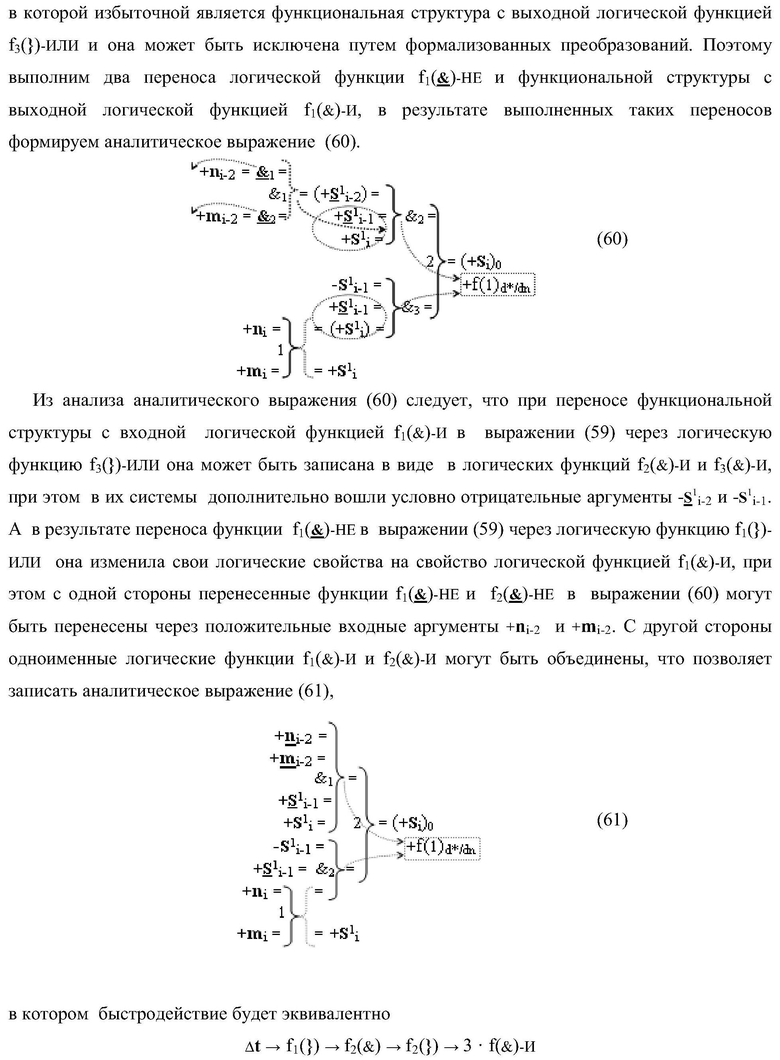

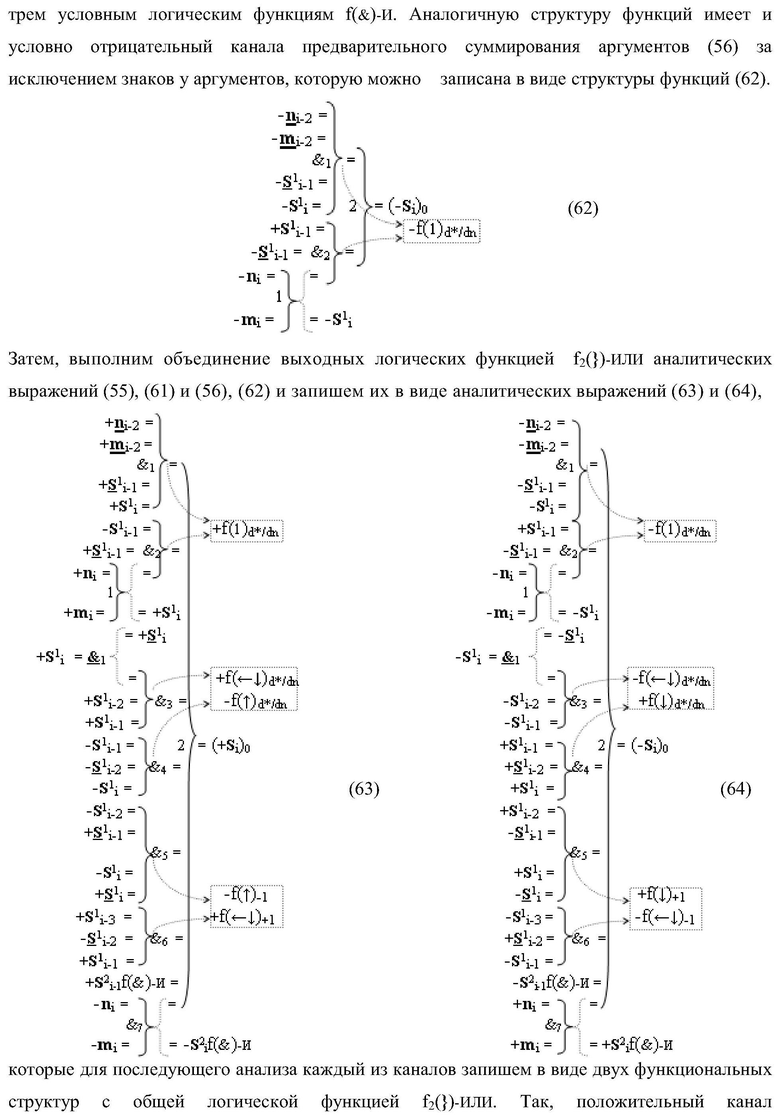

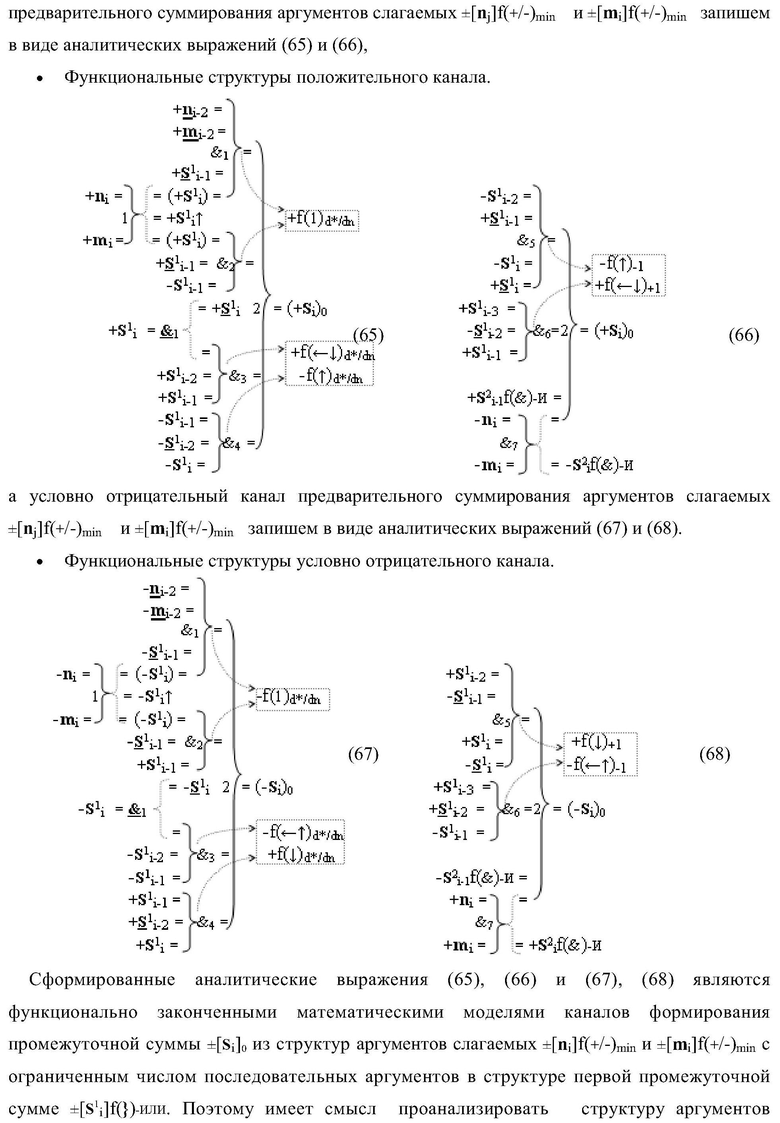

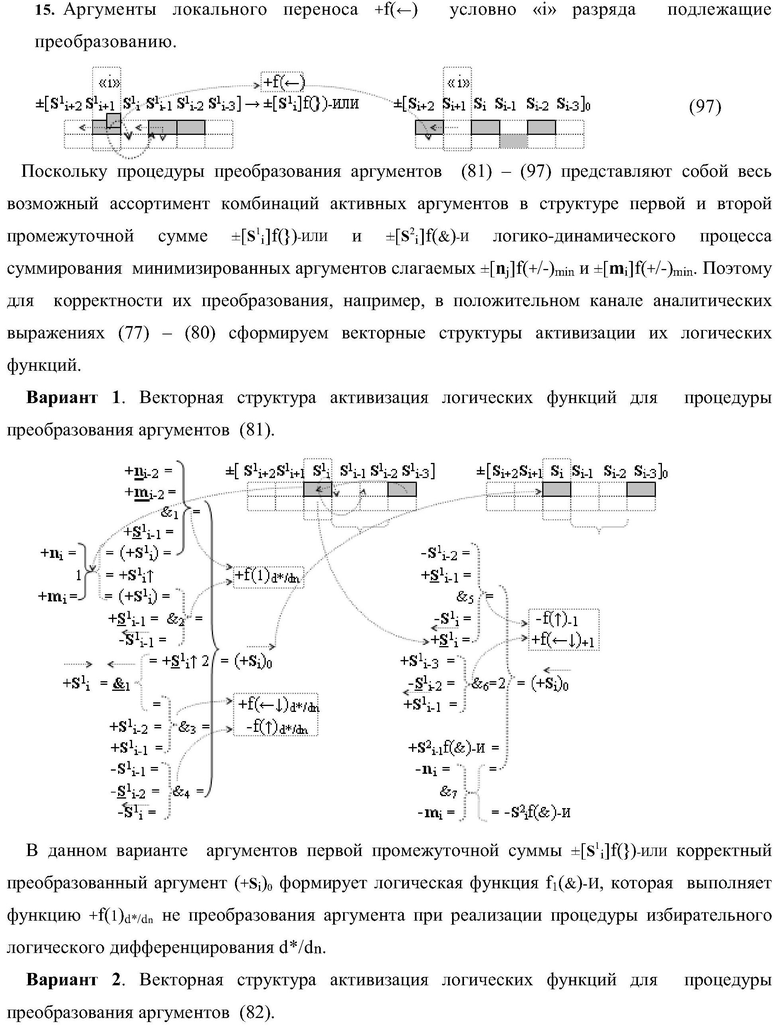

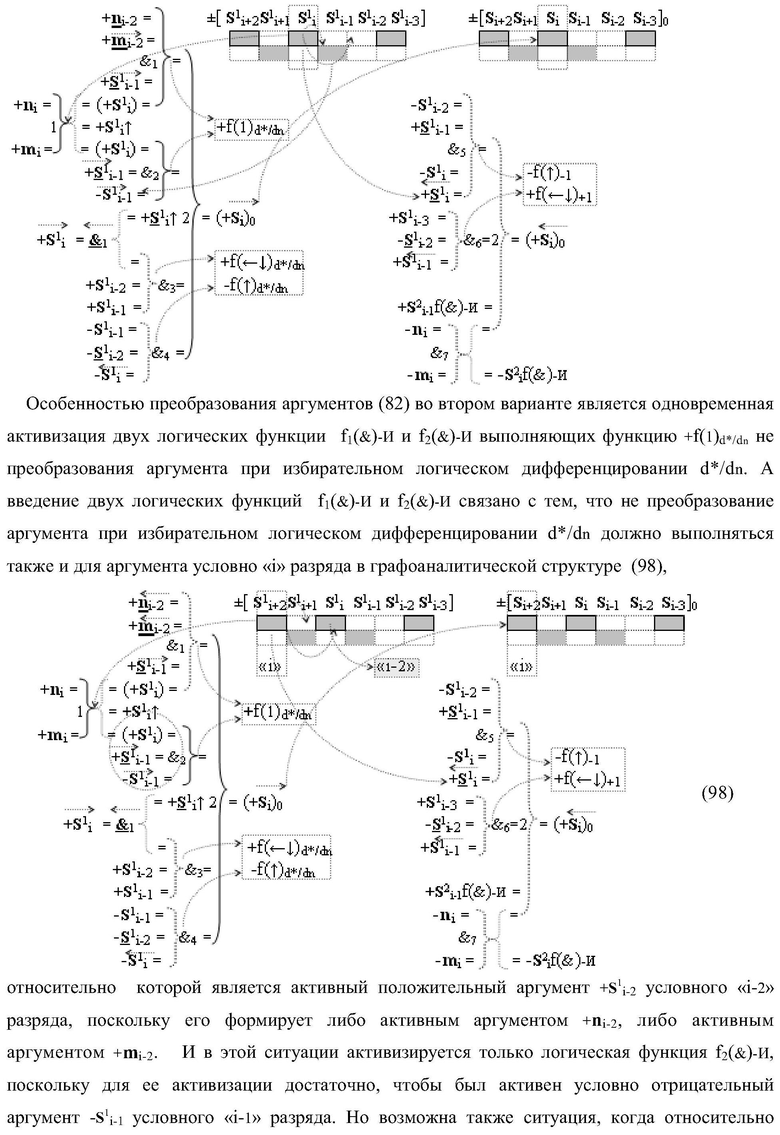

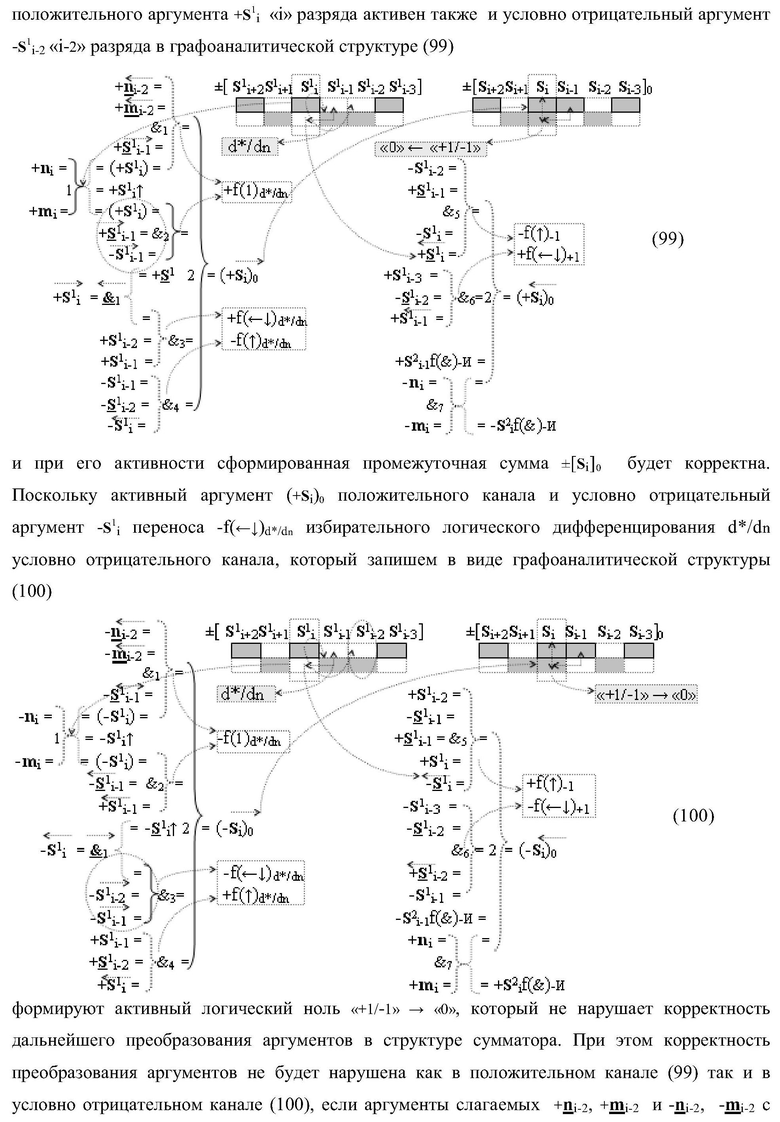

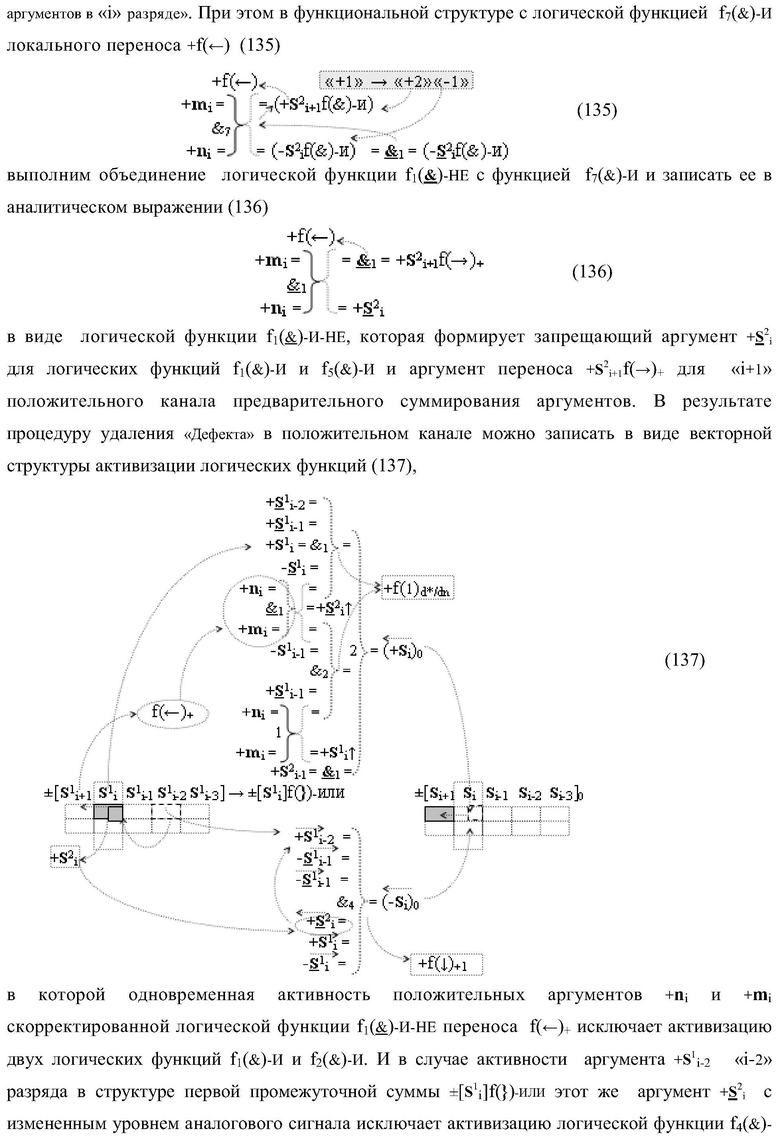

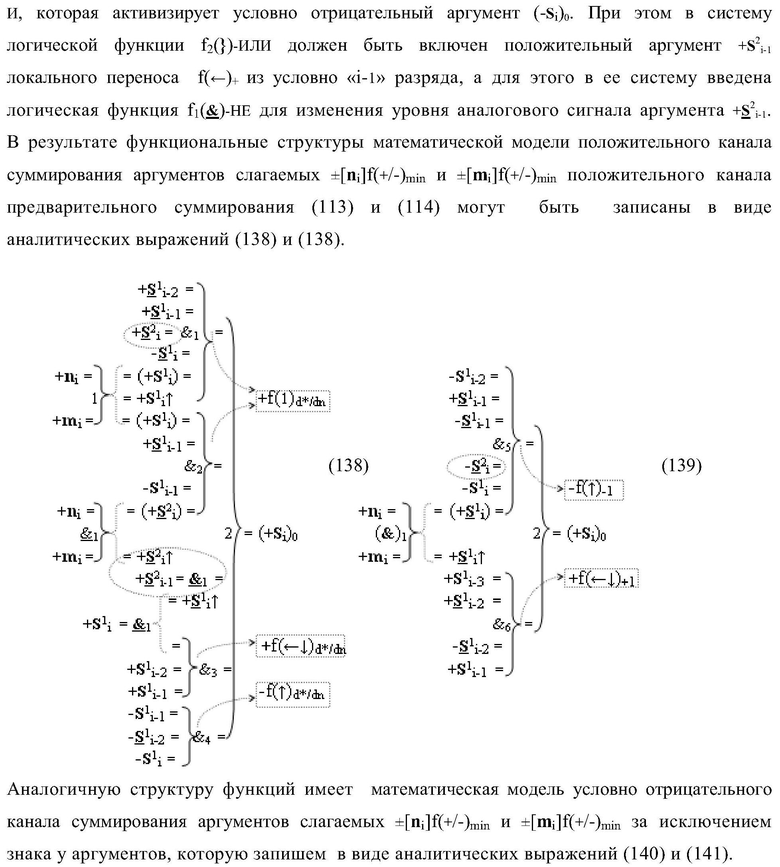

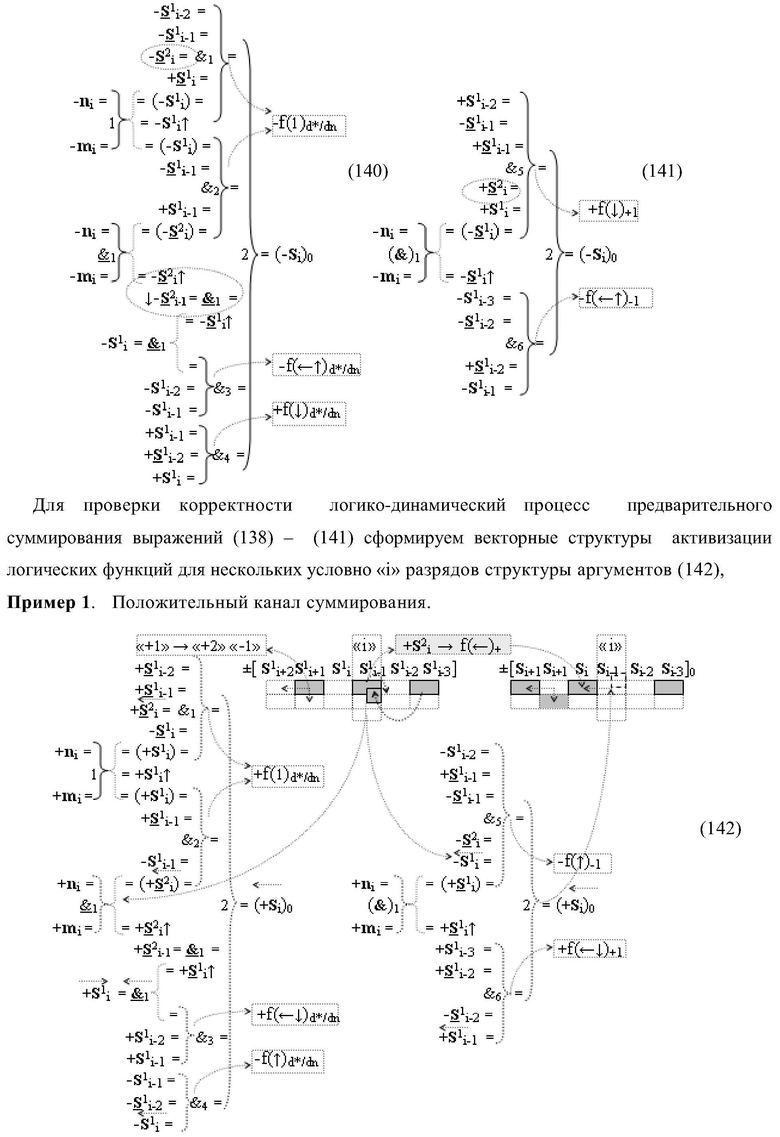

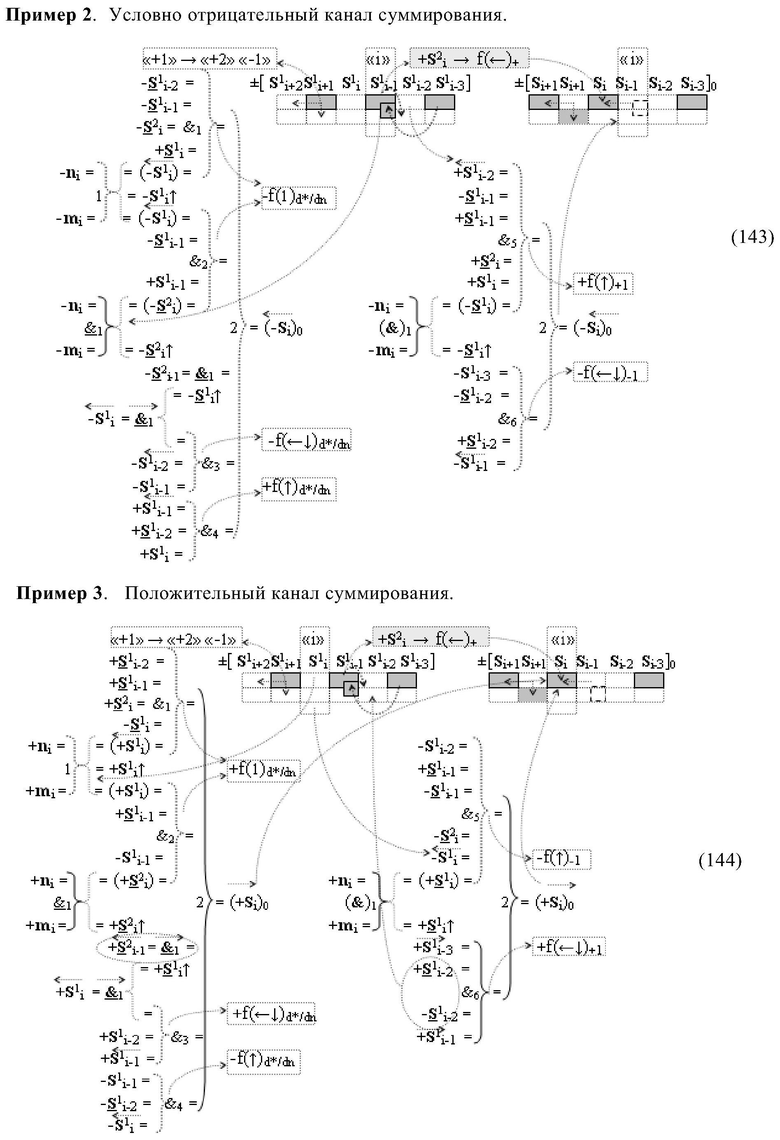

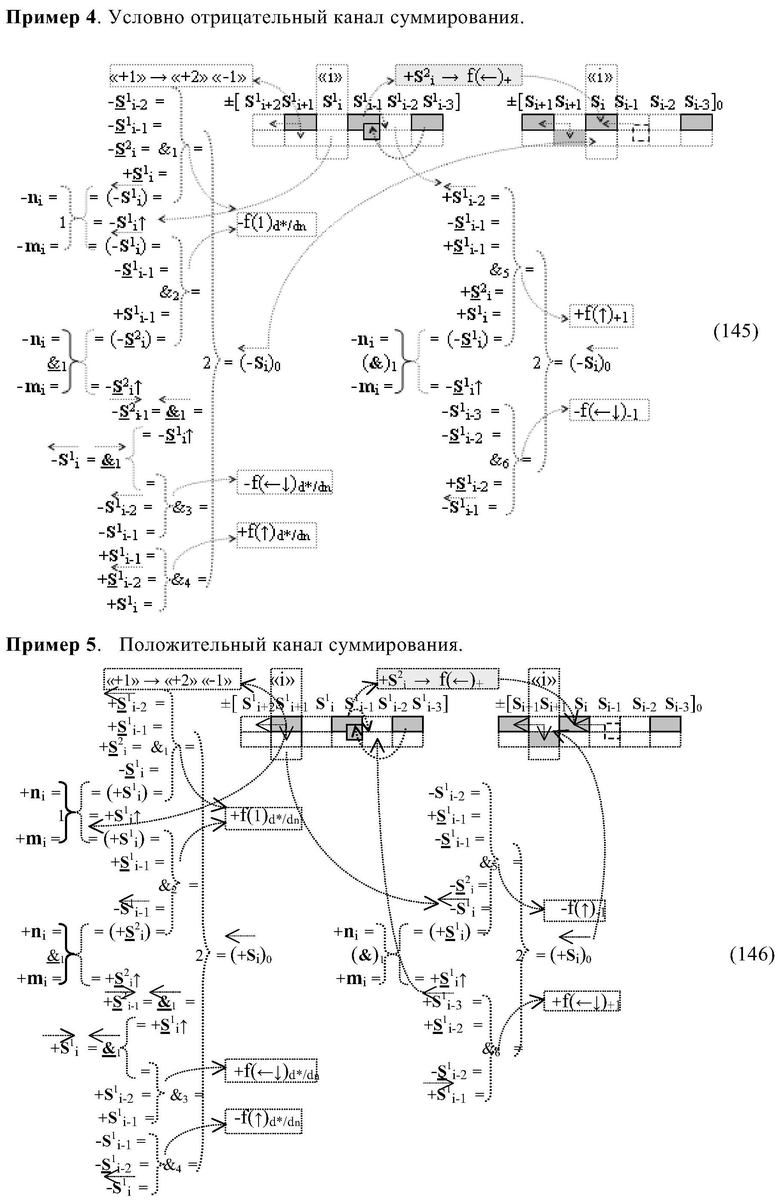

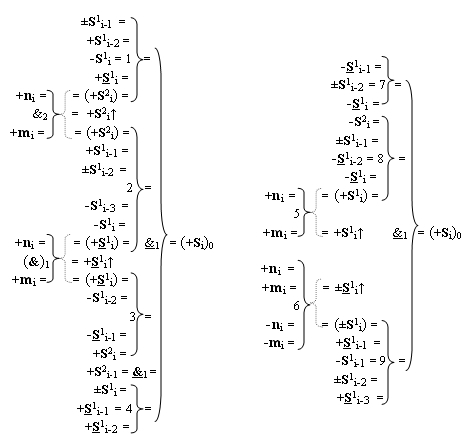

1. Функциональная входная структура сумматора с избирательным логическим дифференцированием d*/dn первой промежуточной суммы ±[S1 i] минимизированных структур аргументов слагаемых ±[ni]f(+/-)min и ±[mi]f(+/-)min, условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов суммирования слагаемых и каждый канал «i» разряда включает входные логические функции f1({)-ИЛИ и f1(&)-И-НЕ, две функциональные входные связи которых являются функциональными входными связями каналов для приема входных положительных аргументов +ni и +mi или входных условно отрицательных аргументов -ni и -mi в соответствующих каналах, а выходные функциональные связи этих логических функций, которые формируют преобразованные положительные аргументы первой промежуточной суммы +S1 i или условно отрицательные аргументы -S

1 i и измененные по уровню аналогового сигнала положительные аргументы +S

2 i или условно отрицательные аргументы -S

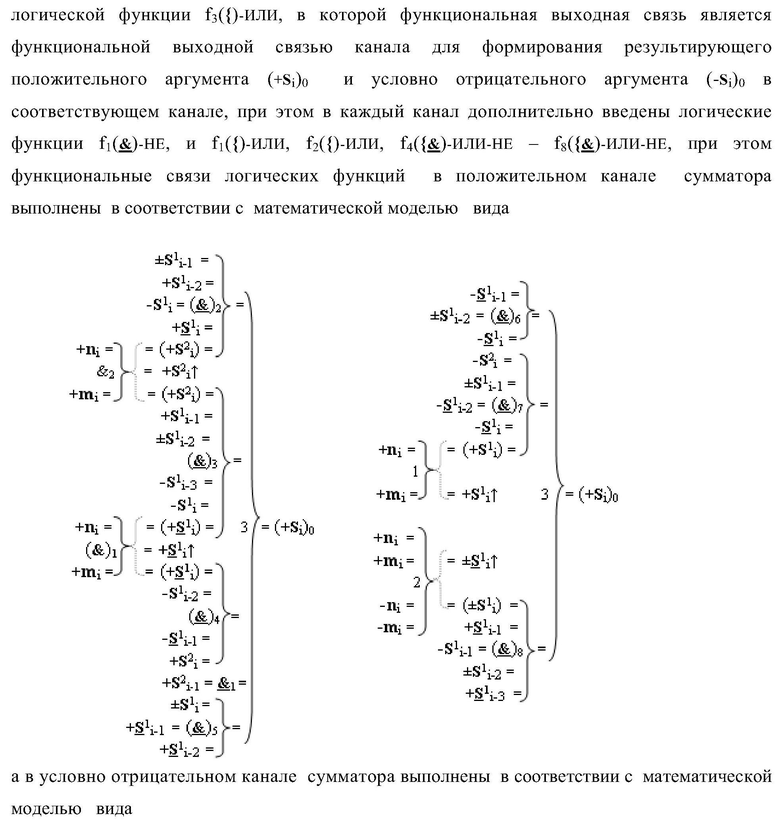

2 i второй промежуточной суммы в соответствующих каналах являются функциональными выходными связями каналов и функциональными входными связями логической функции f2(&)-И, каналы сумматора включают также логические функции f1(&)-НЕ и f2({)-ИЛИ, отличающаяся тем, что в каждый канал дополнительно введены логические функции f1({&)-ИЛИ-НЕ, f2({&)-ИЛИ-НЕ, f1(&)-И и f3(&)-И - f7(&)-И, при этом функциональные связи логических функций в положительном канале сумматора выполнены в соответствии с математической моделью вида

где  - логическая функция f1(})-ИЛИ;

- логическая функция f1(})-ИЛИ;  - логическая функция f1(&)-И;

- логическая функция f1(&)-И;

где  - логическая функция f1(}&)-ИЛИ-НЕ;

- логическая функция f1(}&)-ИЛИ-НЕ;  - логическая функция f1(&)-И-НЕ; «=&

1=» - логическая функция f1(&)-НЕ изменения активности аргумента аналогового сигнала, а в условно отрицательном канале сумматора выполнены в соответствии с математической моделью вида

- логическая функция f1(&)-И-НЕ; «=&

1=» - логическая функция f1(&)-НЕ изменения активности аргумента аналогового сигнала, а в условно отрицательном канале сумматора выполнены в соответствии с математической моделью вида

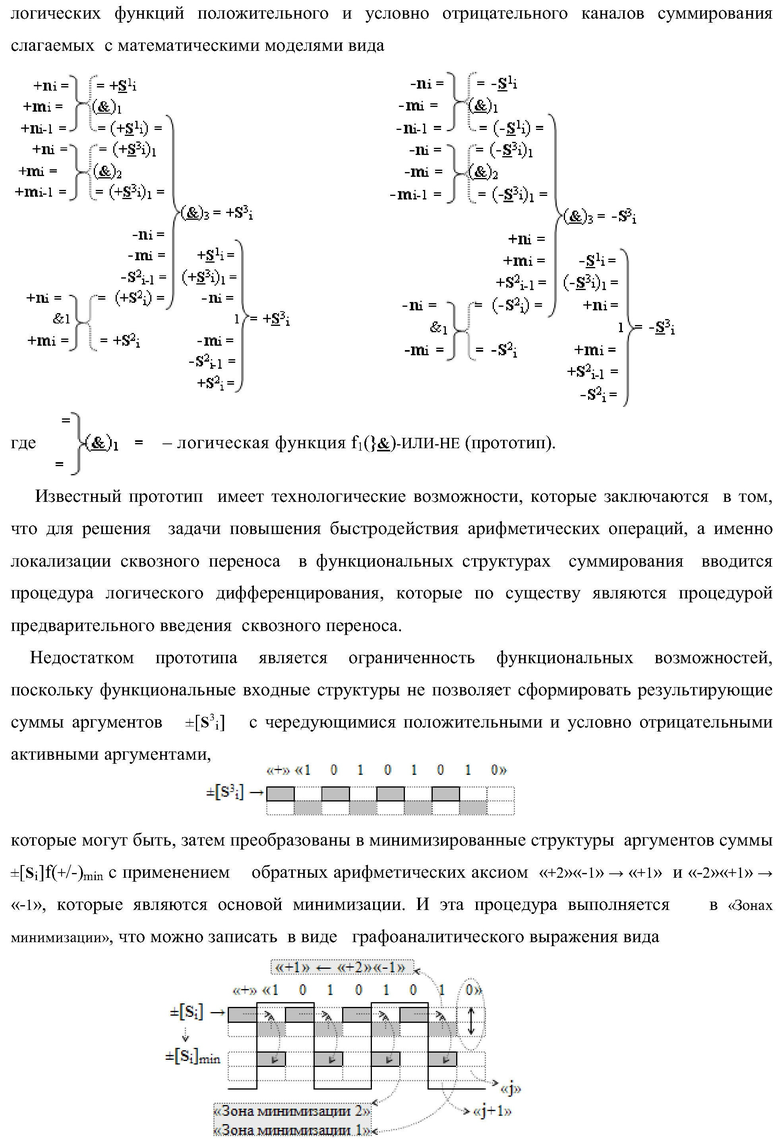

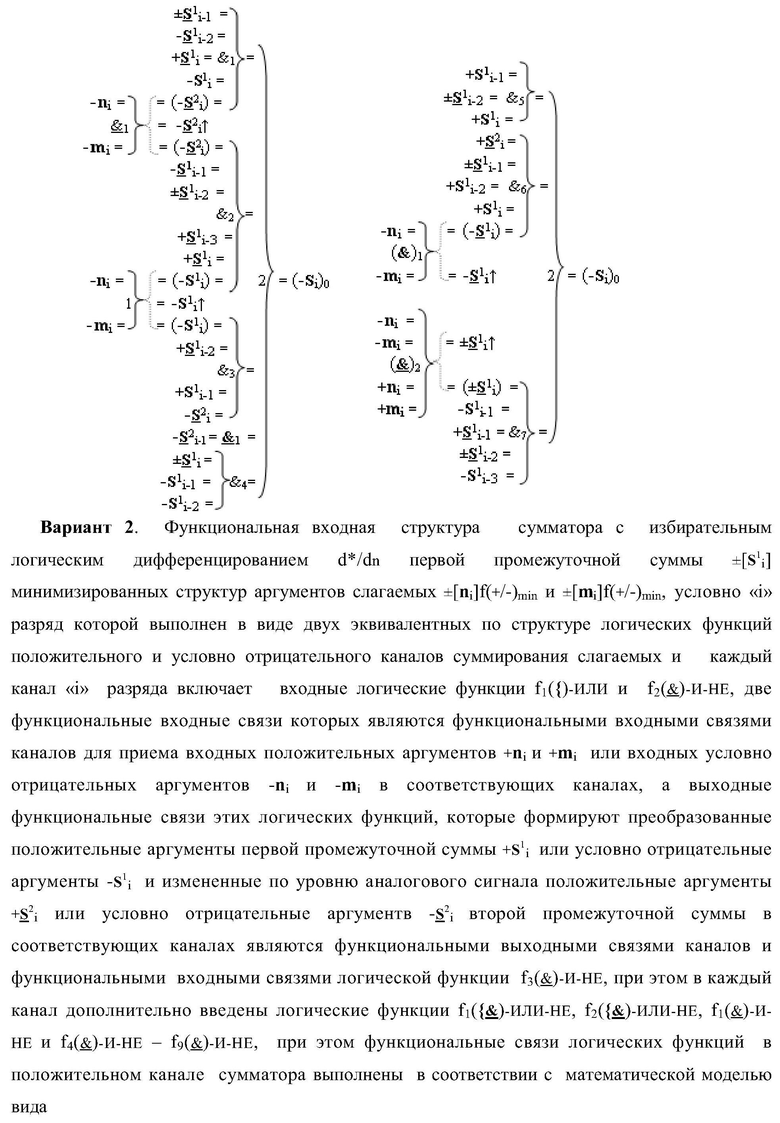

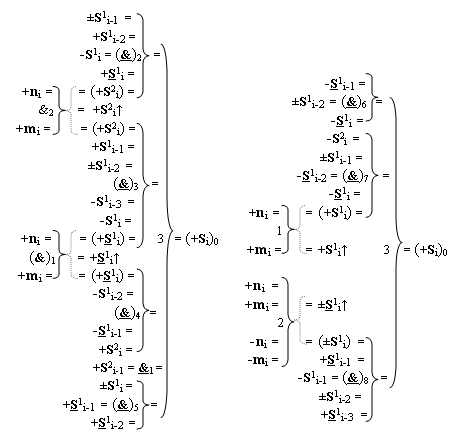

2. Функциональная входная структура сумматора с избирательным логическим дифференцированием d*/dn первой промежуточной суммы ±[S1 i] минимизированных структур аргументов слагаемых ±[ni]f(+/-)min и ±[mi]f(+/-)min, условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов суммирования слагаемых и каждый канал «i» разряда включает входные логические функции f1({)-ИЛИ и f2(&)-И-НЕ, две функциональные входные связи которых являются функциональными входными связями каналов для приема входных положительных аргументов +ni и +mi или входных условно отрицательных аргументов -ni и -mi в соответствующих каналах, а выходные функциональные связи этих логических функций, которые формируют преобразованные положительные аргументы первой промежуточной суммы +S1 i или условно отрицательные аргументы -S1 i и измененные по уровню аналогового сигнала положительные аргументы +S

2 i или условно отрицательные аргументы -S

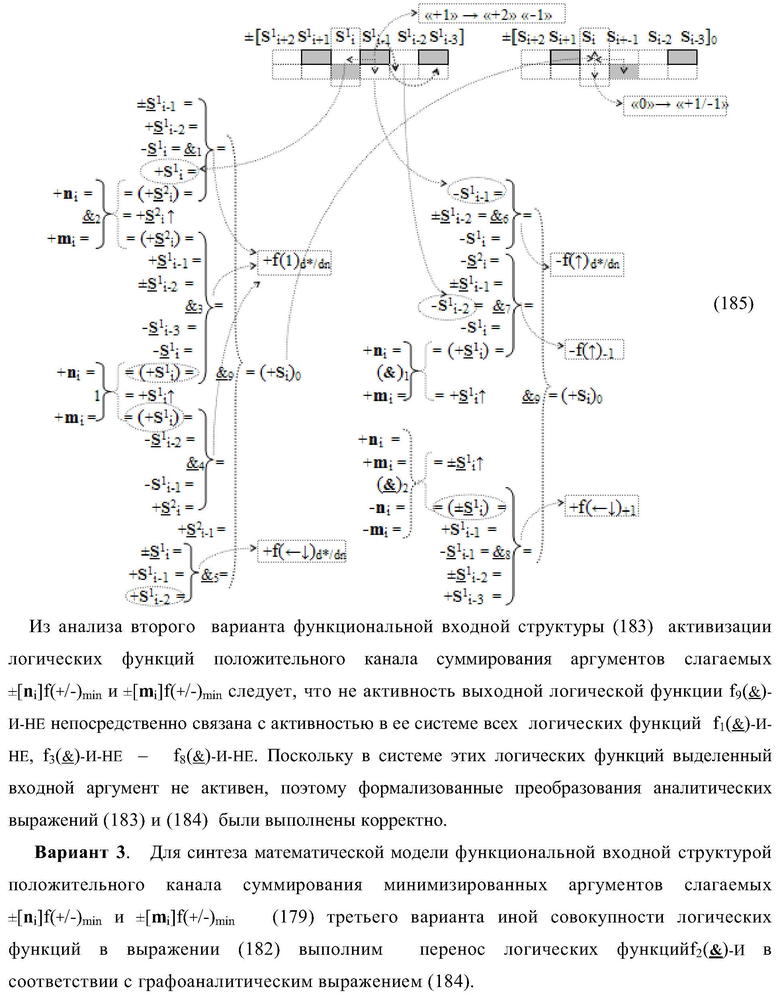

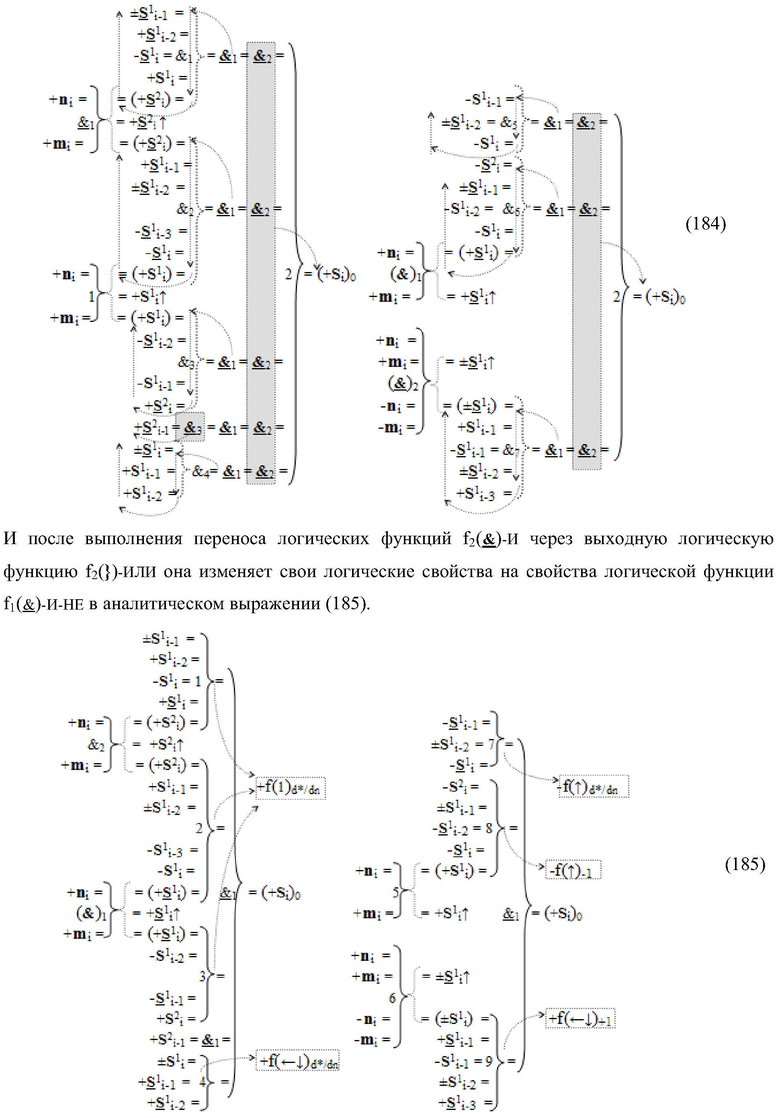

2 i второй промежуточной суммы в соответствующих каналах являются функциональными выходными связями каналов и функциональными входными связями логической функции f3(&)-И-НЕ, отличающаяся тем, что в каждый канал дополнительно введены логические функции f1({&)-ИЛИ-НЕ, f2({&)-ИЛИ-НЕ, f1(&)-И-НЕ и f4(&)-И-НЕ - f9(&)-И-НЕ, при этом функциональные связи логических функций в положительном канале сумматора выполнены в соответствии с математической моделью вида

а в условно отрицательном канале сумматора выполнены в соответствии с математической моделью вида

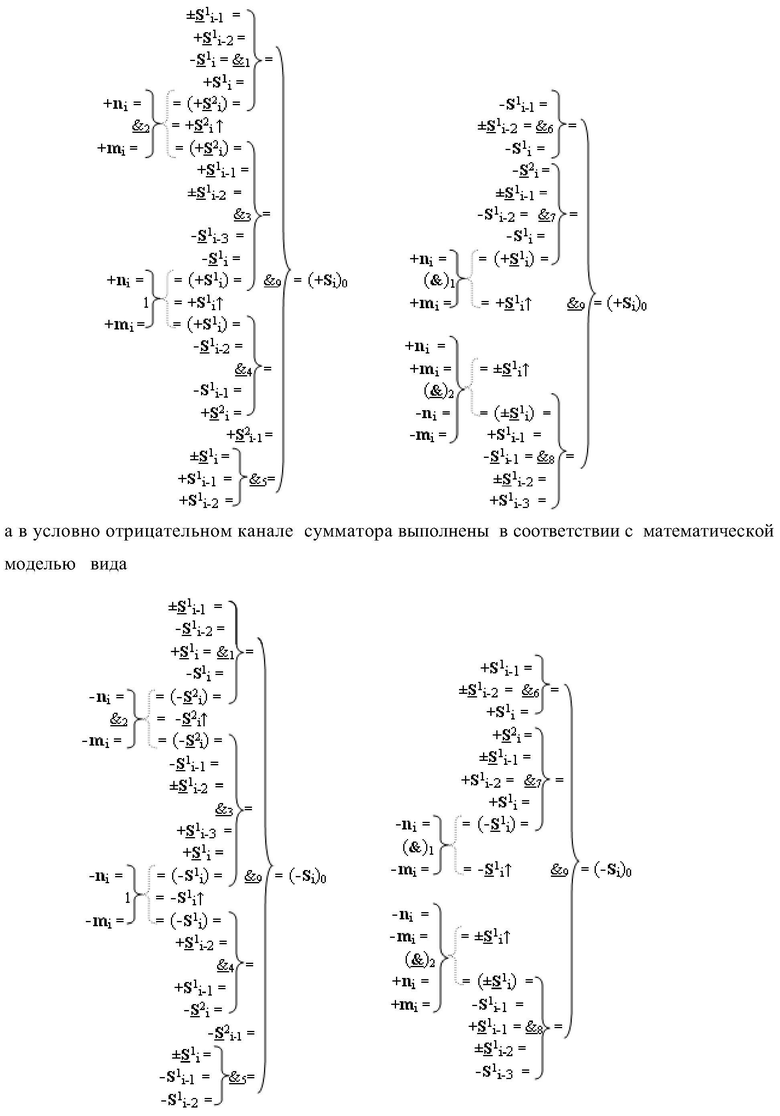

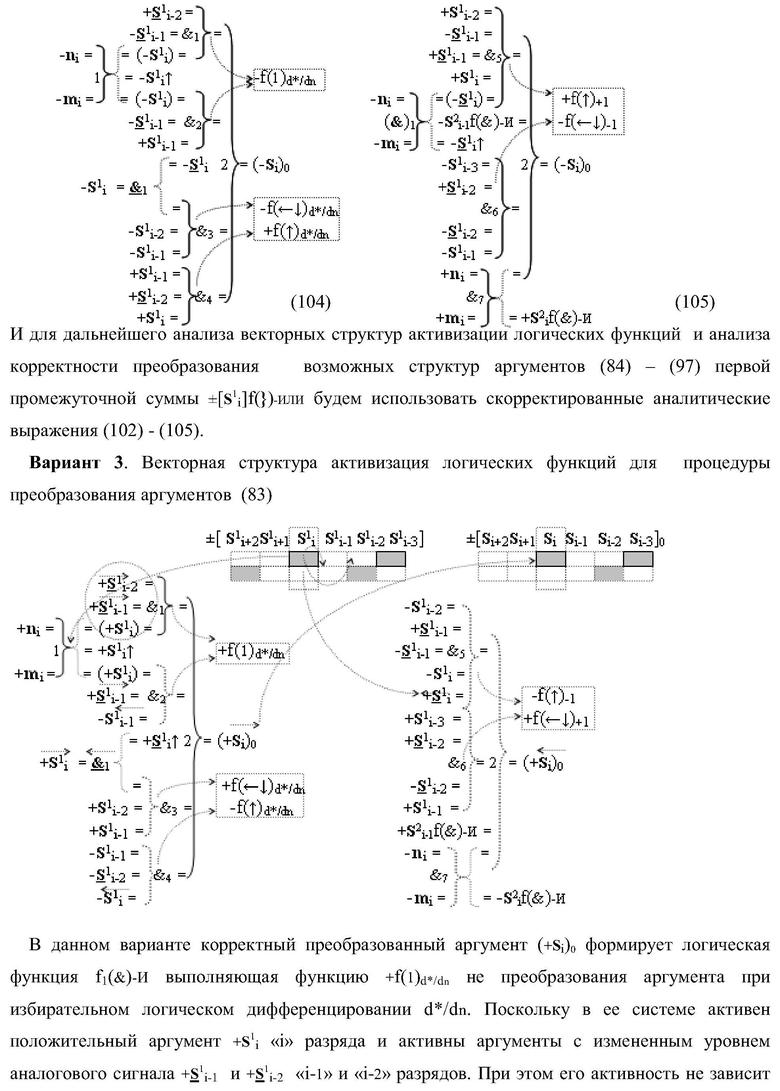

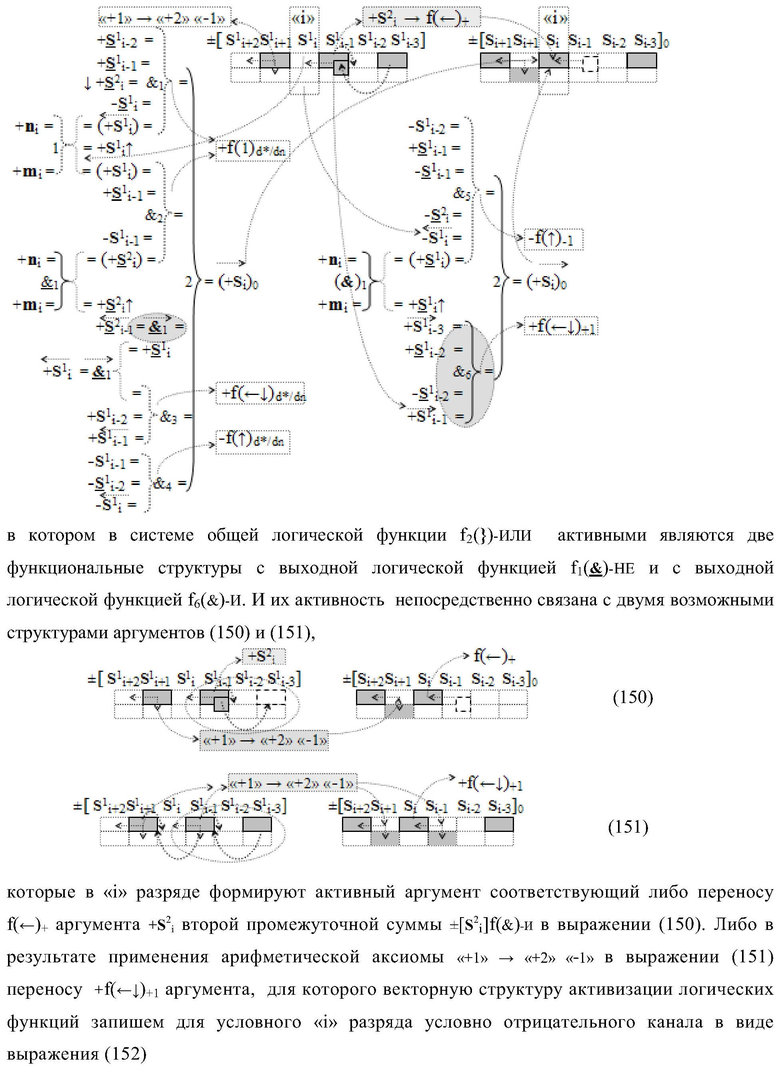

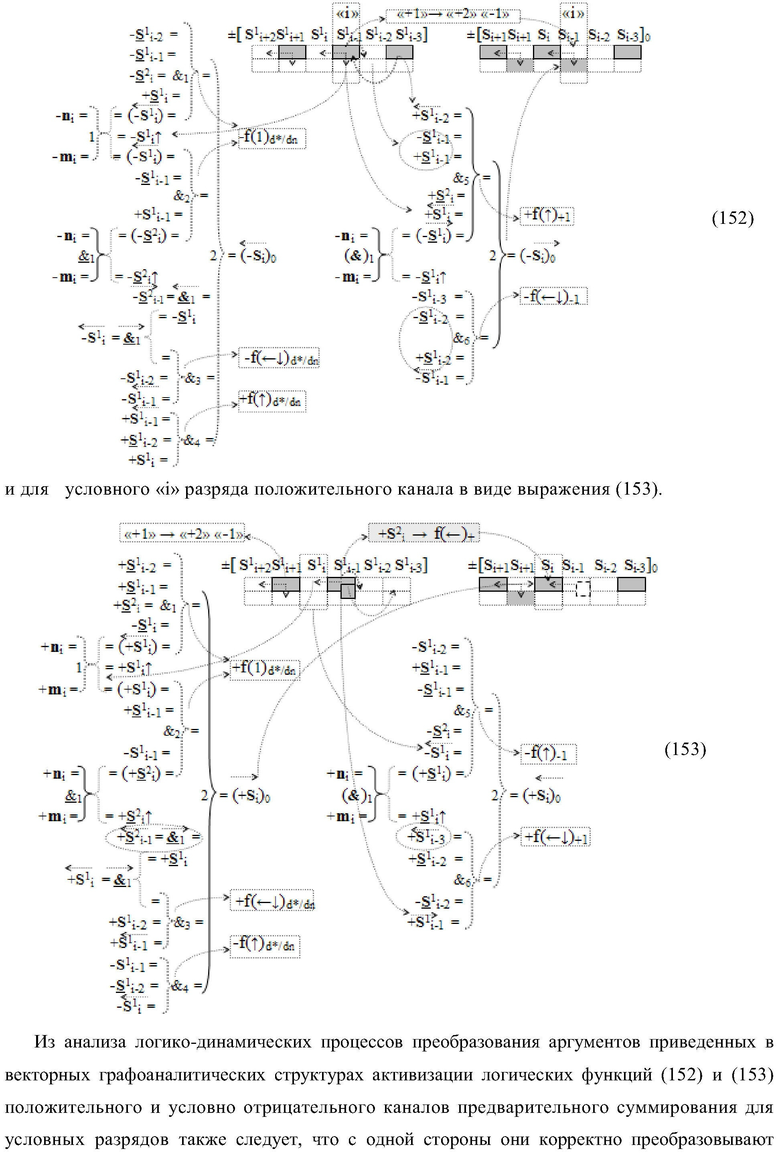

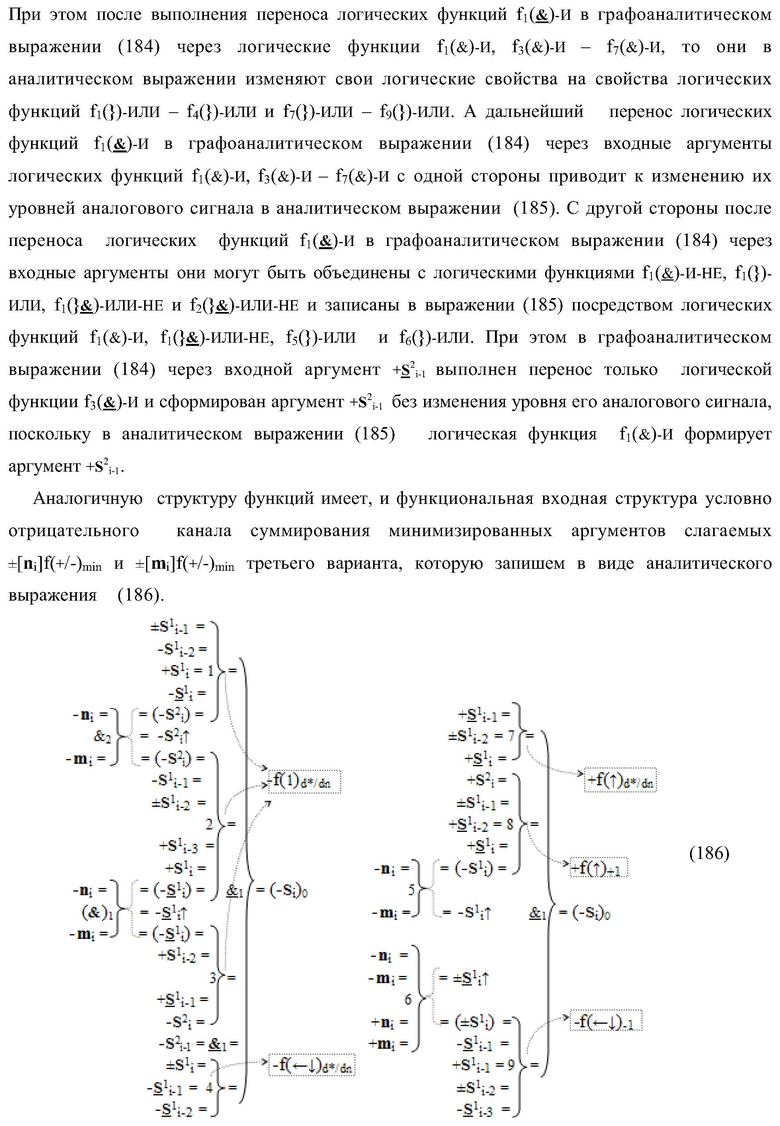

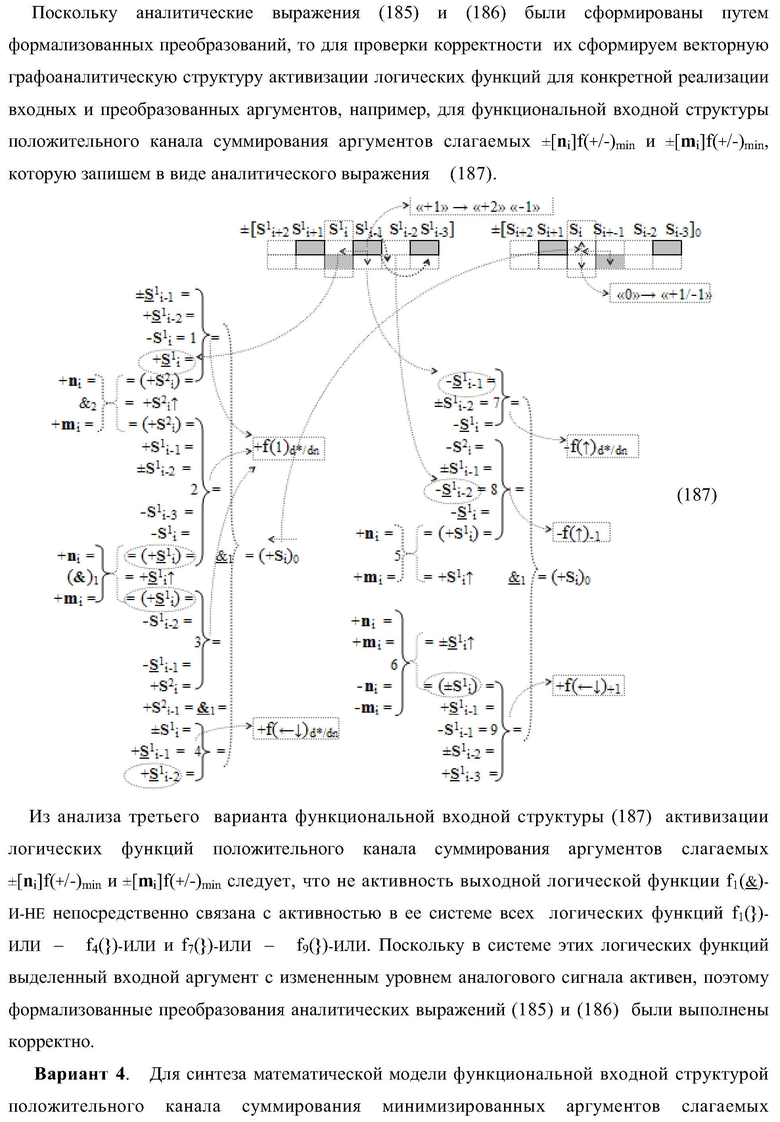

3. Функциональная входная структура сумматора с избирательным логическим дифференцированием d*/dn первой промежуточной суммы ±[S1 i] минимизированных структур аргументов слагаемых ±[ni]f(+/-)min и ±[mi]f(+/-)min, условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов суммирования слагаемых и каждый канал «i» разряда включает входные логические функции f1({&)-ИЛИ-НЕ и f2(&)-И, две функциональные входные связи которых являются функциональными связями каналов сумматора для приема входных положительных аргументов +ni и +mi или входных условно отрицательных аргументов -ni и -mi в соответствующих каналах, а выходные функциональные связи этих логических функций, которые формируют преобразованные положительные аргументы первой промежуточной суммы +S

1 i или условно отрицательные аргументы -S

1 i с измененным уровнем аналогового сигнала и положительные аргументы +S2 i или условно отрицательные аргументы -S2 i второй промежуточной суммы в соответствующих каналах являются функциональными выходными связями каналов и функциональными входными связями логической функции f2({)-ИЛИ, отличающаяся тем, что в каждый канал дополнительно введены логические функции f1(&)-НЕ, f1({)-ИЛИ, f3({)-ИЛИ - f9({)-ИЛИ и f1(&)-И-НЕ, при этом функциональные связи логических функций в положительном канале сумматора выполнены в соответствии с математической моделью вида

а в условно отрицательном канале сумматора выполнены в соответствии с математической моделью вида

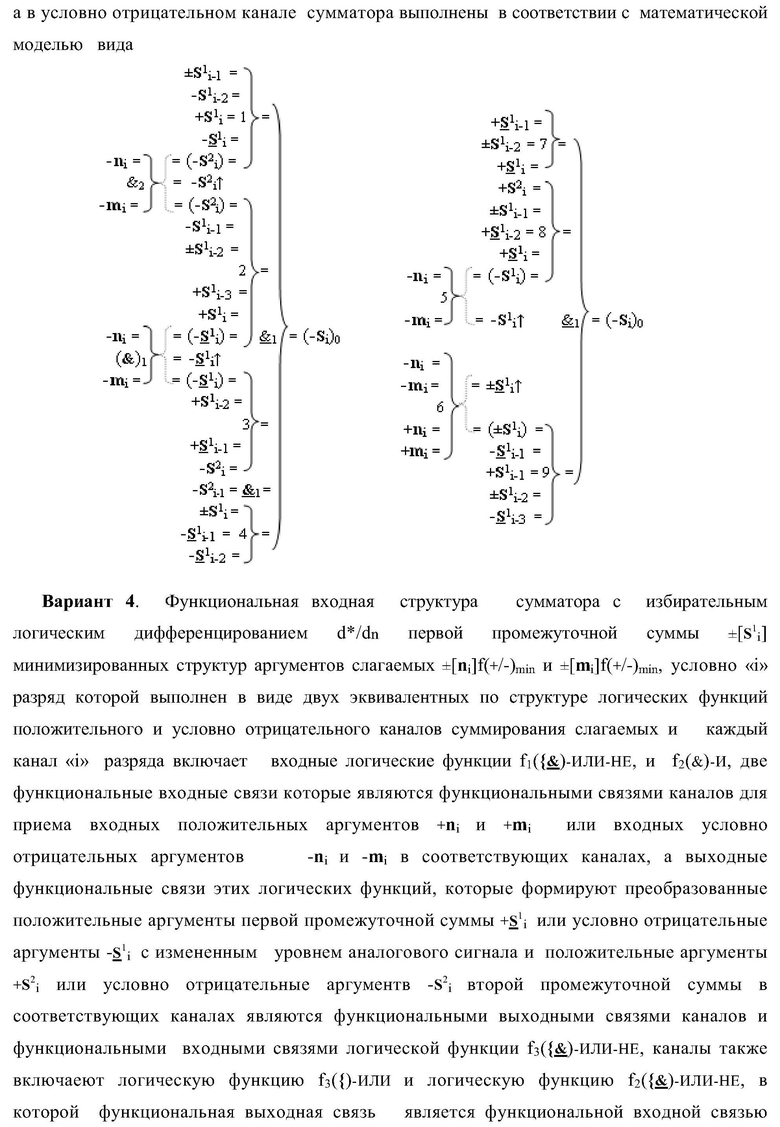

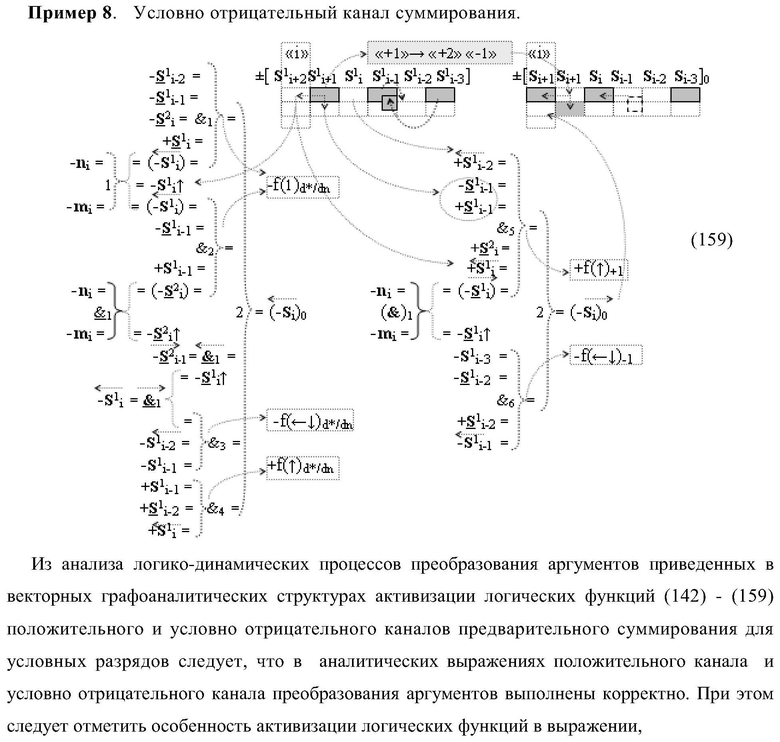

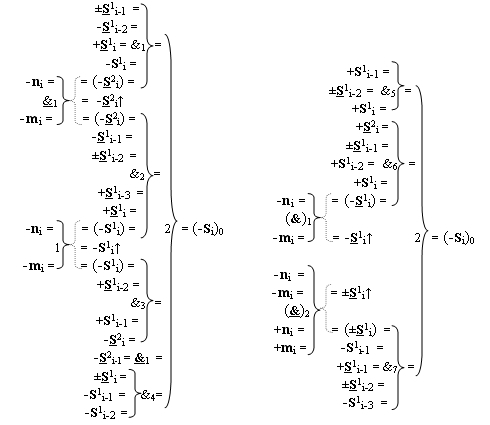

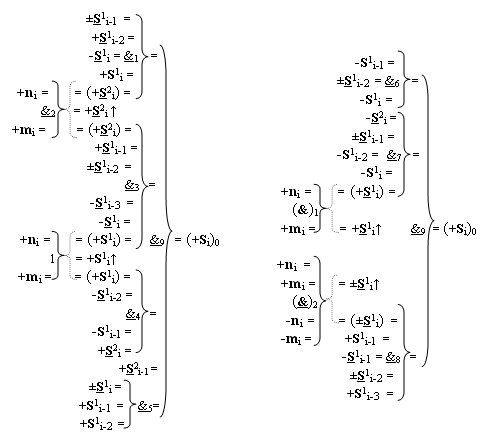

4. Функциональная входная структура сумматора с избирательным логическим дифференцированием d*/dn первой промежуточной суммы ±[S1 i] минимизированных структур аргументов слагаемых ±[ni]f(+/-)min и ±[mi]f(+/-)min, условно «i» разряд которой выполнен в виде двух эквивалентных по структуре логических функций положительного и условно отрицательного каналов суммирования слагаемых и каждый канал «i» разряда включает входные логические функции f1({&)-ИЛИ-НЕ и f2(&)-И, две функциональные входные связи которые являются функциональными связями каналов для приема входных положительных аргументов +ni и +mi или входных условно отрицательных аргументов -ni и -mi в соответствующих каналах, а выходные функциональные связи этих логических функций, которые формируют преобразованные положительные аргументы первой промежуточной суммы +S

1 i или условно отрицательные аргументы -S

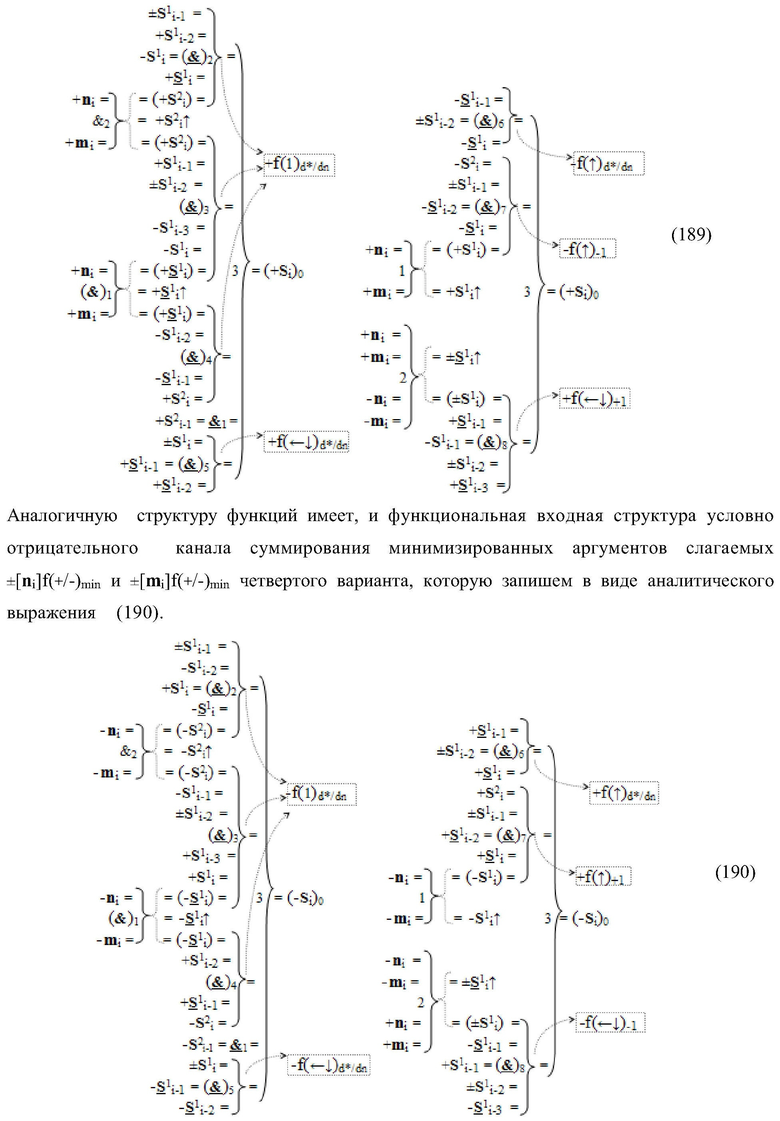

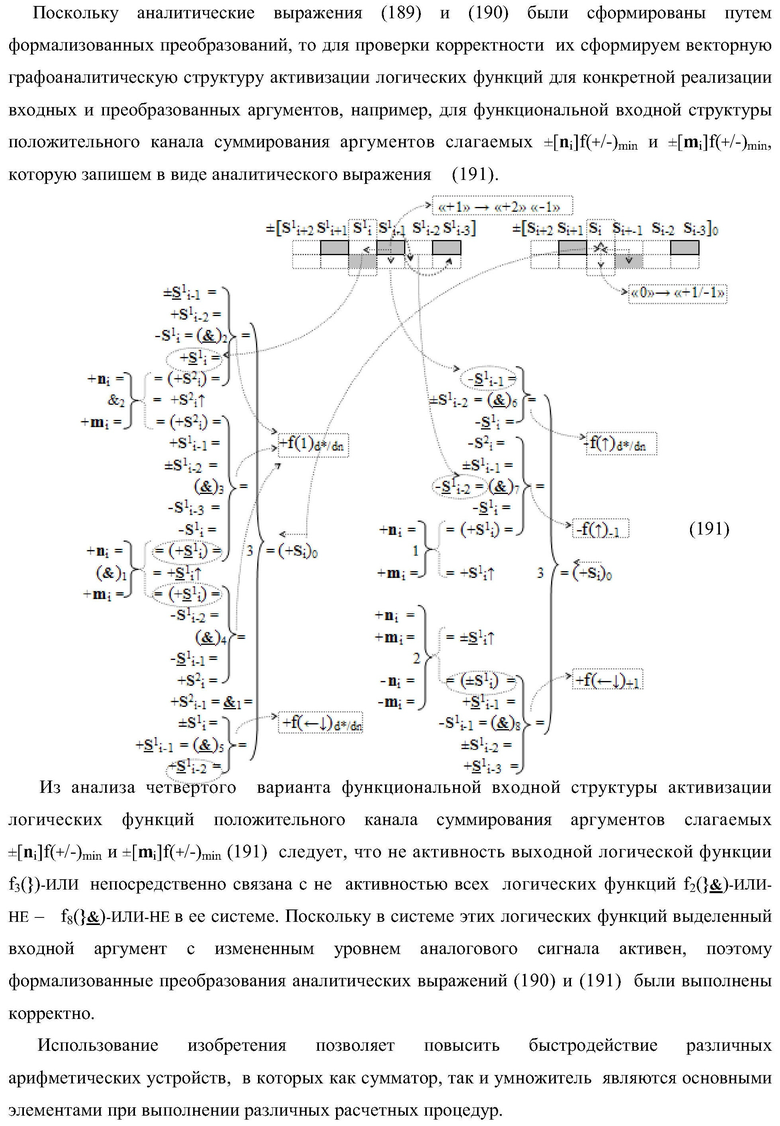

1 i с измененным уровнем аналогового сигнала и положительные аргументы +S2 i или условно отрицательные аргументв -S2 i второй промежуточной суммы в соответствующих каналах являются функциональными выходными связями каналов и функциональными входными связями логической функции f3({&)-ИЛИ-НЕ, каналы также включаеют логическую функцию f3({)-ИЛИ и логическую функцию f2({&)-ИЛИ-НЕ, в которой функциональная выходная связь является функциональной входной связью логической функции f3({)-ИЛИ, в которой функциональная выходная связь является функциональной выходной связью канала для формирования результирующего положительного аргумента (+Si)0 и условно отрицательного аргумента (-Si)0 в соответствующем канале, отличающаяся тем, что в каждый канал дополнительно введены логические функции f1(&)-НЕ, и f1({)-ИЛИ, f2({)-ИЛИ, f4({&)-ИЛИ-НЕ - f8({&)-ИЛИ-НЕ, при этом функциональные связи логических функций в положительном канале сумматора выполнены в соответствии с математической моделью вида

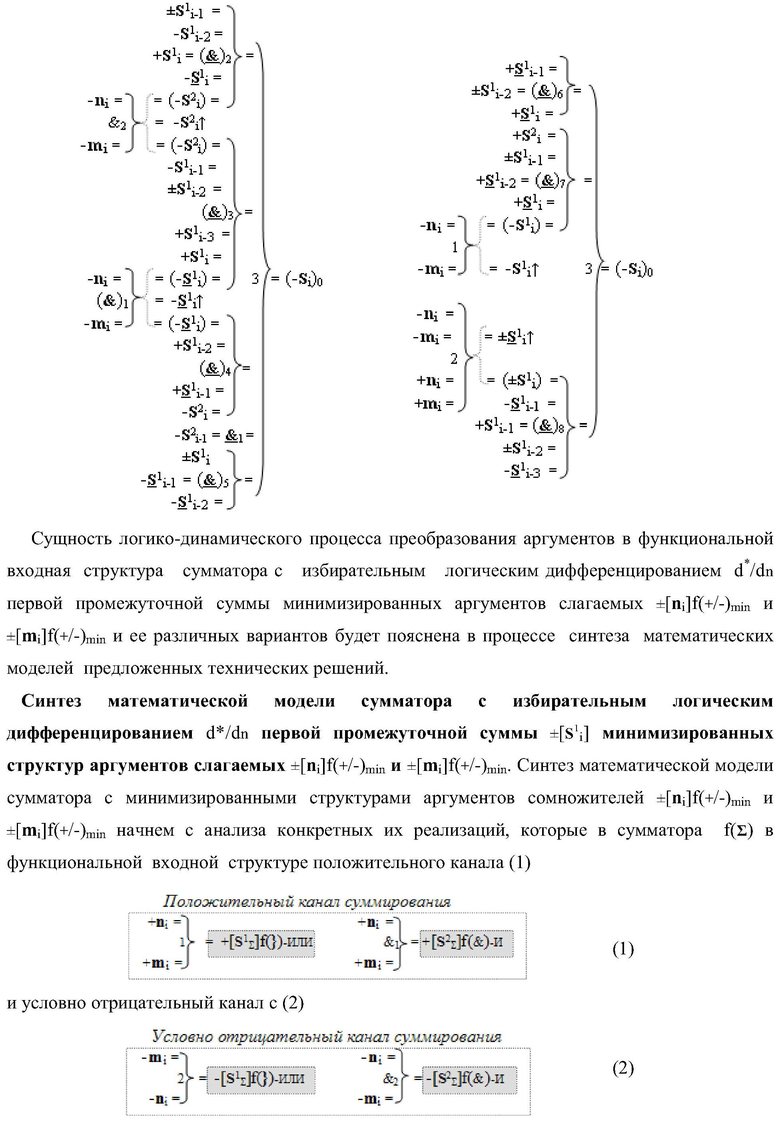

а в условно отрицательном канале сумматора выполнены в соответствии с математической моделью вида

| RU 2007146288 А, 27.06.2009 | |||

| Устройство для параллельного сложения чисел, представленных в двоичной знакоразрядной системе счисления | 1989 |

|

SU1727120A1 |

| Последовательный сумматор в избыточной двоичной системе счисления | 1988 |

|

SU1619251A1 |

| JP 9016378 A, 17.01.1997 | |||

| JP 1304532 A, 08.12.1989. | |||

Авторы

Даты

2011-07-20—Публикация

2009-11-10—Подача