Текст описания приведен в факсимильном виде.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций, в частности процессов суммирования и вычитания, в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия. Каждый разряд сумматора содержит четыре элемента ИЛИ, два элемента И, три элемента НЕ и выполнен в виде двух каналов - канала формирования положительной суммы и канала формирования условно отрицательной суммы. 5 ил.

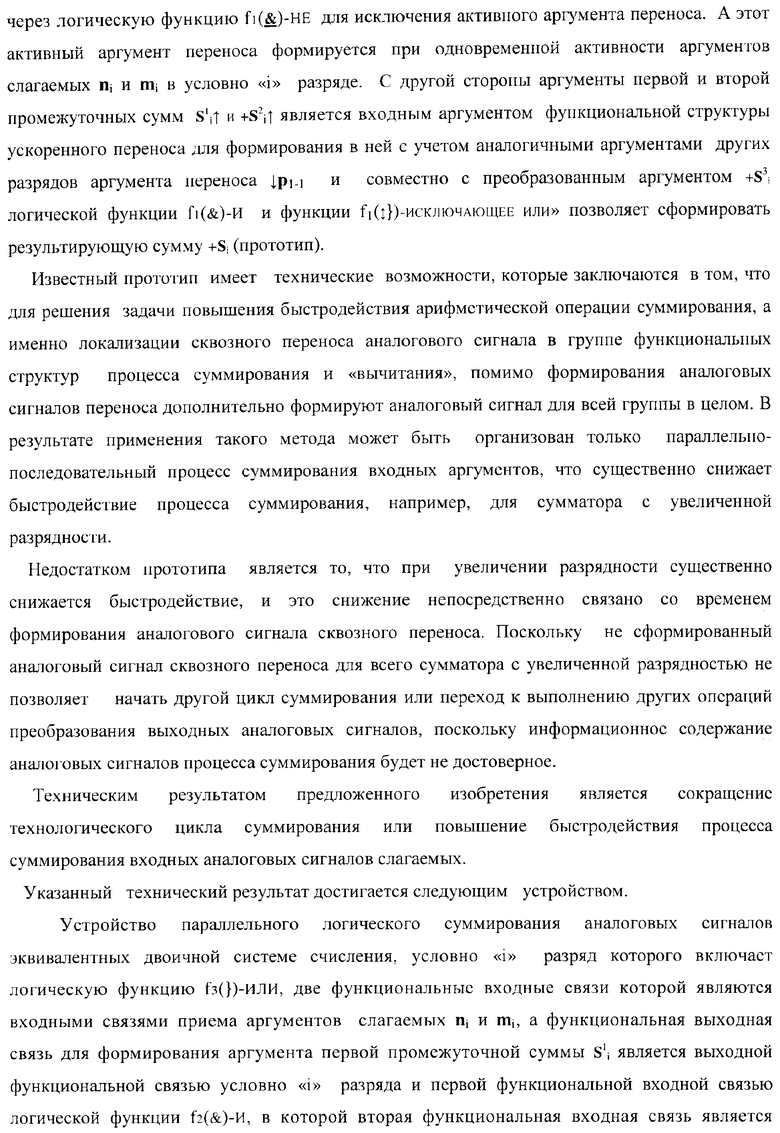

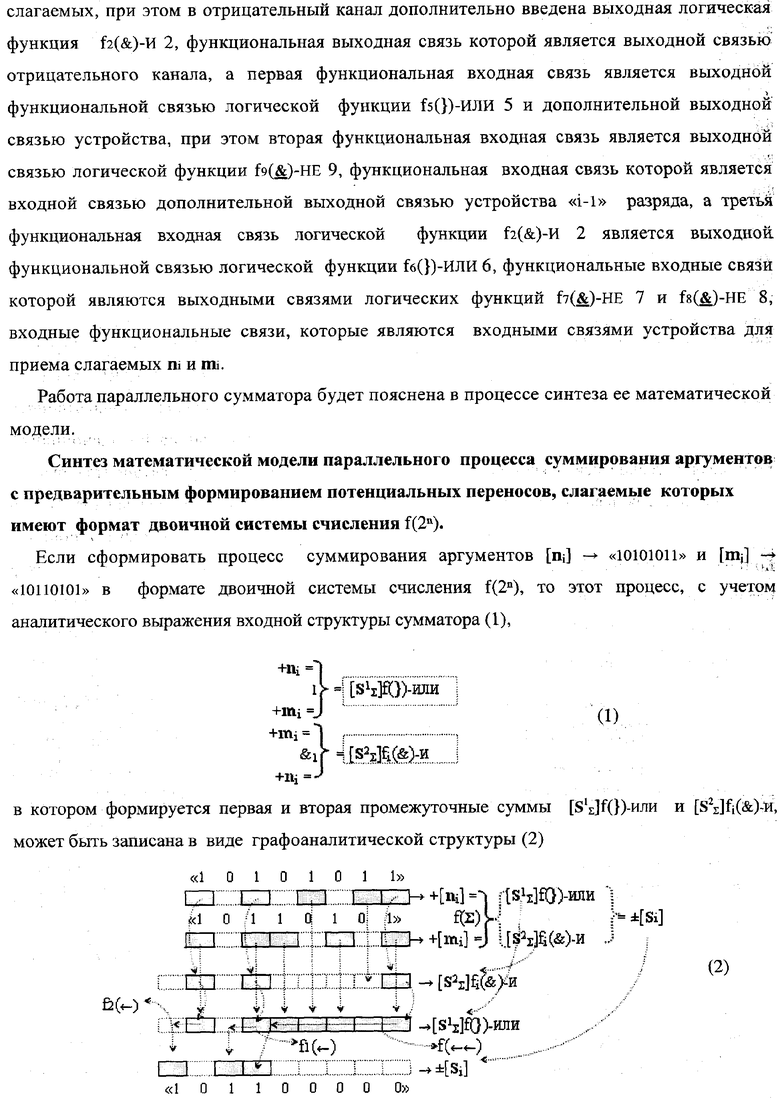

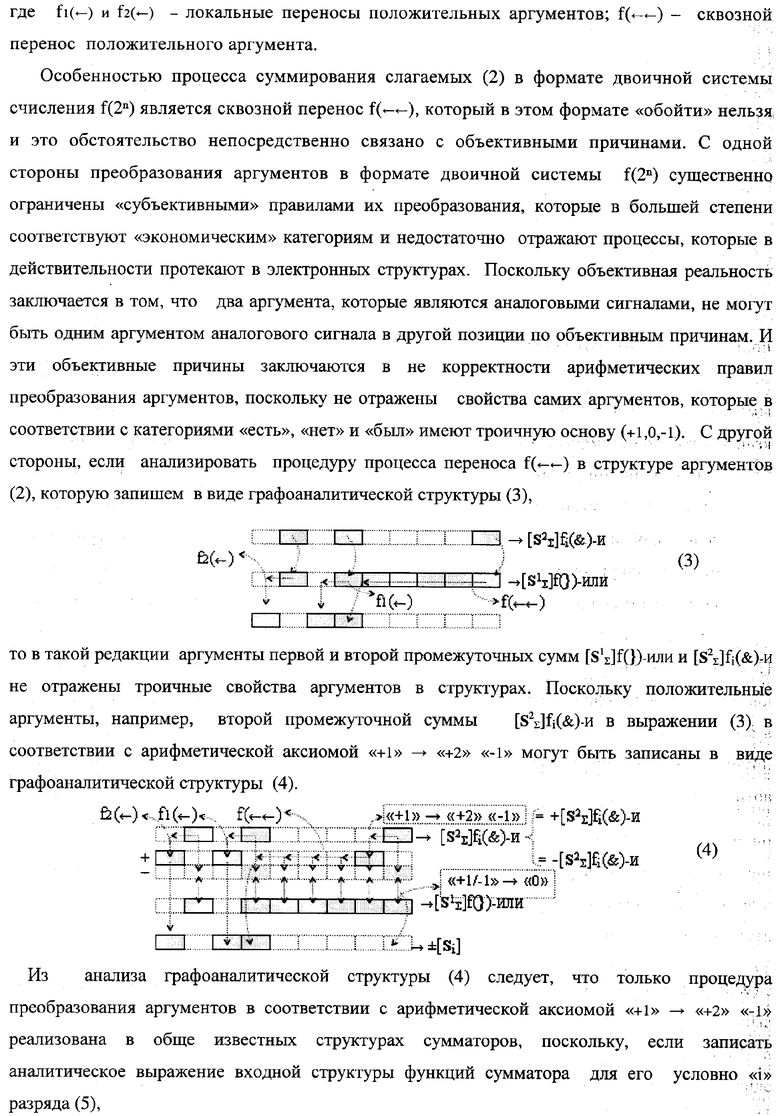

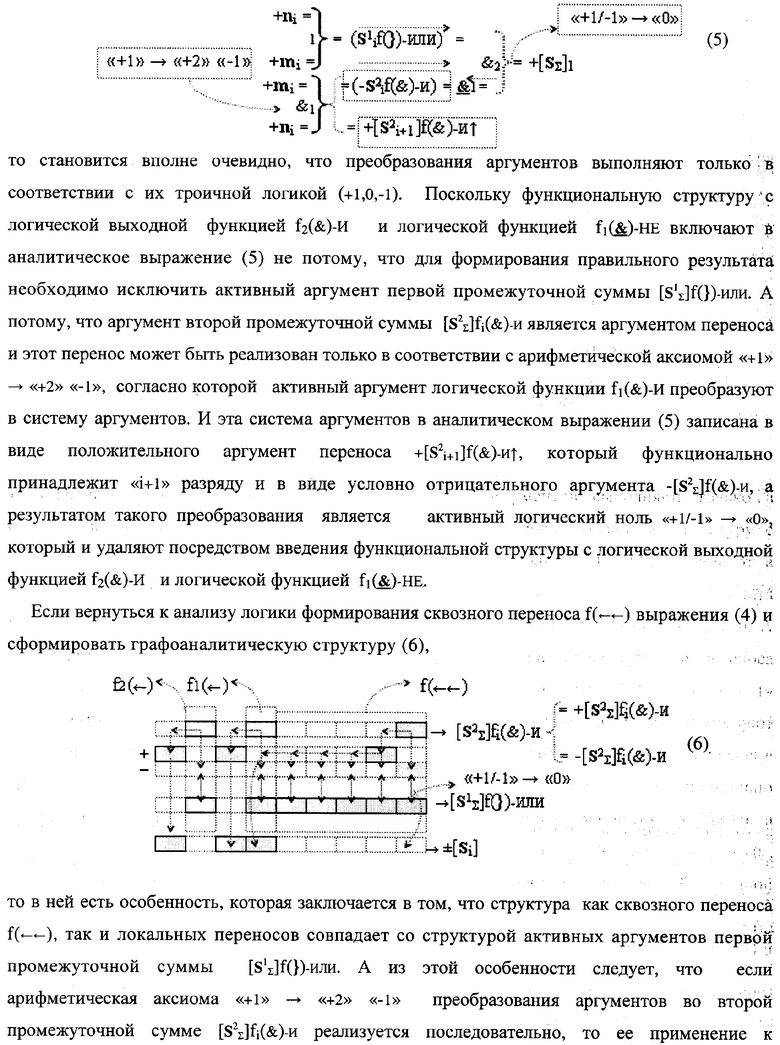

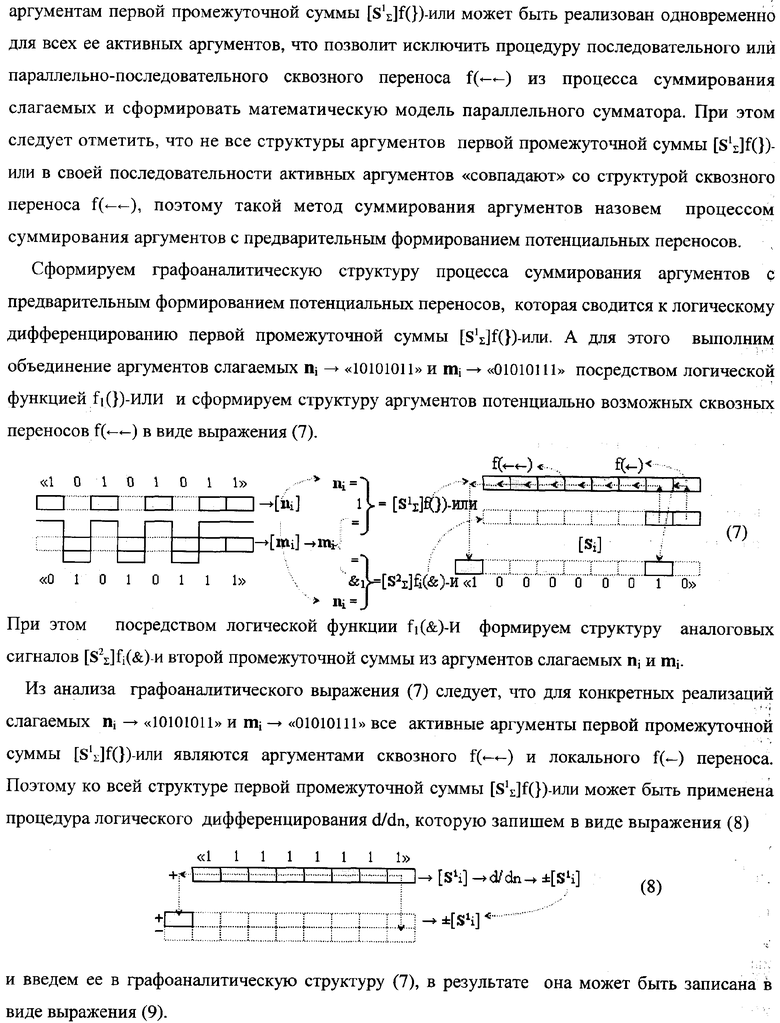

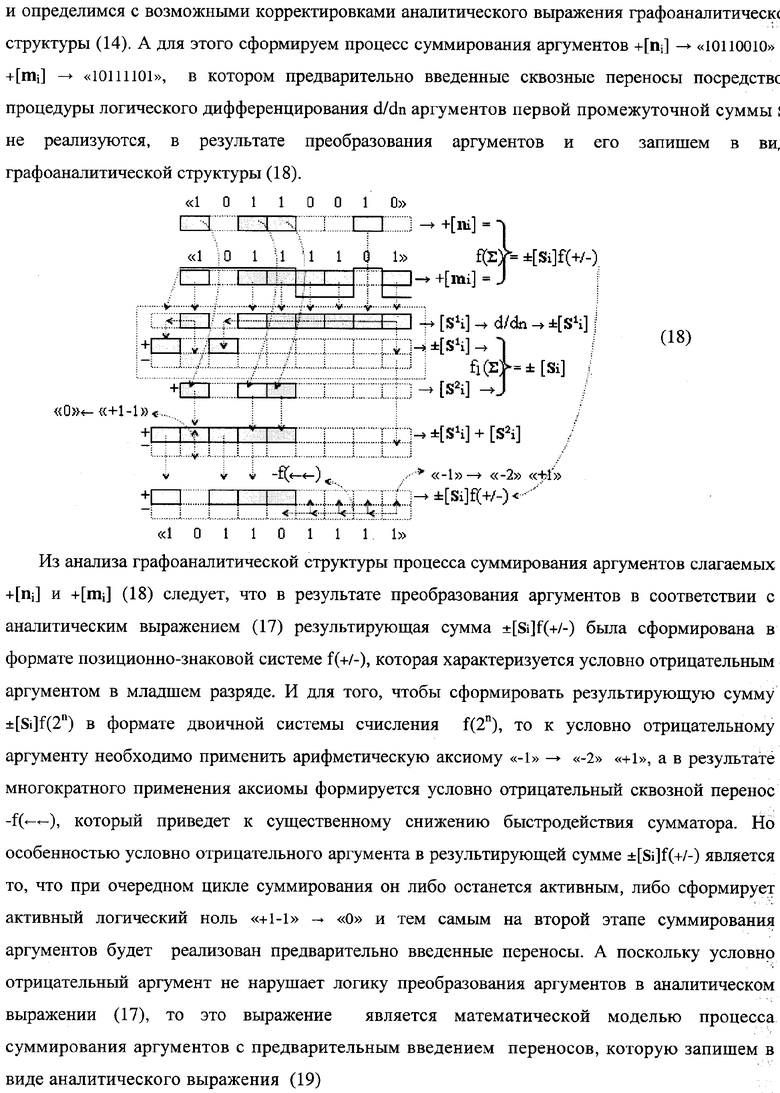

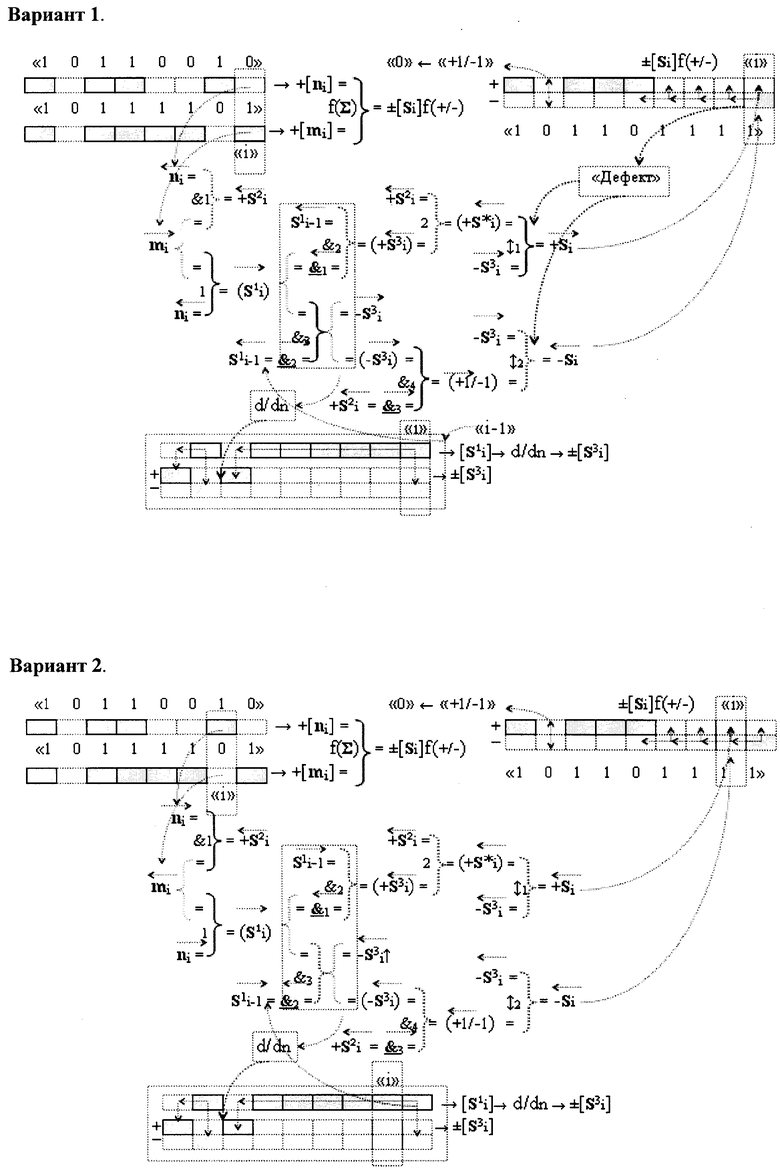

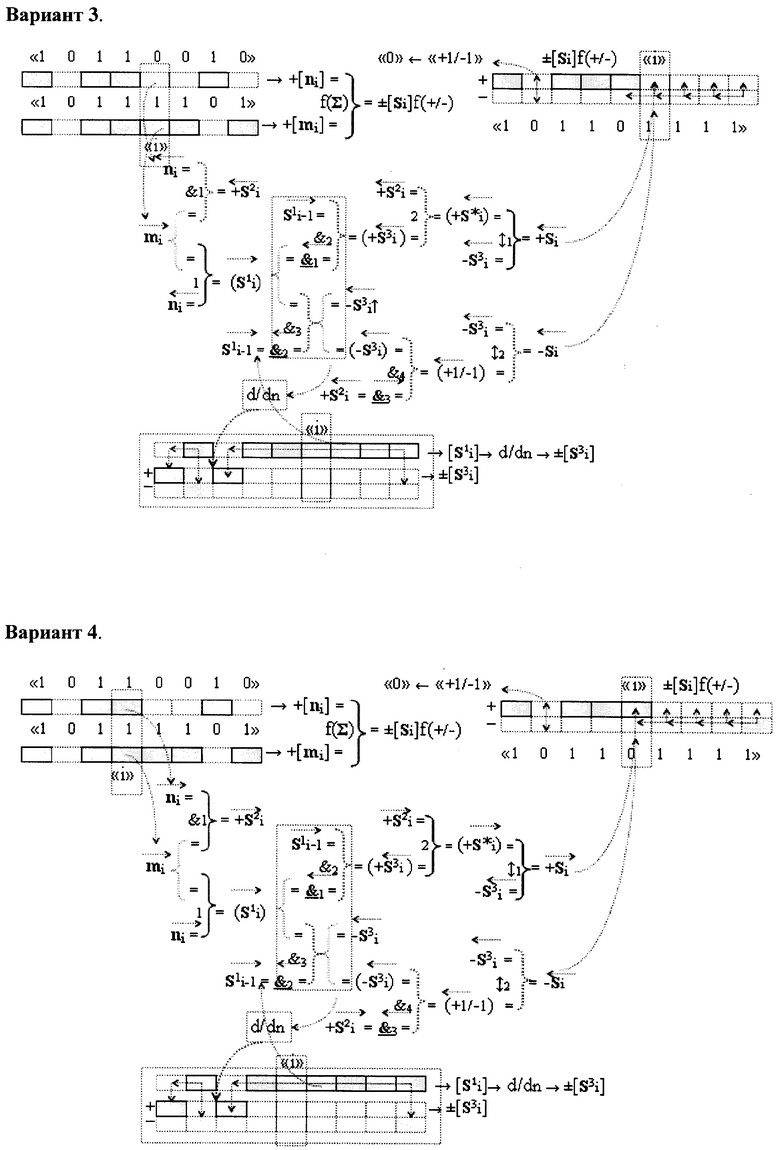

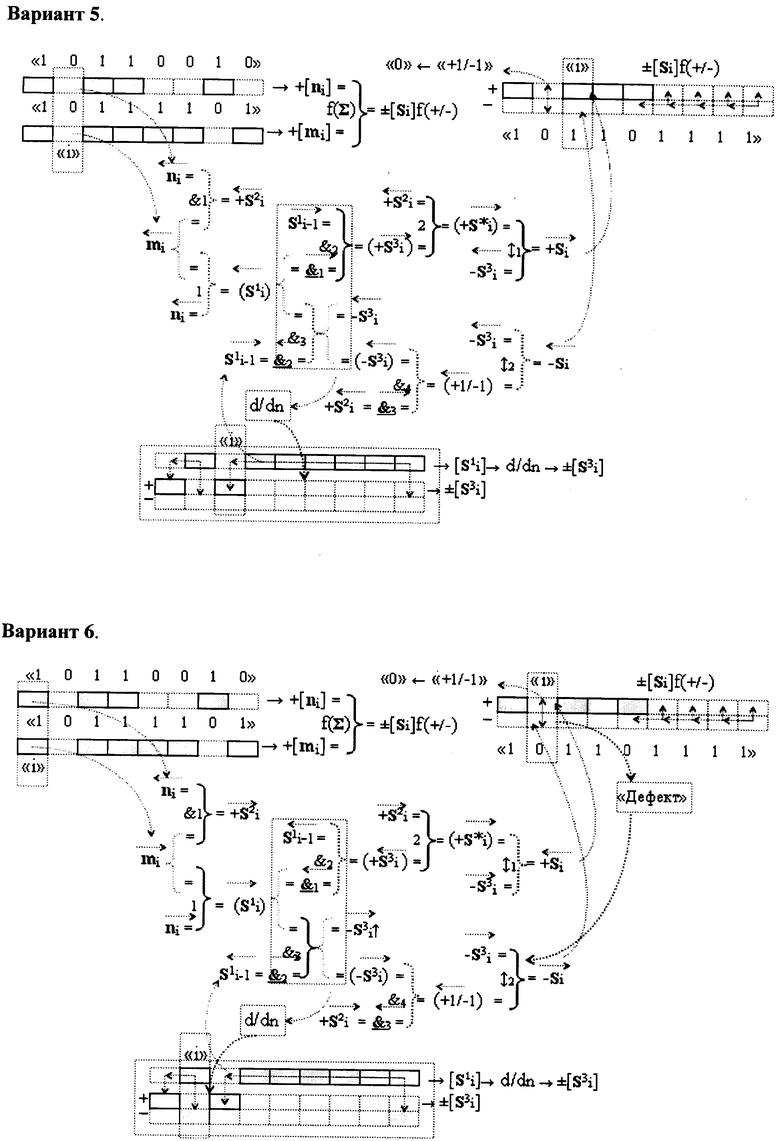

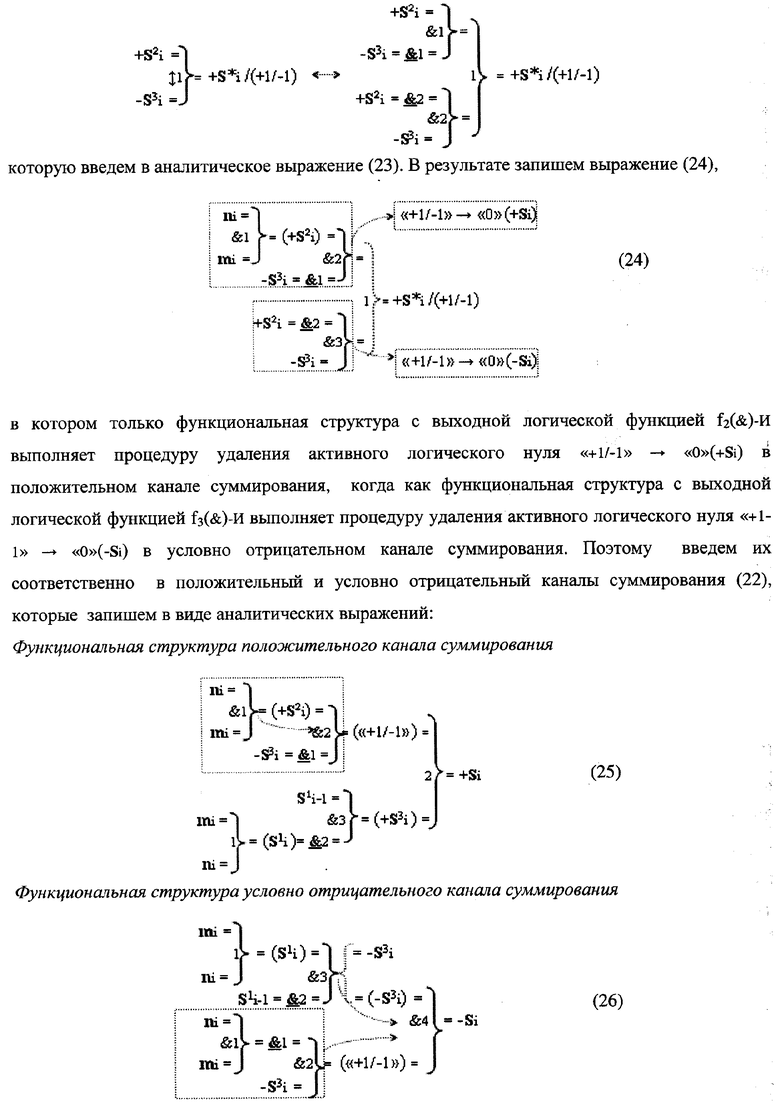

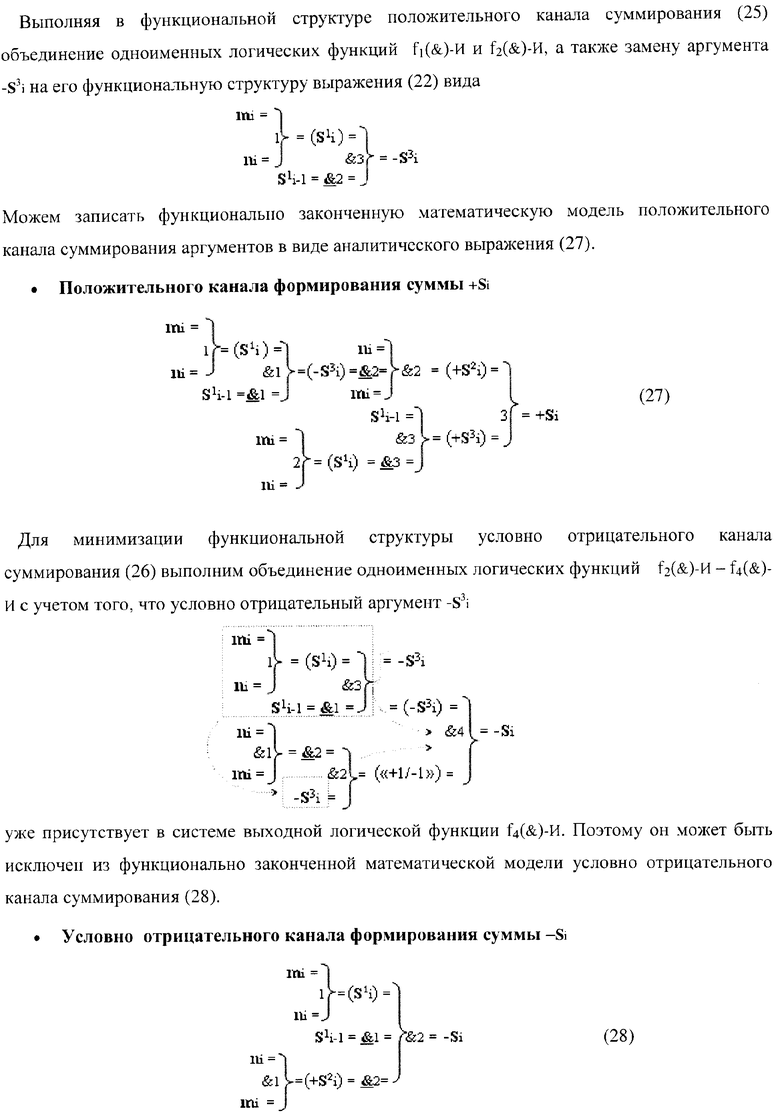

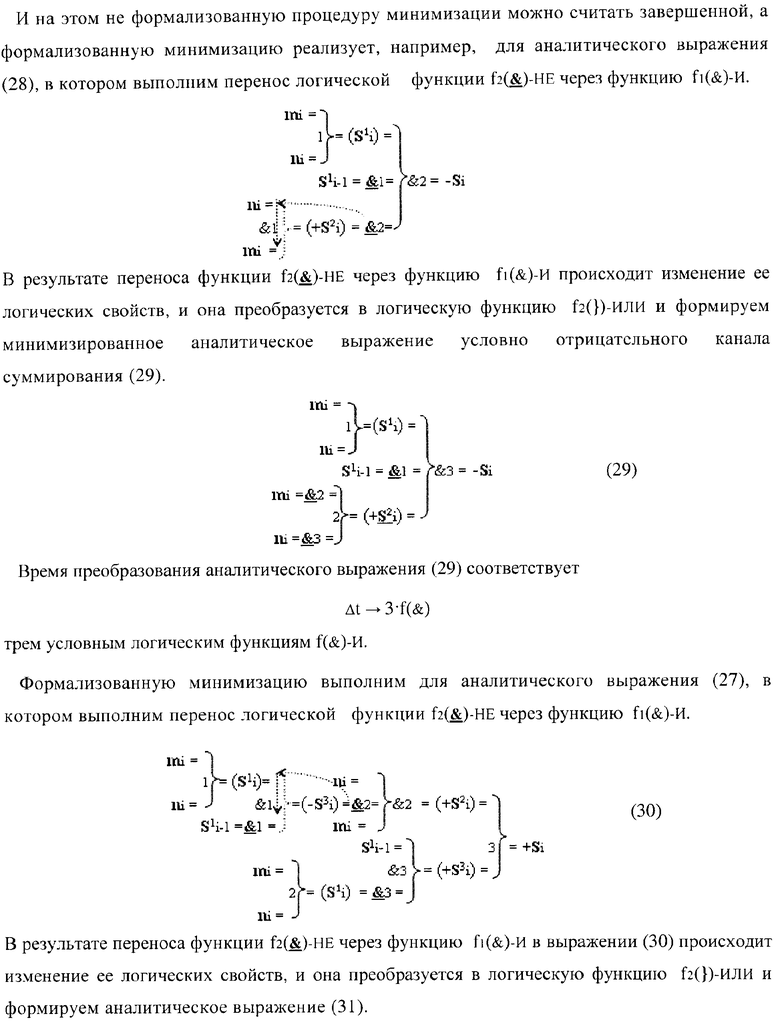

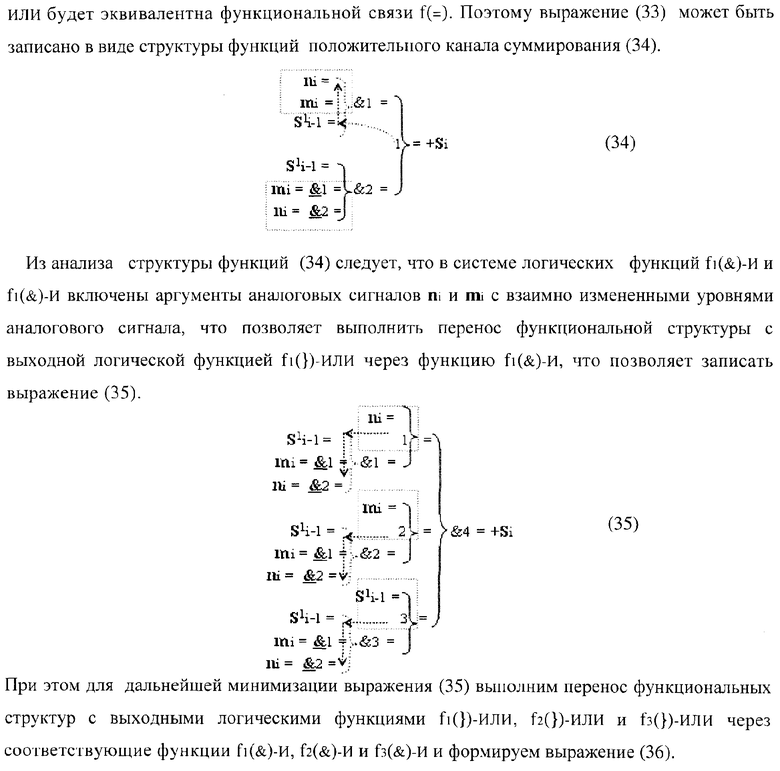

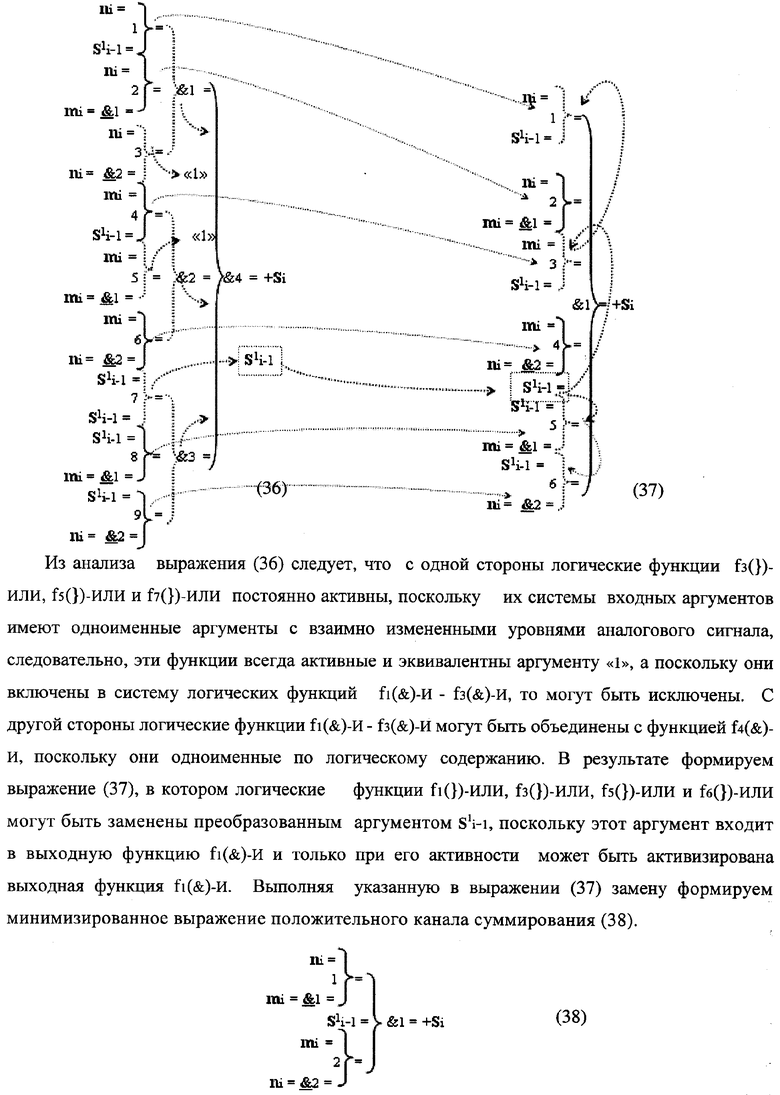

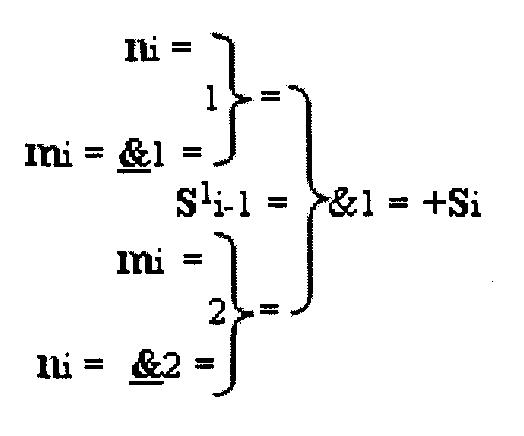

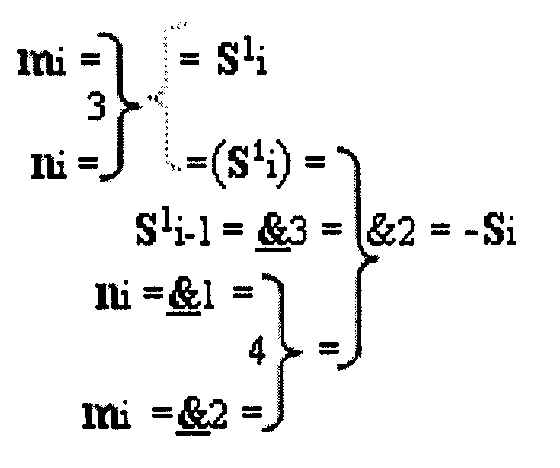

Устройство параллельного логического суммирования аналоговых сигналов, эквивалентных двоичной системе счисления, условно «i» разряд которого включает логическую функцию f3(})-ИЛИ, две функциональные входные связи которой являются входными связями приема аргументов слагаемых ni и mi, а функциональная выходная связь для формирования аргумента первой промежуточной суммы S1 i является выходной функциональной связью условно «i» разряда и первой функциональной входной связью логической функции f2(&)-И, в которой вторая функциональная входная связь является выходной функциональной связью логической функции f3 -HE, отличающееся тем, что условно «i» разряд параллельного сумматора выполнен в виде двух каналов формирования положительной +Si и условно отрицательной -Si суммы, при этом в условно отрицательный канал введены логические функции f4(})-ИЛИ f1

-HE, отличающееся тем, что условно «i» разряд параллельного сумматора выполнен в виде двух каналов формирования положительной +Si и условно отрицательной -Si суммы, при этом в условно отрицательный канал введены логические функции f4(})-ИЛИ f1 -HE и f2

-HE и f2 -HE, а в положительный канал введены логические функции f1(})-ИЛИ, f2(})-ИЛИ, f1

-HE, а в положительный канал введены логические функции f1(})-ИЛИ, f2(})-ИЛИ, f1 -HE, f2

-HE, f2 -HE и f1

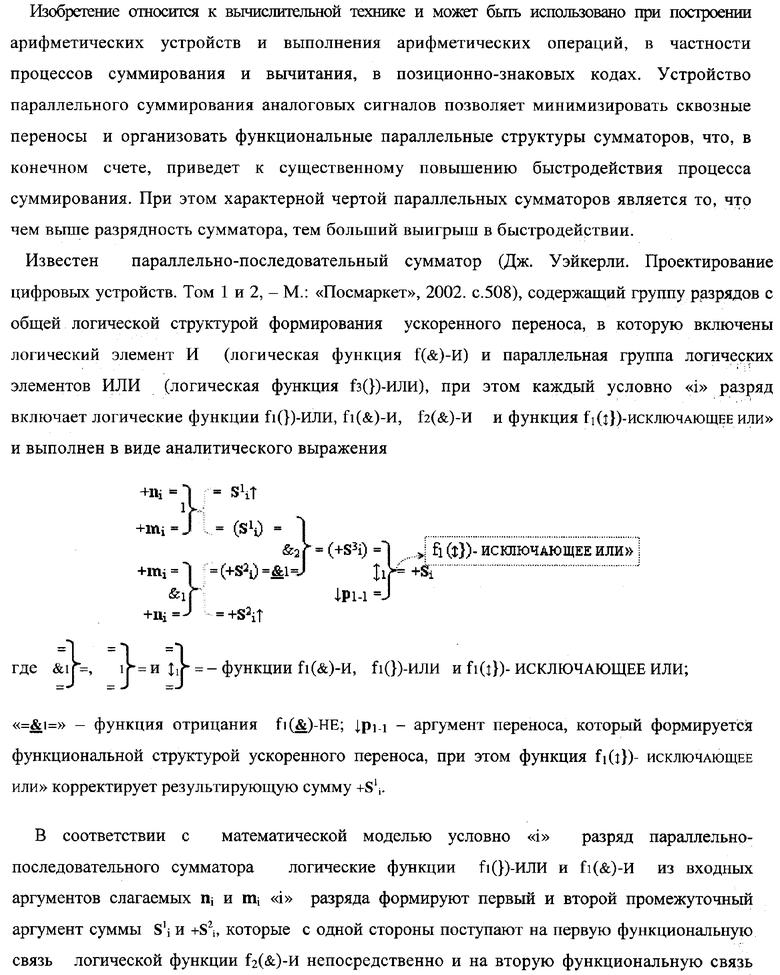

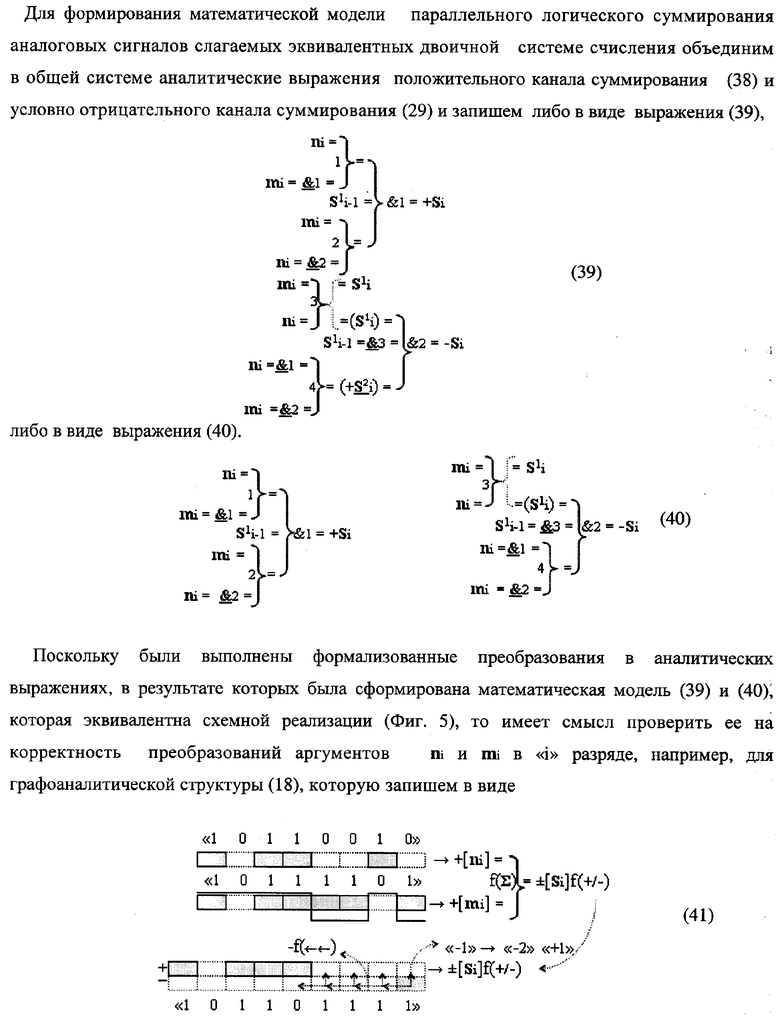

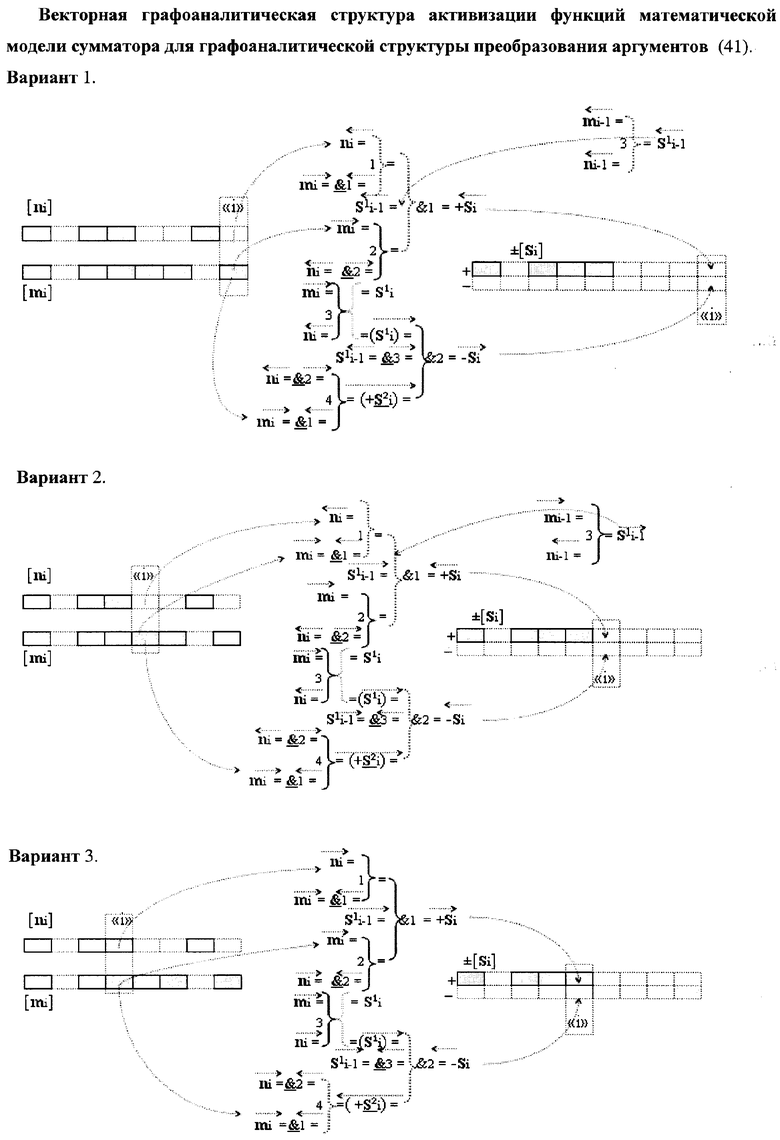

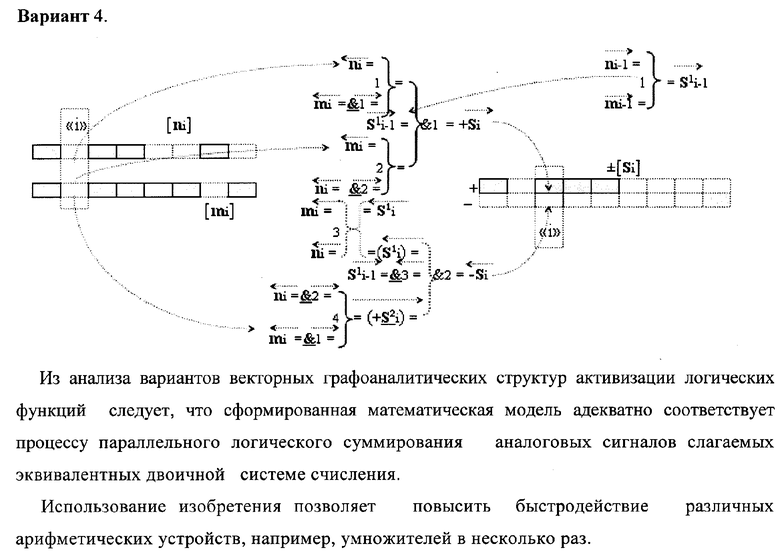

-HE и f1 -И, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

-И, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

где

- логическая функция f(&)-И;

- логическая функция f(&)-И;  логическая функция f1(})-ИЛИ;

логическая функция f1(})-ИЛИ;  - логическая функция f

- логическая функция f -HE изменения активности уровня аналоговых сигналов входного аргумента.

-HE изменения активности уровня аналоговых сигналов входного аргумента.

| УЭЙКЕРЛИ Д | |||

| Проектирование цифровых устройств | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| - М.: Постмаркет, 2002, с.508 | |||

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Устройство для сложения в двоичной избыточной системе счисления | 1981 |

|

SU997032A1 |

| Параллельный сумматор | 1986 |

|

SU1594523A1 |

| JP 62204332 A, 09.09.1987 | |||

| JP 63197227 A, 16.08.1988. | |||

Авторы

Даты

2009-08-10—Публикация

2006-12-15—Подача