Изобретение относится к области вычислительной техники и может быть использовано для реализации оперативной памяти в микропроцессорных системах

Известна многопортовая ячейка оперативной памяти (Патент США №6909662, Fig 1, G11C 8/00, 7/00, 8/16, НКИ 265/230.05, от 21.06.2005), содержащая два инвертора с обратными связями, порт записи на двух МДП транзисторах n-типа с управлением от адресной шины записи и двух шин данных и независимый порт считывания, содержащий шину считывания и два последовательно соединенных транзистора n- и p-типов с управлением по затворам от одного из инверторов и адресной шины считывания. Недостатком ячейки памяти является недостаточно высокое быстродействие за счет ограниченного тока считывания через транзистор p-типа. Наиболее близким техническим решением к предлагаемому является двухпортовая ячейка оперативной памяти (Патент США №6917560, Fig.11, G11C 8/00, 8/16, НКИ 365 /230.05, от 12.07.2005). Это устройство, принятое за прототип, содержит два КМДП инвертора с обратными связями, два транзистора записи n-типа с управлением по затворам от адресной шины записи и двух шин данных и два транзистора считывания n-типа, которые включены последовательно между шиной считывания и шиной смещения с управлением по затворам от одного из инверторов и адресной шины считывания. Недостаток этого устройства - ограниченное быстродействие, обусловленное недостаточной величиной тока считывания, поскольку ток считываня определяется транзистором, который является по затвору нагрузкой инвертора и, следовательно, увеличение размеров этого транзистора для увеличения тока считывания и повышения скорости считывания ведет одновременно к уменьшению скорости записи.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства.

Поставленная цель достигается тем, что двухпортовая ячейка оперативной памяти, содержащая два КМДП инвертора, включенных между шиной питания и шиной земли, два транзистора записи n-типа, затворы которых подключены к адресной шине записи, и первый и второй транзисторы считывания n-типа, которые включены последовательно соответственно между шиной смещения и шиной считывания, выход первого КМДП инвертора подключен к затвору первого транзистора считывания n-типа, к входу второго КМДП инвертора и через первый транзистор записи n-типа соединен с прямой шиной данных, выход второго КМДП инвертора подключен к входу первого КМДП инвертора и через второй транзистор записи n-типа соединен с дополняющей шиной данных, затвор второго транзистора считывания n-типа соединен с адресной шиной считывания, содержит транзистор считывания p-типа, который включен параллельно с первым транзистором считывания n-типа и затвор которого соединен с выходои второго КМДП инвертора

Существенными отличительными признаками в указанной совокупности признаков является наличие транзистора считывания p-типа, который включен параллельно с первым транзистором считывания n-типа и затвор которого соединен с выходом второго КМДП инвертора.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства.

Действительно, в известном устройстве порты записи и считывания реализованы на независимых транзисторах n-типа. Скорость записи определяется наибольшей емкостной нагрузкой того инвертора, выход которого соединен с затвором транзистора считывания n-типа. Ток считывания определяется транзисторами считывания n-типа, один из которых является по затвору нагрузкой инвертора, и, следовательно, увеличение размеров этого транзистора для повышения тока и скорости считывания ведет одновремнно к увеличению емкостной нагрузки инвертора и уменьшению скорости записи. В заявленном устройстве при тех же транзисторах считывания n-типа ток считывания увеличен за счет введенного транзистора считывания p-типа, который создает дополнительную емкостную нагрузку только для инвертора с меньшей нагрузкой. При равном размере транзисторов считывания обоих типов наибольшая переключаемая нагрузка инверторов не увеличивается и быстродействие по записи не уменьшается. Параллельно включенные транзисторы считывания n- и p-типов не только обеспечивают больший ток считывания, чем один транзистор n-типа, но и в процессе считывания обеспечивают его более постоянное значение, что в целом ведет к увеличению скорости считывания без уменьшения скорости записи. Новый балланс размеров (в сторону уменьшения) транзисторов считывания n- и p-типов ведет к повышению быстродействия как при записи, так и при считывании.

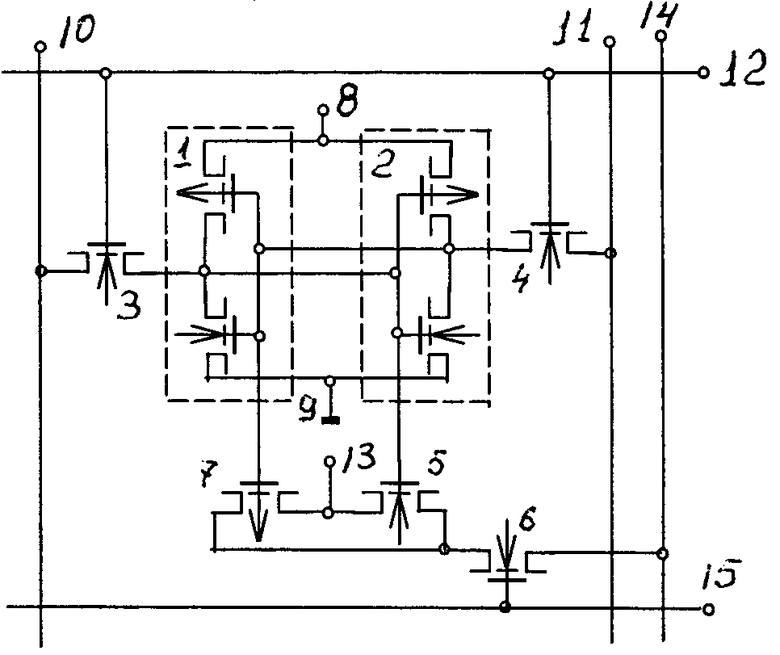

На чертеже приведена принципиальная схема заявляемой двухпортовой ячейки оперативной памяти. Устройство содержит первый 1 и второй 2 КМДП инверторы, первый 3 и второй 4 транзисторы записи n-типа, первый 5, второй 6 транзисторы считывания n-типа и транзистор считывания p-типа 7.

КМДП инверторы 1 и 2 включены между шиной питания 8 и шиной земли 9. Выход первого КМДП инвертора 1 подключен к входу второго КМДП инвертора 2, к затвору первого транзистора считывания 5 n-типа и через первый транзистор записи 3 соединен с прямой шиной данных 10. Выход второго КМДП инвертора 2 подключен к входу первого КМДП инвертора 1, к затвору транзистора считывания p-типа 7 и через второй транзистор записи 4 n-типа соединен с дополняющей шиной данных 11. Затворы транзисторов записи 3 и 4 n-типа подключены к адресной шине записи 12. Первый 5 и второй 6 транзисторы считывания n-типа включены последовательно соответственно между шиной смещения 13 и шиной считывания 14. Транзистор считывания 7 p-типа включен параллельно с первым транзистором считывания 5 n-типа, а затвор второго транзистора считывания 6 n-типа соединен с адресной шиной считывания 15.

Транзисторы записи 3 и 4 n-типа с адресной шиной записи 12 и шинами данных 10 и 11 составляют порт записи. Транзисторы считывания 5 и 6 n-типа и транзистор считывания 7 p-типа совместно с адресной шиной считывания 15 и шиной считывания 14 представляют собой порт считывания.

Устройство работает следующим образом. В состоянии хранения информации выходы инверторов 1 и 2, включенных по схеме триггера, находятся в парафазном статическом состоянии. При записи 1 на прямой шине данных 10 формируется единичный потенциал шины питания, а на дополняющей шине данных 11 - нулевой потенциал шины земли. На адресную шину записи 12 подается единичный потенциал и транзисторы записи 3 и 4 n-типа открываются. Током от прямой шины данных 10 узловая емкость выхода первого инвертора 1 заряжается до единичного потенциала, а током на дополняющую шину данных 11 узловая емкость выхода второго инвертора 2 разряжается до 0. При записи 0 единичный потенциал формируется на дополняющей шине данных 11, а на прямой шине данных 10 - нулевой потенциал.

Режим считывания осуществляется при предварительном формировании на шине считывания 14 потенциала высокого уровня. На адресную шину считывания 15 также подается высокий потенциал. Второй транзистор считывания n-типа 6 при этом открывается. Если в ячейке памяти была записана 1, первый транзистор считывания 5 n-типа открыт с выхода первого инвертора 1, а транзистор считывания 7 p-типа открыт с выхода второго инвертора 2. При этом формируется проводящая цепь между шиной считывания 14 и шиной смещения 13, состоящая из транзистора 7 и параллельно вкченных транзисторов 5 и 7. Током считывания через данную транзисторную цепь емкость шины считывания 14 разряжается до потенциала шины смещения 13, что по команде считывания фиксируется дифференциальным усилителем считывания. Положительный потенциал шины смещения 13, отличный от 0 позволяет снизить перепад потенциалов на шине считывания 14 и сохранить положительное смещение на токовых электродах транзисторов считывания n-типа 5 и 6 для снижения их емкостей, что в сумме также ведет к повышению скорости считывания. Параллельно включенные транзисторы считывания n- и p-типов 5 и 7 не только обеспечивают больший ток считывания, чем один транзистор n-типа, но и в процессе считывания обеспечивают его более постоянное значение, что в целом ведет к увеличению скорости считывания без уменьшения скорости записи.

Если в ячейке памяти был записан 0, первый транзистор считывания 5 n-типа закрыт, поскольку на выходе первого инвертора нулевой потенциал, а транзистор считывания 7 p-типа закрыт, поскольку на выходе второго инвертора высокий потенциал. Первоначальное состояние шины считывания 14 с высоким потенциалом при этом не изменится.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2390860C1 |

| Ячейка оперативного запоминающего устройства | 2018 |

|

RU2688242C1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Многопортовая ячейка оперативного запоминающего устройства | 2017 |

|

RU2665248C1 |

| Порт чтения | 2018 |

|

RU2693331C1 |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

Изобретение относится к области вычислительной техники и может быть использовано для реализации оперативной памяти в микропроцессорных системах. Техническим результатом является повышение быстродействия устройства. Устройство содержит два КМДП инвертора, два транзистора записи n-типа, два транзистора считывания n-типа и транзистор считывания р-типа. Выход первого КМДП инвертора подключен к входу второго КМДП инвертора, к затвору первого транзистора считывания n-типа и через первый транзистор записи соединен с прямой шиной данных. Выход второго КМДП инвертора подключен к входу первого КМДП инвертора, к затвору транзистора считывания р-типа и через второй транзистор записи n-типа соединен с дополняющей шиной данных. Затворы транзисторов записи n-типа подключены к адресной шине записи. Первый и второй транзисторы считывания n-типа включены последовательно между шиной смещения и шиной считывания. Транзистор считывания р-типа включен параллельно с первым транзистором считывания n-типа, а затвор второго транзистора считывания n-типа соединен с адресной шиной считывания. 1 ил.

Двухпортовая ячейка оперативной памяти, содержащая два КМДП инвертора, включенных между шиной питания и шиной земли, два транзистора записи n-типа, затворы которых подключены к адресной шине записи, и первый и второй транзисторы считывания n-типа, которые включены последовательно соответственно между шиной смещения и шиной считывания, выход первого КМДП инвертора подключен к затвору первого транзистора считывания n-типа, к входу второго КМДП инвертора и через первый транзистор записи n-типа соединен с прямой шиной данных, выход второго КМДП инвертора подключен к входу первого КМДП инвертора и через второй транзистор записи n-типа соединен с дополняющей шиной данных, затвор второго транзистора считывания n-типа соединен с адресной шиной считывания, отличающаяся тем, что содержит транзистор считывания р-типа, который включен параллельно с первым транзистором считывания n-типа, и затвор которого соединен с выходом второго КМДП инвертора.

| US 6917560 В2, 12.07.2005 | |||

| US 6909662 В2, 21.06.2005 | |||

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1977 |

|

SU708417A1 |

| Ассоциативная ячейка памяти | 1973 |

|

SU513393A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| US 6181591 B1, 30.01.2001. | |||

Авторы

Даты

2010-06-10—Публикация

2008-12-12—Подача