1

Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств на КМДП-транзисто pax.

Целью изобретения является повышение быстродействия запоминающего устройства за счет организации его работы по реальным задержкам элементов путем индикации моментов окончания .переходных процессов в устройстве.

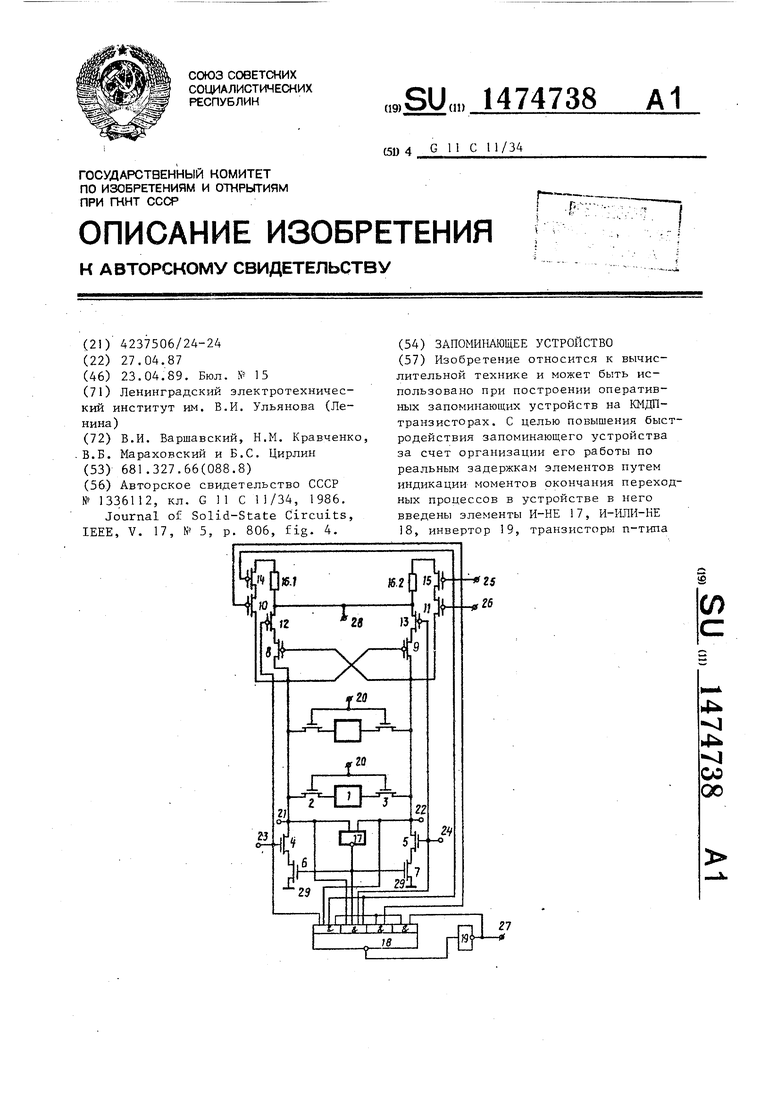

На чертеже приведена схема запоминающего устройства.

Устройство содержит элементы 1 памяти, ключевые элементы, выполнен- ные на МДП-транзисторах п-типа 2 и 3, блок записи, состоящий из четырех МДП-транзисторов п-типа 4-7, блок задания режимов работы, состоящий из восьми МДП-транзисторов р-типа 8-15 и двух резисторов 16, элементы И-НЕ 17, И-ИЛИ-НЕ 18, инвертор 19. На чер-J теже показаны также адресные входы 20, нулевой и единичный информационные выходы 21 и 22 и входы 23 и 24, входы управления записью 25 и чтением 26 и выход 27 готовности устройства, шина 28 питания и шина 29 нулевого потенциала устройства.

Запоминающее устройство работает следующим образом.

В режиме хранения на адресные входы 20 всех элементов 1 памяти подаются низкие потенциалы, закрывающие транзисторы 2 и 3, на входы управле- ния записью 25 и чтением 26 и нулевой 23 и единичный 24 информационные входы также подаются низкие потенциалы. В результате закрыты транзисторы 4, 5 и 8, 9 и открыты транзисторы 10, 11, 14 и 15 и 12 и 13, что при- водит к появлению высоких потенциалов на нулевом 21 и единичном 22 вы

5

0

5 0

5 0

5

0

ходах устройства. Последние вызывают низкий потенциал на выходе элемента 17, высокий потенциал на выходе элемента 18 и, наконец, низкий по тенциал на выходе инвертора 19, т.е. на управляющем выходе 27.

В режиме чтения информации из элемента 1 на адресный вход 20 подается высокий потенциал, открывающий транзисторы 2 и 3, и низкий потенциал с нулевого или единичного входа-выхода этого элемента 1 поступает на выход 21 или 22. Одновременно подается высокий потенциал на вход 26 управления чтением, закрывающий транзисторы 10 и 11. Если низкий потенциал установится на выходе 2Г, то будет открыт транзистор 9 и на выходе 22 будет высокий потенциал, закрывающий транзистор 8. Если же низкий потенциал установится на выходе 22, то будет открыт транзистор 8 и на выходе 21 будет высокий потенциал, закрывающий транзистор 9. В обоих случаях на выходе элемента 17 появится высокий потенциал, на выходе элемента 18 - низкий потенциал, а на выходе инвертора 19, т.е. на управляющем выходе готовности 27 устройства, - высокий потенциал, что является признаком завершения переходных процессов в этом режиме.

В режиме записи информации в элемент 1 памяти на вход 20, как и в предыдущем- случае, подается высокий потенциал, открывающий транзисторы 2 и 3, и низкий потенциал с нулевого или единичного входа-выхода этого элемента 1 памяти поступает на выход 21 или 22. Одновременно подается вы- с.окий потенциал на вход 25 управления записью устройства, закрывающий транзисторы 14 и 15. Далее, как и в

режиме чтения, один из пары транзисторов 8 и 9 открывается, а другой остается закрытым и на выходе элемента 17 появляется высокий потенциал, открывающий транзисторы 6 и 7. Кроме того, на информационные входы 23 и 24 подается информация, записываемая в элемент 1 памяти, т.е. на одном из этих входов устанавливается высокий потенциал. Если этот потенциал устанавливается на входе 23, то открывается транзистор 6 и закрывается транзистор 12,в результате чего на выходе 21 появляется низкий потенциал. Если же высокий потенциал устанавливается на входе 24, то открывается транзистор 7 и закрывается транзистор 13, в результате чего низкий потенциал появляется на выходе 22.

Если информация, установленная на информационных входах 23 и 24 совпадает с ранее записанной в элементе 1 то изменения состояния последнего не происходит и после того, как на выходе элемента I7 появится высокий потенциал, на выходе элемента 18 появится низкий потенциал, а на выходе инвертора 19, т.е. на управляющем выходе 27 устройства, - высокий потенциал, что, как и в режиме чтения, является признаком завершения переходных процессов.

Если же информация, установленная на информационных входах 23 и 24 противоположна ранее записанной в элемент 1, то происходит переключение последнего. При этом несмотря на высокий потенциал на выходе элемента 17 переключение элемента 18 не произойдет до тех пор, пока в элементе 1 не установится требуемое состояние В этом случае сначала на обоих выходах 21 и 22 появятся низкие потенциалы, затем в результате записи информации в элемент 1 на одном из выходо 21 или 22 восстановится высокий потенциал. Только после этого на выход элемента 18 появится низкий потенциал, а на выходе инвертора 19, т.е. на управляющем выходе 27 устройства, высокий потенциал, что является признаком завершения переходных процессов в режиме записи.

Для того, чтобы вернуть устройство в режим хранения, необходимо установить низкие потенциалы на адресном входе 20 и управляющих входах 25 и 26, а также на информационных входах

0

5

0

5

0

5

0

5

0

5

23 и 24. При этом закрываются транзисторы 2-5 и открываются транзистор ры 10, 11 и 14, 15, в результате чего на обоих выходах 21 и 22 восстанавливаются высокие потенциалы, на выходе элемента 17 - низкий потенциал, затем на выходе элемента 18 - высокий потенциал и, наконец, на выходе инвертора 19, т.е. на управляющем выходе 27 устройства, - низкий потенциал, что является признаком завершения переходных процессов в режиме хранения.

Б случае задержки закрывания транзисторов 2 и 3, например из-за запаздывания установки низкого потенциала на адресном входе 20, искажения информации в элементе 1 памяти не происходит, так как выходы 21 и 22 подключены открытыми транзисторами 10, 11 и 14, 15 к шине питания через резисторы 16, что позволяет сохранить низкий потенциал на соответствующем выходе 21 или 22 до тех пор, пока не закроются транзисторы 2 и 3.

Признаком завершения переходных процессов в устройстве при смене режимов является изменение потенциала на управляющем выходе 27 готовности. Этот сигнал появляется по окончании реальных переходных процессов при любых величинах задержек транзисторов устройства. Таким образом, в устройстве индицируются моменты окончания переходных процессов, что позволяет организовать его работу по реальным задержкам, а следовательно, повысить его быстродействие.

Из приведенного описания работы запоминающего устройства видно, что .в любом из режимов устойчивое состояние характеризуется тем, что в каждой из цепей устройства между его шиной питания и шиной нулевого потенциала включен хотя бы один закрытый МДП-транзистор р- или п-типа, что обеспечивает в предлагаемом устройстве столь же низкое потребление энергии, что и в известном.

Формула изобретения

Запоминающееустройство, содержащее элементы памяти и соответствую- . щие им пары ключевых элементов, каждый из которых выполнен на транзисторе n-типа, причем истоки первого

и второго транзисторов n-типа соединены соответственно с нулевым и единичным входами-выходами элемента памяти, затворы являются соответствующим адресным входом устройства, а стоки - нулевым и единичным информационными выходами устройства, блок записи, состоящий из первого и второИ-НЕ и с первыми входами каждой группы И элемента И-ИЛИ-НЕ, выход которого соединен с входом инвертора, выход которого соединен с вторым входом первой группы И элемента И-ИЛИ-НЕ и является выходом готовности устройства, в блок задания режимов работы введены первый и второй резисторы и

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1365129A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1411823A2 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств на КМДП-транзисторах. С целью повышения быстродействия запоминающего устройства за счет организации его работы по реальным задержкам элементов путем индикации моментов окончания переходных процессов в устройстве в него введены элементы И-НЕ 17, И-ИЛИ-НЕ 18, инвертор 19, транзисторы п-типа 6 и 7 и транзисторы р -типа 12-15. Причем выход элемента 17 соединен с затворами транзисторов 6,7 и входами элемента 18, а его входы - с входами элемента 18, другие входы которого соединены с информационными выходами 21,22 и входами 23,24 устройства, с управляющими 25, 26 входами устройства и с его управляющим выходом 27, который соединен с выходом инвертора 19, вход которого соединен с выходом элемента 18. 1 ил.

го транзисторов n-типа, затворы кото- 10 пятый, шестой, седьмой и восьмой

транзисторы р-типа, стоки которых соединены с истоками первого, второго, третьего и четвертого транзисторов р-типа соответственно, затвор

рых являются нулевым и единичным информационными входами устройства, а стоки соединены со стоками соответствующих транзисторов n-типа ключевых элементов, блок задания режимов рабо- 15 четвертого транзистора р-типа соеди- ты, состоящий из четырех транзисторов Нен с вторым входом второй группы И р-типа, причем затворы третьего и четвертого транзисторов р-типа являются входом управления чтением устройэлемента И-ИЛИ-НЕ, затворы седьмого и восьмого транзисторов р-типа соединены с вторыми входами третьей и

ства, затворы первого и второго тран- 2о четвертой групп И элемента И-ИЛИ-НЕ

зисторов р-типа соединены соответственно со стоками второго и четвертого и первого и третьего транзисторов р-типа и со стоками первого и второго транзисторов n-типа ключевых элементов.

отличающееся тем,

что, с целью повышения быстродействия устройства, в него введены элемент И-ИЛИ-НЕ, инвертор и элемент И-НЕ, в блок записи введены третий и четвертый транзисторы n-типа, стоки которых соединены соответственно с истоками первого и второго транзисторов п-ти- па, истоки - с шиной нулевого потенциала, а затворы - с выходом элемента

транзисторы р-типа, стоки которых соединены с истоками первого, второго, третьего и четвертого транзисторов р-типа соответственно, затвор

четвертого транзистора р-типа соеди- Нен с вторым входом второй группы И

четвертого транзистора р-типа соеди- Нен с вторым входом второй группы И

элемента И-ИЛИ-НЕ, затворы седьмого и восьмого транзисторов р-типа соединены с вторыми входами третьей и

и являются входом управления записью устройства, истоки пятого и шестого транзисторов р-типа соединены с шиной питания устройства и через первый и второй резисторы - с истоками седьмого и восьмого транзисторов р-типа, затворы пятого и шестого транзисторов р-типа соединены с третьими входами третьей и четвертой групп И элемента И-ИЛИ-НЕ и с затворами первого и второго транзисторов n-типа блока записи, стоки которых соединены с четвер-| тыми входами четвертой и третьей групп И элемента И-ИЛИ-НЕ соответственно, и с входами элемента И-НЕ.

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Journal of Solid-State Circuits, IEEE, V | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Водоподъемный аппарат | 1923 |

|

SU806A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-04-23—Публикация

1987-04-27—Подача