Изобретение относится к устройствам цифровой вычислительной техники, и может быть использовано в качестве базового элемента при построении многопортовых запоминающих устройств.

Известно «Многопортовое запоминающее устройство» [SU №1718270 A1, G11C 7/00, 07.03.1992], содержащее бистабильный элемент 1 хранения, N портов 2 записи, буферный дифференциальный усилитель 3, М портов 4 считывания, дешифраторы 5-1…5-N записи строк, дешифраторы 6-1…6-N записи столбцов, дешифраторы 7-1…7-М считывания строк, дешифраторы 8-1…8-М считывания столбцов.

Недостатком данного устройства является его довольно сложная конструкция.

Наиболее близким к заявляемому является «Многовходовый логический элемент И на КМДП транзисторах» [RU №2319299 С1, H03K 19/094, 10.03.2008], содержащий элемент И-НЕ, инвертирующий элемент, тактовый транзистор n-типа и тактовый транзистор p-типа, элемент И-НЕ содержит предзарядовый транзистор p-типа, включенный между шиной питания и выходом данного элемента, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, первый вывод ключевой цепи подключен к выходу элемента И-НЕ, а второй вывод через тактовый транзистор n-типа соединен с нулевой шиной, тактовый транзистор p-типа включен между шиной питания и вторым выводом ключевой цепи элемента И-НЕ, инвертирующий элемент содержит логический транзистор р-типа, включенный между шиной питания и выходом устройства, и предзарядовый транзистор n-типа, включенный между выходом устройства и нулевой шиной, затворы тактовых транзисторов и предзарядового транзистора р-типа подключены к тактовой шине, затворы логического транзистора р-типа и предзарядового транзистора n-типа инвертирующего элемента подключены соответственно к выходу элемента И-НЕ и ко второму выводу ключевой цепи элемента И-НЕ, так же содержит дополнительный транзистор n-типа, который включен между выходом элемента И-НЕ и вторым выводом ключевой цепи того же элемента и затвор которого соединен с выходом устройства, причем устройство содержит не менее 8 входов.

Недостатком данного элемента является отсутствие возможности его использования при построении многопортовых запоминающих устройств.

Техническим результатом является расширение функциональных возможностей порта за счет его использования при построении многопортовых запоминающих устройств.

Технический результат достигается тем, в порт чтения, содержащий элемент И-НЕ, n-канальный транзистор и p-канальный транзистор, представляющий собой две динамические схемы, дополнительно введены две локальных битовых шины, глобальная битовая шина и шесть адресных шин, каждая i-я динамическая схема, где i=1, 2, содержит четыре пары последовательно соединенных n-канальных транзисторов, p-канальный транзистор, n-канальный транзистор и выходы ячеек памяти порта, локальные битовые шины динамических схем соединены с первым и вторым входами элемента И-НЕ, выход которого соединен с затвором n-канального транзистора 6, сток которого соединен с корпусом, а исток с динамической глобальной битовой шиной, выход элемента И-НЕ соединен с затвором p-канального транзистора, сток и исток которого соединены соответственно с локальными битовыми шинами динамических схем, первые четыре адресные шины первого уровня выборки соединены с затворами соответственно с первого по четвертый n-канальных транзисторов первой динамической схемы и с затворами с первого по четвертый n-канальных транзисторов второй динамической схемы, пятая адресная шина второго уровня выборки соединена с затворами соответственно р-канального транзистора и n-канального транзистора второй динамической схемы, шестая адресная шина второго уровня выборки соединена с затворами соответственно р-канального транзистора и n-канального транзистора первой динамической схемы, стоки р-канальных транзисторов и n-канальных транзисторов первой и второй динамических схем соединены с корпусом, стоки верхних из каждой пары транзисторов первой динамической схемы и второй динамической схемы соединены со стоками соответственно р-канальных транзисторов, истоки нижних из каждой пары транзисторов первой динамической схемы второй динамической схемы соединены со стоками соответственно n-канальных транзисторов, затворы нижних из каждой пары транзисторов первой динамической схемы второй динамической схемы соединены с соответствующими выходами ячеек памяти порта.

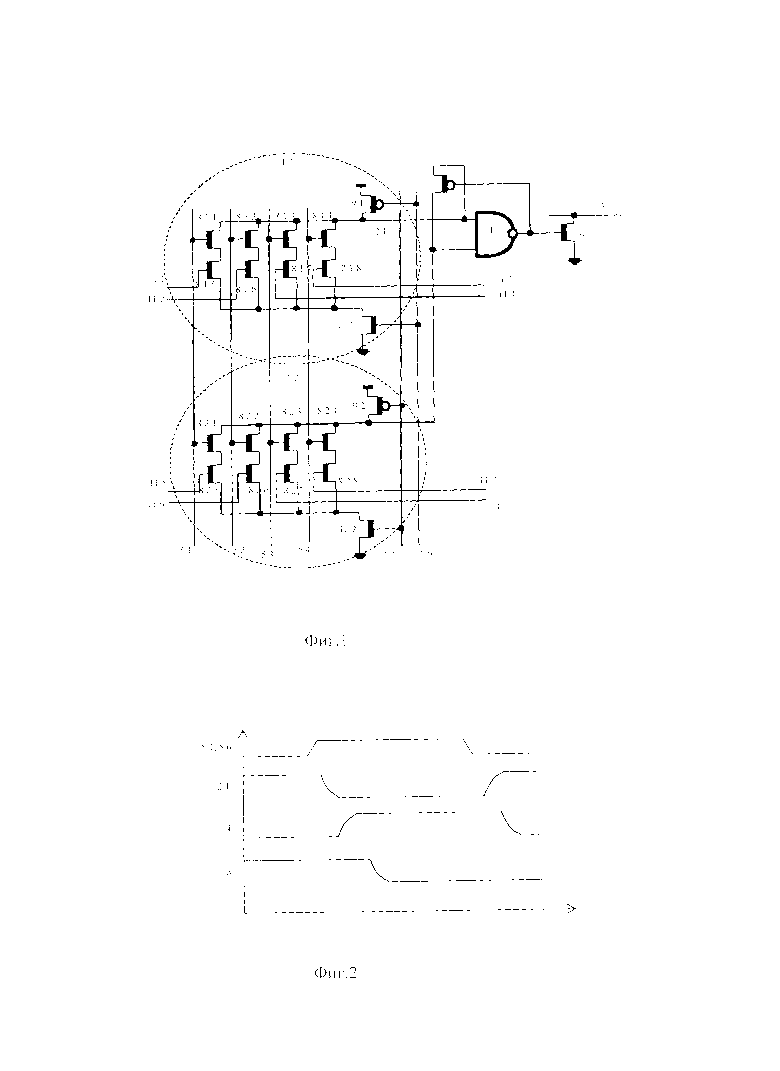

На фиг. 1 представлена схема порта чтения.

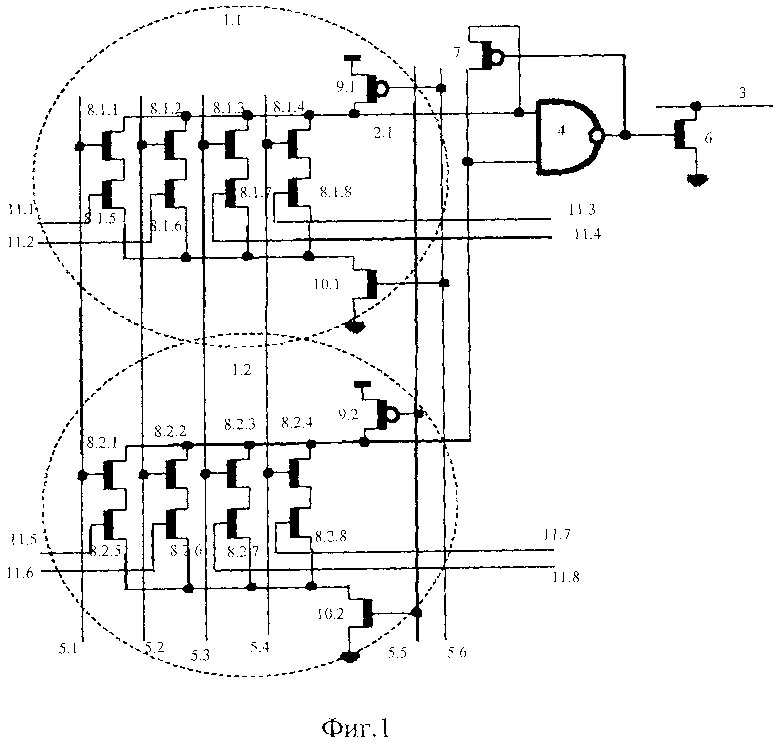

На фиг. 2 представлена временная диаграмма работы порта чтения.

Порт чтения (фиг. 1) содержит две динамические схемы 1.1 и 1.2, две локальных битовых шины 2.1 и 2.2, глобальную битовую шину 3, элемент И-НЕ 4, шесть адресных шин 5.1, 5.2, …, 5.6, n-канальный транзистор 6 и р-канальный транзистор 7, а каждая i-я, где i=1, 2, каждая динамическая схема 1.i содержит четыре пары последовательно соединенных n-канальных транзисторов 8.i.j и 8.i.j+4, где j=1, 2, 3, 4, р-канальный транзистор 9.i, и n-канальный транзистор 10.i и выходы ячеек памяти порта 11.1, 11.2 …, 11.8.

Порт чтения (фиг. 1) содержит две динамические схемы 1.1 и 1.2, две локальных битовых шины 2.1 и 2.2, глобальную битовую шину 3, элемент И-НЕ 4, шесть адресных шин 5.1, 5.2, …, 5.6, n-канальный транзистор 6 и р-канальный транзистор 7, а каждая i-я динамическая схема 1.i, где i=1, 2, содержит четыре пары последовательно соединенных n-канальных транзисторов 8.i.j и 8.i.j+4, где j=1, 2, 3, 4, р-канальный транзистор 9.i, и n-канальный транзистор 10.i и выходы ячеек памяти порта 11.1, 11.2 …, 11.8, локальные битовые шины 2.1 и 2.2 динамических схем 1.1 и 1.2 соединены с первым и вторым входами элемента И-НЕ 4, выход которого соединен с затвором n-канального транзистора 6, сток которого соединен с корпусом, а исток с динамической глобальной битовой шиной 3, выход элемента И-НЕ 4 соединен с затвором р-канального транзистора 7, сток и исток которого соединены соответственно с локальными битовыми шинами 2.1 и 2.2 динамических схем 1.1 и 1.2, первые четыре адресные шины 5.1, 5.2, … 5.4 первого уровня выборки соединены с затворами соответственно с первого по четвертый 8.1.1, 8.1.2, 8.1.3 и 8.1.4 n-канальных транзисторов первой динамической схемы 1.1 и с первого по четвертый 8.2.1, 8.2.2, 8.2.3, 8.2.4 второй динамической схемы 1.2, пятая адресная шина 5.5 второго уровня выборки соединена с затворами соответственно р-канального транзистора 9.2 и n-канального транзистор 10.2 второй динамической схемы 1.2, шестая адресная шина 5.6 второго уровня выборки соединена с затворами соответственно р-канального транзистора 9.1 и n-канального транзистор 10.1 первой динамической схемы 1.1, стоки р-канальных транзисторов 9.1 и 9.2 соединены с шиной питания, стоки n-канальных транзисторов 10.1 и 10.2 первой и второй динамических схем 1.1 и 1.2 соединены с корпусом. Стоки верхних из каждой пары транзисторов 8.1.1, 8.1.2, 8.1.3 и 8.1.4 первой динамической схемы 1.1 и 8.2.1, 8.2.2, 8.2.3, 8.2.4 второй динамической схемы 1.2 соединены со стоками соответственно р-канальных транзисторов 9.1 и 9.2, истоки нижних из каждой пары транзисторов 8.1.5, 8.1.6, 8.1.7 и 8.1.8 первой динамической схемы 1.1 и 8.2.5, 8.2.6, 8.2.7 и 8.2.8 второй динамической схемы 1.2 соединены со стоками соответственно n-канальных транзисторов 10.1 и 10.2. Затворы нижних из каждой пары транзисторов 8.1.5, 8.1.6, 8.1.7 и 8.1.8 первой динамической схемы 1.1 и 8.2.5, 8.2.6, 8.2.7 и 8.2.8 второй динамической схемы 1.2 соединены с соответствующими выходами ячеек памяти порта 11.1, 11.2 …, 11.8.

Схема удержания высокого уровня на локальных битовых шинах 2.1 и 2.2 реализована на р-канальном транзисторе 7, который включен стоком и истоком между локальными битовыми шинами 2.1 и 2.2, а затвором подключен к выходу элемента И-НЕ 4 для обеспечения положительной обратной связи во время считывания информации.

Предзаряд локальных битовых шин 2.1 и 2.2 в динамических схемах 1.1 и 1.2 происходит через р-канальные транзисторы 9.1 и 9.2 соответственно, при отсутствии положительных сигналов на входах 5.5 и 5.6. Это исключает возможность появления помех от перераспределения заряда между локальными битовыми шинами 2.1 и 2.2 и не требует применения отдельного синхронизируемого сигнала управления предзарядом.

Порт чтения (фиг. 1) работает следующим образом. В исходном состоянии, при отсутствии положительных сигналов выборки на адресных шинах 5.1, 5.2, …, 5.6, n-канальные транзисторы 8.1.1-8.1.4, 8.2.1-8.2.4, 10.1 и 10.2 закрыты, р-канальные транзисторы 9.1, 9.2 открыты, локальные битовые шины 2.1 и 2.2 имеют потенциал питания, выход элемента И-НЕ 4 имеет потенциал корпуса, n-канальный транзистор 6 закрыт, глобальная битовая шина 3 предзаряжена к потенциалу питания.

Работа рассматривается на примере считывания из запоминающей ячейки, выход которой подается на шину 11.1. Схема активируется сигналами выборки. На адресные шины 5.1 и 5.6 подается потенциал питания. При этом закрывается р-канальный транзистор 9.1 предзаряда локальной битовой шины 2.1 схемы 1.1, и открываются n-канальные транзисторы 10.1, 8.1.1. Если на выходе 11.1 первой ячейки памяти порта имеется потенциал питания, то локальная битовая шина 2.1 начинает разряжаться через 3 последовательно включенных n-канальных транзистора 8.1.1, 8.1.5 и 10.1 до потенциала корпуса (фиг. 2.).

Выход элемента И-НЕ 4 получает потенциал питания, и открывается n-канальный транзистор 6, через который глобальная битовая шина 3 разряжается до потенциала корпуса.

В случае, когда на выходе первой ячейки памяти порта 11.1 имеется потенциал корпуса, то n-канальный транзистор 8.1.5 остается закрытым, и локальная битовая шина 2.1 сохраняет потенциал питания, который поддерживается через открытые последовательно соединенные р-канальные транзисторы 9.2 и 7. Выход элемента И-НЕ 4 имеет при этом потенциал корпуса, n-канальный транзистор 6 закрыт, глобальная битовая шина 3 сохраняет потенциал питания.

Таким образом, порт чтения обеспечивает возможность использования его при построении многопортовых запоминающих устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2674935C1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2013 |

|

RU2541854C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2012 |

|

RU2496227C1 |

| Устройство контроля сопротивления резистивного элемента | 1988 |

|

SU1700744A1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

Изобретение относится к устройствам цифровой вычислительной техники и может быть использовано в качестве базового элемента при построении многопортовых запоминающих устройств. Техническим результатом является расширение функциональных возможностей порта за счет его использования при построении многопортовых запоминающих устройств. Порт чтения содержит две динамические схемы, две локальные битовые шины, глобальную битовую шину, элемент И-НЕ, шесть адресных шин, n-канальный транзистор и р-канальный транзистор, а каждая i-я динамическая схема, где i=1,2, содержит четыре пары последовательно соединенных n-канальных транзисторов, р-канальный транзистор, n-канальный транзистор и выходы ячеек памяти порта. 2 ил.

Порт чтения, содержащий элемент И-НЕ, n-канальный транзистор и р-канальный транзистор, представляющий собой две динамические схемы, отличающийся тем, что в него дополнительно введены две локальные битовые шины, глобальная битовая шина и шесть адресных шин, каждая i-я динамическая схема, где i=1, 2, содержит четыре пары последовательно соединенных n-канальных транзисторов, р-канальный транзистор, n-канальный транзистор и выходы ячеек памяти порта, локальные битовые шины динамических схем соединены с первым и вторым входами элемента И-НЕ, выход которого соединен с затвором n-канального транзистора 6, сток которого соединен с корпусом, а исток - с динамической глобальной битовой шиной, выход элемента И-НЕ соединен с затвором р-канального транзистора, сток и исток которого соединены соответственно с локальными битовыми шинами динамических схем, первые четыре адресные шины первого уровня выборки соединены с затворами соответственно с первого по четвертый n-канальных транзисторов первой динамической схемы и с затворами с первого по четвертый n-канальных транзисторов второй динамической схемы, пятая адресная шина второго уровня выборки соединена с затворами соответственно р-канального транзистора и n-канального транзистора второй динамической схемы, шестая адресная шина второго уровня выборки соединена с затворами соответственно р-канального транзистора и n-канального транзистора первой динамической схемы, стоки р-канальных транзисторов и n-канальных транзисторов первой и второй динамических схем соединены с корпусом, стоки верхних из каждой пары транзисторов первой динамической схемы и второй динамической схемы соединены со стоками соответственно р-канальных транзисторов, истоки нижних из каждой пары транзисторов первой динамической схемы второй динамической схемы соединены со стоками соответственно n-канальных транзисторов, затворы нижних из каждой пары транзисторов первой динамической схемы и второй динамической схемы соединены с соответствующими выходами ячеек памяти порта.

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Токарный резец | 1924 |

|

SU2016A1 |

| US 8971096 B2, 03.03.2015 | |||

| ЭЛЕМЕНТ ПАМЯТИ | 1991 |

|

RU2006967C1 |

| US 6469328 B2, 22.10.2002 | |||

| US 4833648 A1, 23.05.1989. | |||

Авторы

Даты

2019-07-02—Публикация

2018-02-07—Подача