Изобретение относится к электронным схемам общего назначения и может быть использовано в системах автоматического управления для ограничения сигналов в дополнительном цифровом коде, превышающих динамический диапазон, в частности в радиолокационных станциях для подавления пассивных помех.

Известны методы ограничения сигналов, приведенные в книге В.Каппелини и др. «Цифровые фильтры и их применение». - М.: Энергоатомиздат, 1983, (стр.159).

Для исключения разрядов, превышающих длину регистров, применяются следующие методы:

- усечение, т.е. отбрасывание лишних разрядов;

- аппроксимация на низшем уровне, т.е. когда число принимает то же значение, что и в первом методе, если отбрасываемая часть меньше половины цены младшего разряда представления;

- округление, т.е. когда число увеличивается на единицу, если отбрасываемая часть половина или больше половины цены младшего разряда представления.

Однако данные методы и устройства для их реализации применимы для исключения младших разрядов.

Известно устройство для преобразования динамического диапазона выходного сигнала, которое содержит квадратурный фазовращатель, корректор, квадратичные детекторы, сумматоры, аналоговые делители (а.с. СССР №1058077, кл. Н04В 1/64).

Известно также устройство для преобразования динамического диапазона звукового сигнала, которое содержит квадратурный фазовращатель, аналоговые делители, квадратичные детекторы, сумматоры, блоки коррекции, вычитатель (а.с. СССР №1363489, кл. Н04В 1/64).

Данные устройства предназначены для преобразования динамического диапазона путем коррекции частотной характеристики в области высоких частот, в частности преобразования динамического диапазона звуковых сигналов. В случае, когда входные сигналы превышают динамический диапазон, производится преобразование, в результате которого в выходных сигналах устанавливается соотношение уровней, аналогично их соотношению на входе.

Недостатком данных устройств является то, что входные сигналы, лежащие за пределом динамического диапазона, например инфразвуковое, ультразвуковое, инфракрасное, ультрафиолетовое излучение, т.е. превышающее предел восприятия, также преобразуются, что ведет к усложнению устройства и снижению надежности.

Задачей, на решение которой направлено изобретение, является создание устройства, позволяющего преобразовать сигналы, превышающие динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов, что позволяет повысить надежность и упростить конструкцию

Эта задача решается тем, что ограничитель в дополнительном коде для цифрового тракта выполнен в виде электрической схемы типа мультиплексора, содержащей логический элемент И-НЕ, логический элемент ИЛИ, логический элемент НЕ, первый и второй логические элементы И, первый и второй коммутаторы. Устройство содержит k входов отбрасываемых разрядов, n входов преобразуемых разрядов, вход знакового разряда, вход логической 1, при этом k входы отбрасываемых разрядов соединены с k входами логических элементов И-НЕ и ИЛИ, выход логического элемента И-НЕ соединен с первым входом первого логического элемента И, выход логического элемента ИЛИ соединен с первым входом второго логического элемента И. Вход знакового разряда соединен с входом логического элемента НЕ, с вторым входом первого логического элемента И и с адресным входом первого коммутатора. Выход логического элемента НЕ соединен с вторым входом второго логического элемента И и с (n-1) входами всех разрядов, кроме младшего, n-разрядного сигнала первого информационного входа второго коммутатора. Вход логической 1 соединен с входом младшего разряда n-разрядного сигнала первого информационного входа второго коммутатора, n входов преобразуемых разрядов соединены с n вторыми информационными входами второго коммутатора. Выход первого логического элемента И соединен с первым информационным входом первого коммутатора, выход второго логического элемента И соединен с вторым информационным входом первого коммутатора. Выход первого коммутатора соединен с адресным входом второго коммутатора, выходы второго коммутатора являются выходами n преобразованных разрядов.

За счет комбинационной логической схемы производится преобразование входных сигналов, превышающих динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов.

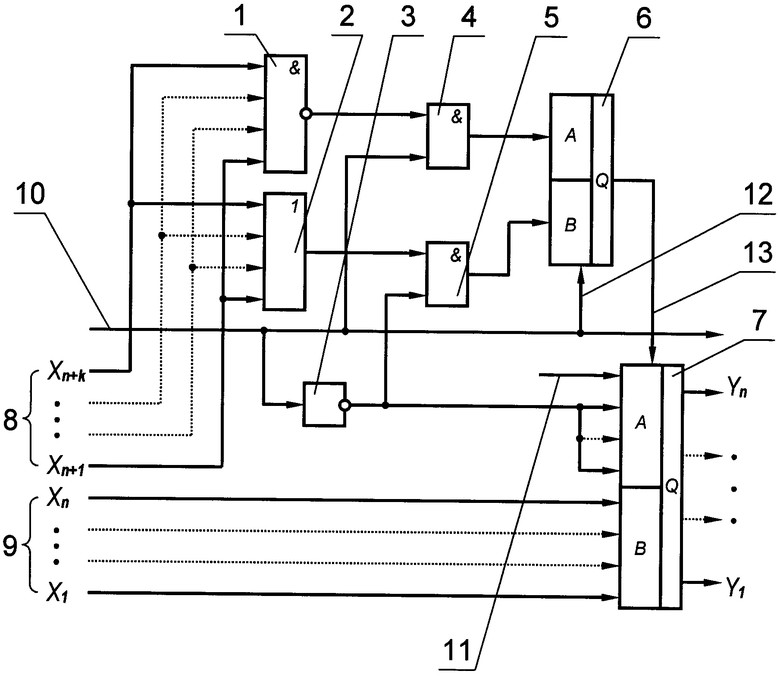

На чертеже приведена электрическая принципиальная схема ограничителя в дополнительном коде для цифрового тракта.

Устройство содержит логический элемент И-НЕ 1, логический элемент ИЛИ 2, логический элемент НЕ 3, первый логический элемент И 4, второй логический элемент И 5, первый коммутатор 6, второй коммутатор 7, входы Xn+k 8 отбрасываемых разрядов, входы Xn 9 преобразуемых разрядов, вход знакового разряда 10, вход логической 1 11, адресный вход 12 первого коммутатора 6, адресный вход 13 второго коммутатора 7. Входы Xn+k 8 отбрасываемых разрядов соединены с k входами логических элементов И-НЕ 1 и ИЛИ 2. Выход логического элемента И-НЕ 1 соединен с первым входом первого логического элемента И 4, выход логического элемента ИЛИ 2 соединен с первым входом второго логического элемента И 5. Вход знакового разряда 10 соединен с входом логического элемента НЕ 3, с вторым входом первого логического элемента И 4 и с адресным входом 12 первого коммутатора 6. Выход логического элемента НЕ 3 соединен с вторым входом второго логического элемента И 5 и с (n-1) входами всех разрядов, кроме младшего, n-разрядного сигнала первого информационного входа А второго коммутатора 7. Вход логической 1 11 соединен с входом младшего разряда n-разрядного сигнала первого информационного входа А второго коммутатора 7. Входы Xn 9 преобразуемых разрядов соединены с n вторыми информационными входами В второго коммутатора 7. Выход первого логического элемента И 4 соединен с первым информационным входом А первого коммутатора 6, выход второго логического элемента И 5 соединен с вторым информационным входом В первого коммутатора 6. Выход Q первого коммутатора 6 соединен с адресным входом 13 второго коммутатора 7. Выходы Q коммутатора 7 являются выходами Yn преобразованных разрядов.

В таблице 1 приведено состояние выходов Q первого коммутатора 6 и второго коммутатора 7.

В таблице 2 приведено соответствие входящих Xn+k и выходящих Yn сигналов при n=3 и k=2.

Ограничитель в дополнительном коде для цифрового тракта работает следующим образом.

На входы Xn+k 8 и входы Xn 9 поступает (n+k)-разрядный сигнал, причем k отбрасываемых разрядов поступают на входы Xn+k 8, n преобразуемых разрядов поступают на вход Xn 9. На вход знакового разряда 10 поступает логический 0 или логическая 1.

Если на входе знакового разряда 10 логический 0, на выходе Q первого коммутатора 6 повторяется второй информационный вход В (см. табл.1).

Если все k отбрасываемых разрядов, поступивших на входы Xn+k 8, имеют логический 0, то на выходе второго логического элемента И 5 и на выходе Q первого коммутатора 6 будет логический 0. Т.к. на адресном входе 13 второго коммутатора 7 логический 0, на выходе Q второго коммутатора 7 повторяется второй информационный вход В (см. табл.1), т.е. n разрядов сигнала, поступивших на входы Xn 9 (см. табл.2).

Если хотя бы один из k разрядов сигнала, поступивших на входы Xn+k 8, имеет логическую 1, то на выходе логического элемента И 5 и на выходе Q первого коммутатора 6 будет логическая 1. Т.к. на адресном входе 13 второго коммутатора 7 логическая 1, на выходе Q второго коммутатора 7 повторяется первый информационный вход А (см. табл.1), т.е. все n разрядов сигнала будут иметь логическую 1. Преобразованный сигнал будет иметь максимальное положительное значение динамического диапазона (см. табл.2).

Если на входе знакового разряда 10 логическая 1, на выходе Q первого коммутатора 6 повторяется первый информационный вход А (см. табл.1).

Если все k отбрасываемых разрядов, поступивших на входы Xn+k 8, имеют логическую 1, то на выходе первого логического элемента И 4 и на выходе Q первого коммутатора 6 будет логический 0. Т.к. на адресном входе 13 второго коммутатора 7 логический 0, на выходе Q второго коммутатора 7 повторяется второй информационный вход В (см. табл.1), т.е. n разрядов сигнала, поступивших на входы Xn 9 (см. табл.2).

Если хотя бы один из k разрядов сигнала, поступивших на входы Xn+k 8, имеет логический 0, то на выходе первого логического элемента И 4 и на выходе Q первого коммутатора 6 будет логическая 1. Т.к. на адресном входе 13 второго коммутатора 7 логическая 1, на выходе Q второго коммутатора 7 повторяется первый информационный вход А (см. табл.1), т.е. по входу логической 1 11 младший разряд будет иметь логическую 1, а остальные (n-1) разрядов сигнала будут иметь логический 0. Преобразованный сигнал будет иметь минимальное отрицательное значение динамического диапазона (см. табл.2).

Таким образом, ограничитель в дополнительном коде обеспечивает преобразование сигналов, превышающих динамический диапазон, из (n+k)-разрядных в n-разрядные с отбрасыванием k старших и преобразованием n младших разрядов, что позволяет повысить надежность и упростить конструкцию.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОГРАНИЧИТЕЛЬ В ДОПОЛНИТЕЛЬНОМ КОДЕ | 2010 |

|

RU2439790C1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для арифметического разложения логических функций | 1989 |

|

SU1633388A1 |

Изобретение относится к электронным схемам общего назначения и может быть использовано в системах автоматического управления для ограничения сигналов в дополнительном цифровом коде, превышающих динамический диапазон, в частности в радиолокационных станциях для подавления пассивных помех. Технический результат - повышение надежности. Устройство выполнено в виде электрической схемы типа мультиплексора, содержащей логические элементы И, И-НЕ, ИЛИ, НЕ и коммутаторы. В случае, когда сигнал превышает динамический диапазон, производится его преобразование из (n+k)-разрядного в n-разрядный с отбрасыванием k старших и преобразованием n младших разрядов. 1 ил., 2 табл.

Ограничитель в дополнительном коде для цифрового тракта, отличающийся тем, что содержит логический элемент И-НЕ, логический элемент ИЛИ, логический элемент НЕ, первый и второй логические элементы И, первый и второй коммутаторы, k входов отбрасываемых разрядов, n входов преобразуемых разрядов, вход знакового разряда, вход логической 1, причем k входов отбрасываемых разрядов соединены с k входами логических элементов И-НЕ и ИЛИ, выход логического элемента И-НЕ соединен с первым входом первого логического элемента И, выход логического элемента ИЛИ соединен с первым входом второго логического элемента И, вход знакового разряда соединен с входом логического элемента НЕ, с вторым входом первого логического элемента И и с адресным входом первого коммутатора, выход логического элемента НЕ соединен с вторым входом второго логического элемента И и с (n-1) входами всех разрядов, кроме младшего, n-разрядного сигнала первого информационного входа второго коммутатора, вход логической 1 соединен с входом младшего разряда n-разрядного сигнала первого информационного входа второго коммутатора, n входов преобразуемых разрядов соединены с n вторыми информационными входами второго коммутатора, выход первого логического элемента И соединен с первым информационным входом первого коммутатора, выход второго логического элемента И соединен с вторым информационным входом первого коммутатора, выход первого коммутатора соединен с адресным входом второго коммутатора, выходы коммутатора являются выходами n преобразованных разрядов.

| КАППЕЛИНИ В | |||

| и др | |||

| Цифровые фильтры и их применение | |||

| - М.: Энергоатомиздат, 1983, с.159 | |||

| Устройство для преобразования динамического диапазона звуковых сигналов | 1982 |

|

SU1058077A1 |

| Устройство для преобразования динамического диапазона звуковых сигналов | 1986 |

|

SU1363489A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1998 |

|

RU2145422C1 |

| АМПЛИТУДНЫЙ ОГРАНИЧИТЕЛЬ | 1985 |

|

SU1840049A1 |

Авторы

Даты

2010-11-27—Публикация

2008-12-04—Подача