Изобретение относится к области вычислительной техники и может быть использовано для реализации КМДП логических устройств конвейерного типа.

Известен тактируемый логический элемент с функцией И типа «домино» на КМДП транзисторах (патент РФ №2275737, H03K 19/01, 19/094 от 06.12.2004). Он содержит последовательно включенные тактируемый элемент И-НЕ с предзарядовым транзистором p-типа в качестве нагрузки и инвертирующий элемент с логическим транзистором p-типа и предзарядовым транзистором n-типа. Недостатком элемента является низкое быстродействие, что обусловлено медленным процессом переключения элемента ИЛИ-НЕ при большом числе логических входов.

Наиболее близким техническим решением к предлагаемому является многовходовой логический элемент И на КМДП транзисторах (патент РФ №2319299, H03K 19/017, 19/094 от 13.11.2006). Это устройство, принятое за прототип, содержит тактируемый элемент И-НЕ, тактируемый в противофазе инвертирующий элемент с предзарядовым транзистором n-типа и транзистор обратной связи n-типа. Элемент И-НЕ содержит предзарядовый транзистор p-типа и логическую часть в виде ключевой цепи, выполненной на последовательно соединенных транзисторах n-типа.

Недостаток этого устройства - ограниченное быстродействие, что связано с медленным процессом включения транзистора обратной связи при большом числе входов по И при значительной нагрузке на выходе устройства.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства. Поставленная цель достигается тем, что тактируемый многовходовый элемент И, содержащий элемент И-НЕ, инвертирующий элемент, тактовый транзистор n-типа, тактовый транзистор p-типа и транзистор обратной связи n-типа, элемент И-НЕ содержит предзарядовый транзистор p-типа, включенный между шиной питания и выходом данного элемента, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, инвертирующий элемент содержит логический транзистор p-типа, включенный между шиной питания и выходом устройства, и предзарядовый транзистор n-типа, включенный между выходом устройства и нулевой шиной, первый вывод ключевой цепи соединен с выходом элемента И-НЕ и с затвором логического транзистора p-типа, затворы тактового транзистора p-типа и предзарядового транзистора p-типа подключены к тактовой шине, а также содержит дополнительную ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, и транзистор обратной связи p-типа, первый вывод дополнительной ключевой цепи подключен к затвору транзистора обратной связи p-типа и через тактовый транзистор p-типа соединен с шиной питания, второй вывод дополнительной ключевой цепи подключен к противофазной тактовой шине, второй вывод ключевой цепи соединен через транзистор обратной связи n-типа с нулевой шиной, затвор транзистора обратной связи n-типа через тактовый транзистор n-типа соединен с нулевой шиной, а через транзистор обратной связи p-типа соединен с шиной питания, затворы тактового транзистора n-типа и предзарядового транзистора n-типа подключены к противофазной тактовой шине.

Существенным отличительным признаком в указанной совокупности признаков является наличие дополнительной ключевой цепи и транзистора обратной связи p-типа, которые в совокупности с новыми связями и известными признаками формируют две логические цепи на транзисторах n-типа, включенные последовательно-параллельно, и две цепи обратной связи с малыми входными и выходными емкостными нагрузками.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства. В известном устройстве на полутакте - включения элемента происходит разряд емкостной нагрузки выхода элемента И-НЕ через всю ключевую цепь. Транзистор обратной связи n-типа включается достаточно поздно, когда напряжение на выходе элемента И-НЕ падает до величины, равной сумме пороговых напряжений транзисторов обоих типов, т.е. примерно до половины напряжения питания. Ускорение включения происходит только на второй половине фронта выходного сигнала. Причем при большой нагрузке на выходе устройства логический транзистор не может обеспечить высокое быстродействие, т.к. он сам является нагрузкой ключевой цепи. В предлагаемом устройстве на том же полутакте дополнительная ключевая цепь обеспечивает быстрый разряд минимальной емкости нагрузки (затвора транзистора обратной связи p-типа) и включение первого контура обратной связи, после чего включается второй контур обратной связи - транзистор обратной связи n-типа. В результате выходная емкость элемента И-НЕ разряжается только через данный транзистор и ключевую цепь. Количество транзисторов n-типа в обоих ключевых цепях (при их общем числе, равном числу входов по функции И) в зависимости от величины нагрузки на выходе устройства выбирается на основе требуемой чистой задержки включения и длительности фронта нарастания выходного сигнала.

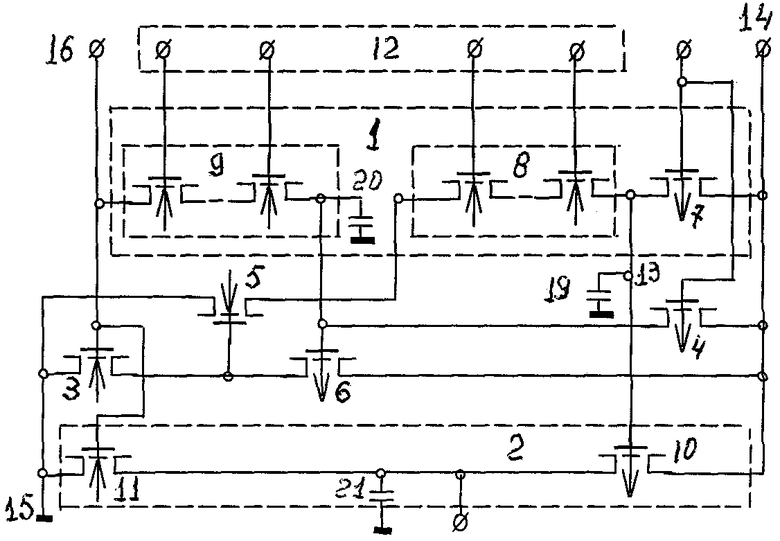

На чертеже приведена принципиальная схема заявляемого тактируемого многовходового элемента И.

Устройство содержит элемент И-НЕ 1, инвертирующий элемент 2, тактовый транзистор 3 n-типа, тактовый транзистор 4 p-типа, транзистор обратной связи 5 n-типа и транзистор обратной связи 6 p-типа. Элемент И-НЕ 1 содержит предзарядовый транзистор 7 p-типа, ключевую цепь 8 и дополнительную ключевую цепь 9. Инвертирующий элемент 2 содержит логический транзистор 10 p-типа и предзарядовый транзистор 11 n-типа.

Ключевые цепи 8 и 9 выполнены на последовательно соединенных транзисторах n-типа, затворы которых подключены к входам 12 устройства. Первый вывод ключевой цепи 8 соединен с выходом 13 элемента И-НЕ, с затвором логического транзистора 10 p-типа и через предзарядовый транзистор 7 p-типа соединен с шиной питания 14. Второй вывод ключевой цепи 8 через транзистор обратной связи 5 n-типа подключен к нулевой шине 15. Первый вывод дополнительной ключевой цепи 9 соединен с затвором транзистора обратной связи 6 p-типа и через тактовый транзистор 4 p-типа соединен с шиной питания 14. Второй вывод дополнительной ключевой цепи 9 подключен к противофазной тактовой шине 16, с которой соединены также затворы тактового 3 и предзарядового 11 транзисторов n-типов.

Затворы тактового транзистора 4 p-типа и предзарядового транзистора 7 p-типа соединены с тактовой шиной 17. Выход инвертирующего элемента 2 соединен через предзарядовый транзистор 11 n-типа с нулевой шиной 15, через логический транзистор 10 p-типа - с шиной питания 14 и соединен непосредственно с выходом 18 устройства.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 17 тактовый транзистор 4 и предзарядовый транзистор 7 p-типов открыты, емкостные нагрузки 19 и 20 заряжены до напряжения питания. На противофазной тактовой шине 16 при этом сигнал высокого уровня, тактовый 3 и предзарядовый 11 транзисторы n-типа открыты, транзисторы 5 и 6 обратной связи и логический транзистор 10 закрыты. Ключевые цепи 8 и 9 не проводят и на выходе 18 устройства - сигнал низкого уровня. На входах 12 устройства при этом устанавливаются сигналы, соответствующие входным переменным. Если хотя бы на одном из входов 12 сигнал логического 0 - низкого уровня, одна из ключевых цепей 8 или 9 будет закрыта, логический транзистор 10 также будет закрыт и состояние выхода 18 устройства не изменится (логический 0) даже при подаче тактовых сигналов.

На втором полутакте на тактовую шину 17 подается сигнал высокого уровня, и транзисторы 4 и 7 p-типа закрываются, на противофазной тактовой шине 16 сигнал низкого уровня и транзисторы 3 и 11 n-типа закрываются. Если все сигналы, подаваемые на входы 12 устройства согласно функции И, соответствуют высокому уровню, ключевые цепи 8 и 9 находятся в проводящем состоянии. Узловая емкость 20 (затвор транзистора обратной связи 6 p-типа с минимальными размерами) быстро разряжается через дополнительную ключевую цепь 9, и данный транзистор 6 открывается, что ведет к открытию транзистора обратной связи 5 n-типа. Узловая емкость 19, величина которой определяется размером логического транзистора 10, разряжается через ключевую цепь 8 и транзистор обратной связи 5, и логический транзистор 10 p-типа открывается. На узловой емкости 21 выходной нагрузки формируется положительный сигнал, соответствующий логической 1.

Количество транзисторов n-типа в обоих ключевых цепях (при их общем числе, равном числу входов по функции И) в зависимости от величины нагрузки на выходе устройства выбирается на основе требуемой чистой задержки включения и длительности фронта нарастания выходного сигнала. Увеличение числа транзисторов n-типа в дополнительной ключевой цепи 9 ведет к возрастанию доли чистой задержки включения элемента в общей задержке на выходе и одновременно ведет к сокращению фронта нарастания сигнала на выходе. Увеличение числа транзисторов n-типа в ключевой цепи 8 ведет к уменьшению доли чистой задержки включения элемента в общей задержке на выходе и одновременно ведет к удлинению фронта нарастания сигнала на выходе. Эффект существенного повышения быстродействия - уменьшения общей задержки на выходе устройства относительно тактового сигнала наиболее выражен при большой выходной нагрузке.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2007 |

|

RU2334354C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| Многовходовый логический элемент И | 2015 |

|

RU2613853C2 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2015 |

|

RU2580095C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

Изобретение относится к области вычислительной техники и может быть использовано для реализации КМДП логических устройств конвейерного типа. Достигаемый технический результат - повышение быстродействия устройства. Тактируемый многовходовый элемент И содержит элемент И-НЕ (1), инвертирующий элемент (2), тактовый транзистор n-типа (3), тактовый транзистор p-типа (4), транзистор обратной связи n-типа (5) и транзистор обратной связи p-типа (6). Элемент И-НЕ (1) содержит предзарядовый транзистор p-типа (7), ключевую цепь (8) и дополнительную ключевую цепь (9). Инвертирующий элемент (2) содержит логический транзистор p-типа (10) и предзарядовый транзистор n-типа (11). Ключевые цепи (8) и (9) выполнены на последовательно соединенных транзисторах n-типа, затворы которых являются входами устройства. 1 ил.

Тактируемый многовходовый элемент И, содержащий элемент И-НЕ, инвертирующий элемент, тактовый транзистор n-типа, тактовый транзистор p-типа и транзистор обратной связи n-типа, элемент И-НЕ содержит предзарядовый транзистор p-типа, включенный между шиной питания и выходом данного элемента, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, инвертирующий элемент содержит логический транзистор p-типа, включенный между шиной питания и выходом устройства, и предзарядовый транзистор n-типа, включенный между выходом устройства и нулевой шиной, первый вывод ключевой цепи соединен с выходом элемента И-НЕ и с затвором логического транзистора p-типа, затворы тактового транзистора p-типа и предзарядового транзистора p-типа подключены к тактовой шине, отличающийся тем, что содержит дополнительную ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, и транзистор обратной связи p-типа, первый вывод дополнительной ключевой цепи подключен к затвору транзистора обратной связи p-типа и через тактовый транзистор p-типа соединен с шиной питания, второй вывод дополнительной ключевой цепи подключен к противофазной тактовой шине, второй вывод ключевой цепи соединен через транзистор обратной связи n-типа с нулевой шиной, затвор транзистора обратной связи n-типа через тактовый транзистор n-типа соединен с нулевой шиной, а через транзистор обратной связи p-типа соединен с шиной питания, затворы тактового транзистора n-типа и предзарядового транзистора n-типа подключены к противофазной тактовой шине.

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| CN 101547004 А, 30.09.2009 | |||

| US 2007176642 A1, 02.08.2007. | |||

Авторы

Даты

2011-02-20—Публикация

2009-10-02—Подача