Изобретение относится к области вычислительной техники и может быть использовано для реализации каскадных логических устройств конвейерного типа.

Известен тактируемый логический элемент с функцией И-ИЛИ на КМДП транзисторах (Патент РФ №2368072, от 24.03.2008, МКИ H03K 19/01). В нем используются логический блок в виде ключевых цепей на транзисторах n-типа, тактовый, предзарядовый и логический транзисторы p-типа и тактовый транзистор n-типа Недостаток этого устройства - избыточная потребляемая мощность при переключении элемента в состояние логической 1 в следствие тока, протекающего через открытый предзарядовый транзистор p-типа. Наиболее близким техническим решением к предлагаемому является тактируемый логический элемент И-ИЛИ (Патент РФ №2515702, от 18.3.2014, МКИ H03K 19/20). Это устройство, принятое за прототип, содержит логический блок в виде ключевых цепей на транзисторах n-типа, тактовый, предзарядовый и логический транзисторы p-типа и тактовый транзистор n-типа. Недостаток этого устройства - избыточная сложность, как следствие наличия двух шин питания и двух тактовых шин.

Техническим результатом изобретения является упрощение устройства. Технический результат достигается тем, что динамический логический элемент И-ИЛИ, содержит тактовый, предзарядовый и логический транзисторы p-типа, тактовый транзистор n-типа и логический блок, содержащий ключевые цепи, включенные параллельно между выходом логического блока и тактовой шиной, к которой подключен также затвор тактового транзистора n-типа, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, логический транзистор p-типа, затвор которого соединен с выходом логического блока, включен между выходом элемента и противофазной тактовой шиной, тактовый транзистор p-типа, затвор которого соединен с противофазной тактовой шиной, включен последовательно с предзарядовым транзистором p-типа, затвор которого соединен с выходом элемента, а соединенные последовательно предзарядовый и тактовый транзисторы p-типа включены между выходом логического блока и тактовой шиной, а тактовый транзистор n-типа включен между выходом элемента и противофазной тактовой шиной.

Существенными отличительными признаками в указанной совокупности признаков является включение соединенных последовательно предзарядового и тактового транзисторов p-типа между выходом логического блока и тактовой шиной, а также включение тактового транзистора n-типа между выходом элемента и противофазной тактовой шиной. Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - упрощение устройства. В устройстве-прототипе используются две шины питания и две тактовые шины. В заявленном устройстве две шины питания совмещены с тактовыми шинами, т.е. устройство содержит на две шины меньше.

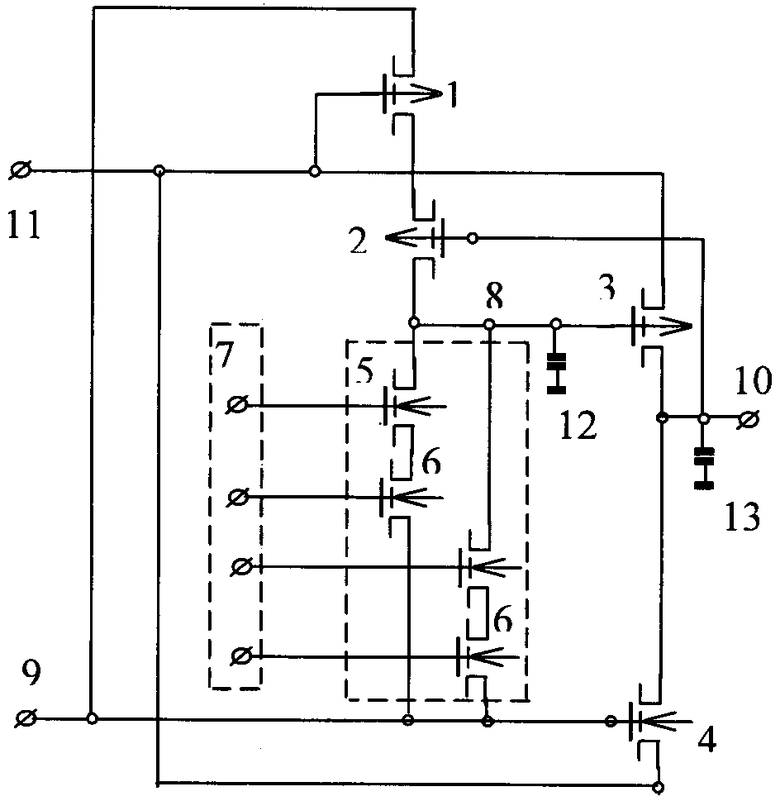

На чертеже приведена принципиальная схема заявленного устройства на примере двух двухвходовых элементов И (элемента 2И-2ИЛИ).

Динамический логический элемент И-ИЛИ, содержит тактовый 1, предзарядовый 2 и логический 3 транзисторы p-типа, тактовый 4 транзистор n-типа и логический блок 5, содержащий ключевые цепи 6, каждая из которых состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам 7 элемента, ключевые цепи 6 включены параллельно между выходом 8 логического блока 5 и тактовой шиной 9, к которой подключен также затвор тактового транзистора 4 n-типа, соединенные последовательно предзарядовый 2 и тактовый 1 транзисторы p-типа включены между выходом 8 логического блока 5 и тактовой шиной 9, логический транзистор 3 p-типа, затвор которого соединен с выходом 8 логического блока 5, включен между выходом 10 элемента и противофазной тактовой шиной 11, затворы предзарядового 2 и тактового 1 транзисторов p-типа подключены соответственно к выходу 10 элемента и к противофазной тактовой шине 11, а тактовый транзистор 4 n-типа включен между выходом 10 элемента и противофазной тактовой шиной 11.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при положительном сигнале на тактовой шине 9 (на противофазной тактовой шине 11 нулевой сигнал) тактовый транзистор 4 n-типа открыт, логический транзистор 3 p-типа работает в инверсионном режиме и конденсатор 13, представляющий собой узловую нагрузку, разряжается до 0. Ключевые цепи 6 и 7 либо закрыты, либо работают в инверсионном режиме. Тактовый транзистор 1 p-типа открывается и конденсатор 12, являющийся узловой емкостью, через открытый предзарядовый транзистор 1 p-типа заряжается до напряжения питания. Логический транзистор 3 p-типа при этом закрывается. На первом полутакте на логических входах 7 устанавливаются сигналы, соответствующие выполняемой функции.

На втором полутакте - на тактовую шину 9 поступает нулевой, а на противотактовую шину 11 с некоторой задержкой - положительный сигналы. Например, на противотактовую шину 11 поступает сигнал от тактовой шины 9 через инвертор. При этом за счет емкости затвор-исток транзистора 4 потенциал выхода 10 элемента понижается, а за счет тока стока того же транзистора повышается. Балланс этих токов должен приводить к сохранению нулевого потенциала выхода 10 элемента, или к его некоторому росту. Это достигается параметрами транзистора 4 и величиной задержки противофазной тактовой шины.

Тактовые транзисторы 1 и 4 при этом закрываются и подготавливает выход 10 устройства к формированию логического сигнала. При выполняемой функции по И равной 0 ключевые цепи 6 не проводят, и состояние выхода 8 логического блока 5 и выхода 10 устройства не изменяется и соответствует исходному - нулевому, поскольку логический транзистор 3 закрыт по затвору. Когда на затворы транзисторов n-типа хотя бы одной из ключевых цепей 6 поданы сигналы логической 1, что соответствует функции И равной 1, соответствующая ключевая цепь оказывается в проводящем состоянии и узловая емкость (конденсатор 12) выхода 8 логического блока 5 разряжается до нулевого уровня напряжения на тактовой шине 9. Логический транзистор 3 p-типа при этом открывается, и, поскольку на противофазной тактовой шине 11 напряжение питания, на выходе 10 элемента формируется сигнал логической 1.

При каскадном соединении логических элементов с целью повышения глубины логики тактовый транзистор 1 является общим для всех каскадов, что позволяет дополнительно упростить каскадное устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ТАКТИРУЕМЫЙ МНОГОВХОДОВЫЙ ЭЛЕМЕНТ И | 2009 |

|

RU2412542C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2014 |

|

RU2542660C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2007 |

|

RU2334354C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Изобретение относится к области вычислительной техники и может быть использовано для реализации каскадных логических устройств конвейерного типа. Технический результат заключается в упрощении конструкции динамического логического элемента. Технический результат достигается за счет того, что динамический логический элемент И-ИЛИ содержит тактовый 1, предзарядовый 2 и логический 3 транзисторы p-типа, тактовый 4 транзистор n-типа и логический блок 5, содержащий ключевые цепи 6, каждая из которых состоит из последовательно соединенных транзисторов n-типа, логические входы 7 элемента, выход 8 логического блока 5, тактовую шину 9, к которой подключен также затвор тактового транзистора 4 n-типа, выход 10 элемента и противофазную тактовую шину 11. 1 ил.

Динамический логический элемент И-ИЛИ, содержащий тактовый, предзарядовый и логический транзисторы p-типа, тактовый транзистор n-типа и логический блок, содержащий ключевые цепи, включенные параллельно между выходом логического блока и тактовой шиной, к которой подключен также затвор тактового транзистора n-типа, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, логический транзистор p-типа, затвор которого соединен с выходом логического блока, включен между выходом элемента и противофазной тактовой шиной, тактовый транзистор p-типа, затвор которого соединен с противофазной тактовой шиной, включен последовательно с предзарядовым транзистором p-типа, затвор которого соединен с выходом элемента, отличающийся тем, что соединенные последовательно предзарядовый и тактовый транзисторы p-типа включены между выходом логического блока и тактовой шиной, а тактовый транзистор n-типа включен между выходом элемента и противофазной тактовой шиной.

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ВСЕСОЮЗНАЯ | 0 |

|

SU374878A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2016-04-10—Публикация

2015-02-17—Подача