Изобретение относится к области вычислительной техники и может быть использовано для реализации КМДП логических устройств.

Известен многофункциональный тактируемый логический элемент типа «домино» на КМДП транзисторах (патент США №5208489. FIG.2, Н03К 19/094. НКИ 307/451 от 04.05.1993). В нем используются тактируемые элементы И-НЕ с предзарядовыми транзисторами р-типа в качестве нагрузок, выходы которых подключены к входам логического элемента ИЛИ-НЕ статического типа. Недостатком элемента является низкое быстродействие, что связано с избыточной величиной узловой емкости, обусловленной входами статического элемента ИЛИ-НЕ.

Наиболее близким техническим решением к предлагаемому является логический элемент с функцией И-ИЛИ на КМДП транзисторах (патент РФ №2275737, МКИ Н03К 19/01, 19/094 от 06.12.2004). Это устройство, принятое за прототип, содержит тактируемые элементы И-НЕ, выходы которых подключены к затворам логических транзисторов р-типа тактируемого в противофазе инвертирующего элемента. Каждый элемент И-НЕ содержит предзарядовый транзистор р-типа и логическую часть в виде ключевой цепи, выполненной на последовательно соединенных транзисторах n-типа.

Недостаток этого устройства - ограниченное быстродействие, обусловленное дополнительными затратами времени на перезаряд узловых емкостей выходов элементов в результате передачи заряда на фронте тактового сигнала, на выход соответствующего элемента через проходную емкость затвор - токовый элетрод тактируемого транзистора.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства.

Поставленная цель достигается тем, что логический элемент И-ИЛИ, содержащий два элемента И-НЕ и инвертирующий элемент, каждый из элементов И-НЕ содержит включенный между шиной питания и выходом данного элемента предзарядовый транзистор р-типа, затвор которого подключен к тактовой шине, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, которая включена между выходом своего элемента И-НЕ и противофазной тактовой шиной, причем затворы транзисторов n-типа соответствующей ключевой цепи подключены к входам своего элемента И-НЕ, инвертирующий элемент содержит два логических транзистора р-типа, затворы которых соответственно подключены к выходам элементов И-НЕ, и тактовый транзистор n-типа, затвор которого соединен с противофазной тактовой шиной, причем логические транзисторы р-типа включены параллельно между шиной питания и выходом устройства, а тактовый транзистор n-типа включен между нулевой шиной и выходом устройства, причем каждый элемент И-НЕ содержит включенный между шиной питания и выходом элемента предзарядовый транзистор n-типа, затвор которого соединен с противофазной тактовой шиной, а инвертирующий элемент содержит включенный между нулевой шиной и выходом устройства тактовый транзистор р-типа, затвор которого соединен с тактовой шиной.

Существенными отличительными признаками в указанной совокупности признаков является наличие в элементе И-НЕ включенного между шиной питания и выходом элемента предзарядового транзистора n-типа, затвор которого соединен с противофазной тактовой шиной, и наличие в инвертирующем элементе включенного между нулевой шиной и выходом устройства тактового транзистора р-типа, затвор которого соединен с тактовой шиной.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышения быстродействия устройства. В известном устройстве во время действия положительного фронта на тактовой шине через проходную емкость затвор-токовый электрод предзарядовых транзисторов протекает ток, который создает дополнительный положительный заряд на емкости, обусловленной выходами элементов И-НЕ. Это выражается в повышении напряжения на выходах этих элементов выше уровня напряжения на шине питания, что ведет к увеличению времени разряда емкости нагрузки этих элементов и, соответственно, увеличению времени формирования сигнала логического 0, т.е. к снижению быстродействия устройства. Аналогичный процесс происходит на выходе элемента И-ИЛИ во время спада сигнала на противофазной тактовой шине за счет наличия проходной емкости тактируемого транзистора n-типа, в результате чего уровень выходного сигнала снижается ниже уровня нулевой шины, что ведет к увеличению времени формирования сигнала логической 1 на выходе элемента. Введение предзарядовых транзисторов n-типа с противофазным тактированием по отношению к предзарядовым транзисторам р-типа и соответственно тактового транзистора р-типа типа с противофазным тактированием по отношению к тактовому транзистору n-типа ведет к компенсации дополнительных зарядов на емкостях выходов во время действия фронтов тактовых сигналов. При надлежащем выборе размеров предзарядовых транзисторов n- и р-типа, а также размеров тактовых транзисторов n- и р-типа в зависимости от взаимного расположения во времени и длительности фронтов на тактовых шинах, а также параметров структур самих транзисторов n- и р-типов токи противоположной направленности через проходные емкости предзарядовых транзисторов n- и р-типа и тактовых транзисторов n- и р-типа компенсируются и полностью исключается отрицательное влияние фронтов тактовых сигналов на процесс переключения.

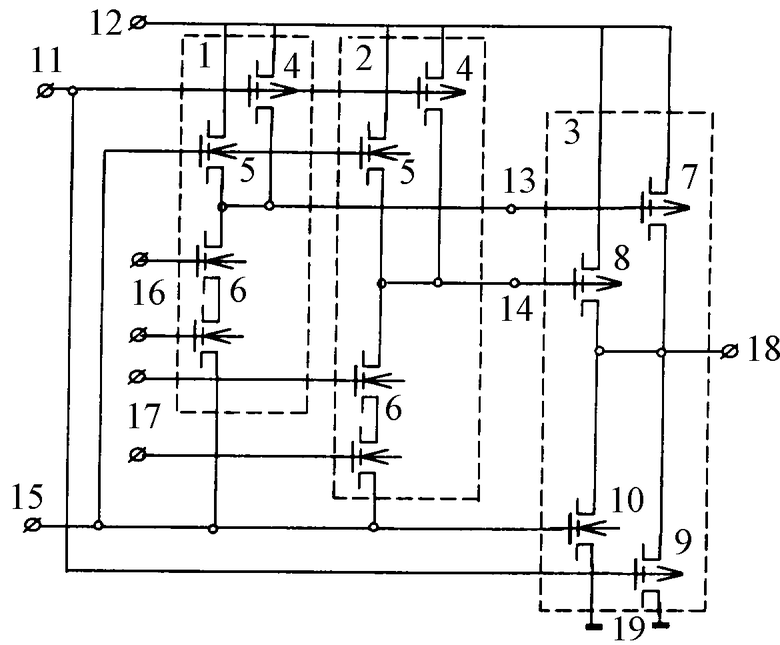

На чертеже приведена принципиальная схема заявляемого логического элемента И-ИЛИ на примере двухвходовых элементов И-НЕ.

Логический элемент И-ИЛИ содержит два элемента И-НЕ 1-2 и инвертирующий элемент 3. Каждый элемент И-НЕ 1-2 содержит предзарядовый транзистор 4 р-типа, предзарядовый транзистор 5 n-типа и ключевую цепь 6, выполненную на последовательно соединенных транзисторах n-типа.

Инвертирующий элемент 3 содержит два логических транзистора 7-8 р-типа, тактовый транзистор 9 р-типа и тактовый транзистор 10 n-типа.

В каждом из элементов И-НЕ предзарядовый транзистор 4 р-типа, затвор которого подключен к тактовой шине 11, включен между шиной питания 12 и соответствующим выходом 13 или 14 данного элемента. Ключевая цепь 6, состоящая из последовательно соединенных транзисторов n-типа, включена между выходом 13 или 14 своего элемента И-НЕ и противофазной тактовой шиной 15, причем затворы транзисторов n-типа ключевых цепей 6 подключены к входам 16-17 соответствующего элемента И-НЕ.

В инвертирующем элементе 3 логические транзисторы 7-8 р-типа, затворы которых подключены соответственно к выходам 13 и 14 элементов И-НЕ, включены параллельно между шиной питания 12 и выходом 18 устройства, тактовые транзисторы 10 n-типа и 9 р-типа, затворы которых соединены соответственно с противофазной тактовой шиной 15 и с тактовой шиной 11, включены параллельно между выходом 18 устройства и нулевой шиной 19

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 11 и положительном сигнале на противофазной тактовой шине 15 предзарядовые транзисторы 4 р-типа, предзарядовые транзисторы 5 n-типа и тактовые транзисторы 10-9 соответственно n- и р-типа открыты. Ключевые цепи 6 независимо от сигналов на входах 16-17 логических элементов И-НЕ находятся в непроводящем состоянии. От шины питания 12 через предзарядовые транзисторы 4 и 5 происходит процесс предзаряда до уровня логической 1, равного напряжению питания, узловых емкостей, связанных с выходами 13-14 элементов И-НЕ, а через тактовые транзисторы 9 и 10 происходит установка выхода 18 устройства до уровня сигнала нулевой шины 19. На выходах 13 и 14 элементов И-НЕ - состояния логической 1, логические транзисторы 7-8 при этом закрыты и на выходе 18 устройства - состояние логического 0. На первом полутакте на входах 16-17 элементов И-НЕ устанавливаются сигналы, соответствующие входным переменным.

На втором полутакте после подачи положительного сигнала на тактовую шину 11 и нулевого сигнала на противофазную тактовую шину 15 предзарядовые транзисторы 4 р-типа и 5 n-типа, а также тактовые транзисторы 9 р-типа и 10 n-типа закрываются и подготавливают выход 18 устройства к формированию выходного сигнала. Если сигналы, подаваемые на входы 16 или 17 элементов И-НЕ, соответствуют логической 1, соответствующая ключевая цепь 6 оказывается в проводящем состоянии и узловая емкость выхода 13 или 14 элементов И-НЕ разряжается до нулевого уровня противофазной тактовой шины 15. При этом логические транзисторы 7 или 8 р-типа инвертирующего элемента 3, затворы которых подключены к выходу данного элемента И-НЕ, открываются и на выходе 18 устройства формируется сигнал логической 1. Если сигнал логической 1 на выходах 13-14 элементов И-НЕ 1 и 2 не изменяется, логические транзисторы 7 и 8 р-типа остаются в закрытом состоянии и на выходе 18 устройства сохраняется состояние логического 0. Инвертирующий элемент 3 выполняет при этом функцию ИЛИ-НЕ.

Во время действия положительного фронта на тактовой шине 11 через проходную емкость затвор-токовый электрод предзарядовых транзисторов 4 р-типа протекает ток, который пропорционален величине этой емкости, т.е. ширине канала этого транзистора. Одновременно через проходную емкость затвор-токовый электрод предзарядовых транзисторов 5 n-типа с противофазным тактированием протекает ток противоположного направления, что ведет к компенсации дополнительных зарядов на емкостях выходов 13-14 во время действия фронтов тактовых сигналов.

Аналогичный процесс происходит на выходе 18 устройства за счет наличия проходных емкостей тактовых транзисторов 9 р-типа и 10 n-типа, которые тактируются в противофазе, что ведет к компенсации дополнительных зарядов на емкости выхода 18 во время действия фронтов тактовых сигналов. При надлежащем выборе соотношения размеров предзарядовых транзисторов 5 n-типа и 4 р-типа, а также соотношения размеров тактовых транзисторов 10 n-типа и 9 р-типа в зависимости от взаимного расположения во времени и длительности фронтов на тактовых шинах 11 и 15, а также параметров структур самих транзисторов n- и р-типов возможно полностью исключить отрицательное влияние фронтов тактовых сигналов на процесс переключения. При этом уменьшение временной задержки переключения элемента составляет от 10 до 30% в зависимости от величины емкостной нагрузки. Таким же образом можно дополнительно повысить быстродействие устройства, если за счет предзарядовых транзисторов 5 n-типа и тактового 9 р-типа сдвинуть изменение напряжений на выходах 13-14 и соответственно 18 во время действия фронтов тактовых сигналов в направлении формирования выходных сигналов. Например, если допустить понижение напряжения на выходах 13-14 элементов И-НЕ на величину, равную 0.5 порогового напряжения транзисторов р-типа, и повышение напряжения на выходе 18 на величину, равную 0.5 порогового напряжения транзисторов n-типа.

После прекращения действия тактовых сигналов предзарядовые транзисторы 5 и 4 n- и р-типов открываются и параллельно создают цепь для восстановления исходного состояния. Причем за счет их одновременного включения время восстановления уменьшается, что также ведет к повышению быстродействия устройства.

Элементы И-НЕ могут содержать более двух входов, а также могут содержать не одну, а несколько ключевых цепей, включенных параллельно, что позволяет реализовывать многофункциональные логические устройства от большего числа входных переменных.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАКТИРУЕМЫЙ МНОГОВХОДОВЫЙ ЭЛЕМЕНТ И | 2009 |

|

RU2412542C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2015 |

|

RU2580095C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| Многовходовый логический элемент И | 2015 |

|

RU2613853C2 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Изобретение относится к вычислительной технике для использования в МДП интегральных схемах. Технический результат заключается в повышении быстродействия. Устройство содержит элементы И-НЕ (1, 2), выходы (13, 14) которых подключены к затворам логических транзисторов (Т) (7, 8) р-типа инвертирующего элемента (ИЭ) (3), которые включены параллельно между шиной питания (12) и выходом (18) устройства, причем элемент И-НЕ (1, 2) содержит ключевую цепь (6) на Т n-типа и включенных между шиной питания (12) и выходом данного элемента, предзарядовые Т (4) р-типа и Т (5) n-типа, затворы которых подключены соответственно к тактовой шине (11) и противофазной тактовой шине (15), а ИЭ (3) содержит включенные между нулевой шиной (19) и выходом (18) устройства тактовые Т (9) р-типа и Т (10) n-типа, затворы которых соединены соответственно с тактовой (11) и противофазной тактовой (15) шинами. Введение предзарядовых Т n-типа с противофазным тактированием ведет к компенсации дополнительных зарядов на емкостях выходов во время действия фронтов тактовых сигналов. Токи через проходные емкости предзарядовых Т n- и р-типа и тактовых Т n- и р-типа компенсируются, и полностью исключается отрицательное влияние фронтов тактовых сигналов на процесс переключения. 1 ил.

Логический элемент И-ИЛИ, содержащий два элемента И-НЕ и инвертирующий элемент, каждый из элементов И-НЕ содержит включенный между шиной питания и выходом данного элемента предзарядовый транзистор р-типа, затвор которого подключен к тактовой шине, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, которая включена между выходом своего элемента И-НЕ и противофазной тактовой шиной, причем затворы транзисторов n-типа соответствующей ключевой цепи подключены к входам своего элемента И-НЕ, инвертирующий элемент содержит два логических транзистора р-типа, затворы которых соответственно подключены к выходам элементов И-НЕ, и тактовый транзистор n-типа, затвор которого соединен с противофазной тактовой шиной, причем логические транзисторы р-типа включены параллельно между шиной питания и выходом устройства, а тактовый транзистор n-типа включен между нулевой шиной и выходом устройства, отличающийся тем, что каждый элемент И-НЕ содержит между шиной питания и выходом элемента предзарядовый транзистор n-типа, затвор которого соединен с противофазной тактовой шиной, а инвертирующий элемент содержит включенный между нулевой шиной и выходом устройства тактовый транзистор р-типа, затвор которого соединен с тактовой шиной.

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| Логический элемент на МДП-транзисторах | 1990 |

|

SU1764159A1 |

| Логический элемент на МДП-транзисторах | 1990 |

|

SU1734206A1 |

| US 5208489 A, 04.05.1993 | |||

| US 4851714, 25.07.1989. | |||

Авторы

Даты

2008-09-20—Публикация

2007-03-02—Подача