Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических устройств.

Известен тактируемый логический элемент И типа «домино» с несколькими входами (Патент США №5208489, FIG.1, Н03К 19/094, НКИ 307/451 от 04.05.1993). Он содержит элемент И-НЕ с предзарядовым транзистором p-типа, ключевую цепь на транзисторах n-типа и выходной статический инвертор. Недостатком элемента является ограниченное быстродействие, что связано с наличием нескольких последовательно включенных транзисторов ключевой цепи и нагрузкой выходного инвертора.

Наиболее близким техническим решением к предлагаемому является логический элемент на КМДП транзисторах с функцией И на несколько входов (Патент РФ №2275737, Н03К 19/01, 19/094 от 06.12.2004). Это устройство, принятое за прототип, содержит элемент И-НЕ, инвертирующий элемент и два тактовых транзистора. Элемент И-НЕ содержит предзарядовый транзистор p-типа и логическую часть в виде ключевой цепи, выполненной на последовательно соединенных транзисторах n-типа, а инвертирующий элемент содержит логический транзистор p-типа и предзарядовый транзистор n-типа. Недостаток этого устройства - ограниченное быстродействие при большом числе входов по И, что обусловлено медленным процессом переключения элемента И-НЕ.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства. Поставленная цель достигается тем, что многовходовый логический элемент И на КМДП транзисторах, содержащий элемент И-НЕ, инвертирующий элемент, тактовый транзистор n-типа и тактовый транзистор p-типа, элемент И-НЕ содержит предзарядовый транзистор p-типа, включенный между шиной питания и выходом данного элемента, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, первый вывод ключевой цепи подключен к выходу элемента И-НЕ, а второй вывод через тактовый транзистор n-типа соединен с нулевой шиной, тактовый транзистор p-типа включен между шиной питания и вторым выводом ключевой цепи элемента И-НЕ, инвертирующий элемент содержит логический транзистор p-типа, включенный между шиной питания и выходом устройства, и предзарядовый транзистор n-типа, включенный между выходом устройства и нулевой шиной, затворы тактовых транзисторов и предзарядового транзистора p-типа подключены к тактовой шине, затворы логического транзистора p-типа и предзарядового транзистора n-типа инвертирующего элемента подключены соответственно к выходу элемента И-НЕ и к второму выводу ключевой цепи элемента И-НЕ, содержит дополнительный транзистор n-типа, который включен между выходом элемента И-НЕ и вторым выводом ключевой цепи того же элемента и затвор которого соединен с выходом устройства, причем устройство содержит не менее 8 входов.

Существенными отличительными признаками в указанной совокупности признаков является наличие дополнительного транзистора n-типа, который в совокупности с новыми связями формирует дополнительную цепь обратной связи параллельно с ключевой цепью элемента И-НЕ.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение бвстродействия устройства. В известном устройстве при реализации функции И переключение элемента И-НЕ происходит через ключевую цепь с наличием нескольких последовательно включенных транзисторов транзисторов n-типа, а при большом числе входов - инвертирующий элемент переключается дополнительно через несколько последовательно включенных логических транзисторов p-типа, что ограничивает быстродействие многовходового элемента И. В предлагаемом устройстве переключение элемента И-НЕ через ключевую цепь происходит только на начальном этапе - до достижения на выходе устройства порогового напряжения транзисторов n-типа, что составляет не более 20% напряжения питания. В дальнейшем формирование выходного сигнала до уровня напряжения питания осуществляется при переключении элемента И-НЕ через дополнительный транзистор n-типа, сопротивление которого много меньше сопротивления ключевой цепи, что повышает быстродействие многовходового элемента И и позволяет использовать в ключевой цепи транзисторы n-типа с минимальными геометрическими размерами с наименьшей входной емкостью, что дополнительно ведет к повышению быстродействия устройства.

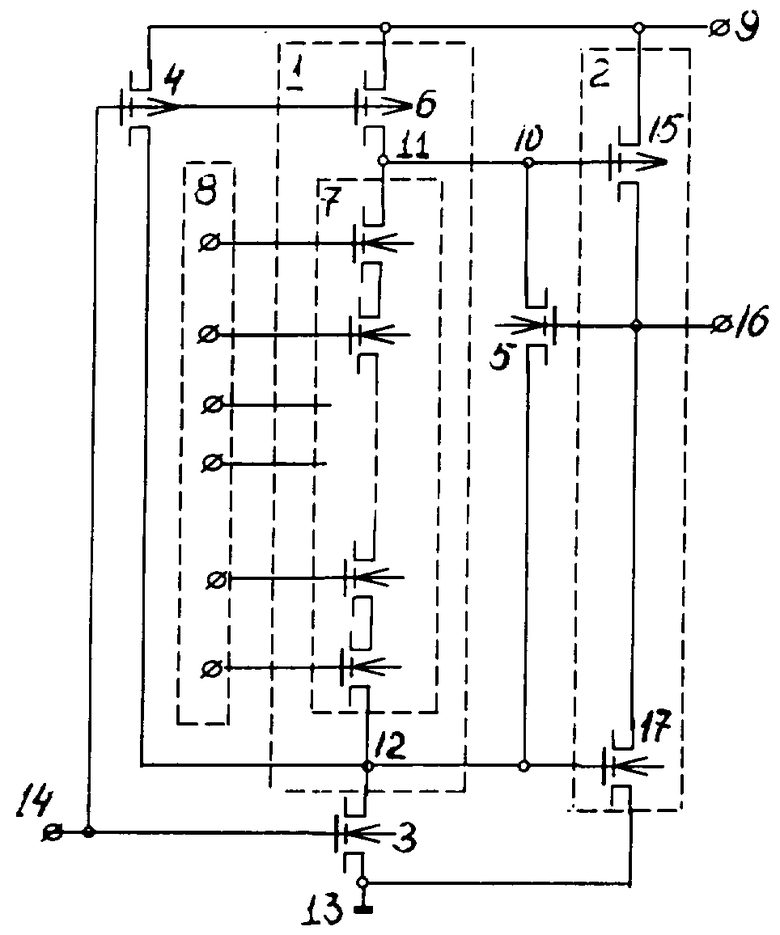

На чертеже приведена принципиальная схема заявляемого многовходового логического элемента И на КМДП транзисторах.

Многовходовый логический элемент на КМДП транзисторах содержит элемент И-НЕ 1, инвертирующий элемент 2, тактовые транзисторы 3 и 4 соответственно n-типа и p-типа, дополнительный транзистор 5 n-типа. Элемент И-НЕ 1 содержит предзарядовый транзистор 6 p-типа и ключевую цепь 7, выполненную на последовательно соединенных транзисторах n-типа, затворы которых подключены к входам 8 устройства. Предзарядовый транзистор 6 p-типа включен между шиной питания 9 и выходом 10 элемента И-НЕ. Первый вывод 11 ключевой цепи 7 элемента И-НЕ соединен с выходом 10 элемента И-НЕ, а второй вывод 12 через тактовый транзистор 3 n-типа соединен с нулевой шиной 13. Тактовый транзистор 4 p-типа включен между шиной питания 9 и вторым выводом 12 ключевой цепи 7 элемента И-НЕ 1. Затворы тактовых транзисторов 3, 4 и предзарядового транзистора 6 подключены к тактовой шине 14.

Инвертирующий элемент 2 содержит логический транзистор 15 p-типа, включенный между шиной питания 9 и выходом 16 устройства, и предзарядовый транзистор 17 n-типа, включенный между выходом 16 устройства и нулевой шиной 13. Затворы логического транзистора 15 p-типа и предзарядового транзистора 17 n-типа инвертирующего элемента 2 подключены соответственно к выходу 10 и к второму выводу 12 ключевой цепи 7 элемента И-НЕ.

Дополнительный транзистор 5 транзистор n-типа, затвор которого соединен с выходом 16 устройства, включен между выходом 10 и вторым выводом 12 ключевой цепи 7 элемента И-НЕ 1.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 14 тактовый транзистор 3 n-типа закрыт, а тактовый транзистор 4 p-типа и предзарядовый транзистор 6 p-типа - открыты. От шины питания 9 через предзарядовые транзисторы 6 и 4 p-типа происходит процесс предзаряда до уровня логической 1, равного напряжению на шине питания 9, узловых емкостей, связанных с выходом 10 элемента И-НЕ и с вторым выводом 12 ключевой цепи 7 того же элемента. В результате логический транзистор 15 p-типа инвертирующего элемента 2 закрыт, а предзарядовый транзистор 17 n-типа - открыт. На выходе 16 устройства устанавливается сигнал логического 0. На первом полутакте на входах 8 устройства устанавливаются сигналы соответствующие входным переменным.

На втором полутакте после подачи положительного сигнала на тактовую шину 14 тактовый транзистор 3 n-типа открывается, а тактовый транзистор 4 p-типа и предзарядовый транзистор 6 p-типа закрываются. Тактовый транзистор 3 n-типа с большой шириной канала обеспечивает быстрый разряд емкостной нагрузки, связанной с вторым выводом 12 ключевой цепи 7, и предзарядовый транзистор 17 n-типа закрывается, что подготавливает выход 16 устройства к формированию выходного сигнала. Если все сигналы, подаваемые на входы 8 устройства, согласно функции И соответствуют логической 1, ключевая цепь 7 оказывается в проводящем состоянии и узловая емкость выхода 10 элемента И-НЕ начинает разряжаться через указанную ключевую цепь и тактовый транзистор 3 n-типа. При этом логический транзистор 15 p-типа инвертирующего элемента 2, затвор которого подключен к выходу элемента И-НЕ, открывается, и повышается уровень сигнала на выходе 16 устройства. При большом числе входов устройства и малых размерах транзисторов n-типа ключевой цепи 7 переходной процесс разряда узловой емкости, связанной с выходом 10 элемента И-НЕ, протекал бы достаточно медленно, как и в устройстве-прототипе. При достижении на выходе 16 устройства напряжения, равного пороговому для транзисторов n-типа, открывается дополнительный транзистор 5 n-типа и скорость разряда узловой емкости, связанной с выходом 10 элемента И-НЕ существенно возрастает, и соответственно сильнее открывается логический транзистор 15 p-типа и быстрее растет сигнал на выходе 16 устройства. Дополнительный транзистор 5 n-типа играет роль положительной обратной связи и его наличие позволяет использовать транзисторы n-типа в ключевой цепи 7 с минимальными размерами, что существенно уменьшает емкостную нагрузку по входам 8 элемента и повышает быстродействие при каскадном включении логических элементов. При большом числе входов (не менее 8) дополнительный транзистор 5 n-типа при тех же размерах, что и транзисторы n-типа ключевой цепи 7, существенно ускоряет процесс формирования сигнала логической 1 на выходе устройства.

При подаче нулевого сигнала на тактовую шину 14 происходит восстановление исходного состояния элемента тактовый транзистор 3 n-типа закрывается, а тактовый транзистор 4 p-типа и предзарядовый транзистор 6 p-типа открываются. В диапазоне пока уровень сигнала на выходе 16 устройства выше порогового дополнительный транзистор 5 n-типа работает в инверсном режиме, что увеличивает скорость заряда узловой емкости выхода 10 элемента И-НЕ, что уменьшает также время восстановления исходного состояния элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАКТИРУЕМЫЙ МНОГОВХОДОВЫЙ ЭЛЕМЕНТ И | 2009 |

|

RU2412542C1 |

| Многовходовый логический элемент И | 2015 |

|

RU2613853C2 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2007 |

|

RU2334354C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПЕРЕНОСА В СУММАТОРЕ | 2013 |

|

RU2525111C1 |

| Порт чтения | 2018 |

|

RU2693331C1 |

Изобретение относится к области вычислительной техники и может быть использовано в МДП интегральных схемах при реализации логических устройств. Устройство содержит элемент И-НЕ (1), инвертирующий элемент (ИЭ) (2), тактовые транзисторы (Т) (3) и (4) соответственно n-типа и р-типа, дополнительный Т (5) n-типа. Элемент И-НЕ (1) содержит предзарядовый Т (6) р-типа и ключевую цепь (7), выполненную на последовательно соединенных Т n-тина, затворы которых подключены к входам (8) устройства. Предзарядовый Т (6) включен между шиной питания (9) и выходом (10) элемента И-НЕ (1). Первый вывод (11) ключевой цепи (7) элемента И-НЕ (1) соединен с выходом (10) элемента И-НЕ (1), а второй вывод (12) через тактовый Т (3) соединен с нулевой шиной (13), тактовый Т (4) включен между шиной питания (9) и вторым выводом (12) ключевой цепи (7). Затворы тактовых Т (3, 4) и предзарядового Т (6) подключены к тактовой шине (14). ИЭ (2) содержит логический Т (15) р-типа, включенный между шиной питания (9) и выходом (16), и предзарядовый Т (17) n-типа, включенный между выходом устройства и нулевой шиной, затворы Т (15, 17) ИЭ (2) подключены соответственно к выходу (10) и к второму выводу (12) ключевой цепи (7). Дополнительный Т (5), затвор которого соединен с выходом (16) устройства, включен между выходом (10) устройства и вторым выводом (12) ключевой цепи (7). Технический результат - повышение быстродействия устройства. 1 ил.

Многовходовый логический элемент И на КМДП транзисторах, содержащий элемент И-НЕ, инвертирующий элемент, тактовый транзистор n-типа и тактовый транзистор р-типа, элемент И-НЕ содержит предзарядовый транзистор р-типа, включенный между шиной питания и выходом данного элемента, и ключевую цепь, состоящую из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам устройства, первый вывод ключевой цепи подключен к выходу элемента И-НЕ, а второй вывод через тактовый транзистор n-типа соединен с нулевой шиной, тактовый транзистор р-типа включен между шиной питания и вторым выводом ключевой цепи элемента И-НЕ, инвертирующий элемент содержит логический транзистор р-типа, включенный между шиной питания и выходом устройства, и предзарядовый транзистор n-типа, включенный между выходом устройства и нулевой шиной, затворы тактовых транзисторов и предзарядового транзистора р-типа подключены к тактовой шине, затворы логического транзистора р-типа и предзарядового транзистора n-типа инвертирующего элемента подключены соответственно к выходу элемента И-НЕ и к второму выводу ключевой цепи элемента И-НЕ, отличающийся тем, что содержит дополнительный транзистор n-типа, который включен между выходом элемента И-НЕ и вторым выводом ключевой цепи того же элемента и затвор которого соединен с выходом устройства, причем устройство содержит не менее 8 входов.

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| Логический элемент на МДП-транзисторах | 1990 |

|

SU1764159A1 |

| Логический элемент на МДП-транзисторах | 1990 |

|

SU1734206A1 |

| US 5208489 А, 04.05.1993 | |||

| СПОСОБ ПОЛУЧЕНИЯ ТРИЦИКЛОДЕКАДИЕНОВ | 0 |

|

SU320111A1 |

Авторы

Даты

2008-03-10—Публикация

2006-11-13—Подача