Текст описания приведен в факсимильном виде.

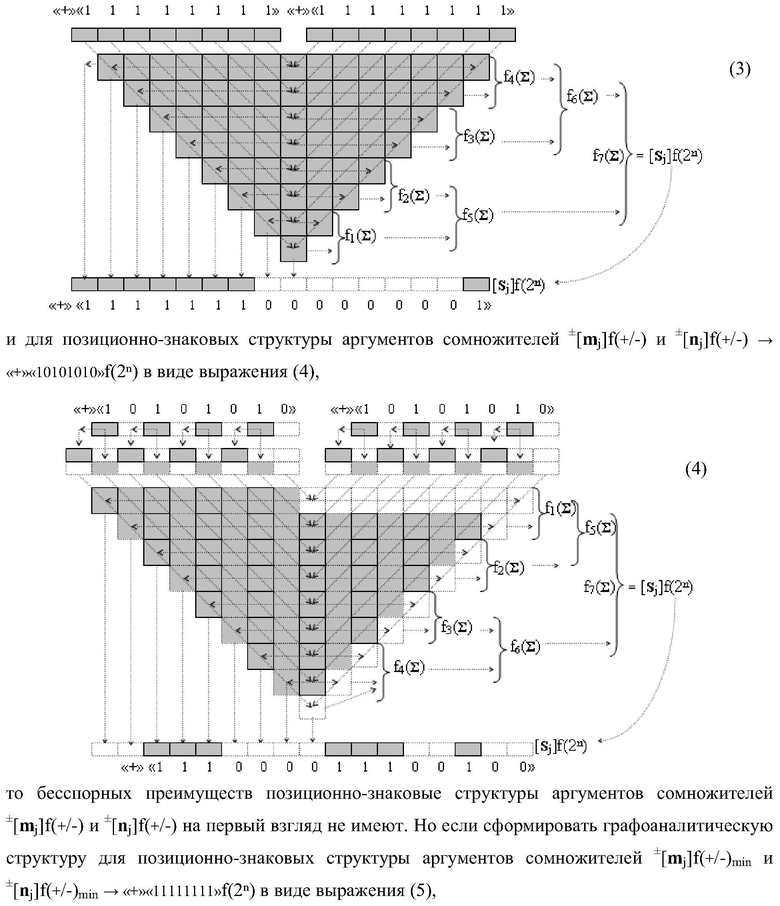

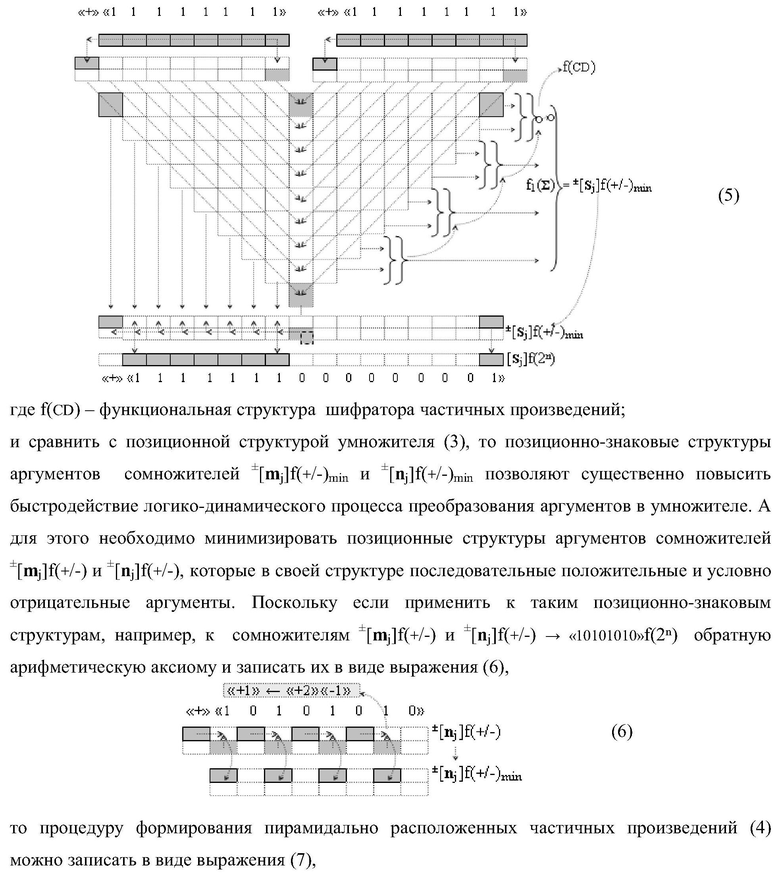

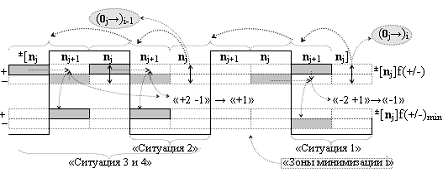

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций суммирования и вычитания в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия процесса преобразования аргументов при формировании сквозного последовательного переноса. В одном из вариантов функциональная структура выполнена с использованием элементов, реализующих логические функции И и ИЛИ. При этом функциональная структура условно «i»-ой зоны минимизации выполнена в виде двух эквивалентных структур логических функций - функциональной логической структуры параллельного переноса для формирования преобразованного аргумента переноса (0j)i j-го разряда и функциональной логической структуры для формирования преобразованного аргумента переноса (0j+1→)i (j+1)-го разряда. 6 н.п. ф-лы.

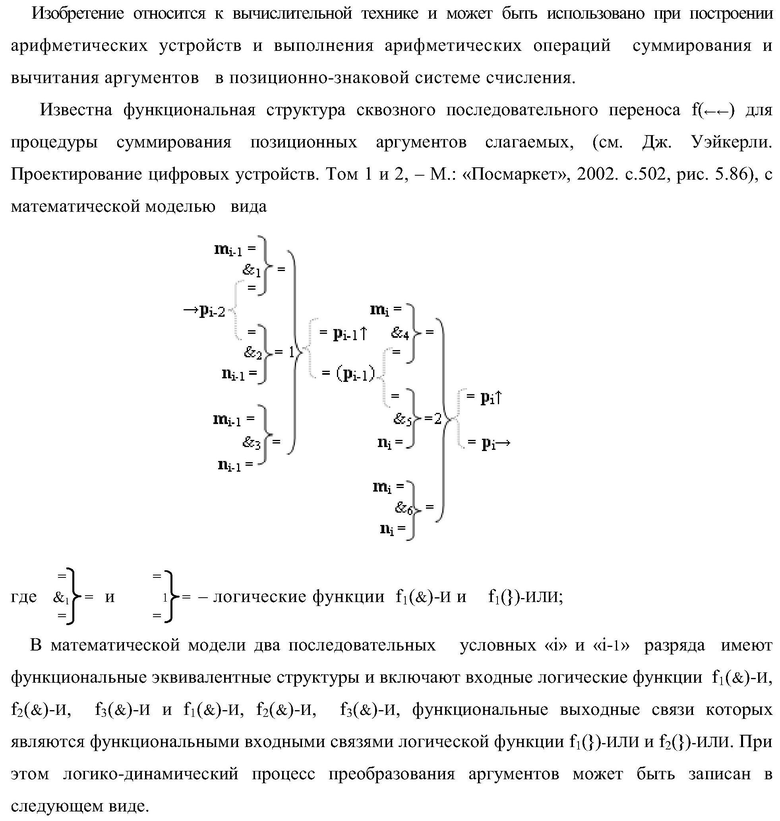

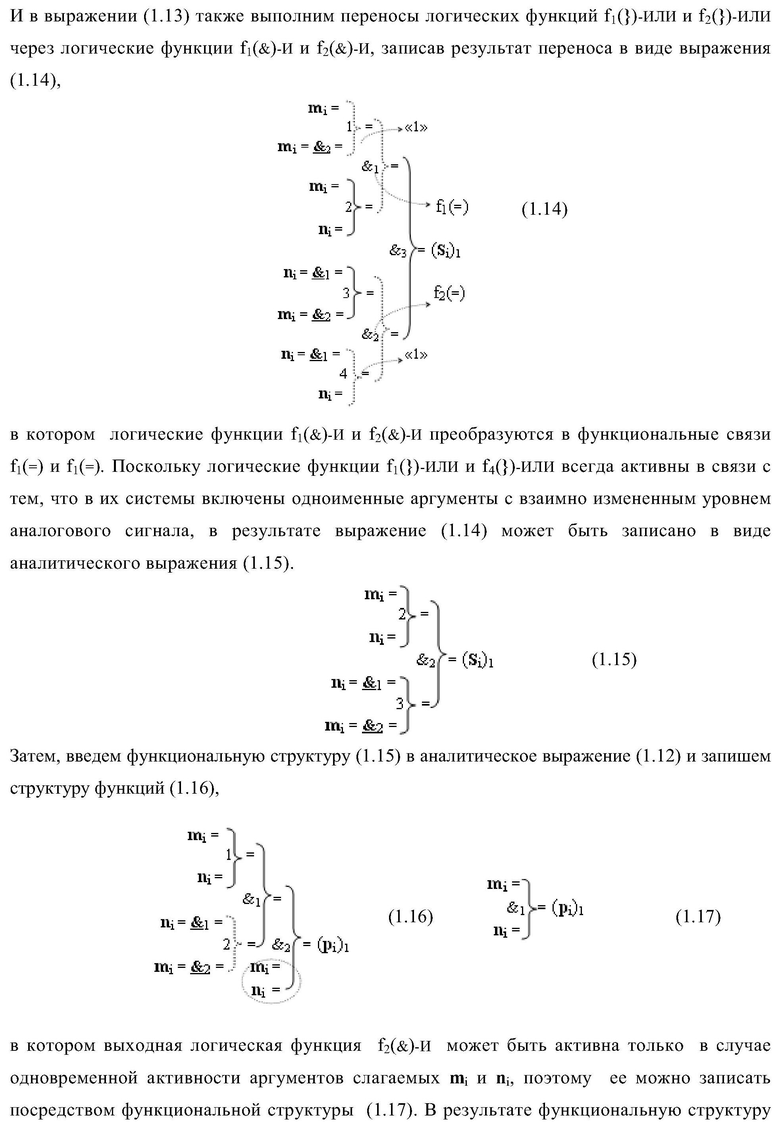

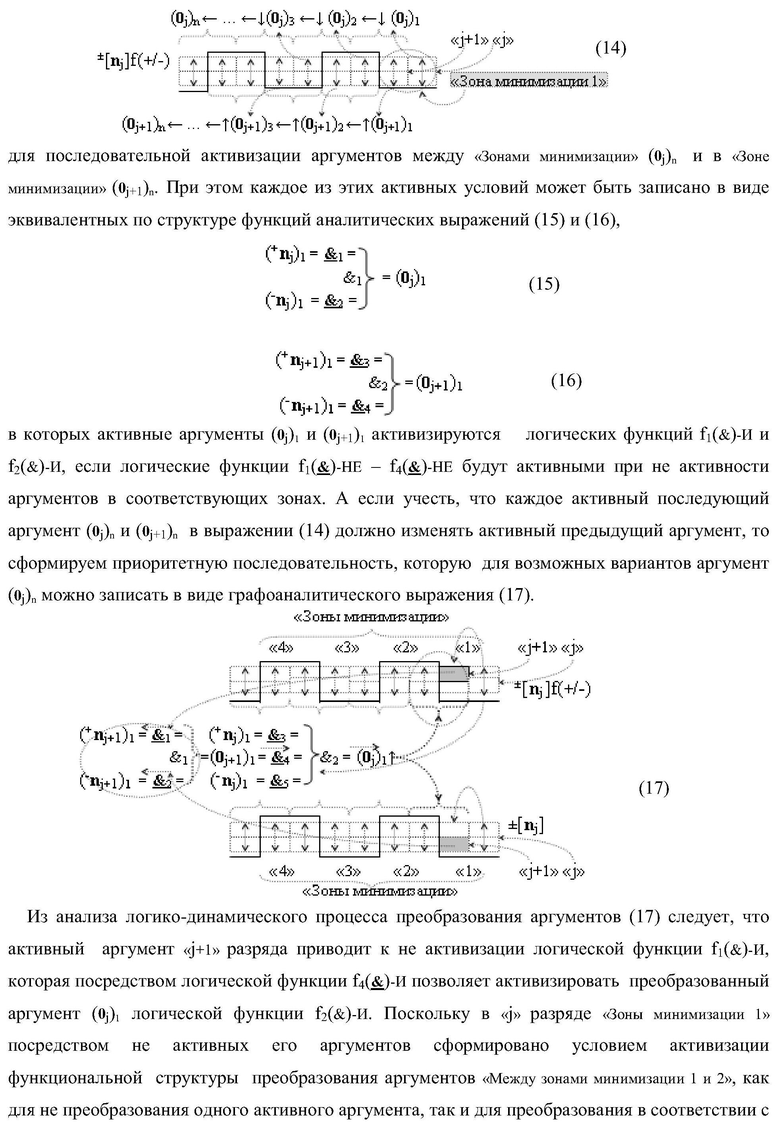

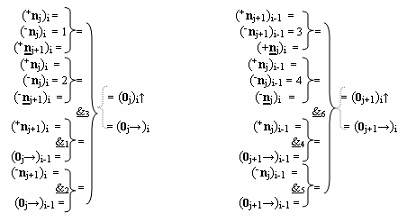

1. Способ активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру ±[n

j]f(+/-)min аналоговых сигналов, в котором для активизации аргумента (0

j+1→)i и аргумента (0

j→)i посредством функциональной логической структуры условно «j+1» и «j» разряда выполняют одновременный анализ в этих разрядах активности положительных аргументов (+

n

j+1)i, (+

n

j)i «i» «Зоны минимизации» и положительных аргументов (+

n

j+1)i-1, (+

n

j)i-1 «i-1» «Зоны минимизации», а также анализируют активность аргумента локального переноса (0

j+1→)i-1 и (0

j→)i-1 «i-1» «Зоны минимизации», после чего активизируют аргументы (0

j+1→)i и (0

j→)i сквозного последовательного переноса f1,2(←←)±0 в «i» «Зоне минимизации», отличающийся тем, что посредством функциональной логической структуры условно «j+1» и «j» разряда выполняют дополнительный анализ активности как условно отрицательных аргументов (-

n

j+1)i условно «j+1» разряда и (-

n

j)i условно «j» разряда «i» «Зоны минимизации», так и условно отрицательных аргументов (-

n

j+1)i-1 условно «j+1» разряда и (-

n

j)i-1 условно «j» разряда «i-1» «Зоны минимизации», при этом аргумент (0

j→)i активизируют в «i» «Зоне минимизации» посредством логической функциональной структуры условно «j» разряда в четырех ситуациях, в двух из которых одновременно не активны входные ее аргументы, как положительный аргумент (+

n

j)i, так и условно отрицательный аргумент (-

n

j)i «j» разряда «i» «Зоны минимизации» и активны либо положительный аргумент (+

n

j+1)i, либо условно отрицательный аргумент (-

n

j+1)i той же «Зоны минимизации», а в двух других ситуациях в логической функциональной структуре условно «j» разряда одновременно активен входной аргумент (0

j→)i-1 аргумент локального переноса (0

j→)i-1 «i-1» «Зоны минимизации» и либо входной условно отрицательный аргумент (-

n

j+1)i , либо входной положительный аргумент (+

n

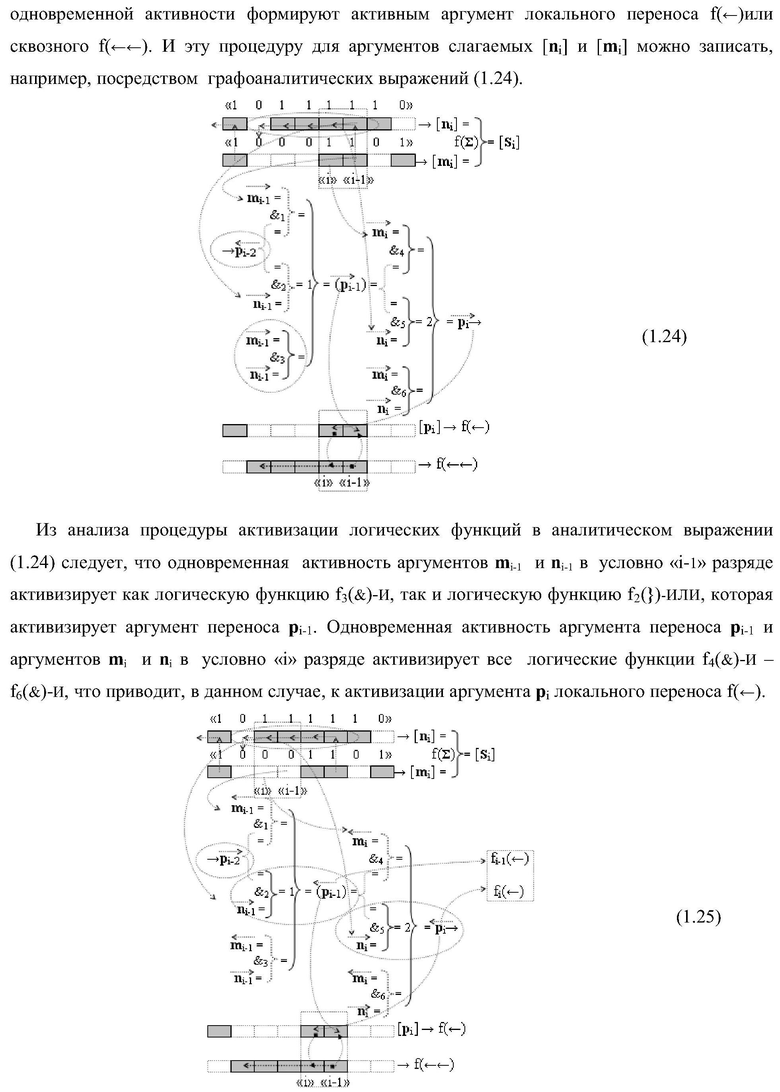

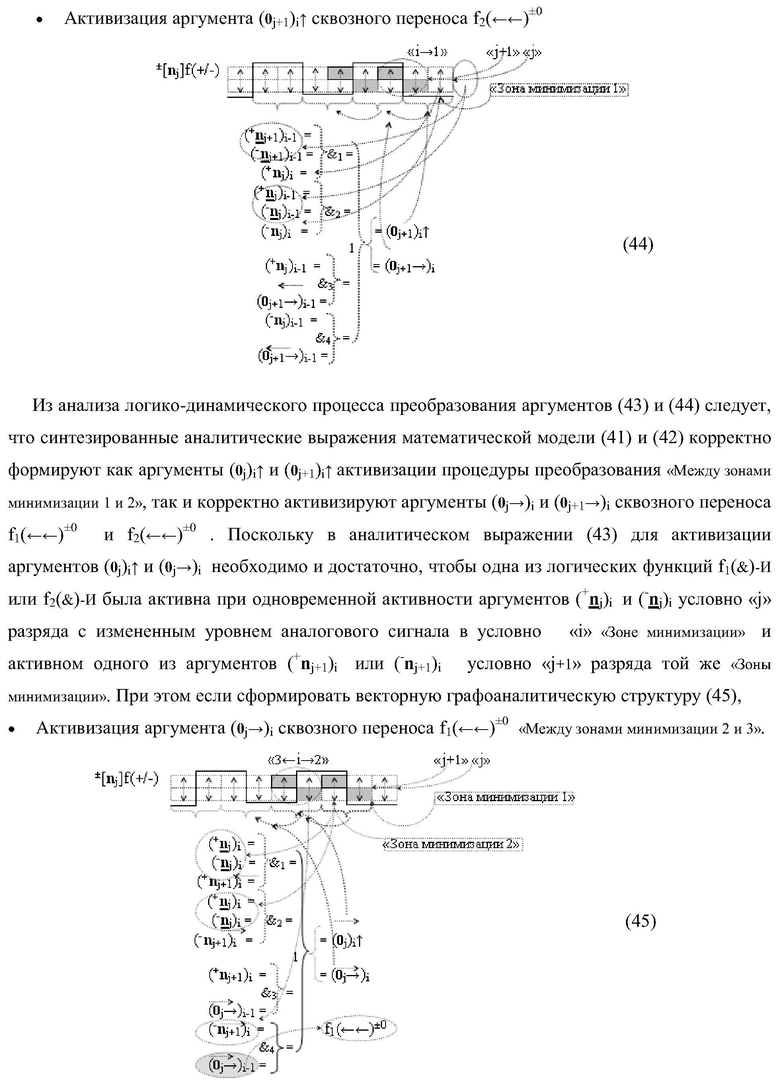

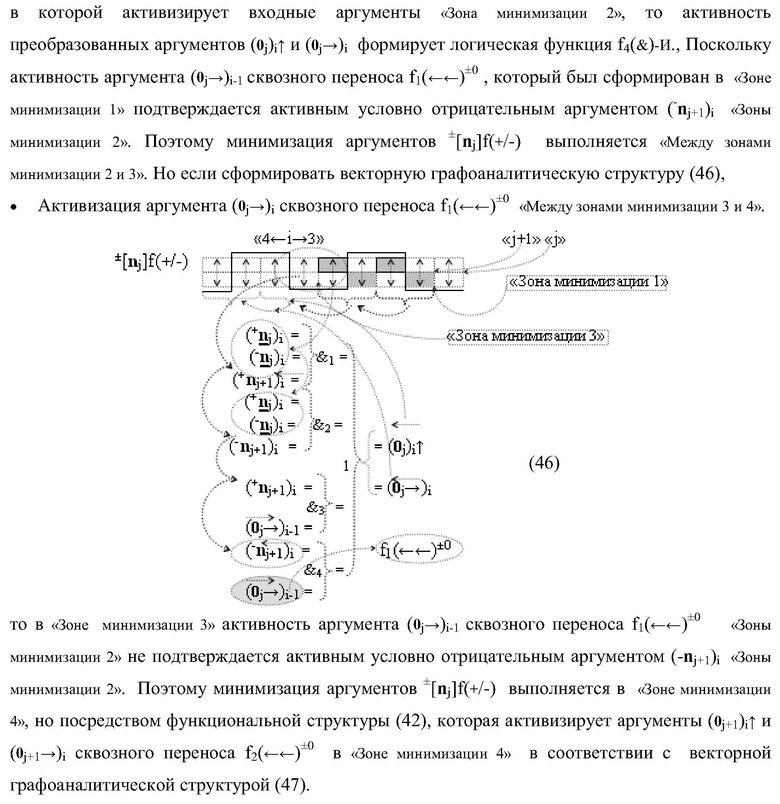

j+1)i «i» «Зоны минимизации» в соответствии с логико-динамическим процессом преобразования аргументов вида

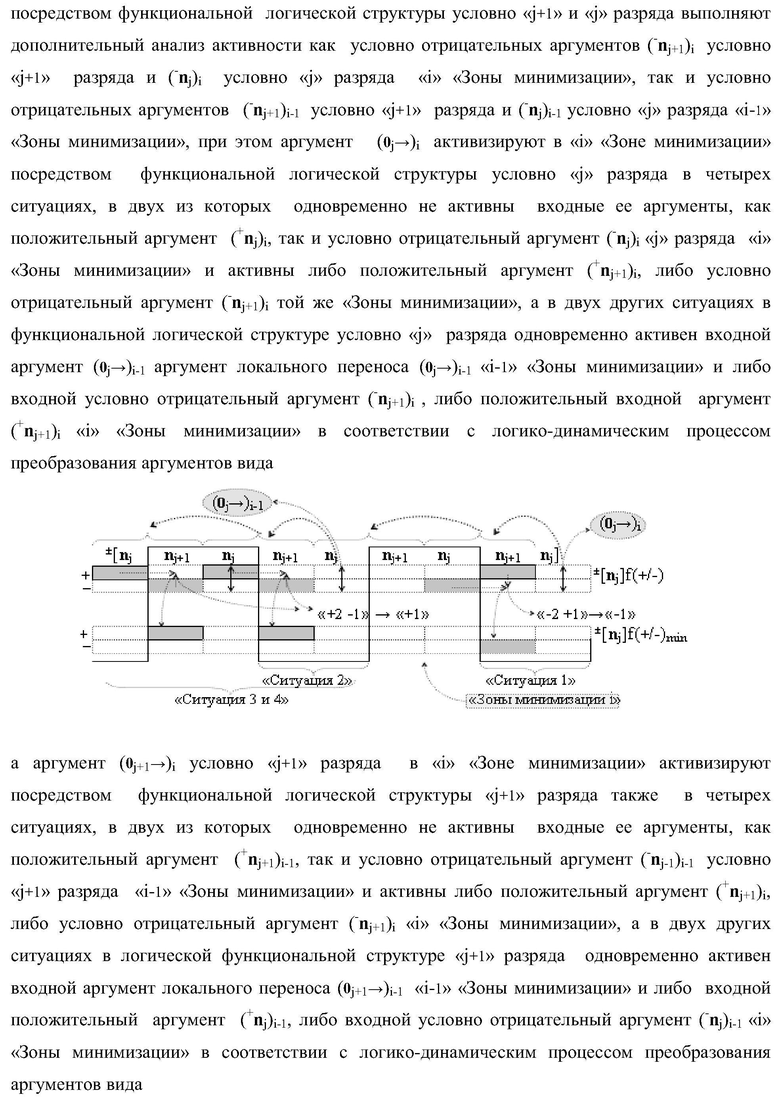

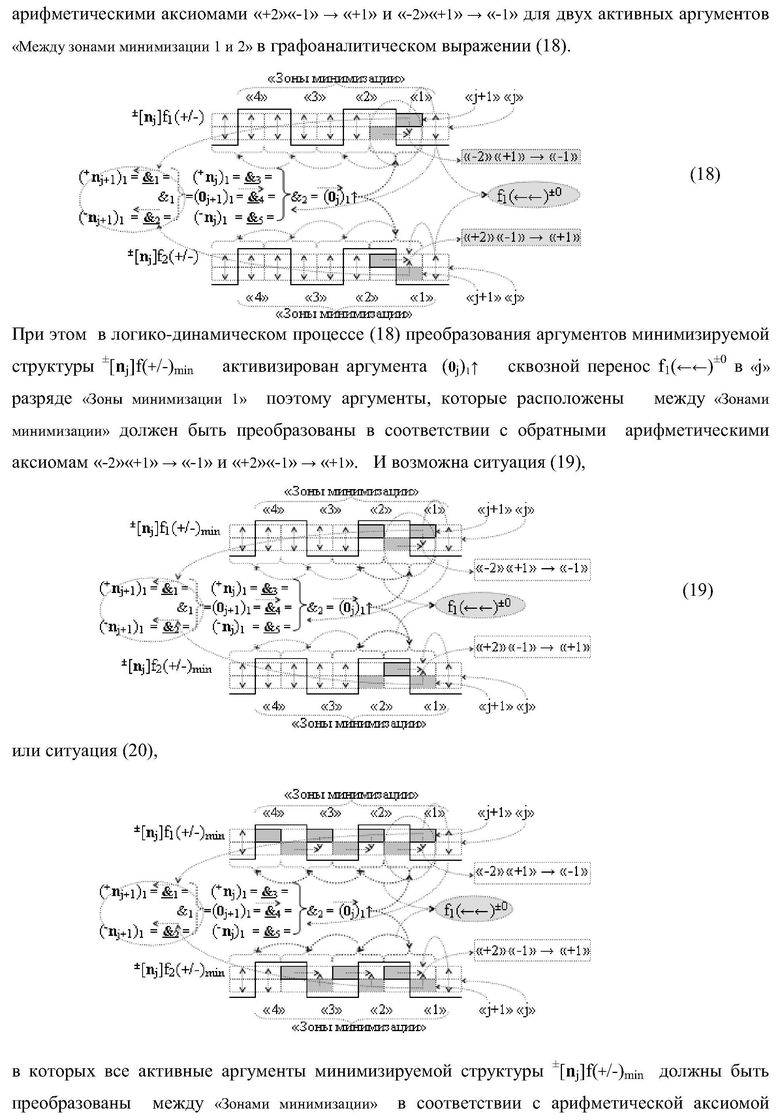

а аргумент (0

j+1→)i условно «j+1» разряда в «i» «Зоне минимизации» активизируют посредством функциональной логической структуры «j+1» разряда также в четырех ситуациях, в двух из которых одновременно не активны входные ее аргументы, как положительный аргумент (+

n

j+1)i-1, так и условно отрицательный аргумент (-

n

j-1)i-1 условно «j+1» разряда «i-1» «Зоны минимизации» и активны либо положительный аргумент (+

n

j+1)i, либо условно отрицательный аргумент (-

n

j+1)i «i» «Зоны минимизации», а в двух других ситуациях в логической функциональной структуре «j+1» разряда одновременно активен входной аргумент локального переноса (0

j+1→)i-1 «i-1» «Зоны минимизации» и либо входной положительный аргумент (+

n

j)i-1, либо входной условно отрицательный аргумент (-

n

j)i-1 «i» «Зоны минимизации» в соответствии с логико-динамическим процессом преобразования аргументов вида

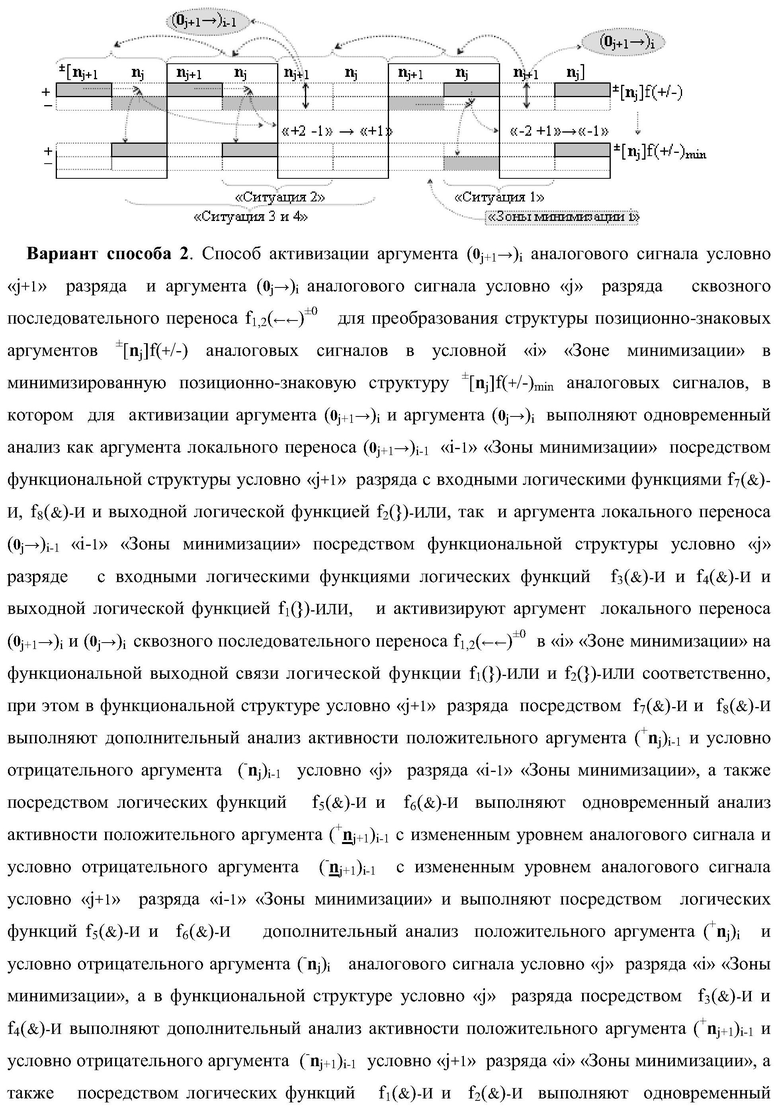

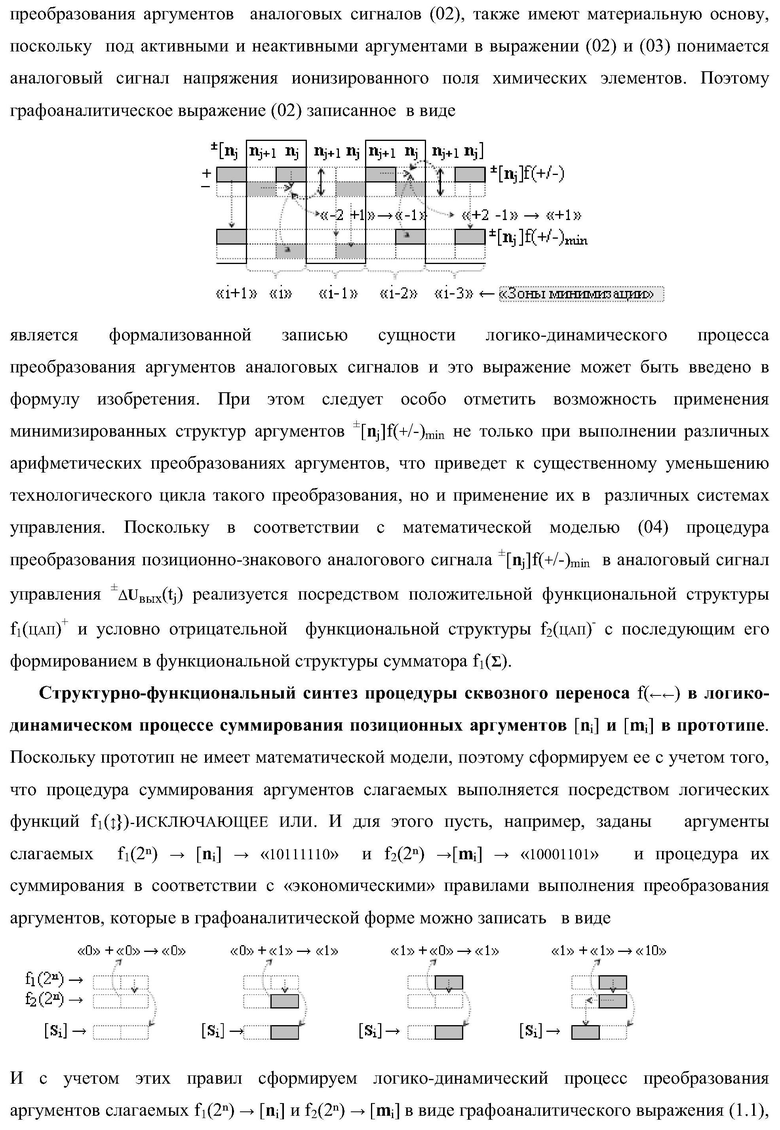

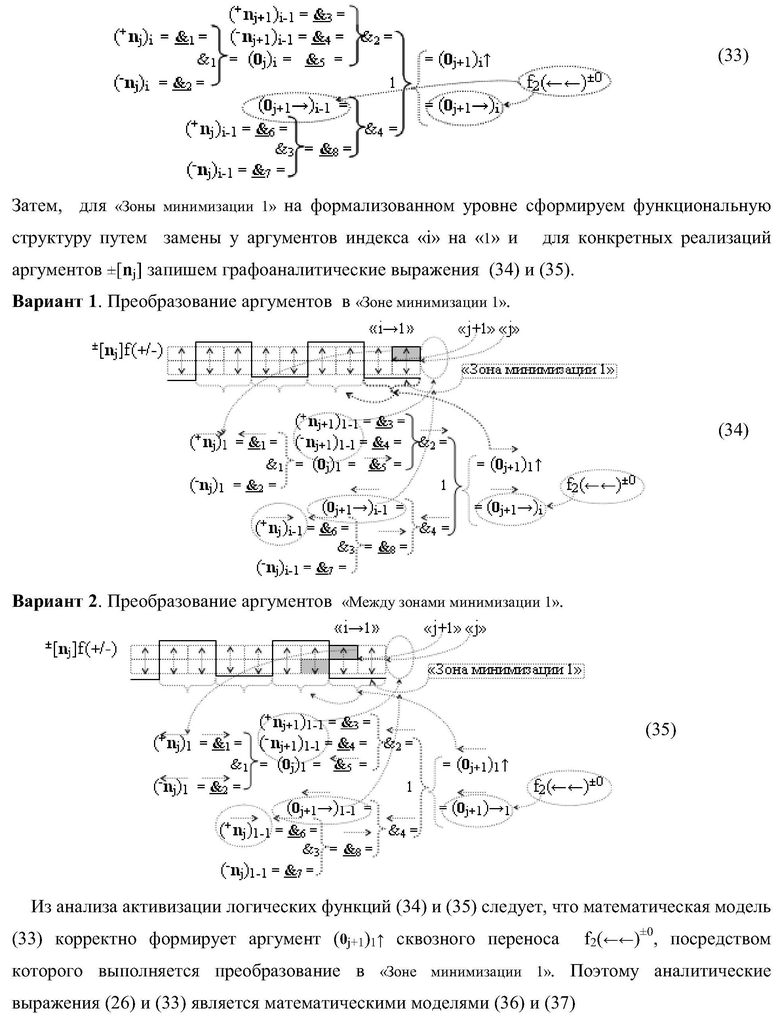

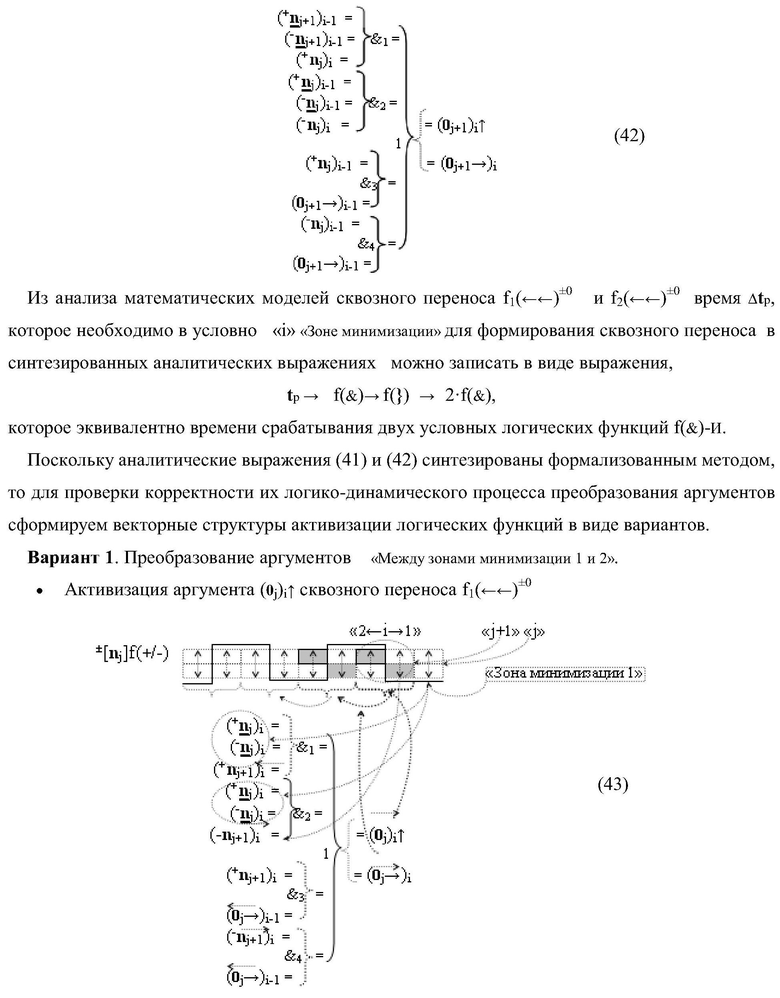

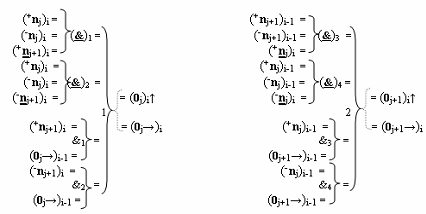

2. Способ активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру ±[n

j]f(+/-)min аналоговых сигналов, в котором для активизации аргумента (0

j+1→)i и аргумента (0

j→)i выполняют одновременный анализ как аргумента локального переноса (0

j+1→)i-1 «i-1» «Зоны минимизации» посредством функциональной структуры условно «j+1» разряда с входными логическими функциями f7(&)-И, f8(&)-И и выходной логической функцией f2(})-ИЛИ, так и аргумента локального переноса (0

j→)i-1 «i-1» «Зоны минимизации» посредством функциональной структуры условно «j» разряде с входными логическими функциями логических функций f3(&)-И и f4(&)-И и выходной логической функцией f1(})-ИЛИ, и активизируют аргумент локального переноса (0

j+1→)i и (0

j→)i сквозного последовательного переноса f1,2(←←)±0 в «i» «Зоне минимизации» на функциональной выходной связи логической функции f1(})-ИЛИ и f2(})-ИЛИ соответственно, отличающийся тем, что в функциональной структуре условно «j+1» разряда посредством f7(&)-И и f8(&)-И выполняют дополнительный анализ активности положительного аргумента (+

n

j)i-1 и условно отрицательного аргумента (-

n

j)i-1 условно «j» разряда «i-1» «Зоны минимизации», а также посредством логических функций f5(&)-И и f6(&)-И выполняют одновременный анализ активности положительного аргумента (+

n

j+1)i-1 с измененным уровнем аналогового сигнала и условно отрицательного аргумента (-

n

j+1)i-1 с измененным уровнем аналогового сигнала условно «j+1» разряда «i-1» «Зоны минимизации» и выполняют посредством логических функций f5(&)-И и f6(&)-И дополнительный анализ положительного аргумента (+

n

j)i и условно отрицательного аргумента (-

n

j)i аналогового сигнала условно «j» разряда «i» «Зоны минимизации», а в функциональной структуре условно «j» разряда посредством f3(&)-И и f4(&)-И выполняют дополнительный анализ активности положительного аргумента (+

n

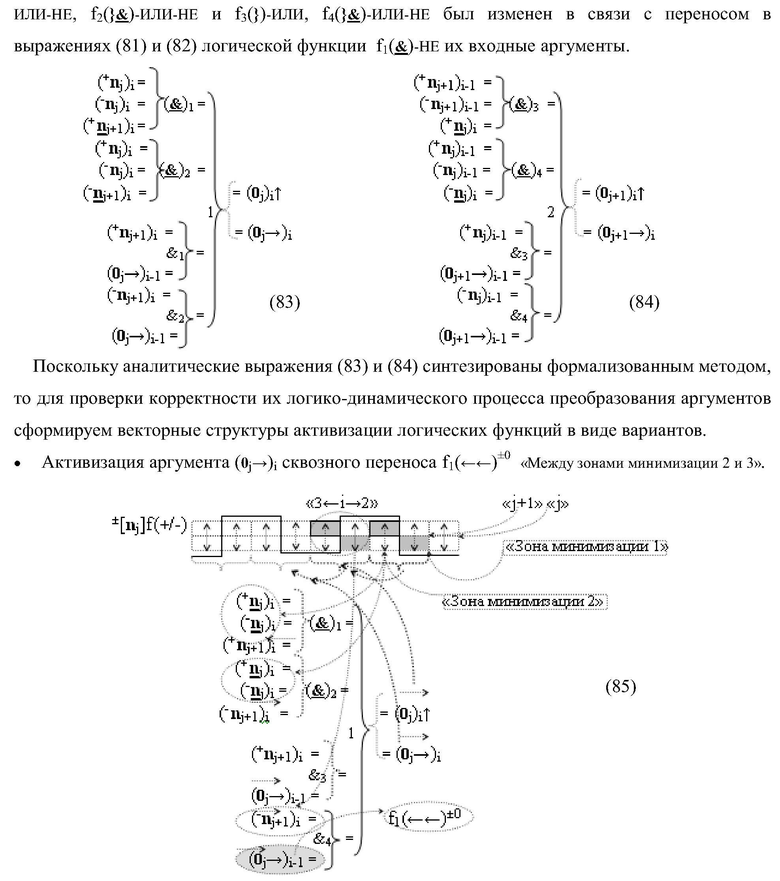

j+1)i-1 и условно отрицательного аргумента (-

n

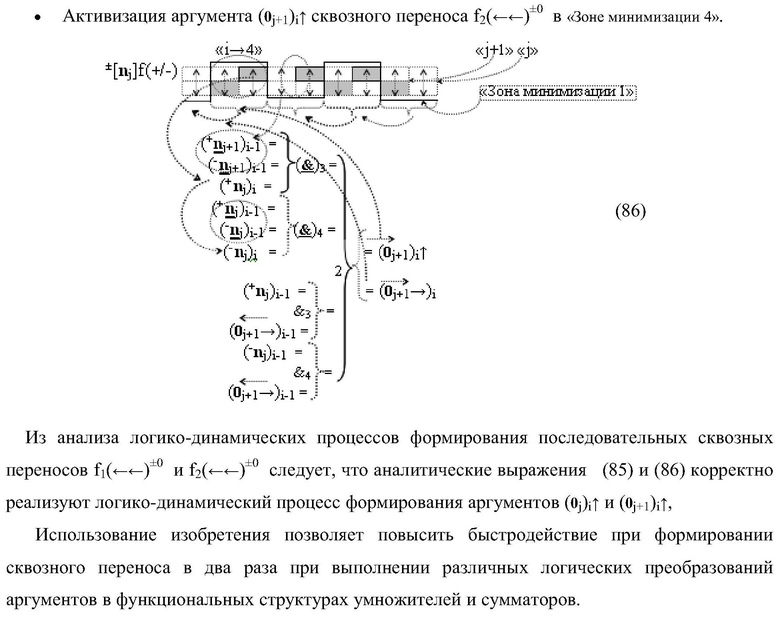

j+1)i-1 условно «j+1» разряда «i» «Зоны минимизации», а также посредством логических функций f1(&)-И и f2(&)-И выполняют одновременный анализ активности положительного аргумента (+

n

j)i-1 с измененным уровнем аналогового сигнала и условно отрицательного аргумента (-

n

j)i-1 с измененным уровнем аналогового сигнала условно «j» разряда «i-1» «Зоны минимизации» и выполняют посредством логических функций f1(&)-И и f2(&)-И дополнительный анализ положительного аргумента (+

n

j+1)i и условно отрицательного аргумента (-

n

j+1)i аналогового сигнала условно «j» разряда «i» «Зоны минимизации», при этом логико-динамический процесс преобразования аргументов аналоговых сигналов реализуют в соответствии с математической моделью сигнала условно «j+1» разряда и условно «j» разряда вида

где  - логическая функция f1(&)-И;

- логическая функция f1(&)-И;  - логическая функция f1(})-ИЛИ.

- логическая функция f1(})-ИЛИ.

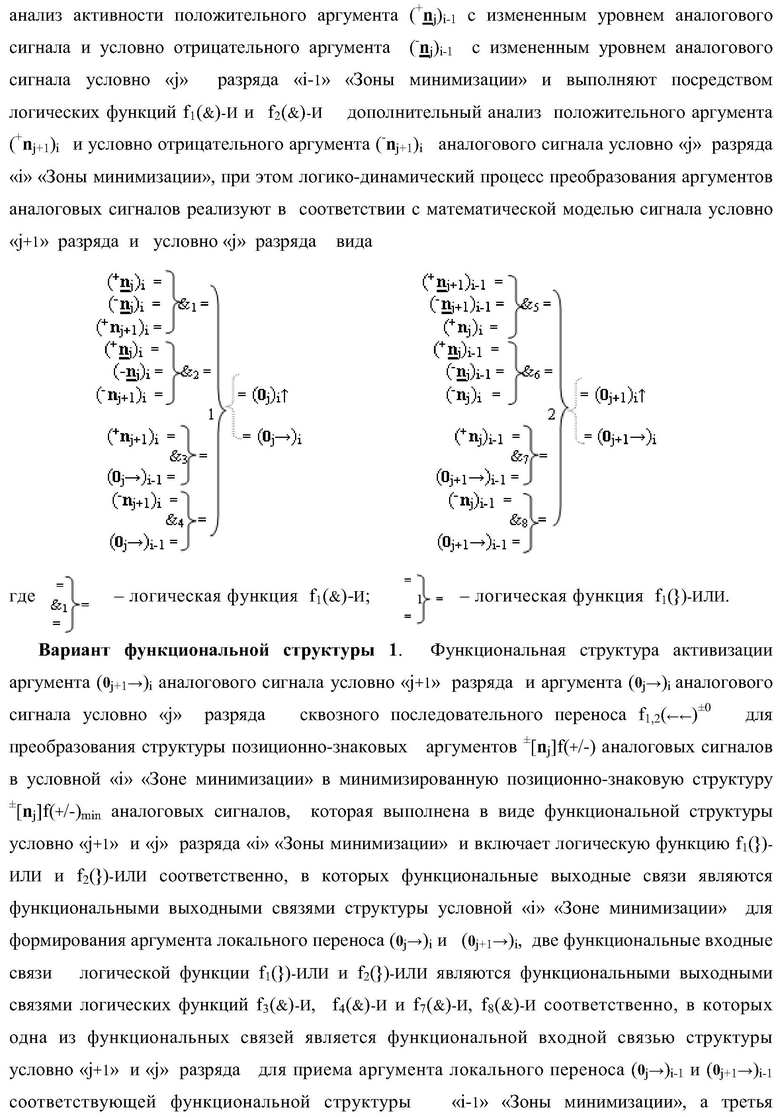

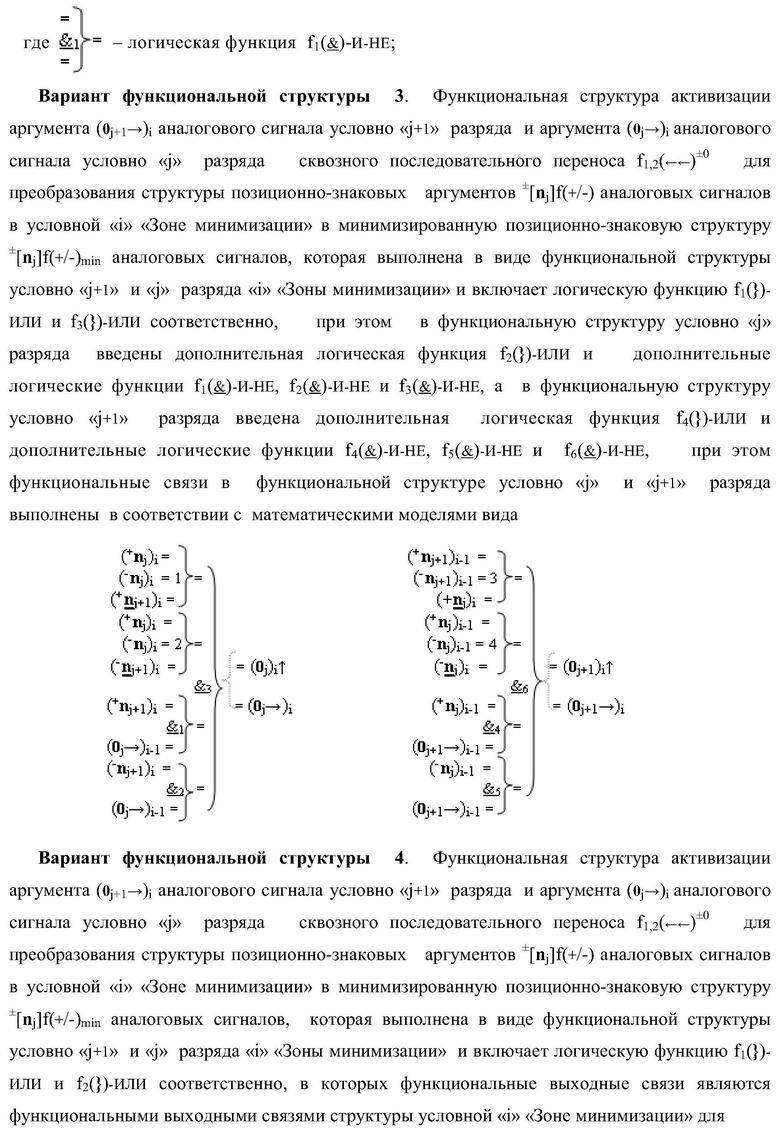

3. Функциональная структура активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру

±[n

j]f(+/-)min аналоговых сигналов, которая выполнена в виде функциональной структуры условно «j+1» и «j» разряда «i» «Зоны минимизации» и включает логическую функцию f1(})-ИЛИ и f2(})-ИЛИ соответственно, в которых функциональные выходные связи являются функциональными выходными связями структуры условной «i» «Зоне минимизации» для формирования аргумента локального переноса (0

j→)i и (0

j+1→)i, две функциональные входные связи логической функции f1(})-ИЛИ и f2(})-ИЛИ являются функциональными выходными связями логических функций f3(&)-И, f4(&)-И и f7(&)-И, f8(&)-И соответственно, в которых одна из функциональных связей является функциональной входной связью структуры условно «j+1» и «j» разряда для приема аргумента локального переноса (0

j→)i-1 и (0

j+1→)i-1 соответствующей функциональной структуры «i-1» «Зоны минимизации», а третья функциональная входная связь логической функции f1(})-ИЛИ и f2(})-ИЛИ является функциональной выходной связью логической функции f1(&)-И и f5(&)-И, отличающаяся тем, что в функциональную структуру условно «j» разряда введены дополнительная логическая функция f2(&)-И, а в функциональную структуру условно «j+1» разряда введена дополнительная логическая функция f6(&)-И соответственно, при этом функциональные связи в структуре условно «j» и «j+1» разряда выполнены в соответствии с математическими моделями вида

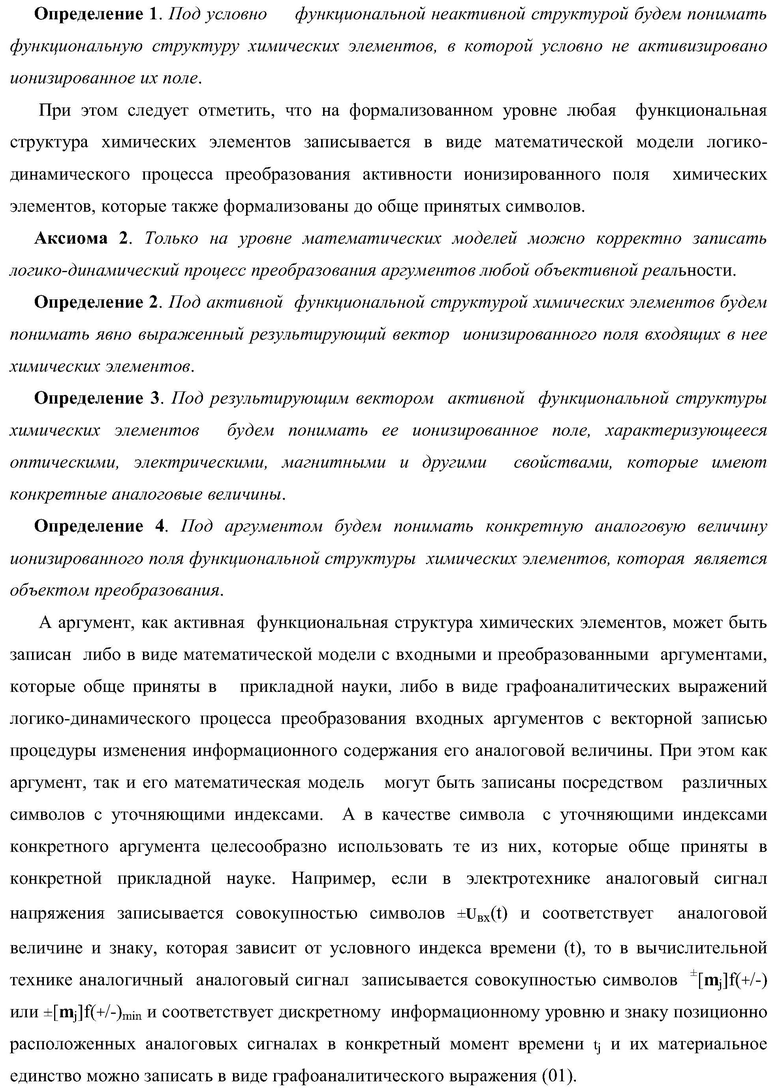

4. Функциональная структура активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру

±[n

j]f(+/-)min аналоговых сигналов, которая выполнена в виде функциональной структуры условно «j+1» и «j» разряда «i» «Зоны минимизации», отличающаяся тем, что в функциональную структуру условно «j» разряда введены логические функции f1(

&

)-И-НЕ, f2(

&

)-И-НЕ, f3(

&

)-И-НЕ, f4(

&

)-И-НЕ и f5(

&

)-И-НЕ, а в функциональную структуру условно «j+1» разряда введены логические функции f6(

&

)-И-НЕ, f7(

&

)-И-НЕ, f8(

&

)-И-НЕ, f9(

&

)-И-НЕ и f10(

&

)-И-НЕ, при этом функциональные связи в функциональной структуре условно «j» и «j+1» разряда выполнены в соответствии с математическими моделями вида

где  - логическая функция f1(

&

)-И-НЕ;

- логическая функция f1(

&

)-И-НЕ;

5. Функциональная структура активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру

±[n

j]f(+/-)min аналоговых сигналов, которая выполнена в виде функциональной структуры условно «j+1» и «j» разряда «i» «Зоны минимизации» и включает логическую функцию f1(})-ИЛИ и f3(})-ИЛИ соответственно, отличающаяся тем, что в функциональную структуру условно «j» разряда введены дополнительная логическая функция f2(})-ИЛИ и дополнительные логические функции f1(

&

)-И-НЕ, f2(

&

)-И-НЕ и f3(

&

)-И-НЕ, а в функциональную структуру условно «j+1» разряда введена дополнительная логическая функция f4(})-ИЛИ и дополнительные логические функции f4(

&

)-И-НЕ, f5(

&

)-И-НЕ и f6(

&

)-И-НЕ, при этом функциональные связи в функциональной структуре условно «j» и «j+1» разряда выполнены в соответствии с математическими моделями вида

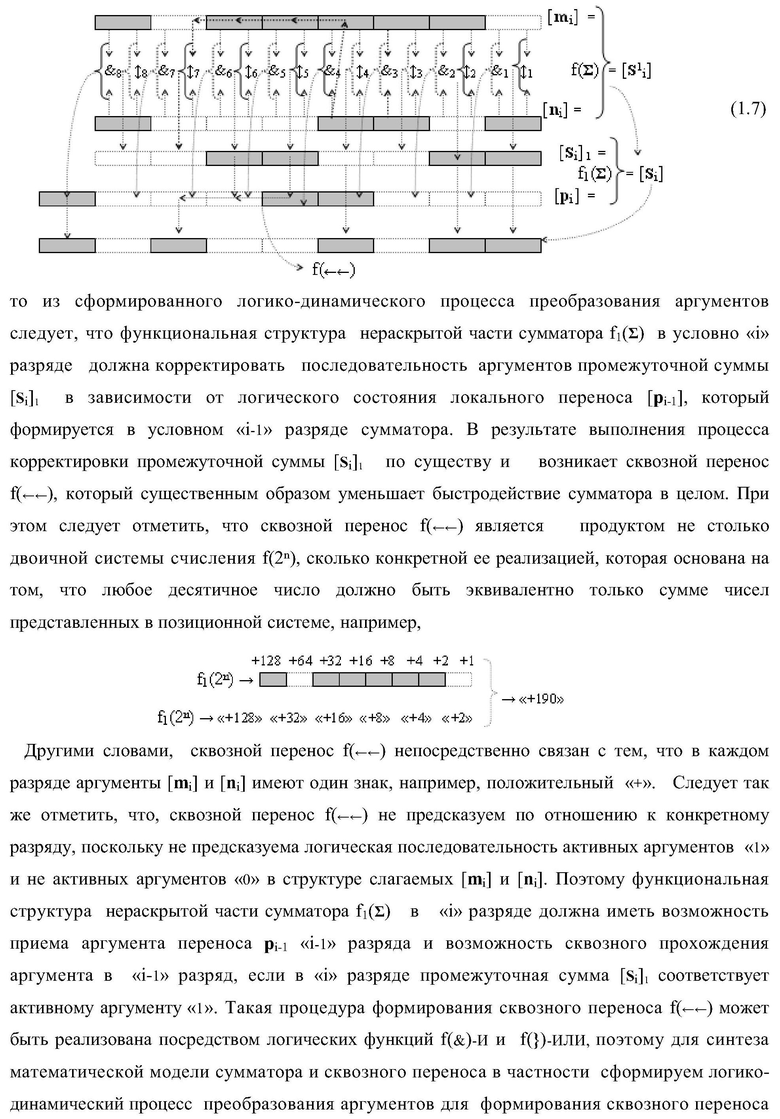

6. Функциональная структура активизации аргумента (0

j+1→)i аналогового сигнала условно «j+1» разряда и аргумента (0

j→)i аналогового сигнала условно «j» разряда сквозного последовательного переноса f1,2(←←)±0 для преобразования структуры позиционно-знаковых аргументов ±[n

j]f(+/-) аналоговых сигналов в условной «i» «Зоне минимизации» в минимизированную позиционно-знаковую структуру

±[n

j]f(+/-)min аналоговых сигналов, которая выполнена в виде функциональной структуры условно «j+1» и «j» разряда «i» «Зоны минимизации» и включает логическую функцию f1(})-ИЛИ и f2(})-ИЛИ соответственно, в которых функциональные выходные связи являются функциональными выходными связями структуры условной «i» «Зоне минимизации» для формирования аргумента локального переноса (0

j→)i и (0

j+1→)i, две функциональные входные связи логической функции f1(})-ИЛИ и f2(})-ИЛИ являются функциональными выходными связями логических функций f3(&)-И, f4(&)-И и f7(&)-И, f8(&)-И соответственно, в которых одна из функциональных связей является функциональной входной связью структуры условно «j+1» и «j» разряда для приема аргумента локального переноса (0

j→)i-1 и (0

j+1→)i-1 соответствующей функциональной структуры «i-1» «Зоны минимизации», отличающаяся тем, что в функциональную структуру условно «j» разряда введены дополнительные логические функции f1(}&

)-ИЛИ-НЕ и f2(}&

)-ИЛИ-НЕ, а в функциональную структуру условно «j+1» разряда введены дополнительные логические функции f3(}&

)-ИЛИ-НЕ, f4(}&

)-ИЛИ-НЕ, при этом функциональные связи в функциональной структуре условно «j» и «j+1» разряда выполнены в соответствии с математическими моделями вида

где  - логическая функция f1(}&

)-ИЛИ-НЕ.

- логическая функция f1(}&

)-ИЛИ-НЕ.

| Д.УЭЙКЕРЛИ | |||

| Проектирование цифровых устройств, Т.1 | |||

| - М.: Постмаркет, 2002, с.502, рис.5.86 | |||

| Блок формирования сквозного переноса в сумматоре | 1984 |

|

SU1196852A1 |

| Устройство для параллельного сложения чисел, представленных в двоичной знакоразрядной системе счисления | 1989 |

|

SU1727120A1 |

| US 4868777 A, 19.09.1989 | |||

| JP 63197227 A, 16.08.1988. | |||

Авторы

Даты

2011-07-27—Публикация

2009-08-24—Подача