В настоящее время в связи с интенсивным введением вычислительных средств в состав систем управления (СУ) высокоманевренными объектами авиационной и ракетно-космической техники и особенно в космические аппараты, длительное время работающие при воздействии дестабилизирующих факторов космического пространства, возникла задача создания новых малогабаритных устройств для получения навигационной информации с оптических датчиков (оптико-электронных средств), которые дают информацию об угловом положении объектов визирования (чаще всего определенные созвездия, характеризуемые фиксированным угловым расстоянием между звездами созвездия).

Кроме того, для ряда объектов, к которым относятся обычные самолеты и космические челноки типа «БУРАН», возникает задача уточнения координат при заходе на посадку, для чего используют карты местности в зоне захода на посадку.

Одним из вариантов является использование радиовысотомеров, информация которых сравнивается с эталонными картами высот местности.

В том и другом случае требуется проведение большого объема обработки полученной с датчиков информации с части устранения различного вида помех (фильтрация) и проведения сравнения отфильтрованной информации с эталонными картами.

В идеальном случае в центральную управляющую бортовую вычислительную систему (БЦВС) информация должна поступать в цифровом виде, содержащем угловую ориентацию и угловые скорости объекта, в первом случае, и отклонения пространственных координат центра масс и объекта управления в пространстве, во втором.

В связи с этим в состав подсистем ориентации и определения координат центра масс вводят собственные специализированные вычислительные устройства (СВУ), обеспечивающие формирование упомянутой выше системы координат в математическом виде путем непрерывной обработки информации оптических или радиоизмерительных датчиков.

Особенностью этих СВУ является необходимость обеспечения быстрого (практически непрерывного) пересчета входной информации датчиков в систему координат, что позволяет использовать полученную информацию для коррекции ориентации и движения объекта управления. Основными вычислительными задачами СВУ являются однотипные задачи перебора различной информации. Учитывая необходимость размещения СВУ на борту аппаратов от него требуются минимально возможные габаритно-массовые характеристики и энергопотребление. Эти ограничения повлекли широкое внедрение в состав бортовых вычислительных устройств больших и сверхбольших интегральных микросхем (БИС и СБИС) микропроцессоров (МП) и запоминающих устройств (ЗУ), изготавливаемых в основном по КМОП технологии. Это позволяет получить хорошие приборные характеристики, но выдвигает проблему обеспечения работоспособности устройства при длительной работе в условиях воздействия дестабилизирующих факторов космического пространства, когда под действием ионизирующего излучения и накопления дозовых изменений параметров БИС снижается их быстродействие и СВУ теряет работоспособность, несмотря на отсутствие катастрофических отказов.

Все это выдвигает задачу сохранения работоспособности устройства, например, путем изменения быстродействия, задаваемого средствами синхронизации вычислителей, включающих задающие генераторы. Задача может быть решена подбором частоты задающего генератора в соответствии с текущим быстродействием элементов и устройства в целом. При этом частоту желательно изменять в обоих направлениях, чтобы обеспечить на каждый интервал времени максимальное быстродействие вычислителя.

Известны вычислительные устройства, реализованные на основе МП типа 8085 (См. И.Янсен. Курс цифровой электроники. Т.4 / Микрокомпьютеры, с.190-195, рис.4.2 и 4.5). Устройства содержат микропроцессор и подключенные к нему ЗУ разного типа (постоянные (ПЗУ) и оперативные (ОЗУ)).

Реализация такого типа вычислителей на основе современных КМОП БИС позволяет получить небольшие габариты устройств при приемлемом энергопотреблении.

Однако особенность их структуры, а именно последовательное обращение по общим связям к памяти программ и данных не позволяет получить высокую производительность, требуемую от СВУ в части перебора однотипной информации.

Реализация задач опознавания образов (сравнения с эталоном) с обработкой большого объема информации датчиков на указанных выше устройствах на основе МП 8085 не удовлетворяет требованиям, предъявляемым к СВУ.

Известны решения, направленные на повышение производительности вычислителей путем введения дополнительных блоков, обеспечивающих повышение производительности управляющих ЭВМ, подключением управляющей ЭВМ матрицы из малых ЭВМ. Примером может быть вычислительная система ILLIAC IV (См. Б. Байцер. Архитектура вычислительных комплексов., Т.1, стр.23, рис.1.8. М.: Мир, 1974).

Данное решение может быть принято за прототип. Решение на специальном матричном аппаратурном расширителе - матричном сопроцессоре (МАП)) отдельных задач, например сравнения с эталоном и поиск решения с минимальной разностью, как можно сделать в известном решении существенно, сокращает время сравнения выделенных функций, но производительность управляющей ЭВМ при этом увеличивается незначительно, так как каждый вычислитель МАП работает по своей программе, обращаясь поочередно к ПЗУ и ОЗ. Кроме того, обработка данных, полученных от датчика, ведется последовательно. С целью повышения производительности СВУ целесообразно реализовать параллельную одновременную обработку разной информации на вычислителях МАП.

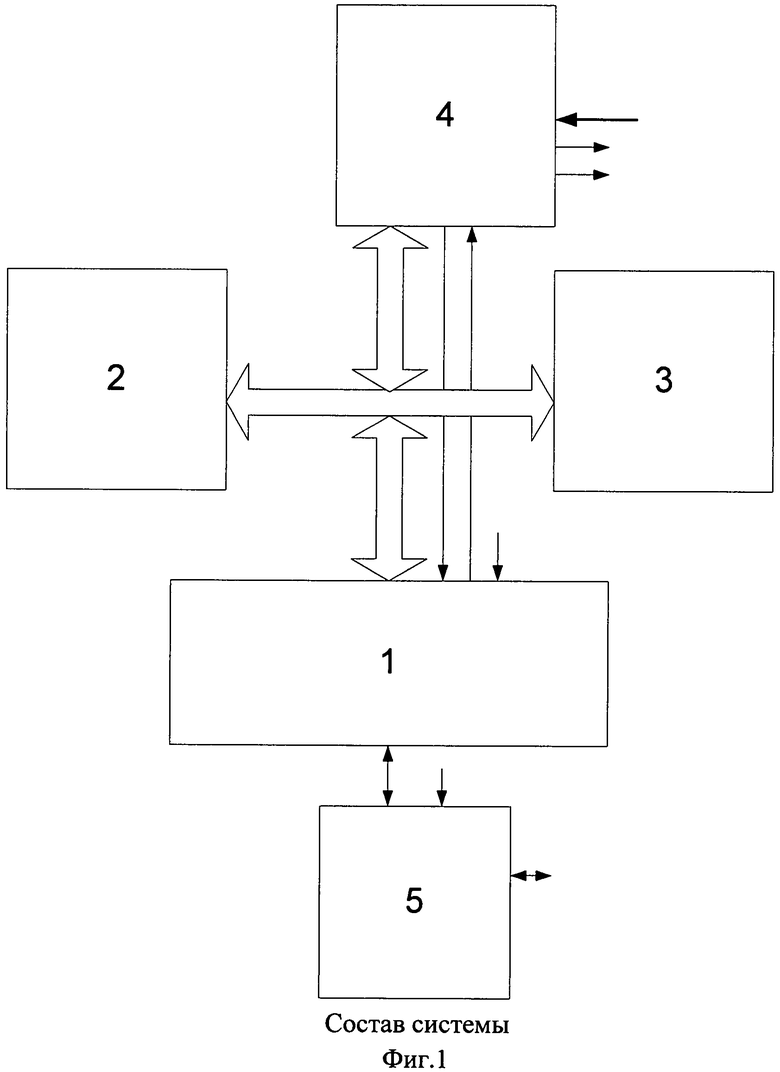

Предлагается система обработки изображений, содержащая управляющий микропроцессор (МП) с подключенными к нему процессором обмена (ПО) блоками запоминающих устройств и блок матричного процессора (МАП), который подключен к магистрали процессора, аналогично блокам ЗУ. Структура предлагаемой вычислительной системы приведена на чертеже (Фиг.1), где цифрой 1 обозначен управляющий микропроцессор (МП), например серии 1867ВМ3, цифрой 2 обозначен модуль ОЗУ. Цифрой 3 обозначен модуль ПЗУ, цифрой 4 обозначен МАП, цифрой 5 обозначен процессор обмена. Все эти модули подключены к шинам процессора. Кроме того, выход прерывания МП подключен к соответствующему входу МАП, выход прерывания которого подключен к соответствующему входу МП. Управляющий вход МАП является одноименным входом устройства, а его первый и второй частотные выходы подключены соответственно к частотным входам МП и процессоров обмена. Двунаправленные входы-выходы процессора обмена являются входами-выходами вычислительного устройства для связи с датчиками и подсистемой верхнего уровня - БЦВС соответственно.

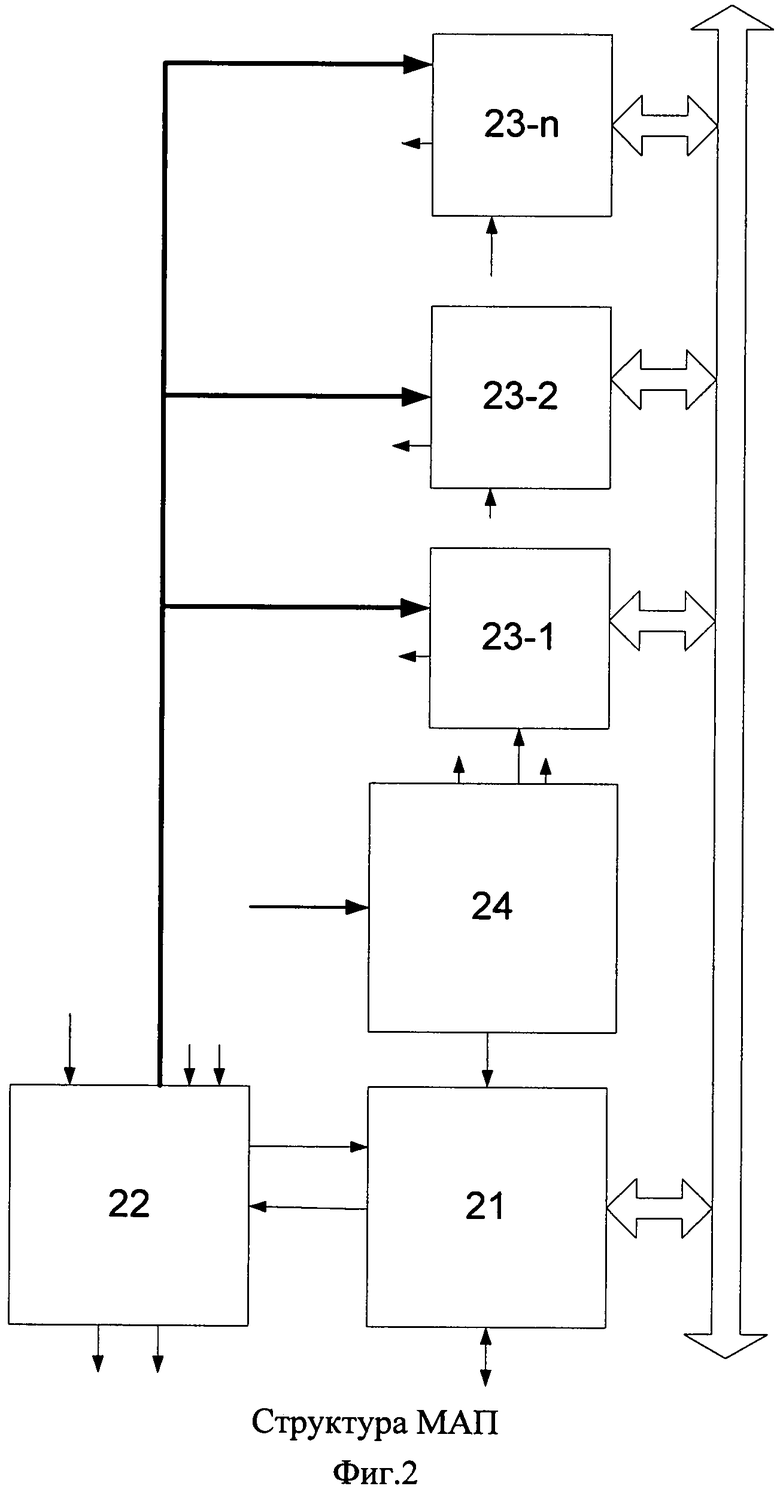

Структура МАП приведена на чертеже (Фиг 2), где цифрой 21 обозначен процессор обмена (МПО), в качестве которого может быть использован микропроцессор на основе серии 1825ВС3, цифрой 22 обозначено УСТРОЙСТВО УПРАВЛЕНИЯ (УУ), цифрами от 23-1 до 23-n обозначены матричные микропроцессоры (ММП) (БИС серии 1825ВС3 с собственными ОЗУ), образующие матрицу, цифрой 24 обозначен формирователь синхроимпульсов (ФСИ). Двунаправленные входы-выходы МПО являются входами-выходами МАП, подключенными к МП, а первая и вторая группа адресных выходов БС подключены к адресным входам соответственно ЛОЗУ и ФАМ. Управляющий вход УУ является входом МАП и устройства в целом, а первый и второй частотные выходы ФСИ являются выходами МАП.

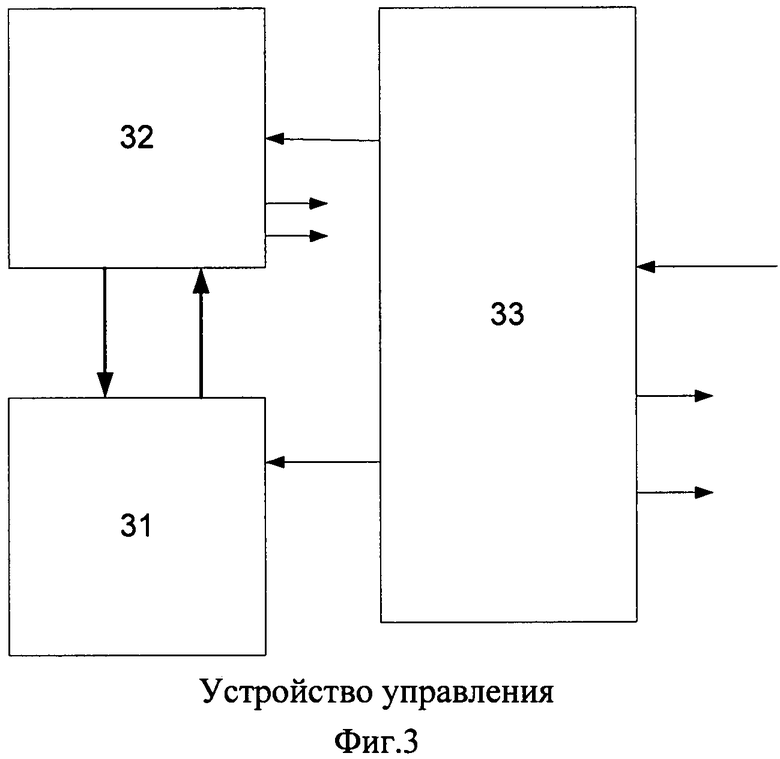

Остальные синхронизирующие выходы ФСИ подключены к синхровходам микропроцессоров 23-1 - 23-n, УУ22 и МПО 21, подключенного магистральной шиной ко всем микропроцессорам, управляющие входы которых подключены к выходу УУ, к входам которого подключены выходы признаков микропроцессоров. Адресные входы и дополнительный выход УУ подключены к соответствующим выходам и входам МПО. Структура устройства управления приведена на чертеже (Фиг.3), где цифрой 31 обозначен формирователь адреса микропрограмм (ФАМ), цифрой 32 - микропрограммное запоминающее устройство (МПЗУ), цифрой 33 обозначен формирователь синхроимпульсов. Управляющий вход и первый и второй частотные выходы ФСИ являются одноименными входом и выходами устройства управления. Синхровходы ФАМ и МПЗУ подключены к первой и второй группам выходов ФСИ, а выходы МПЗУ являются выходами устройства управления.

Структура формирователя синхроимпульсов приведена на чертеже (Фиг.4), где цифрами 41, 42, 43 обозначены соответственно основной, первый и второй задающие генераторы частоты, а цифрой 44 обозначен узел формирования синхроимпульсов, выходы которого являются синхронизирующими выходами формирователя, а выходы первого и второго генераторов являются первым и вторым частотным выходами формирователя, управляющий вход которого является входом первого и второго задающих генераторов.

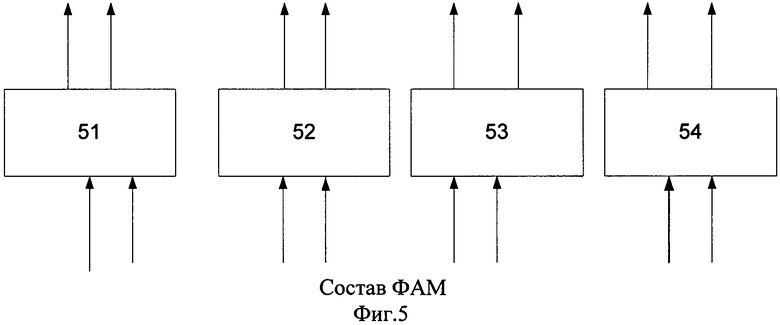

Структура формирователя адреса микрокоманд (ФАМ) приведена на чертеже (Фиг.5), где цифрой 51 обозначен регистр смещения, цифрой 52 обозначен регистр кода операции, цифрой 53 обозначен регистр признаков и цифрой 54 обозначен счетчик адреса.

Входы регистра кода операции и информационный и счетный входы счетчика являются входами формирователя, подключенными к выходу МПО.

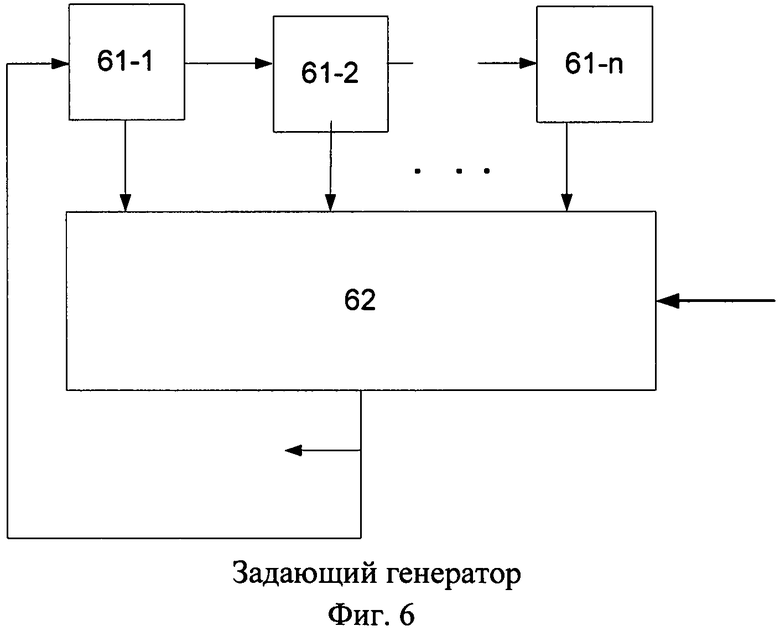

Схема генератора частоты приведена на чертеже (Фиг.6), где цифрами от 61-1 до 61-n обозначены n последовательно соединенных инверторов, подключенных к входу мультиплексора 62, выход которого подключен к входу первого инвертора, а вход является управляющим входом генератора.

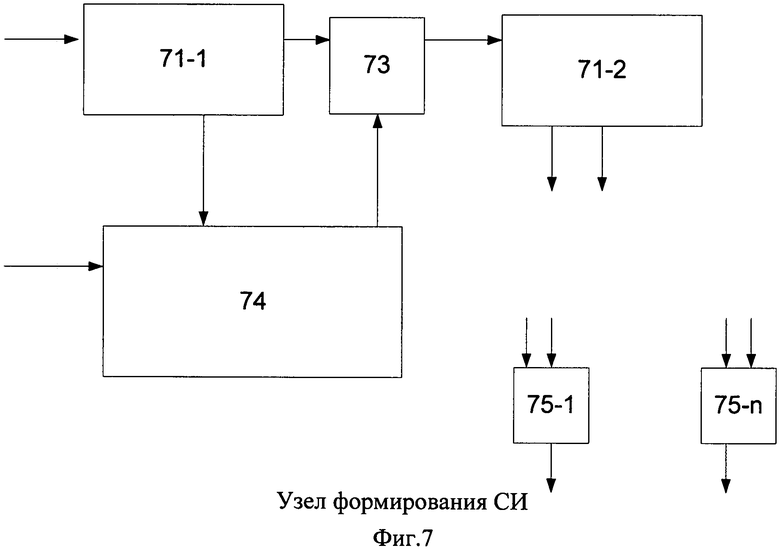

Структура узла формирования синхроимпульсов (СИ) приведена на чертеже (Фиг.7), где цифрами 71-1 и 71-2 обозначены младшая и старшая секции сдвигающего регистра, цифрой 73 обозначен элемент И, цифрой 74 обозначен триггер привязки, цифрами от 75-1 до 75-n обозначены триггеры-формирователи. Управляющий вход триггера привязки является одноименным входом узла, а синхронизирующий вход подключен к первому выходу младшей секции сдвигающего регистра, вход которой является входом узла, подключенным к основному генератору частоты, второй выход секции подключен ко входу элемента И, выход которого подключен ко входу второй секции сдвигающего регистра, четные и нечетные выходы которой являются соответственно запускающими и сбрасывающими входами триггеров-формирователей, выходы которых являются выходами узла формирования.

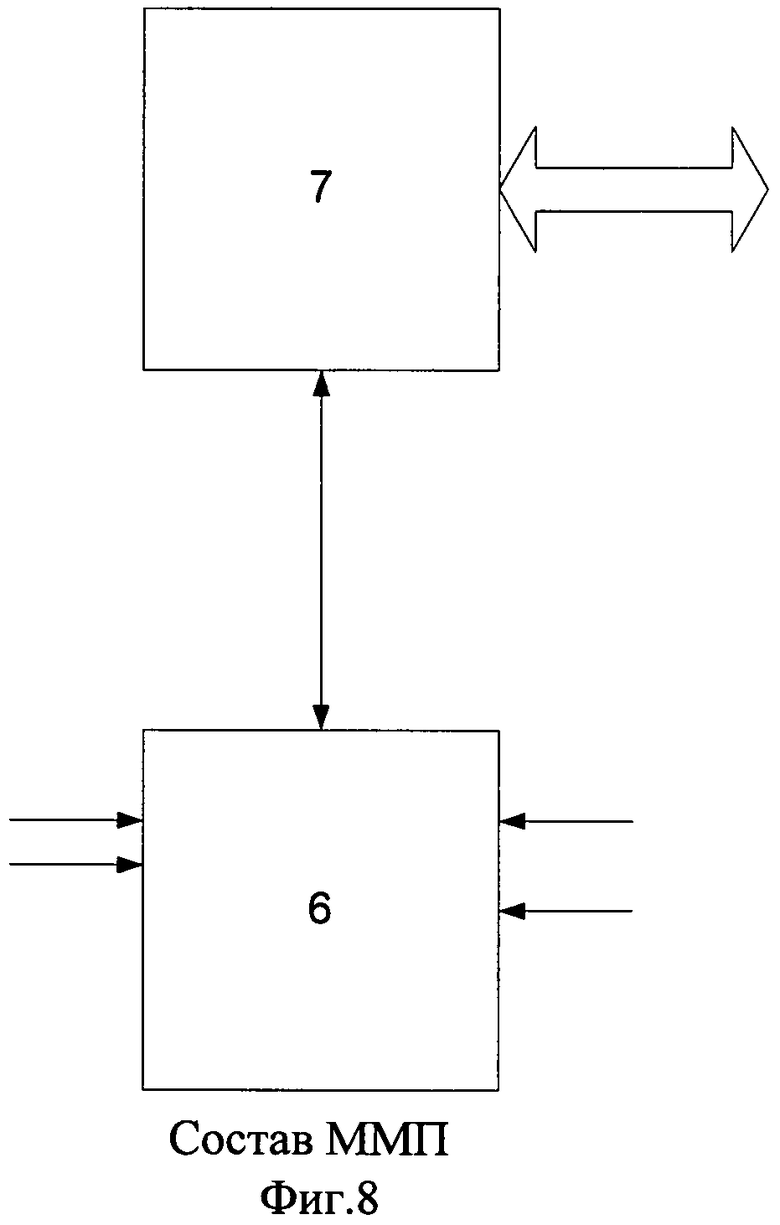

Состав матричного микропроцессора приведен на чертеже (Фиг.8), где цифрой 6 обозначен микропроцессор - БИС 1825ВС3, а цифрой 7 обозначена собственная оперативная память ММП, магистральный вход-выход которой является одноименным входом-выходом ММП, а синхронизирующие и микропрограммные входы и выходы признаков которого являются одноименными входами и выходами ММП.

Устройство работает следующим образом.

МП по своей программе, размещенной в ПЗУ3, выполняет вычисления.

Если требуется обработать полученную информацию, МП проводит обмен с МПО МАП, который загружает данные в собственную память ММП и дает сигнал в их УУ. Для обеспечения доступа к собственной памяти ММП на время сеанса связи с магистралью данных синхроимпульсы с ММП, что исключает конфликты при обращении к собственной памяти ММП со стороны БИС 1825ВС3 и магистрали. С началом поступления синхроимпульсов в регистр кода операции и счетчик ФАМ заносятся начальные значения, начинается выборка микрокоманд и выполнение заданной операции с записью результатов БИС 1825ВС3 в собственную память. МПО считывает полученные результаты, проводит выбор наименьшего значения и передает полученный результат в МП, после чего ожидает очередного обращения со стороны МП.

Дополнительно предусмотрено управление быстродействием устройства путем перестройки частот задающих генераторов по командам БЦВС путем изменения количества инверторов в кольце инверторов 61 подключенных к мультиплексору 62

Перестройка быстродействия производится для отслеживания изменения параметров БИС во времени или из-за действия ионизирующего излучения космического пространства. Кроме того, на отдельных наиболее загруженных по вычислениям участках возможно плановое повышение быстродействия. Возможное максимальное быстродействие для каждого интервала работы определяется по результатам тестовых проверок отдельных компонентов устройства и устанавливается индивидуально для каждого компонента, для чего в состав формирователя синхроимпульсов введены несколько задающих генераторов, для каждого из которых в общем управляющем слове отведена своя часть кода.

Все эти решения обеспечивают максимальную производительность вычислительного устройства на протяжении всего времени работы инерциальной системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

Изобретение относится к системам обработки изображения. Техническим результатом является расширение функциональных возможностей за счет подбора частоты задающего генератора в соответствии с текущим быстродействием элементов и устройства в целом. Система обработки изображений содержит микропроцессор с подключенными к его магистральным шинам оперативным и постоянным запоминающими устройствами и подключенный к его входу-выходу процессор обмена, дополнительно к магистральным шинам подключен матричный арифметический процессор, управляющий вход которого является одноименным входом системы, входы и выходы прерывания подключены к выходам и входам прерывания микропроцессора, а первый и второй частотные выходы подключены к частотным входам микропроцессора и процессора обмена, вход-выход которого является входом-выходом системы. 7 з.п. ф-лы. 8 ил.

1. Система обработки изображений, содержащая микропроцессор с подключенными к его магистральным шинам оперативным и постоянным запоминающими устройствами и подключенный к его входу-выходу процессор обмена, отличающаяся тем, что дополнительно к магистральным шинам подключен матричный арифметический процессор, управляющий вход которого является одноименным входом системы, входы и выходы прерывания подключены к выходам и входам прерывания микропроцессора, а первый и второй частотные выходы подключены к частотным входам микропроцессора и процессора обмена, вход-выход которого является входом-выходом системы.

2. Система по п.1, отличающаяся тем, что матричный арифметический процессор содержит микропроцессор обмена, к которому через магистраль подключены n матричных микропроцессоров, микропрограммные и синхронизирующие входы и выходы признаков которых подключены к соответствующим выходам и входам устройства управления, подключенного дополнительными входами и выходами к одноименным выходам и входам микропроцессора обмена, вход-выход которого является входом-выходом матричного арифметического процессора.

3. Система по п.2, отличающаяся тем, что матричный микропроцессор содержит собственно микропроцессор, синхронизирующие и микропрограммные входы и выходы признаков которого являются одноименными входами и выходами матричного микропроцессора, а вход-выход подключен к собственному запоминающему устройству, магистральный вход-выход которого является одноименным входом-выходом матричного микропроцессора.

4. Система по п.2, отличающаяся тем, что устройство управления содержит формирователь адреса микропрограмм, адресные вход и выход которого подключены к одноименным входам микропрограммного запоминающего устройства, выходы которого являются выходами устройства, вход синхронизации подключен к первому выходу формирователя синхроимпульсов, второй выход которого подключен к синхровходу формирователя адреса микропрограмм, а управляющий вход, первый и второй частотные выходы которого являются одноименными входом и выходом устройства.

5. Система по п.4, отличающаяся тем, что формирователь синхроимпульсов содержит основной, первый и второй задающие генераторы, управляющие входы которых являются входом формирователя, причем выходы первого и второго генераторов являются частотными выходами формирователя, а выход основного генератора подключен к входу узла формирования синхроимпульсов, выходы которого являются выходами формирователя.

6. Система по п.4, отличающаяся тем, что формирователь адреса микропрограмм содержит регистры кода операции, смещения, признаков и счетчик, входы и выходы которых являются соответствующими входами и выходами формирователя.

7. Система по п.5, отличающаяся тем, что задающий генератор содержит n последовательно соединенных инверторов, выходы которых подключены к входам мультиплексора, выход которого подключен к входу первого инвертора и является выходом генератора, а управляющий вход - одноименным входом формирователя.

8. Система по п.5, отличающаяся тем, что узел формирования синхроимпульсов содержит первую и вторую секции сдвигового регистра, причем вход первой секции является входом узла, а выход подключен к первому входу элемента И, ко второму входу которого подключен выход триггера привязки, вход которого является входом узла, дополнительный вход подключен к одноименному выходу первой секции, а выходы четных и нечетных разрядов второй секции подключены соответственно к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются выходами узла.

| EP 0762328 A2, 12.03.1997 | |||

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| 0 |

|

SU188828A1 | |

| СИСТЕМА ДИСПЛЕЯ | 1991 |

|

RU2119187C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

Авторы

Даты

2012-05-27—Публикация

2011-06-23—Подача