Изобретение относится к автоматизированным системам управления технологическими процессами при наземных испытаниях изделий ракетно-космической техники (РКТ) и может быть использовано при стендовой отработке авиационной, транспортной техники, а также химических установок.

Особенностями стендовых наземных испытаний изделий РКТ являются высокие требования к быстродействию систем управления этими испытаниями и распределенный характер построения этих систем. Цикл работы управляющих программируемых контроллеров, на которых строятся эти системы, составляет обычно 10-20 мс. Распределенный характер их связан с наличием на стенде ряда расположенных на удалении друг от друга (из соображений безопасности) технологических систем с различными выполняемыми функциями (по управлению системами горючего, окислителя, воды, газами; по управлению системами изделия, стенда; по реализации задач регулирования, логического управления, аварийной защиты). В итоге количество управляющих контроллеров с учетом необходимого (из требований надежности) их резервирования может достигать на одном стенде 15-20 комплектов, реализующих до 10 подсистем системы управления этим стендом и изделием.

Информация, в том числе измерительная, циркулирующая в управляющих контроллерах, должна быть синхронизирована, чтобы подсистемами выдавались команды с заданной временной точностью и обеспечивалась корректная послепусковая обработка зарегистрированной информации. Кроме того, синхронизация очень важна для управляющих контроллеров, включенных по схеме 2 из 3, для исключения расхождения по различным ветвям реализуемых в них алгоритмов управления.

Известно устройство синхронизации системы управления стендовыми испытаниями РКТ (см. статью Афонина В.В. и др. «Синхронизация каналов троированных ПЛК жесткого РВ», журнал «Промышленные АСУ и контроллеры», №6, 2004 г.), реализованное в каждом управляющем контроллере системы управления и содержащее блок сопряжения с локальной вычислительной сетью, связанный первым и вторым входами-выходами соответственно с локальной вычислительной сетью и с первым входом-выходом блока управления, второй вход-выход которого соединен с входами-выходами счетчика цикла и таймера длительности цикла.

Процедура синхронизации работы управляющих контроллеров заключается в этом случае в обмене процессорами управляющих контроллеров сигналами начала очередного цикла их работы и реализации, затем начала отсчета его длительности по логической функции мажоритирования этих сигналов.

Недостатком этого решения является синхронизация каналов каждого троированного или дублированного контроллера, а не всего множества управляющих контроллеров, образующих распределенную в пространстве сеть с различными вариантами их резервирования. В связи с этим возникают проблемы при реализации управляющими контроллерами взаимосвязанных алгоритмов, жестко привязанных к единой шкале времени, и при обработке результатов испытаний.

Техническая задача, решаемая изобретением, заключается в обеспечении единого времени и синхронизации циклов работы распределенной сети однородных управляющих контроллеров независимо от их количества, размещения и варианта резервирования.

Это достигается тем, что в известное устройство синхронизации системы управления стендовыми испытаниями ракетно-космической техники, реализованное в процессоре каждого управляющего контроллера и содержащее блок сопряжения с локальной вычислительной сетью, связанный первым и вторым входами-выходами соответственно с локальной вычислительной сетью и с первым входом-выходом блока управления, второй вход-выход которого соединен с входами-выходами счетчика цикла и таймера длительности цикла, согласно изобретению введены регистр транспортного запаздывания, выход которого подключен ко входу блока управления, счетчик периода коррекции, соединенный своим входом-выходом с третьим входом-выходом блока управления, и регистр периода коррекции, подключенный своим выходом ко входу счетчика периода коррекции.

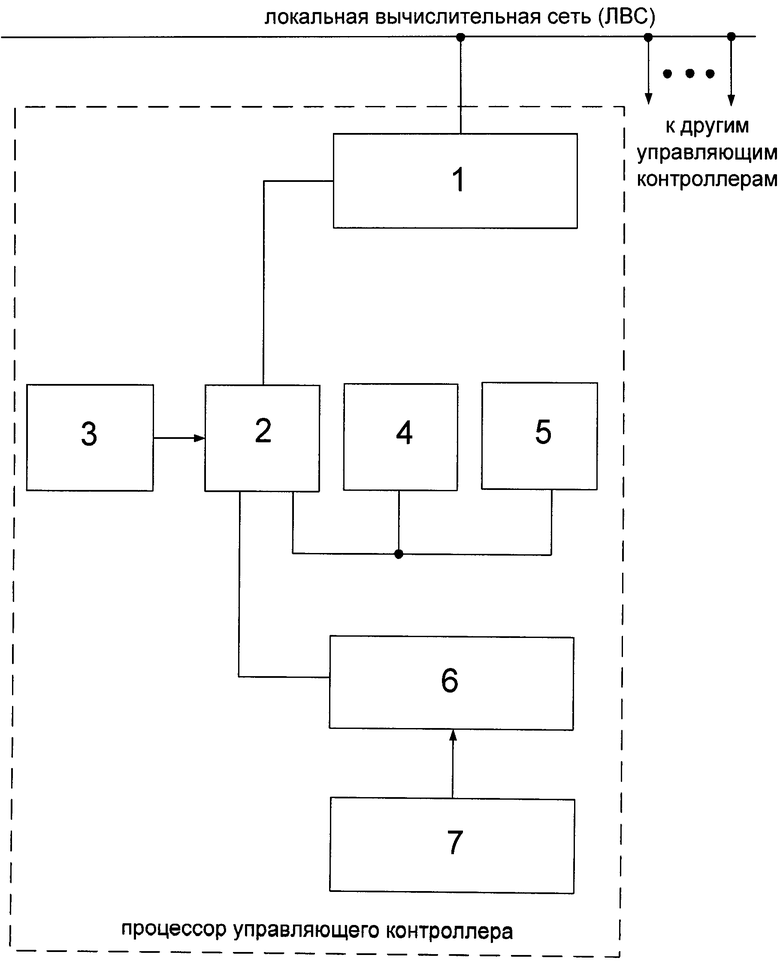

На чертеже изображена схема устройства.

Устройство содержит блок сопряжения с локальной вычислительной сетью 1, первым и вторым входами-выходами соединенный соответственно с локальной вычислительной сетью и первым входом-выходом блока управления 2, регистр транспортного запаздывания 3, подключенный выходом ко входу блока управления 2, счетчик циклов 4 и таймер длительности цикла 5, подключенные входами-выходами ко второму входу-выходу блока управления 2, третий вход-выход которого соединен с входом-выходом счетчика периода коррекции 6. Вход последнего соединен с выходом регистра периода коррекции 7.

Устройство работает следующим образом.

В исходном состоянии все счетчики обнулены. В регистре транспортного запаздывания 3 установлено значение задержки поступления информации из локальной вычислительной сети (ЛВС), определяемое опытным путем. Обычно оно составляет 30-50 мкс. В регистре периода коррекции 7 устанавливается значение 100+5Н, выраженное в количестве циклов работы управляющего контроллера с номером Н в сети. При длительности цикла, равной 10 мс, эти значения для управляющих контроллеров, начиная с определенного первым, будут составлять 1050, 1100, 1150 мс и т.д. С этим периодом времени процессоры управляющих контроллеров через блок управления 2 и блок сопряжения с ЛВС 1 посылают в ЛВС телеграмму о коррекции времени. Телеграмма сопровождается значениями состояний их таймера длительности цикла 5 и счетчика циклов 4.

Устройство в составе процессора первого управляющего контроллера работает следующим образом. В начале очередного цикла работы управляющего контроллера, определяемого в его процессоре блоком управления 2 по сигналу окончания счета таймером длительности цикла 5, из значения счетчика периода коррекции 6, установленного первоначально регистром периода коррекции 7, вычитается единица. Момент окончания счета в счетчике периода коррекции 6 наступит быстрее всего в первом управляющем контроллере (через 1050 мс). В этот же момент времени блок управления 2 считывает значение счетчика циклов 4 и таймера длительности цикла 5 и направляет в ЛВС через блок сопряжения с ЛВС 1 телеграмму коррекции времени в процессорах остальных контроллеров. Эта телеграмма, как указывалось в предыдущем абзаце, сопровождается значениями состояний счетчика циклов 4 и таймера длительности цикла 5 процессора данного управляющего контроллера.

Устройство в составе процессора управляющего контроллера с другим (не с первым) номером работает следующим образом. При получении из ЛВС очередной телеграммы (из описанного выше видно, что при исправности всех управляющих контроллеров это будет телеграмма от первого из них), содержащей значения состояний счетчика циклов 4, равное К-ц1, и таймера длительности цикла 5, равное Т-ц1, процессора первого управляющего контроллера, блок управления 2, получивший через блок сопряжения с ЛВС 1 эти значения в указанный момент времени, присваивает таймеру длительности цикла 5 значение Т-ц1+t, где t высчитывается из регистра транспортного запаздывания 3, а счетчику циклов 4 присваивает значение К-ц1. Затем в счетчик периода коррекции 6 по команде блока управления 2 записывается значение, установленное в регистре периода коррекции 7. Как описано выше, это значение равно 1000+50Н, где Н - номер данного управляющего контроллера. В дальнейшем счетчик периода коррекции 6 уменьшает свое значение на единицу по сигналу таймера длительности цикла 5. В результате выполнения описанных операций процессоры всех управляющих контроллеров будут иметь одинаковые значения счетчиков циклов 4 и таймеров длительности цикла 5.

Незначительные отклонения могут быть связаны с работой операционной системы процессора управляющего контроллера по передаче информации по ЛВС. Из описанного порядка работы устройства следует, что при отказе первого управляющего контроллера функции синхронизации автоматически берет на себя следующий по номеру управляющий контроллер. При включении питания указанная процедура обеспечивает быстрое вхождение системы управления в синхронизм. При работе системы управления значения счетчика циклов 4 и сигналы таймера длительности цикла 5 используются процессором каждого управляющего контроллера при реализации алгоритмов управления испытаниями изделий РКТ. На схеме отсутствуют входы в регистры транспортного запаздывания 3 и периода коррекции 7, что означает принадлежность функции установки кодов в них этим же регистрам, например, с помощью джамперов.

Важным моментом в использовании предлагаемого технического решения является возможность привязки работы управляющих контроллеров к астрономическому времени и повышения надежности синхронизации распределенной системы управления за счет одного или нескольких дополнительных управляющих контроллеров (или их процессорных модулей) с наименьшими номерами, включенных в ЛВС и принимающих сигналы навигационных систем, например Глонасс и GPS.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| Электропривод постоянного тока | 1990 |

|

SU1798881A1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2005 |

|

RU2276402C1 |

| ПРОГРАММНО-ЛОГИЧЕСКОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 2001 |

|

RU2199146C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ СТЕНДОМ ДЛЯ ИСПЫТАНИЙ РАКЕТНО-КОСМИЧЕСКОЙ ТЕХНИКИ | 2010 |

|

RU2434259C1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| МНОГОУРОВНЕВАЯ СИСТЕМА УПРАВЛЕНИЯ И ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ ДВИЖЕНИЯ ПОЕЗДОВ ДЛЯ СОРТИРОВОЧНЫХ СТАНЦИЙ | 2009 |

|

RU2401217C1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство управления стендовыми испытаниями изделий ракетно-космической техники | 2018 |

|

RU2684979C1 |

Изобретение относится к автоматизированным системам управления технологическими процессами при наземных испытаниях изделий ракетно-космической техники (РКТ) и может быть использовано при стендовой отработке авиационной, транспортной техники, а также химических установок. Технический результат заявленного изобретения заключается в обеспечении единого времени и синхронизации циклов работы распределенной сети однородных управляющих контроллеров независимо от их количества, размещения и варианта резервирования. Технический результат достигается за счет устройства синхронизации системы управления стендовыми испытаниями ракетно-космической техники, содержащего в процессоре каждого управляющего контроллера блок сопряжения с локальной вычислительной сетью, подключенный через блок управления к счетчику циклов, таймеру длительности цикла, регистру транспортного запаздывания и счетчику периода коррекции, связанному с регистром периода коррекции времени. 1 ил.

Устройство синхронизации системы управления стендовыми испытаниями ракетно-космической техники, реализованное в процессоре каждого управляющего контроллера и содержащее блок сопряжения с локальной вычислительной сетью, связанный первым и вторым входами-выходами соответственно с локальной вычислительной сетью и с первым входом-выходом блока управления, второй вход-выход которого соединен с входами-выходами счетчика циклов и таймера длительности цикла, отличающееся тем, что в него введены регистр транспортного запаздывания, выход которого подключен ко входу блока управления, счетчик периода коррекции, соединенный своим входом-выходом с третьим входом-выходом блока управления, и регистр периода коррекции, подключенный своим выходом ко входу счетчика периода коррекции.

| АФОНИН В.В | |||

| и др | |||

| Синхронизация каналов троированных ПЛК жесткого РВ | |||

| - В: "Промышленные АСУ и контроллеры", №6, 2004 | |||

| Почвенный бур | 1924 |

|

SU8812A1 |

| УЧЕБНО-ТРЕНИРОВОЧНЫЙ КОМПЛЕКС АВИАЦИОННЫЙ | 2004 |

|

RU2250511C1 |

| СИСТЕМА МОНИТОРИНГА ОПЕРАТИВНОЙ ОБСТАНОВКИ В СОСТАВЕ КОМПЛЕКСА СРЕДСТВ АВТОМАТИЗАЦИИ АВТОМАТИЗИРОВАННОЙ СИСТЕМЫ УПРАВЛЕНИЯ РАДИОЭЛЕКТРОННЫМИ СРЕДСТВАМИ ВОЕННЫХ ОБЪЕКТОВ | 2007 |

|

RU2360272C1 |

| Устройство для счета груженых вагонеток | 1933 |

|

SU35448A1 |

| US 7451005 B2, 11.11.2008. | |||

Авторы

Даты

2014-02-10—Публикация

2012-04-26—Подача