Изобретение относится к области радиотехники и может быть использовано в устройствах передачи непрерывного информационного потока по каналу (сети) пакетной связи.

Известно устройство, описанное в патенте РФ №2261528, H03L 7/00, «Компенсатор блуждания фазы импульсов сетевой синхронизации», в котором джиттер рассматривается как паразитная времяимпульсная модуляция, и его компенсация происходит во времяимпульсном демодуляторе, который управляется в противофазе входному джиттеру.

Известное устройство состоит из последовательно соединенных амплитудного ограничителя, временного дискриминатора, фильтра нижних частот, импульсного автогенератора, управляемого по фазе напряжением. Выход автогенератора соединен со вторым (опорным) входом временного дискриминатора, отличающегося тем, что в него дополнительно введены аналоговый фазоинвертор, времяимпульсный модулятор, линия задержки. При этом низкочастотный вход модулятора подключен к выходу фильтра нижних частот через фазоинвертор, а его высокочастотный вход - к выходу амплитудного ограничителя через линию задержки. Выход модулятора является выходом всего компенсатора.

Однако это устройство работоспособно, если величина джиттера меньше длительности информационного символа. Это условие может выполняться в том случае, когда причиной джиттера являются нестабильность задающего генератора, помехи в канале связи, изменения параметров канала во времени, различная скорость распространения частотных составляющих одного и того же сигнала. Основным недостатком прототипа является невозможность функционирования при джиттере, большем т/2 (т - длительность информационного символа). Это объясняется тем, что выходным сигналом временного дискриминатора является периодическая функция с периодом т, а рабочей точкой в установившемся режиме является середина линейного участка. Поэтому при случайном отклонении фронта сигнала, большем т /2, рабочая точка перескакивает на соседний линейный участок (явление проскальзывания), что нарушает работу синхронного детектора. В результате на выходе фильтра нижних частот будет выделяться сигнал, не соответствующий входному джиттеру, а времяимпульсный модулятор вместо компенсации будет увеличивать джиттер.

Техническим результатом заявленного объекта является компенсация джиттера, величина которого может существенно превосходить длительность информационного символа.

Это достигается тем, что в устройство, состоящее из последовательно соединенных фильтра нижних частот и генератора, управляемого кодом, дополнительно введены счетчик записи, счетчик чтения, два вычитателя, формирователь импульса начальной установки и запоминающее устройство. При этом первый вход счетчика записи является входом тактовых импульсов устройства, второй вход соединен с выходом формирователя импульса начальной установки и вторым входом счетчика чтения, первый вход которого соединен с выходом генератора, являющимся выходом тактовых импульсов устройства. Выходы счетчиков записи и чтения соединены со вторым и третьим входами запоминающего устройства и первым и вторым (инверсным) входами первого вычитателя, а выход первого вычитателя соединен с первым входом второго вычитателя, на второй (инверсный) вход которого подана константа 2n+1 (n - разрядность счетчиков). При этом его выход соединен с входом фильтра нижних частот; первый вход запоминающего устройства является информационным входом устройства, выход - информационным выходом устройства.

Существенным отличием изобретения являются введенные элементы и их связи, так как только они позволяют компенсировать джиттер, существенно превосходящий длительность информационного символа.

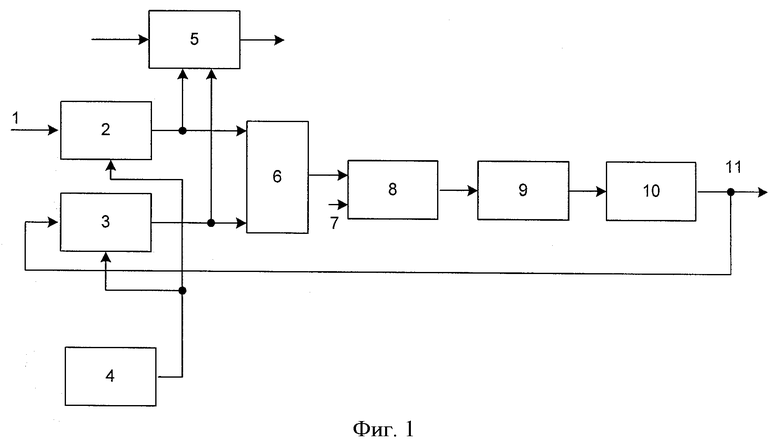

Структурная схема предлагаемого изобретения представлена на фиг.1. На структурной схеме введены следующие обозначения: 1 - тактовые импульсы, 2 - счетчик записи, 3 - счетчик чтения, 4 - формирователь импульса начальной установки, 5 - запоминающее устройство, 6 - первый вычитатель, 7 - константа 2n-1, 8 - второй вычитатель, 9 - фильтр нижних частот, 10 - генератор, управляемый кодом, 11 - импульсы, поступающие с генератора.

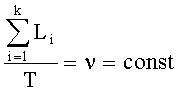

Работа устройства происходит следующим образом. На его вход поступает прерывистая информация. Это могут быть пакеты произвольной длины, приходящие в случайные моменты времени, но при этом должно выполняться условие

где T - интервал времени наблюдения,

k - число пакетов за время T,

Li - величина i-го пакета,

v - скорость непрерывного информационного потока.

Пакеты сопровождаются тактовыми импульсами 1, поступающими на счетчик записи 2, который является адресом для записи входного бита в запоминающее устройство 5. Разрядность счетчика равна n. Таким образом, запоминающее устройство 5 является кольцевой памятью размером 2n. Считывание информации с запоминающего устройства 5 осуществляется в соответствии с адресом, формируемым счетчиком чтения 3, который тактируется импульсами 11, поступающими с генератора, управляемого кодом 10. Они же поступают и на выход устройства.

Первый вычитатель 6 выполняет функцию временного дискриминатора прототипа. Код на его выходе равен области памяти между записываемым и считываемым битом, что можно интерпретировать как временную ошибку между входным и опорным сигналом. При этом «раскрыв» дискриминатора равен τ·2n , где τ - длительность символа непрерывной информации. Таким образом, по сравнению с прототипом линейный участок дискриминатора увеличен в 2n раз, что и позволяет устройству нормально функционировать при джиттере, существенно превосходящем длительность символа непрерывной информации.

Благодаря второму вычитателю 8, на инверсный вход которого подана константа 7, равная 2n-1, система регулирования стремится к состоянию, при котором область памяти между записываемым и считываемым битом была бы равна 2n-1, то есть половине памяти. Код на выходе второго вычитателя 8 в этом случае близок к 0, и его воздействие на генератор 10 через фильтр нижних частот 9 будет минимально. Если область памяти между записываемым и считываемым битом будет больше половины памяти, то код на выходе второго вычитателя 8 и фильтра нижних частот 9 тоже будет больше 0. В результате увеличится частота генератора 10, что приведет к увеличению скорости считывания информации. Если область памяти между записываемым и считываемым битом будет меньше половины памяти, то соответственно скорость считывания уменьшится. Таким образом, если определить среднее значение области памяти между записываемым и считываемым битом за достаточно большое время, то оно будет примерно равно 2n-1. Значение 2n-1 выбрано из соображений максимального удаления областей записи и чтения памяти, чтобы исключить их перекрытие, которое приводит к искажению выходной информации.

Система регулирования сама приходит к состоянию, когда область памяти между записываемым и считываемым битом равна ~2n-1, но на это требуется время, в течение которого могут наблюдаться искажения выходной информации. Для сокращения этого времени (время переходных процессов) в устройство введен формирователь импульса начальной установки счетчиков 4, по которому один счетчик устанавливается в нулевое состояние, а другой - в 2n-1.

Источники информации

1. Патент РФ №2261528, H03L 7/00 Компенсатор блуждания фазы импульсов сетевой синхронизации

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Устройство поиска информации | 2019 |

|

RU2724788C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2022 |

|

RU2792840C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ АСИНХРОННОЙ ИНФОРМАЦИИ | 1992 |

|

RU2030114C1 |

Изобретение относится к области радиотехники и может быть использовано в устройствах передачи непрерывного информационного потока по каналу (сети) пакетной связи. Технический результат - компенсация больших блужданий тактовых импульсов (джиттера). Это достигается увеличением в 2n раз периода дискриминационной характеристики. Устройство содержит фильтр нижних частот и генератор, управляемый кодом, а также счетчик записи, счетчик чтения, два вычитателя, формирователь импульса начальной установки и запоминающее устройство. При этом на второй (инверсный) вход второго вычитателя подана константа 2n-1 (n - разрядность счетчиков), первый вход и выход запоминающего устройства являются соответственно информационным входом и информационным выходом устройства, входом тактовых импульсов которого является первый вход счетчика записи, а выход генератора, управляемого кодом является выходом таковых импульсов устройства. 1 ил.

Устройство тактовой синхронизации для преобразования прерывистой информации в непрерывную, состоящее из последовательно соединенных фильтра нижних частот и генератора, управляемого кодом, отличающееся тем, что в него дополнительно введены счетчик записи, счетчик чтения, два вычитателя, формирователь импульса начальной установки и запоминающее устройство; при этом первый вход счетчика записи является входом тактовых импульсов устройства, а второй вход соединен с выходом формирователя импульса начальной установки и вторым входом счетчика чтения, первый вход которого соединен с выходом генератора, являющимся выходом тактовых импульсов устройства, выходы счетчиков записи и чтения соединены со вторым и третьим входами запоминающего устройства и первым и вторым (инверсным) входами первого вычитателя, при этом выход первого вычитателя соединен с первым входом второго вычитателя, на второй (инверсный) вход которого подана константа 2n-1 (n - разрядность счетчиков), а выход соединен с входом фильтра нижних частот; первый вход запоминающего устройства является информационным входом устройства, а выход - информационным выходом устройства.

| КОМПЕНСАТОР БЛУЖДАНИЯ ФАЗЫ ИМПУЛЬСОВ СЕТЕВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2261528C1 |

| СХЕМА ПОДАВЛЕНИЯ ДЖИТТЕРА | 1995 |

|

RU2110158C1 |

| US 7868949 B2, 11.01.2011 | |||

| US 8125278 B2, 28.02.2012 | |||

| Подставка для термообработки рулонов | 1980 |

|

SU859470A1 |

Авторы

Даты

2014-05-27—Публикация

2012-03-20—Подача