Предлагаемое изобретение относится к вычислительной технике и сетям связи и может быть использовано в локальных вычислительных сетях и внешних запоминающих устройствах.

Известен способ (US №5.408.453, G11B 7/09,1995) и аппаратура для записи, чтения и стирания информации на оптический диск, закодированной канальным кодом. Согласно способу информация записывается на диск на основе преобразования двоичных сигналов в канальный код. При считывании информации с диска канальный код преобразуется в двоичный и затем обрабатывается устройством считывания, в частности, для обнаружения ошибок помехоустойчивыми кодами. Недостатком способа и аппаратуры является то, что при этом не используются способности канального кода к обнаружению искажений.

Известен также способ (Авт. свидетельство №1156246 «Способ демодуляции двухфазных трехуровневых сигналов», МПК H03K 13/00, опубликовано 15.05.85 г., БИ №18) демодуляции сигнала в канальном коде типа Манчестер. Способ заключается в том, что при превышении проинтегрированным информационным сигналом заданных уровней положительной или отрицательной полярности формируют импульсы первой и второй последовательностей, соответствующие единичным и нулевым значениям входного сигнала. Начало импульсов обеих последовательностей формируют в моменты перехода биполярного информационного сигнала от отрицательной полярности к положительной и обратно, а длительность их сигнала устанавливают равной половине периода входного сигнала. Входной сигнал и импульсные сигналы обеих последовательностей нормализуют по амплитуде. Нормализованные сигналы обеих последовательностей складывают с нормализованным входным сигналом со знаками, соответствующими его информационным значениям. Недостатком этого способа является невозможность обнаружения ошибок при демодуляции канального кода.

Из известных наиболее близким по технической сущности является способ декодирования канального кода типа Манчестер, описанный в авторском свидетельстве №1591189, МПК H03M 5/12, 13/00 «Устройство для декодирования сигналов» (БИ №33, опубликовано 07.09.90). Сущность способа заключается в следующем. При кодировании кодом Манчестер каждый двоичный бит преобразуется в 2 биимпульса со сменой полярности сигнала, при декодировании сигналы положительной и отрицательной полярности отдельно регистрируются стробирующими импульсами, вырабатываемыми с помощью генератора тактовых импульсов, счетчиков и дешифраторов. Полученные в результате стробирования сигналы подаются на SR-триггер, на выходе которого получают двоичный демодулированный сигнал. В данном прототипе описан метод обнаружения искажений (ошибок) в канальном коде типа Манчестер, основанный на анализе структуры биполярного сигнала, при регистрации которого на каждом тактовом интервале должно появиться не менее одного стробирующего импульса. Сигнал об ошибке может выдаваться на внешнюю ступень помехоустойчивого декодирования как сигнал «стирание», что существенно повышает достоверность приема информации.

Устройство декодирования сигналов, описанное в авторском свидетельстве №1591189, МПК H03M 5/12, 13/00 «Устройство для декодирования сигналов» (БИ №33, опубликовано 07.09.90), содержит блок синхронизации, блок преобразования канального кода и блок обнаружения ошибок.

Способ декодирования сигналов и реализующее его устройство по авторскому свидетельству №1591189, МПК H03M 5/12, 13/00 и выбраны в качестве прототипа.

Недостатком данного способа и реализующего его устройства является ограниченная его область применения, поскольку, они не могут быть применены для демодуляции и обнаружения искажений других канальных кодов, например, CMI (Complemented mark inversion) и низкая точность преобразования канального кода в двоичный код.

Техническим результатом предлагаемого способа является повышение точности демодуляции канального кода типа CMI в двоичный код и повышение достоверности приема информации, заключающееся в том, что при демодуляции канальных кодов типа CMI с помощью стробирования и анализа структуры кода более точно обнаруживаются искаженные по коду CMI комбинации, сигнал «Ошибка» о которых может подаваться на вторую ступень помехоустойчивого декодирования, что обеспечивает повышение достоверности приема информации.

1. Сущность предлагаемого способа заключается в том, что для демодуляции канального кода типа CMI в двоичные сигналы принимаемая из канала связи информация в коде CMI поступает в блок синхронизации, в котором вырабатываются синхронные тактовые импульсы ТИ1 с тактовыми интервалами T/2, регистрирующие методом стробирования положительные и отрицательные импульсы кода CMI, и результаты регистрации в виде информационного сигнала «Инф. сигнал» выдаются в блок обнаружения ошибок, кроме того импульсы ТИ1 выдаются в блоки обнаружения ошибок и выработки тактовых импульсов, блок выработки тактовых импульсов генерирует тактовые импульсы ТИ2 и ТИ3, следующие соответственно с тактовыми интервалами T и 2T, при этом тактовые импульсы ТИ3 поступают в блок обнаружения ошибок, в котором с помощью регистра сдвига на триггерах и двух дешифраторов на основе логических схем И и логической схемы ИЛИ осуществляется обнаружение запрещенных по коду CMI четырехразрядных комбинаций, при обнаружении на выход устройства подается сигнал «Ошибка», одновременно из блока обнаружения ошибок в блок преобразования канального кода подается один из 4 сигналов, фиксирующих обнаружение комбинаций «00», «01», «10» или «11» канального кода, а из блока выработки тактовых импульсов на блок преобразования канального кода поступают также тактовые импульсы ТИ2, в котором происходит преобразование канального кода в двоичный.

При этом информационный сигнал «Инф. сигнал» с блока синхронизации и тактовые импульсы ТИ1 и ТИ3 из блока выработки тактовых импульсов поступают в блок обнаружения ошибок, в котором информационный сигнал в виде 4-разрядной комбинации записывается в регистр сдвига на D-триггерах с помощью тактовых импульсов ТИ1, записанные двухразрядные комбинации выделяются с помощью логических схем И первого дешифратора, затем четырехразрядные комбинации выделяются с помощью логических схем И второго дешифратора, на 9 выходах которого выделяются ошибочные по коду CMI комбинации (1111, 0000, 0010, 1110, 1010, 1011, 1000, 1001, 0110), сигнал о приеме которых проходит через логическую схему ИЛИ и выдается на выход блока обнаружения ошибок как «Ошибка».

Кроме того, для преобразования кода CMI в двоичный два сигнала об обнаружении комбинаций «11» или «00» с блока обнаружения ошибок поступают на первую логическую схему ИЛИ блока преобразования канального кода, а об обнаружении комбинаций «10» или «01» два сигнала поступают на вторую логическую схему ИЛИ, сигналы с выходов схем ИЛИ поступают через соответствующие логические схемы И, открываемые тактовыми импульсами ТИ2, на S и R входы SR-триггера, на выходе которого получают двоичный код.

Предлагаемый способ для демодуляции канального кода CMI реализуется с помощью устройства (фиг.1). Процессы демодуляции кода CMI поясняются с помощью следующих рисунков.

Фиг.1 - Устройство для демодуляции канального кода CMI.

Фиг.2 - Функциональная схема блока синхронизации.

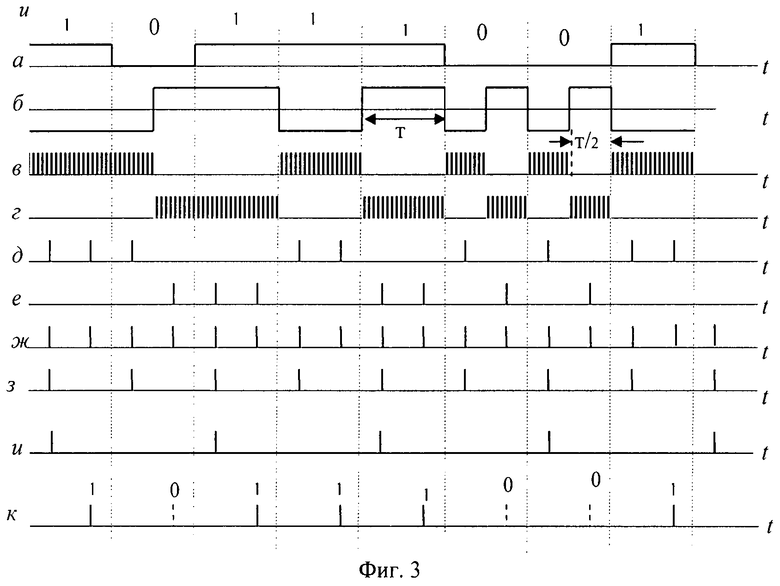

Фиг.3 - Временные диаграммы процессов демодуляции.

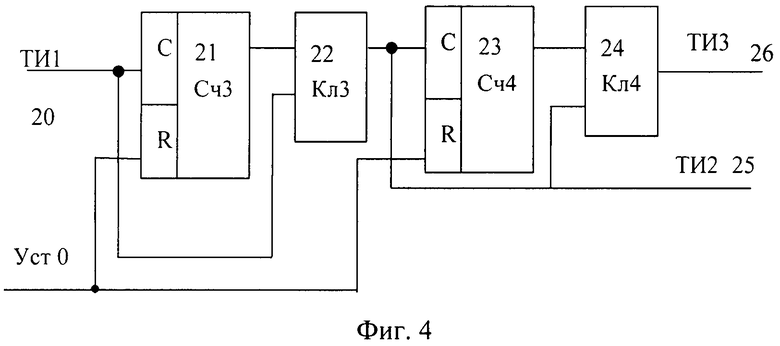

Фиг.4 - Функциональная схема блока выработки тактовых импульсов.

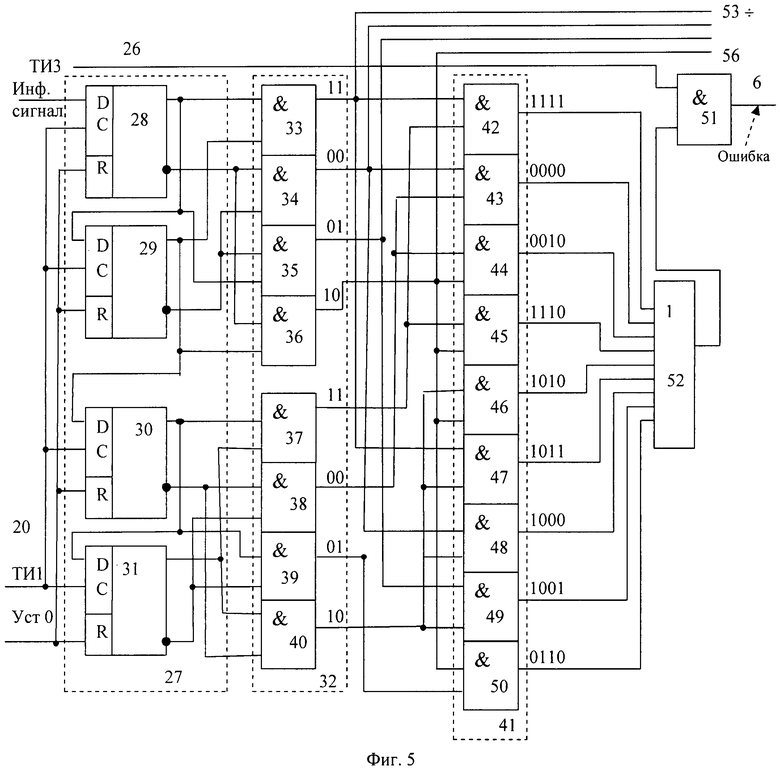

Фиг.5 - Функциональная схема блока обнаружения ошибок.

Фиг.6 - Варианты однократных и двукратных обнаруженных и необнаруженных кодом CMI ошибок.

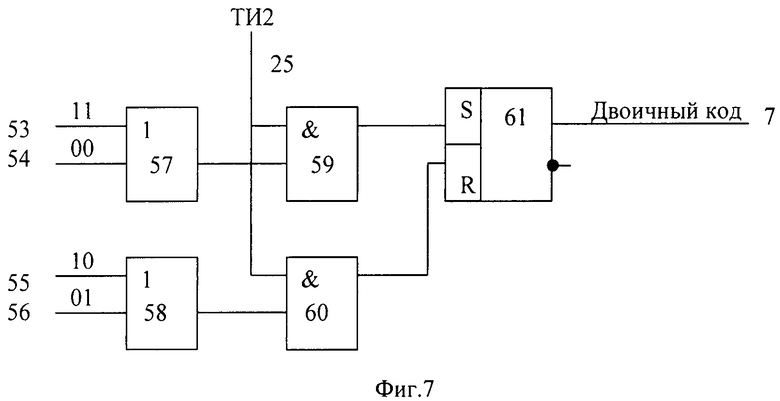

Фиг.7 - Функциональная схема блока преобразования канального кода.

В устройстве для демодуляции канального кода (фиг.1) типа CMI, содержащем блок синхронизации 2, блок обнаружения ошибок 4 (БОО), блок преобразования канального кода 5 (БПКК), при этом вход блока синхронизации 2 соединен с выходом канала связи 1, первый вход блока обнаружения ошибок 4 соединен с первым выходом блока синхронизации 2, первый выход блока обнаружения ошибок 4 является выходом 6 «ошибка» устройства, согласно предлагаемому изобретению дополнительно включен блок выработки тактовых импульсов 3 (БТИ), на вход которого и второй вход БОО 4 подаются с выхода блока синхронизации 2 тактовые импульсы ТИ1, первые 4 входа БПКК 5 подсоединены к соответствующим выходам БОО 4, первый выход БТИ 3 выдает тактовые импульсы ТИ2 на 5 вход БПКК, второй выход БТИ 3 выдает тактовые импульсы ТИ3 на третий вход БОО 4, выход БПКК 5 обеспечивает выдачу двоичного кода.

При этом блок синхронизации 2 (фиг.2) содержит генератор тактовых импульсов 8 (ГТИ), инвертор 9, первый 10 и второй 11 ключи на основе логических схем И, первый 12 и второй 15 делители частоты, построенные на основе счетчиков 13 и 16 и дешифраторов 14 и 17, и логический элемент 18 ИЛИ, выход ГТИ 8 соединен с первыми входами ключей 10 и 11, второй вход первого ключа 10 объединен с входом инвертора 9 и с каналом связи 1, выход инвертора 9 соединен со вторым входом второго ключа 11, выходы первого 10 и второго 11 ключей подсоединены соответственно к счетным входам C счетчиков первого 12 и второго 15 делителей частоты, выходы первого 13 и второго 16 счетчиков подключены соответственно к входам первого 14 и второго 17 дешифраторов, первый выход «Инф. сигнал» блока синхронизации 2 соединен с первым входом блока обнаружения ошибок 3, первым входом логической схемы 18 ИЛИ и R-входом сброса в 0 второго счетчика 16, выход второго делителя частоты 15 соединен со вторым входом логической схемы 18 ИЛИ и R-входом сброса в 0 первого счетчика 13, выход логической схемы 18 ИЛИ является вторым выходом 20 тактовых импульсов ТИ1.

Кроме того блок выработки тактовых импульсов 3 (БТИ) (фиг.4), генерирующий тактовые импульсы ТИ2 с тактовым интервалом T и тактовые импульсы ТИ3 с тактовым интервалом 2T, содержит два счетчика 21 и 23 и два ключа 22 и 24, при этом счетный вход первого счетчика 21 и первый вход первого ключа 22 соединены с первым выходом 20 блока синхронизации 2, вход R счетчиков 21 и 23 соединен с цепью установки в 0 «Уст 0», выход первого счетчика 21 соединен со вторым входом первого ключа 22, выход которого соединен со счетным входом второго счетчика 23 и первым входом второго ключа 24 и является выходом 25 тактовых импульсов ТИ2, выход второго счетчика соединен со вторым входом второго ключа 24, выход которого является выходом 26 тактовых импульсов ТИ3.

При этом, блок обнаружения ошибок 4 (БОО) (фиг.5), содержит регистр сдвига на 4 D-триггерах 28÷31, счетные входы которых соединены с первым выходом 20 ТИ1 блока синхронизации 2, D - вход первого триггера 28 соединен со вторым выходом 20 блока синхронизации 2, который является выходом сигнала «Инф. сигнал», первый дешифратор 32 на 8 логических схемах И33÷И40, второй дешифратор 41 на логических схемах И42÷И50, восемнадцатую логическую схему 51 И, первый вход которой соединен с цепью тактовых импульсов 26 ТИ3, а выход является цепью 6 «ошибка», и логическую схему 52 ИЛИ, выход которой соединен со вторым входом восемнадцатой схемы 51 И, при этом прямой выход первого D-триггера 28 соединен с входами D второго D-триггера 29, первого входа первой логической схемы 33 И и первого входа третьей логической схемы 35 И, инверсный выход первого D-триггера 28 соединен с первым входом второй схемы 34 И и первым входом четвертой схемы 36 И, прямой выход второго D-триггера 29 соединен со входом третьего D-триггера 30 и вторыми входами первой 33 и четвертой 36 логических схем И, инверсный выход второго D-триггера 29 соединен со вторыми входами второй 34 и третьей 35 логических схем И, прямой выход третьего D-триггера 30 соединен с D входом четвертого D-триггера 31 и первыми входам пятой 37 и седьмой 39 логических схем И, инверсный выход третьего D-триггера 30 соединен с первыми входами шестой 38 и восьмой 40 логических схем И, прямой выход четвертого D-триггера 31 соединен со вторыми входами пятой 37 и восьмой 40 логических схем И, инверсный выход четвертого D-триггера 31 соединен со вторыми входами шестой 38 и седьмой 39 логических схем И, выход первой логической схемы 33 И соединен с первыми входами девятой 42 и четырнадцатой 47 логических схем И и является первым выходом 53 блока обнаружения ошибок (БОО), выход второй логической схемы 34 И соединен с первыми входами десятой 43 и пятнадцатой 48 логических схем И и является вторым 54 выходом БОО, выход третьей логической схемы 35 И соединен с первым входом шестнадцатой логической схемы 49 И и является третьим 55 выходом БОО, выход четвертой логической схемы 36 И соединен с первыми входами одиннадцатой 44, двенадцатой 45, тринадцатой 46 и семнадцатой 50 логических схем И и является четвертым 56 выходом БОО, выход пятой логической схемы 37 И соединен со вторыми входами девятой 42 и двенадцатой 45 логических схем И, выход шестой логической схемы 38 И соединен со вторыми входами десятой 43 и одиннадцатой 44 логических схем И, выход седьмой логической схемы 39 И соединен со вторым входом семнадцатой 50 логической схемы И, выход восьмой логической схемы 40 И соединен со вторыми входами тринадцатой 46, четырнадцатой 47, пятнадцатой 48 и шестнадцатой 49 логических схем И, выходы логических схем И с девятой 42 по семнадцатую 50 соединены с соответствующими входами логической схемы 52 ИЛИ, входы R D-триггеров являются входами сигнала установки в 0 «Уст 0».

При этом блок преобразования канального кода (БПКК) 5 (фиг.7) содержит две логические схемы ИЛИ 57 и 58, две логические схемы И 59 и 60 и SR-триггер 61, при этом первый и второй входы первой логической схемы ИЛИ 57 соединены соответственно с первым и вторым выходами БОО 4, а первый и второй входы второй логической схемы ИЛИ 58 соединены соответственно с третьим и четвертым выходами БОО 4, выход первой логической схемы ИЛИ 57 соединен с первым входом первой логической схемы И 59, выход второй логической схемы ИЛИ 58 соединен с первым входом второй логической схемы И 60, вторые входы логических схем И соединены с вторым выходом блока 3 выработки тактовых импульсов ТИ2, выходы первой 59 и второй 60 логических схем И соединены соответственно с входами S и R SR-триггера 61, на выходе 7 которого получают «Двоичный код» устройства для демодуляции канального кода CMI.

Такое сочетание новых признаков с известными позволяет решить поставленную техническую задачу, повысить точность демодуляции канального кода типа CMI в двоичный и повысить достоверность приема информации.

Устройство для демодуляции канального кода CMI работает следующим образом.

Преобразование двоичного кода в канальный код CMI осуществляется следующим образом. При кодировании кодом CMI каждый двоичный бит 0 (см. фиг.3, а), жестко кодируется 2 импульсами (биимпульсами) (-и, +и) (см. фиг 3, б), а двоичный бит 1-2 импульсами одной полярности (-и, -и) или (+и, +и). При этом данная пара биимпульсов меняет свою полярность на противоположную относительно предыдущей двоичной 1, например, (-и, -и) на (-и, -и) (см. фиг.3, б).

Демодуляция происходит следующим образом. Сигнал в коде CMI (см. фиг.3, б) из канала связи (узла считывания с накопителя) поступает в блок синхронизации (см. фиг.2), где управляет ключами Кл1 (10) и Кл2 (11), через которые проходят пачки импульсов длиной T (см. фиг.3, в), вырабатываемые генератором тактовых импульсов ГТИ (8). Частота импульсов от ГТИ равна z*fб, где fб - частота поступающих из канала биимпульсных сигналов fб=1/T, z - коэффициент пересчета счетчиков.

Счетчики Сч1 (13) и Сч2 (16) совместно с дешифраторами Дш1 (14) и Дш2 (17) вырабатывают короткие импульсы (стробы) в середине положительных и отрицательных импульсов (см. фиг.3, д, е). Стробы с выходов дешифраторов объединяются на схеме ИЛИ (18) (см. фиг.3, ж), в результате на выход устройства подаются тактовые импульсы ТИ1, которые следуют с частотой fти1=2/T (фиг.3, ж).

Также на выход устройства с дешифратора Дш1 (14) выдаются короткие импульсы (фиг.3, к), несущие информацию о принятых сигналах 19 «Инф. сигнал».

В блоке тактовых импульсов (см. фиг.4) вырабатываются частоты ТИ2 и ТИ3. Для этого частота ТИ1 с помощью делителя на 2 на счетчике Сч3 (21) и ключе Кл3 (22) уменьшается в 2 раза, в результате чего короткие тактовые импульсы ТИ2 (25) выдаются на выход устройства (фиг.3, з). Частота этих импульсов fти2=1/T. Аналогично получают тактовые импульсы ТИ3 (26) с помощью счетчика Сч4 (23) и ключа Кл4 (24) (фиг.3, и). Частота их равна fти3=1/2T.

На фиг.5 приведена функциональная схема блока обнаружения ошибок (БОО), на фиг.6, к, л, н, о - варианты обнаруженных и не обнаруженных кодом CMI ошибок.

Блок работает следующим образом. На его вход подается «Инф. сигнал» по цепи 19 и тактовые импульсы ТИ1 по цепи 20 с выхода блока синхронизации (см. фиг.3, к), а также тактовые импульсы ТИ3 по цепи 26 с выхода блока выработки тактовых импульсов (см. фиг.4). В результате в регистр сдвига 27 на D-триггерах 28-31 записываются 4 биимпульсных сигнала. Каждая пара биимпульсов соответствует 1 биту данных (см. фиг.6, а, б). Схемы И33-И40 дешифратора 32 выделяют возможные комбинации кода CMI (11, 00, 01, 10), которые необходимы для блока преобразования канального кода 5 (см. фиг.7) и которые подаются на него по цепям 53-56.

Дешифратор 41, построенный на основе логических схем И (И42÷И50), выделяет запрещенные кодом CMI комбинации (1111, 0000, 0010, 1110, 1010, 1011, 1000, 1001, 0110). В результате чего с помощью схем ИЛИ52 и И51, открываемой тактовыми импульсами ТИ3, на выход БОО выдается сигнал «Ошибка» по цепи 6.

На фиг.7 приведена функциональная схема блока преобразования канального кода 5 (БПКК). Блок работает следующим образом. Если в устройстве обнаружения ошибок (фиг.5) на выходе схем И33 или И34 появляется сигнал, фиксирующий прием комбинации кода CMI (11) или (00), то сигнал по цепи 53 или 54 поступает через схему ИЛИ 57 БПКК (фиг.7) на схему И59. Сигнал проходит через схему И59 в момент его стробирования тактовым импульсом ТИ2 и устанавливает SR-триггер 61 в 1. Когда же по цепи 55 или 56 поступает сигнал приема комбинации кода CMI (01) или (10), то открывается схема И 60 и в результате SR-триггер 61 сбрасывается в 0. Таким образом, происходит преобразование кода CMI в исходный двоичный код (цепь 7).

При кодировании кодом CMI, как и при кодировании кодом Манчестер, каждый двоичный бит преобразуется в 2 биимпульса со сменой полярности сигнала. Это необходимо для самосинхронизации приемного устройства. Кроме того, для повышения помехоустойчивости передачи применяют биполярный сигнал типа (+и, -и).

Таким образом, при кодировании канальными кодами CMI и Манчестер k двоичных бит отображаются в n=2k биполярных сигналов, что соответствует введению избыточности в первичный код.

Обнаружение ошибок кодом CMI осуществляется следующим образом.

Код CMI обнаруживает часть однократных и двукратных ошибок. На фиг.6, к и фиг.6, м показаны варианты однократных обнаруженных ошибок, а на фиг.6, к и фиг.6, л - варианты однократных необнаруженных ошибок. Варианты двукратных обнаруженных ошибок показаны на фиг.6, о, а на фиг.6, н - необнаруженных 2-кратных ошибок.

При кодировании кодом CMI последовательности двоичных 1 используется относительный принцип, т.е. если текущая 1 преобразуется в (-и, -и), то следующая 1 преобразуется в (+и, +и). Поэтому, например, трансформация кода CMI (-и, -и) вследствие воздействия помех на полезный сигнал в (+и, +и) или (+и, +и) в (-и, -и) обнаруживаются в блоке обнаружения ошибок (см. фиг.5) за счет обнаружения недопустимой последовательности (+и, +и, +и, +и) схемой И42 или последовательности (-и, -и, -и, -и) схемой И43. С целью упрощения на фиг.6 +и обозначается через 1, а - и - через 0. Поэтому запрещенные кодом CMI комбинации выделяются схемами И42÷И50 и имеют значение: 1111, 0000, 0010, 1110, 1010, 1011, 1000, 1001, 0110.

Оценка способности кода CMI к обнаружению ошибок осуществляется следующим образом.

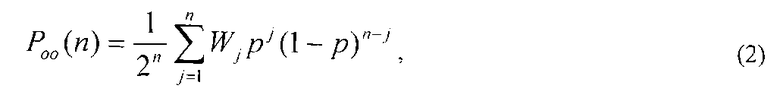

На фиг.6 приведены варианты обнаруживаемых запрещенных 4-битовых комбинаций кода CMI. Канальное кодирование, как правило, ведет к удвоению разрядов двоичного кода. Такой код можно обозначить (n, k,), где n - длина канального кода, k - длина двоичного кода, n=2k. В терминах теории помехоустойчивого кодирования канальный код обладает двойной избыточностью. Вероятность ошибки этого кода

Вероятность обнаружения ошибок кодом

где Wj - число вариантов j-кратной обнаруживаемой кодом CMI ошибки, p - вероятность ошибки на бит.

Поскольку в канале связи наиболее вероятны однократные ошибки, то для нашего случая при n=4 получим:

при p=1·10-3 Pоо(n)=0.00495, Pош(4)=0.0099;

при p=1·10-4 Роо(n)=2·10-4, Pош(4)=4·10-4.

Вероятность необнаруженных кодом CMI можно оценить по формуле:

т.е. при p=1·10-3 Pно(n)=0.00505;

при p=1·10-4 Pно(n)=2·10-4.

Таким образом, примерно половина вариантов ошибок обнаруживаются канальным кодом CMI, что можно эффективно использовать на следующей ступени помехоустойчивого декодирования путем подачи сигнала «Ошибка» при обнаружении ошибок на эту вторую ступень помехоустойчивого декодирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| Цифровой имитатор случайных сигналов | 2019 |

|

RU2722001C1 |

| Устройство для сортировки информации | 1984 |

|

SU1196849A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Обнаружитель комбинаций двоичных сигналов | 1979 |

|

SU987859A1 |

| ТРЕХЧАСТОТНЫЙ МОДУЛЯТОР | 2003 |

|

RU2239939C1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

Группа изобретений относится к вычислительной технике и связи и может быть использована в локальных вычислительных сетях и внешних запоминающих устройствах. Техническим результатом является повышение достоверности приема. Устройство содержит блок синхронизации, блок выработки тактовых импульсов, блок обнаружения ошибок, блок преобразования канального кода. 2 н. и 6 з.п. ф-лы, 7 ил.

1. Способ для демодуляции канального кода, заключающийся в том, что принимаемая из канала связи информация в коде CMI поступает в блок синхронизации, в котором вырабатываются синхронные тактовые импульсы ТИ1 с тактовыми интервалами Т/2, регистрирующие методом стробирования положительные и отрицательные импульсы кода CMI, и результаты регистрации в виде информационного сигнала «Инф. сигнал» выдаются в блок обнаружения ошибок, кроме того импульсы ТИ1 выдаются в блоки обнаружения ошибок и выработки тактовых импульсов, отличающийся тем, что блок выработки тактовых импульсов генерирует тактовые импульсы ТИ2 и ТИ3, следующие соответственно с тактовыми интервалами Т и 2Т, при этом тактовые импульсы ТИ3 поступают в блок обнаружения ошибок, в котором с помощью регистра сдвига на триггерах и двух дешифраторов на основе логических схем И и логической схемы ИЛИ осуществляется обнаружение запрещенных по коду CMI четырехразрядных комбинаций, при обнаружении на выход устройства подается сигнал «Ошибка», одновременно из блока обнаружения ошибок в блок преобразования канального кода подается один из 4 сигналов, фиксирующих обнаружение комбинаций «00», «01», «10» или «11» канального кода, а из блока выработки тактовых импульсов на блок преобразования канального кода поступают также тактовые импульсы ТИ2, в котором происходит преобразование канального кода в двоичный.

2. Способ по п.1, отличающийся тем, что информационный сигнал «Инф. сигнал» с блока синхронизации и тактовые импульсы ТИ1 и ТИ3 из блока выработки тактовых импульсов поступают в блок обнаружения ошибок, в котором информационный сигнал в виде 4-разрядной комбинации записывается в регистр сдвига на D-триггерах с помощью тактовых импульсов ТИ1, записанные двухразрядные комбинации выделяются с помощью логических схем И первого дешифратора, затем четырехразрядные комбинации выделяются с помощью логических схем И второго дешифратора, на 9 выходах которого выделяются ошибочные по коду СМI комбинаций (1111, 0000, 0010, 1110, 1010, 1011, 1000, 1001, 0110), сигнал о приеме которых проходит через логическую схему ИЛИ и выдается на выход блока обнаружения ошибок как «Ошибка».

3. Способ по п.1, отличающийся тем, что для преобразования кода CMI в двоичный два сигнала об обнаружении комбинаций «11» или «00» с блока обнаружения ошибок поступают на первую логическую схему ИЛИ блока преобразования канального кода, а об обнаружении комбинаций «10» или «01» два сигнала поступают на вторую логическую схему ИЛИ, сигналы с выходов схем ИЛИ поступают через соответствующие логические схемы И, открываемые тактовыми импульсами ТИ2, на S и R входы SR-триггера, на выходе которого получают двоичный код.

4. Устройство для демодуляции канального кода типа CMI, содержащее блок синхронизации, блок обнаружения ошибок (БОО), блок преобразования канального кода (БПКК), при этом вход блока синхронизации соединен с выходом канала связи, первый вход блока обнаружения ошибок соединен с первым выходом блока синхронизации, первый выход блока обнаружения ошибок является выходом «ошибка» устройства, отличающееся тем, что в него дополнительно включен блок выработки тактовых импульсов (БТИ), на вход которого и на второй вход БОО подаются с выхода блока синхронизации тактовые импульсы ТИ1, первые 4 входа БПКК подсоединены к соответствующим выходам БОО, первый выход БТИ выдает тактовые импульсы ТИ2 на пятый вход БПКК, второй выход БТИ выдает тактовые импульсы ТИ3 на третий вход БОО, выход БПКК обеспечивает выдачу двоичного кода.

5. Устройство по п.4, отличающееся тем, что блок синхронизации содержит генератор тактовых импульсов (ГТИ), инвертор, первый и второй ключи на основе логических схем И, первый и второй делители частоты, построенные на основе двух счетчиков и двух дешифраторов, и логический элемент ИЛИ, выход ГТИ соединен с первыми входами первого и второго ключей, второй вход первого ключа объединен с входом инвертора и с каналом связи, выход инвертора соединен со вторым входом второго ключа, выходы первого и второго ключей подсоединены соответственно к счетным входам C счетчиков первого и второго делителей частоты, выходы первого и второго счетчиков подключены соответственно к входам первого и второго дешифраторов, первый выход «Инф. сигнал» блока синхронизации соединен с первым входом блока обнаружения ошибок, первым входом логической схемы ИЛИ и R-входом сброса в 0 второго счетчика, выход второго делителя частоты соединен со вторым входом логической схемы ИЛИ и R -входом сброса в 0 первого счетчика, выход логической схемы ИЛИ является вторым выходом тактовых импульсов ТИ1.

6. Устройство по п.4, отличающееся тем, что блок выработки тактовых импульсов (БТИ), генерирующий тактовые импульсы ТИ2 с тактовым интервалом Т и тактовые импульсы ТИ3 с тактовым интервалом 2Т, содержит два счетчика и два ключа, при этом счетный вход первого счетчика и первый вход первого ключа соединены с первым выходом блока синхронизации, вход R обоих счетчиков соединен с цепью установки в 0 «Уст 0», выход первого счетчика соединен со вторым входом первого ключа, выход которого соединен со счетным входом второго счетчика и первым входом второго ключа и является выходом тактовых импульсов ТИ2, выход второго счетчика соединен со вторым входом второго ключа, выход которого является выходом тактовых импульсов ТИ3.

7. Устройство по п.4, отличающееся тем, что блок обнаружения ошибок (БОО), содержит регистр сдвига на 4 D-триггерах, счетные входы которых соединены с вторым выходом ТИ1 блока синхронизации, D вход первого триггера соединен с первым выходом блока синхронизации, который является выходом сигнала «Инф. сигнал», первый дешифратор на 8 логических схемах И с 1-й по 8, второй дешифратор на логических схемах И с 9-й по 17, восемнадцатую логическую схему И, первый вход которой соединен с цепью тактовых импульсов ТИ3, а выход является цепью «Ошибка», и логическую схему ИЛИ, выход которой соединен со вторым входом восемнадцатой схемы И, при этом прямой выход первого D-триггера соединен с входами D второго D-триггера, первого входа первой логической схемы И и первого входа третьей логической схемы И, инверсный выход первого D-триггера соединен с первым входом второй схемы И и первым входом четвертой схемы И, прямой выход второго D-триггера соединен с входом третьего D-триггера и вторыми входами первой и четвертой логических схем И, инверсный выход второго D-триггера соединен со вторыми входами второй и третьей логических схем И, прямой выход третьего D-триггера соединен с D входом четвертого D-триггера и первыми входами пятой и седьмой логических схем И, инверсный выход третьего D-триггера соединен с первыми входами шестой и восьмой логических схем И, прямой выход четвертого D-триггера соединен со вторыми входами пятой и восьмой логических схем И, инверсный выход четвертого D-триггера соединен со вторыми входами шестой и седьмой логических схем И, выход первой логической схемы И соединен с первыми входами девятой и четырнадцатой логических схем И и является первым выходом БОО, выход второй логической схемы И соединен с первыми входами десятой и пятнадцатой логических схем И и является вторым выходом БОО, выход третьей логической схемы И соединен с первым входом шестнадцатой логической схемы И и является третьим выходом БОО, выход четвертой логической схемы И соединен с первыми входами одиннадцатой, двенадцатой, тринадцатой и семнадцатой логических схем И и является четвертым выходом БОО, выход пятой логической схемы И соединен со вторыми входами девятой и двенадцатой логических схем И, выход шестой логической схемы И соединен со вторыми входами десятой и одиннадцатой логических схем И, выход седьмой логической схемы И соединен со вторым входом семнадцатой логической схемы И, выход восьмой логической схемы И соединен со вторыми входами тринадцатой, четырнадцатой, пятнадцатой и шестнадцатой логических схем И, выходы логических схем И с девятой по семнадцатую соединены с соответствующими входами логической схемы ИЛИ, входы R D-триггеров являются входами сигнала установки в 0 «Уст 0».

8. Устройство по п.4, отличающееся тем, что блок преобразования канального кода (БПКК) содержит две логические схемы ИЛИ, две логические схемы И и SR-триггер, при этом первый и второй входы первой логической схемы ИЛИ соединены соответственно с первым и вторым выходами БОО, а первый и второй входы второй логической схемы ИЛИ соединены соответственно с третьим и четвертым выходами БОО, выход первой логической схемы ИЛИ соединен с первым входом первой логической схемы И, выход второй логической схемы ИЛИ соединен с первым входом второй логической схемы И, вторые входы логических схем И соединены с вторым выходом блока выработки тактовых импульсов ТИ2, выходы первой и второй логических схем И соединены соответственно с входами S и R SR-триггера, выход которого является выходом «Двоичный код» устройства для демодуляции канального кода.

| SU 1591189 A1, 07.09.1990 | |||

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| КОМБИНИРОВАННЫЙ УНИВЕРСАЛЬНЫЙ СПОСОБ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ ИНФОРМАЦИИ БИИМПУЛЬСНЫМ КОДОМ МАНЧЕСТЕР II | 2000 |

|

RU2163400C1 |

| "Устройство для декодирования кода "Манчестер-2" | 1990 |

|

SU1809536A1 |

| US 4808970 A, 28.02.1989 | |||

| JP 6149542 A, 11.03.1986 | |||

| JP 6086952 A, 16.05.1985 | |||

Авторы

Даты

2014-06-27—Публикация

2012-11-01—Подача