Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах автоматического распознавания образов, в частности для распознавания состояний сложных объектов по ряду значений их параметров.

Известно устройство для распознавания образов (патент РФ на изобретение №2306605, опубл. 20.09.2007, БИ №26), используемое для идентификации состояний объектов по значениям их параметров, которое по своей технической сущности является наиболее близким к предлагаемому устройству. Это устройство содержит многоканальный коммутатор, информационные входы которого подключены к информационным входам устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, счетчик адресов, блок памяти, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов блока памяти подключены к выходам счетчика адресов и к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, а выходы последних разрядов сдвиговых регистров подключены к выходам блока сдвиговых регистров, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к управляющим входам счетчика адресов, блока памяти, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а вход блока управления является управляющим входом устройства, выходы блока памяти подключены непосредственно к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, выходы которого являются выходами устройства.

Недостатком устройства-прототипа является низкая производительность, обусловленная постоянным циклом распознавания, длительность которого пропорциональна числу используемых признаков n.

Техническим результатом настоящего изобретения является повышение производительности устройства.

Для достижения результата в устройство для распознавания образов, содержащее многоканальный коммутатор, информационные входы которого подключены к информационным входам признаков устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, счетчик адресов старших разрядов, блок памяти коэффициентов ассоциативности признаков, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов блока памяти коэффициентов ассоциативности признаков подключены к выходам счетчика адресов старших разрядов и к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, блок управления, первый, второй, третий и четвертый выходы которого подключены соответственно к счетному входу счетчика адресов старших разрядов, к управляющему входу обращения блока памяти коэффициентов ассоциативности признаков, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а первый вход блока управления подключен к управляющему входу устройства, выходы блока памяти коэффициентов ассоциативности признаков подключены непосредственно к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, дополнительно включены логический элемент ИЛИ, регистр адресов, блок памяти выбора адресов и буферный регистр, причем выходы регистра адресов подключены к адресным входам старших разрядов блока памяти выбора адресов, адресные входы младших разрядов которого подключены к выходам блока сдвиговых регистров, все выходы блока памяти выбора адресов подключены ко входам буферного регистра, а выходы младших разрядов блока памяти выбора адресов, соответствующие адресу следующего признака, подключены также к адресным входам многоканального коммутатора и к адресным входам старших разрядов блока памяти коэффициентов ассоциативности признаков, управляющий вход буферного регистра подключен к управляющему входу аналого-цифрового преобразователя и к четвертому выходу блоку управления, а выходы буферного регистра подключены ко входам регистра адресов, сбросовый вход которого подключен к сбросовому входу блока сдвиговых регистров и к пятому выходу блока управления, а управляющий вход регистра адресов подключен ко второму входу блока логических элементов И и к третьему выходу блока управления, первый выход которого подключен к управляющему входу блока памяти выбора адресов, все выходы сдвиговых регистров подключены к выходам блока сдвиговых регистров, а сбросовые входы всех сдвиговых регистров объединены и подключены к сбросовому входу блока сдвиговых регистров, выходы последних разрядов которого являются выходами устройства и подключены ко входам логического элемента ИЛИ, выход которого подключен ко второму управляющему входу блока управления.

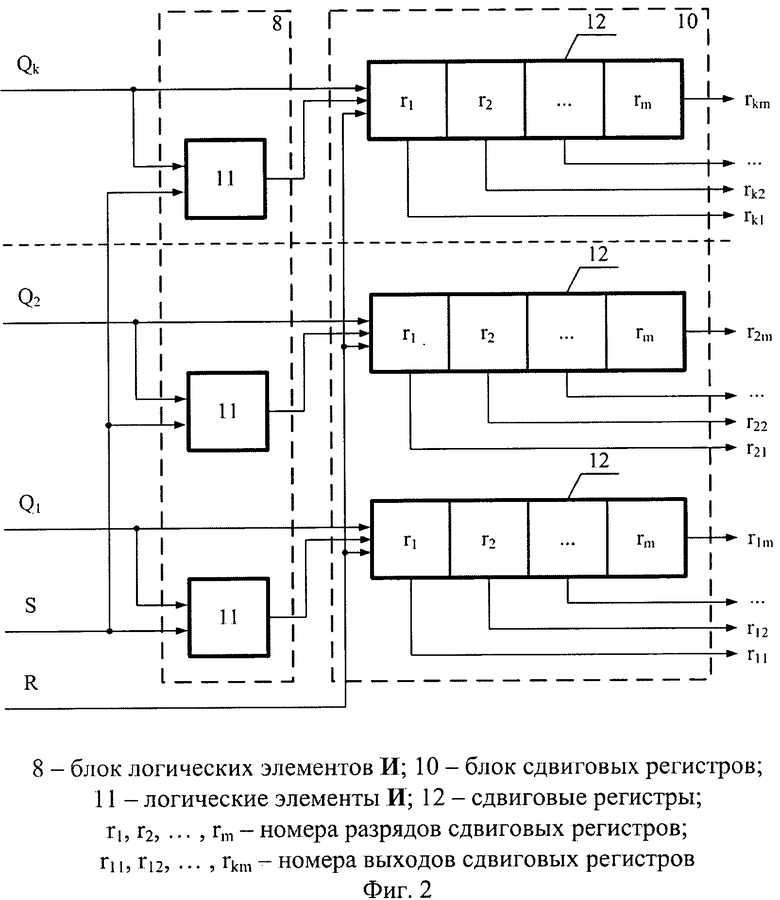

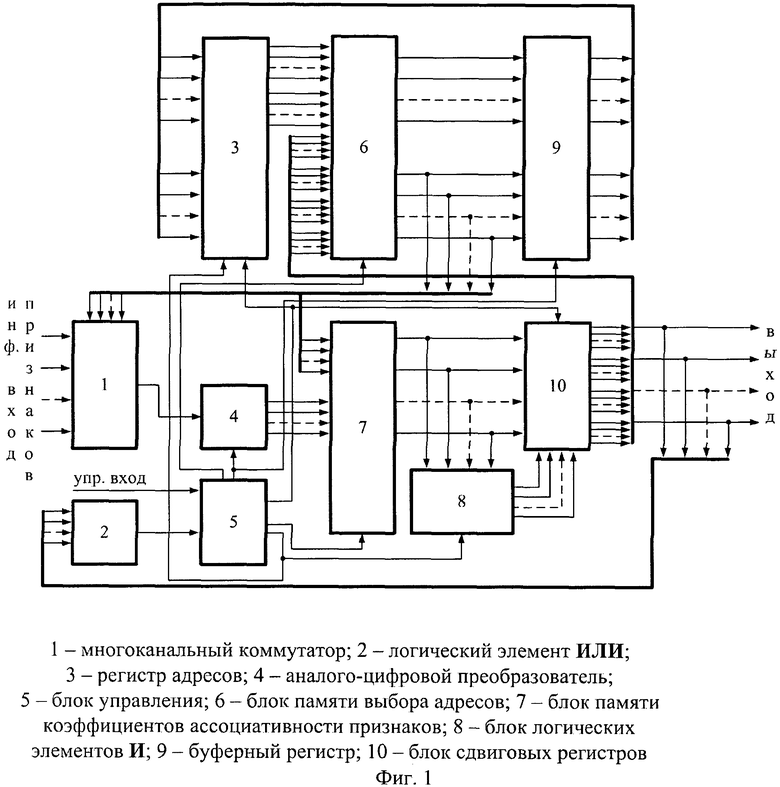

На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - структурные схемы блока логических элементов И и блока сдвиговых регистров, на фиг.3 для пояснения принципа работы предлагаемого устройства и, как пример реализации блока управления, представлена структурная схема блока управления, на фиг.4 - временная диаграмма формирования сигналов на его выходе.

Устройство содержит многоканальный коммутатор 1, логический элемент ИЛИ 2, регистр адресов 3, аналого-цифровой преобразователь 4, блок управления 5, блок памяти выбора адресов 6, блок памяти коэффициентов ассоциативности признаков 7, блок логических элементов И 8, буферный регистр 9, блок сдвиговых регистров 10, причем информационные входы многоканального коммутатора 1 подключены к информационным входам признаков устройства, информационный вход аналого-цифрового преобразователя 4 подключен к выходу многоканального коммутатора 1, адресные входы младших разрядов блока памяти коэффициентов ассоциативности признаков 7 подключены к выходу аналого-цифрового преобразователя 4, а адресные входы старших разрядов блока памяти коэффициентов ассоциативности признаков 7 подключены к адресным входам многоканального коммутатора 1 и к выходам младших информационных разрядов блока памяти выбора адресов 6, все выходы которого подключены ко входам буферного регистра 9, выходы которого подключены ко входам регистра адресов 3, выходы которого подключены к адресным входам старших разрядов блока памяти выбора адресов 6, а адресные входы младших разрядов блока памяти выбора адресов 6 подключены к выходам блока сдвиговых регистров 10, в котором информационные входы первых разрядов сдвиговых регистров 12 подключены к соответствующим информационным входам блока сдвиговых регистров 10, сдвиговые входы сдвиговых регистров 12 подключены к соответствующим сдвиговым входам блока сдвиговых регистров 10, информационные входы которого подключены к выходам блока памяти коэффициентов ассоциативности признаков 7 и к соответствующим первым входам блока логических элементов И 8, в котором первые и вторые входы логических элементов И 11 подключены к соответствующим первым и вторым входам блока логических элементов И 8, выходы логических элементов И 11 являются выходами блока логических элементов И 8, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров 10, все выходы сдвиговых регистров 12 подключены к выходам блока сдвиговых регистров 10, а сбросовые входы всех сдвиговых регистров 12 объединены и подключены к сбросовому входу блока сдвиговых регистров 10, выходы последних разрядов которого являются выходами устройства и подключены ко входам логического элемента ИЛИ 2, выход которого подключен ко второму управляющему входу блока управления 5, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к управляющим входам блоков памятей выбора адресов 6 и коэффициентов ассоциативности признаков 7, ко второму входу блока логических элементов И 8 и управляющему входу регистра адресов 3, к управляющим входам аналого-цифрового преобразователя 4 и буферного регистра 9, к сбросовым входам регистра адресов 3 и блока сдвиговых регистров 10.

Блок логических элементов И 8, как показано на фиг.2, содержит логические элементы И 11, число которых равно числу распознаваемых классов образов k, причем первые входы логических элементов И 11 через первые входы блока логических элементов И 8 подключены к соответствующим информационным входам блока сдвиговых регистров 10 и к соответствующим выходам Q1-Qk блока памяти коэффициентов ассоциативности признаков 7, где Q1 соответствует младшему разряду информационного слова блока памяти коэффициентов ассоциативности признаков 6, a Qk - старшему разряду. Вторые входы логических элементов И 11 блока логических элементов И 8 подключены к объединенным вторым входам блока логических элементов И 8 и к третьему управляющему выходу блока управления 5, а выходы логических элементов И 11 блока логических элементов И 8 через соответствующие выходы блока логических элементов И 8 подключены к соответствующим сдвиговым входам блока сдвиговых регистров 10.

Блок сдвиговых регистров 10, как показано на фиг.2, как и в известном устройстве, содержит k m-разрядных сдвиговых регистров 12, где m соответствует порогу распознавания, причем информационные входы первых разрядов, сдвиговые и объединенные сбросовые входы сдвиговых регистров 12 подключены к соответствующим информационным, сдвиговым и сбросовому входам блока сдвиговых регистров 10, а все выходы сдвиговых регистров 12 подключены к выходам блока сдвиговых регистров 10. Под порогом распознавания в предлагаемом устройстве так же, как и в известном устройстве, понимается минимальное число положительных проверок m на принадлежность значений проверяемых признаков некоторому классу образов, по достижении которого принимается решение о принадлежности проверяемой совокупности признаков данному классу образов. Этот термин достаточно широко используется в научно-технической литературе, например в работе Козлова Ю.М. "Адаптация и обучение в робототехнике" (- M.: Наука, 1990) на странице 221, а также в статье Тельных А., Когана А. и др. "Идентификация личности. Как это делается" (журнал "Компьютера", №10, 1999 г.).

Блок управления, как показано на фиг.3, содержит логический элемент И-НЕ 13, элемент задержки 14, триггер пуска-останова 15, генератор тактовых импульсов 16, логические элементы И 17, 18, блок формирования и распределения управляющих сигналов, логический элемент ИЛИ 20, причем первый вход логического элемента И-НЕ 13 подключен к первому входу блока управления 5, а выход логического элемента И-НЕ 13 подключен к пятому выходу блока управления 5 и к установочному входу триггера пуска-останова 15, сбросовый вход которого подключен к выходу логического элемента ИЛИ 20, первый выход триггера пуска-останова 15 подключен к первому входу логического элемента И 17, а инверсный выход триггера пуска-останова 15 подключен ко входу элемента задержки, выход которого подключен ко второму входу логического элемента И-НЕ 13, второй вход логического элемента И 17 подключен к выходу генератора тактовых импульсов 16 и к первому входу логического элемента И 18, второй вход которого подключен ко второму входу блока управления 5, выход логического элемента И 17 подключен ко входу блока управления и распределения управляющих сигналов 19, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к первому, четвертому, второму, третьему выходам блока управления 5 и к первому входу логического элемента ИЛИ 20, второй вход которого подключен к выходу логического элемента И 18.

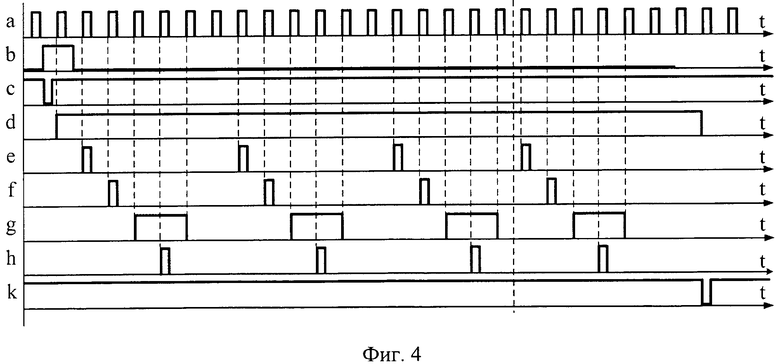

На фиг.4 временные диаграммы ″a″, ″b″, ″c″, ″d″, ″e″, ″f″, ″g″, ″h″ и ″k″ представляют процессы формирования и поступления сигналов соответственно с выхода генератора тактовых импульсов 16, на управляющем входе устройства, на выходе логического элемента И-НЕ 13, на выходе логического элемента И 17, на первом, втором, третьем, четвертом и пятом выходах блока формирования и распределения управляющих сигналов 19.

Предлагаемое устройство работает следующим образом.

Запуск устройства производится подачей на управляющий вход блока управления 5 сигнала "пуск", который обнуляет регистр адресов 3 и все сдвиговые регистры 12 блока сдвиговых регистров 10. По совокупному адресу, сформированному из кода на выходе регистра адресов 3 и кода на выходе блока сдвиговых регистров 10, по сигналу чтения, поступающему с первого выхода блока управления 5 на управляющий вход блока памяти выбора адресов 6, код адреса первого признака поступает с выходов младших разрядов блока памяти выбора адресов 6 на входы буферного регистра 9, на адресные входы многоканального коммутатора 1 и на старшие разряды адреса блока памяти коэффициентов ассоциативности признаков 7 для выбора первого информационного канала устройства и выбора соответствующей страницы блока памяти коэффициентов ассоциативности признаков 7. Далее по управляющему сигналу, поступающему с четвертого выхода блока управления 5 на управляющие входы аналого-цифрового преобразователя 4 и буферного регистра 9, производится занесение информации с выхода блока памяти выбора адресов 6 в буферный регистр 9 и преобразование аналогового сигнала первого признака в цифровой код, который поступает с выходов аналого-цифрового преобразователя 4 на адресные входы младших разрядов блока памяти коэффициентов ассоциативности признаков 7. По совокупному адресу, сформированному из кода адреса признака на выходе младших информационных разрядов блока памяти выбора адресов 6 и цифрового кода с выхода аналого-цифрового преобразователя 4, по сигналу чтения, поступающему со второго выхода блока управления 5 на управляющий вход блока памяти коэффициентов ассоциативности признаков 7, коды классов образов, соответствующие оцифрованному значению первого признака, поступают на информационные входы блока сдвиговых регистров 10 и на первые входы блока логических элементов И 8. Далее на управляющий вход регистра адресов 3 и на объединенные вторые входы блока логических элементов И 8 с третьего выхода блока управления 5 поступает управляющий сигнал занесения для регистра адресов 3 и сигнал занесения-сдвига для сдвиговых регистров 12 блока сдвиговых регистров 10, на информационных входах первых разрядов которых установлен единичный код, поступивший из блока памяти коэффициентов ассоциативности признаков 7. Сигнал занесения-сдвига на сдвиговом входе сдвигового регистра 12 формируется логическим элементом И 11 блока логических элементов И 8 при совпадении на его входах единичного кода из блока памяти коэффициентов ассоциативности признаков 7 и сигнала с третьего выхода блока управления 5. По сигналу занесения-сдвига единичные коды классов образов через информационные входы первых разрядов сдвиговых регистров 12 блока сдвиговых регистров 10 заносятся в сдвиговые регистры 12. При этом порядковый номер каждого сдвигового регистра 12 блока сдвиговых регистров 10 соответствует порядковому номеру информационного разряда блока памяти коэффициентов ассоциативности признаков 7, начиная с младшего разряда, и соответственно номеру классов образов. На этом завершается процедура проверки значения первого признака на соответствие для всех классов образов. Далее аналогично по совокупному адресу, сформированному из кода на выходе регистра адресов 3 и кода ситуации на выходе блока сдвиговых регистров 10, по сигналу чтения, поступающему с первого выхода блока управления 5 на управляющий вход блока памяти выбора адресов 6, составной код, содержащий адреса следующего и предыдущего признака распознавания, поступает с выхода блока памяти выбора адресов 6 на все входы буферного регистра 9. Причем код с выхода младших разрядов блока памяти выбора адресов 6, соответствующий адресу следующего признака, поступает также на адресные входы многоканального коммутатора 1 и на старшие разряды адреса блока памяти коэффициентов ассоциативности признаков 7 для выбора следующего информационного канала устройства и выбора соответствующей страницы блока памяти коэффициентов ассоциативности признаков 7. По сигналам блока управления 5 через многоканальный коммутатор 1 к информационному каналу аналого-цифрового преобразователя 4 подключается информационный канал того признака распознавания, чей порядок приоритетности выше остальных (см. таблицу 1), а на адресные входы старших разрядов. блока памяти коэффициентов ассоциативности признаков 7 поступает код адреса для выбора соответствующей страницы блока памяти коэффициентов ассоциативности признаков 7 для значений и кодов классов выбранного исходя из порядка приоритетности признака распознавания. После аналого-цифрового преобразования значения признака, занесения кода адреса следующего признака в буферный регистр 9 и считывания из блока памяти коэффициентов ассоциативности признаков 7 коды классов образов аналогично предыдущим кодам классов образов заносятся в соответствующие сдвиговые регистры 12 блока сдвиговых регистров 10. При этом составной код адреса опрошенного и последующего признака с выхода буферного регистра 9 заносится в регистр адресов 3. Идентификация класса образа производится по конечному состоянию последних разрядов сдвиговых регистров 12 блока сдвиговых регистров 10 (см. фиг.2). Наличие единичного кода в последнем разряде сдвигового регистра 12 блока сдвиговых регистров 10 свидетельствует о принадлежности исследуемых признаков распознавания классу образов, соответствующему порядковому номеру этого сдвигового регистра.

Для иллюстрации принципа работы предлагаемого устройства в таблицах 1-3 представлены примеры распознавания двух классов образов Q1 и Q2 по принципу «два из трех».

В таблице 1 представлены порядки приоритетности выбора признаков с учетом достоверности принадлежности признаков к каждому образу. В частности, оценка вероятности того, что первый признак достоверно свидетельствует о классе образов Q1, определяется как Р1=0.7. Соответственно, для второго и третьего признаков: Р2=0.9, а Р3=0.8. Для класса образов Q2 оценки вероятностей соответственно равны: Р1=0.8 5, Р1=0.75, Р3=0.95. Двоичные коды адресов каналов, по которым регистрируются признаки, начиная с первого, равны соответственно: ″00″, ″01″ и ″10″.

разряд

разряд

В таблицах 2 и 3 ″r1″ - ″r6″ обозначают значения разрядов в регистре адресов, начиная с младшего, ″R11″ - ″R12″ - значения разрядов первого сдвигового регистра блока сдвиговых регистров, соответствующего классу образов Q1, начиная с младшего разряда, a ″R21″ - ″R22″ - соответственно, значения разрядов сдвигового второго регистра.

В представленном примере рассмотрены два варианта распознавания образа Q1. В таблице 2, когда распознавание происходит без сбоев, в таблице 3, когда допущен сбой во втором такте распознавания в пользу класса образов Q2. Для рассмотрения общего случая в примерах, распознавание начинается с первого признака. Как видно из примеров, если процесс идет без сбоев, то в предлагаемом устройстве он завершается за два такта. Для устройства-прототипа распознавание во всех случаях производится за три такта, то есть по окончании проверки всех признаков распознавания.

Для иллюстрации принципа работы предлагаемого устройства в таблице 4 представлено содержимое блока памяти выбора адресов. В таблице серым цветом выделены значения неиспользуемых адресов для указанного примера, а символ ″X″ в столбцах ″a6″ - ″a1″ сигнализируют о необходимости завершения процесса распознавания при выборе соответствующего значения адреса блока памяти выбора адресов. Ячейки (см. столбцы ″a6″ - ″a1″ таблицы 4) блока памяти выбора адресов содержат адреса информационных каналов устройства по приоритету с учетом предистории опроса признаков.

Блок управления 5, структурная схема которого представлена на фиг.3, работает следующим образом.

В исходном состоянии триггер пуска-останова 15 сброшен, на первом входе логического элемента И 17 установлен отрицательный потенциал, и импульсы с выхода генератора тактовых импульсов 16, представленные на временной диаграмме ″a″ фиг.4, не поступают на выход логического элемента И 17. На первом входе логического элемента И-НЕ 13 также установлен отрицательный потенциал, а на втором входе - положительный потенциал, который поступает с инверсного выхода триггера пуска-останова 15. При подаче на первый вход логического элемента И-НЕ 13 сигнала ″пуск″, который поступает в виде импульса положительной полярности, представленного на временной диаграмме ″b″ фиг.4, на выходе логического элемента И-НЕ 13 формируется импульс отрицательной полярности так, как показано на временной диаграмме ″c″ фиг.4, триггер пуска-останова 15 переключается в единичное состояние так, как показано на временной диаграмме ″d″ фиг.4. При этом с инверсного выхода триггера пуска-останова 15 сигнал отрицательной полярности поступает через элемент задержки 14 на второй вход логического элемента И-НЕ 13, на выходе которого формируется отрицательный импульс необходимой длительности, который поступает на пятый выход блока управления 5 для сброса регистра адресов 3 и блока сдвиговых регистров 10. Это отражено на временной диаграмме ″c″ фиг.4. Далее импульсы с выхода генератора тактовых импульсов 16 поступают на вход блока формирования и распределения управляющих сигналов 19, который выдает последовательно на первый, четвертый, второй и третий выходы блока управления 5 сигналы для чтения из блока памяти выбора адресов 6 так, как показано на временной диаграмме ″e″ фиг.4, сигналы запуска аналого-цифрового преобразователя 4 и занесения информации в буферный регистр 9, представленные на диаграмме ″f″ фиг.4, сигналы чтения из блока памяти коэффициентов ассоциативности признаков 7, представленные на диаграмме ″g″ фиг.4, и сигналы занесения адресов в регистр адресов 3 и занесения-сдвига данных в блок сдвиговых регистров 10, представленные на диаграмме ″h″ фиг.4. При появлении на любых входах логического элемента ИЛИ 20 единичного сигнала, который формируется либо по окончании проверки соответствия всех признаков распознавания на пятом выходе блока формирования и распределения управляющих сигналов 19, либо на выходе логического элемента И 18, при получении на своих обоих входах единичных сигналов, которые поступают от второго управляющего входа U2 блока управления бис выхода генератора тактовых импульсов 16. Далее сигнал с выхода логического элемента ИЛИ 20 поступает на сбросовый вход триггера пуска-останова 15 для перевода блока управления 5 в исходное состояние. Этот сигнал представлен на диаграмме ″k″ фиг.4 в виде импульса отрицательной полярности.

Для оценки прироста производительности предлагаемого устройства на примере устройства, работающего по принципу «два из трех» рассчитаем вероятность сбоя его (Робщ) при анализе любого одного из трех признаков по следующей формуле:

где P1, P2 и Р3 - соответственно оценки вероятностей сбоя принадлежности первого, второго и третьего признаков распознаваемому образу.

Если предположить, что P1=0.01, Р2=0.02, а Р3=0.03, то Робщ=0.0578. Это свидетельствует о том, что процент операций распознавания, при которых необходимо использовать все три признака, составляет примерно 6%. Это означает, что при заданных в примере вероятностях сбоев производительность предлагаемого устройства лишь в 6% от общего числа операций распознавания будет работать с производительностью устройства-прототипа и использовать для распознавания все три признака. В остальных 94% предлагаемое устройство будет работать с повышенной производительностью за счет использования для распознавания двух признаков. При этом численная оценка увеличения производительности составит примерно 33.3%.

Положительный эффект в предлагаемом техническом решении, по сравнению с известным, получен за счет использования ситуационного подхода при выборе очередности признаков распознавания и введением в устройство распознавания логического элемента ИЛИ, регистра адресов, блока памяти выбора адресов и буферного регистра.

Предлагаемое устройство может быть реализовано на базе доступных серийных интегральных микросхем, например сдвиговые регистры - на базе микросхем К155ИР1, блок управления и блок логических элементов И - на базе серии микросхем К 155, буферный регистр и регистр адресов - на микросхеме К155ИЕ7, а блоки памятей - на микросхемах серии КР558РР1.

Примеры реализации блоков предлагаемого устройства представлены в научно-технической литературе. Схемы многоканального коммутатора 1, аналого-цифрового преобразователя 4 представлены, например, в справочном пособии «Аналоговые и цифровые интегральные микросхемы», авторы: Якубовский С.В., Барканов Н.А. и др. (- М.: Радио и связь, 1984 г.), схемы элемента ИЛИ 2, регистра адресов 3, блоков памятей 6 и 7, буферного регистра 9, элементов И 11 блока логических элементов И 8 и сдвиговых регистров 12 блока сдвиговых регистров 10 - в справочнике «Применение интегральных микросхем в электронной вычислительной технике», авторы: Данилов Р.В., Ельцова С.А. и др. (- М.: Радио и связь, 1986), схема блока управления 5 - в книге Букреева И.Н., Горячева В.И. и Мансурова Б.М. «Микроэлектронные схемы цифровых устройств» (- М.: Радио и связь, 1990. - 416 с), а также в книге Угрюмова Е.П. «Цифровая схемотехника» (- Санкт-Петербург: изд-во «Санкт-Петербург», 2000. - 528 с). Принцип страничной адресации описан в ряде литературных источников, например в книге Цилькера Б.Я. и Орлова С.А. «Организация ЭВМ и систем» (- М., Санкт-Петербург: «Питер», 2006. - 668 с). Использование логического элемента ИЛИ 2, регистра адресов 3, дополнительного блока памяти выбора адресов 6 и буферного регистра 10 в предлагаемом устройстве приводит к изменениям в подключении выходов блока сдвиговых регистров 10 к адресным разрядам блока памяти выбора адресов 6 так, как показано на фиг.1, и не изменяет типовых схемных реализации блока памяти коэффициентов ассоциативности признаков 7 и аналого-цифрового преобразователя 4, представленных в известном устройстве и вышеприведенной литературе.

Предлагаемое устройство также может быть использовано для оперативного распознавания дорожных ситуаций в системах обеспечения активной безопасности транспорта при наличии множества дорожно-транспортных признаков распознавания с произвольным характером изменения значений.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2535182C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2013 |

|

RU2540818C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2006 |

|

RU2306605C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОВЕДЕНИЯ ПОЛЬЗОВАТЕЛЯ | 2018 |

|

RU2675896C1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| ОПТИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2035069C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

Изобретение относится к автоматике и вычислительной технике. Технический результат - повышение производительности устройства. Устройство для распознавания образов содержит многоканальный коммутатор, аналого-цифровой преобразователь, блок памяти коэффициентов ассоциативности признаков, блок логических элементов И, блок сдвиговых регистров, блок управления, логический элемент ИЛИ, регистр адресов, блок памяти выбора адресов, буферный регистр. 4 ил., 4 табл.

Устройство для распознавания образов, содержащее многоканальный коммутатор, информационные входы которого подключены к информационным входам признаков устройства, аналого-цифровой преобразователь, информационный вход которого подключен к выходу многоканального коммутатора, блок памяти коэффициентов ассоциативности признаков, у которого адресные входы младших разрядов подключены к выходу аналого-цифрового преобразователя, а адресные входы старших разрядов подключены к адресным входам многоканального коммутатора, блок логических элементов И, в котором первые и вторые входы логических элементов И подключены к соответствующим первым и вторым входам блока логических элементов И, выходы логических элементов И являются выходами блока логических элементов И, блок сдвиговых регистров, в котором информационные входы первых разрядов сдвиговых регистров подключены к соответствующим информационным входам блока сдвиговых регистров, сдвиговые входы сдвиговых регистров подключены к соответствующим сдвиговым входам блока сдвиговых регистров, блок управления, второй, третий и четвертый выходы которого подключены соответственно к управляющему входу блока памяти коэффициентов ассоциативности признаков, ко второму входу блока логических элементов И и к управляющему входу аналого-цифрового преобразователя, а первый вход блока управления подключен к управляющему входу устройства, выходы блока памяти коэффициентов ассоциативности признаков подключены к соответствующим информационным входам блока сдвиговых регистров и к соответствующим первым входам блока логических элементов И, выходы которого подключены к соответствующим сдвиговым входам блока сдвиговых регистров, отличающееся тем, что в него включены: логический элемент ИЛИ, регистр адресов, блок памяти выбора адресов, буферный регистр, причем выходы регистра адресов подключены к адресным входам старших разрядов блока памяти выбора адресов, адресные входы младших разрядов которого подключены к выходам блока сдвиговых регистров, все выходы блока памяти выбора адресов подключены ко входам буферного регистра, а выходы младших разрядов блока памяти выбора адресов, соответствующие адресу следующего признака, подключены также к адресным входам многоканального коммутатора и к адресным входам старших разрядов блока памяти коэффициентов ассоциативности признаков, управляющий вход буферного регистра подключен к управляющему входу аналого-цифрового преобразователя и к четвертому выходу блоку управления, а выходы буферного регистра подключены ко входам регистра адресов, сбросовый вход которого подключен к сбросовому входу блока сдвиговых регистров и к пятому выходу блока управления, а управляющий вход регистра адресов подключен ко второму входу блока логических элементов И и к третьему выходу блока управления, первый выход которого подключен к управляющему входу блока памяти выбора адресов, все выходы сдвиговых регистров подключены к выходам блока сдвиговых регистров, а сбросовые входы всех сдвиговых регистров объединены и подключены к сбросовому входу блока сдвиговых регистров, выходы последних разрядов которого являются выходами устройства и подключены ко входам логического элемента ИЛИ, выход которого подключен ко второму управляющему входу блока управления.

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2006 |

|

RU2306605C1 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2000 |

|

RU2195702C2 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ И ПОДСЧЕТА КРИТИЧЕСКИХ ВЫБРОСОВ ИЛИ ПРОВАЛОВ НАПРЯЖЕНИЯ И ОПРЕДЕЛЕНИЯ СУММАРНОГО ВРЕМЕНИ ОТКАЗОВ ЭЛЕКТРООБОРУДОВАНИЯ | 2001 |

|

RU2193230C1 |

| JP 5231841 A, 07.09.1993 | |||

| US 4490847 A1, 25.12.1984 | |||

Авторы

Даты

2014-11-20—Публикация

2013-11-06—Подача