i4

СО

10

20

25

30

Изобретение относится к вычислительной технике и может быть использована для построения микропрограммных микропроцессорных систем.

Цель изобретения - повышение достоверности функционирования, устройства за счет контроля линейных и ветвящихся участков микропрограмм.

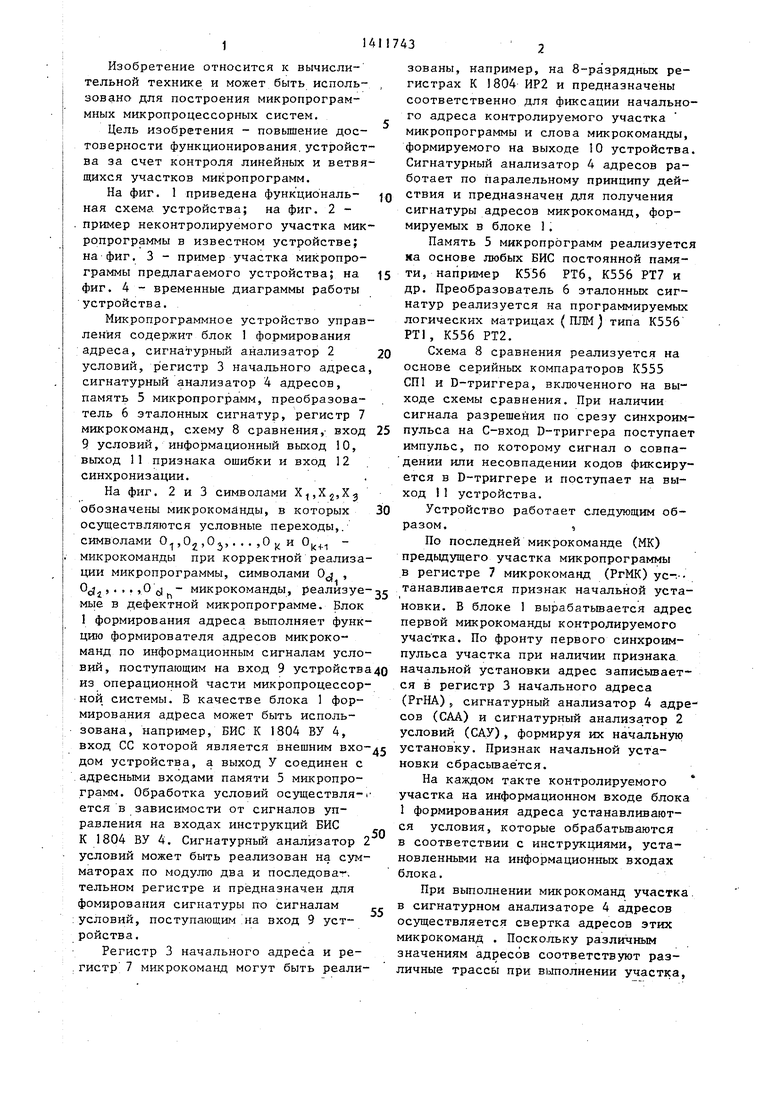

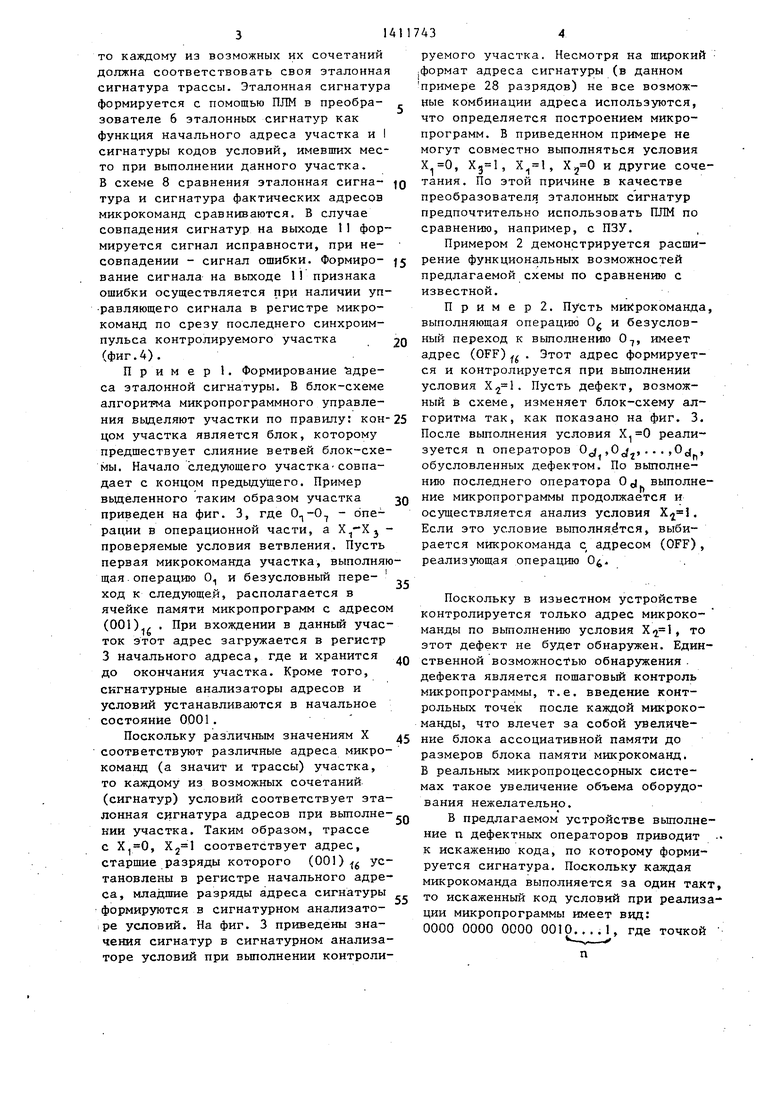

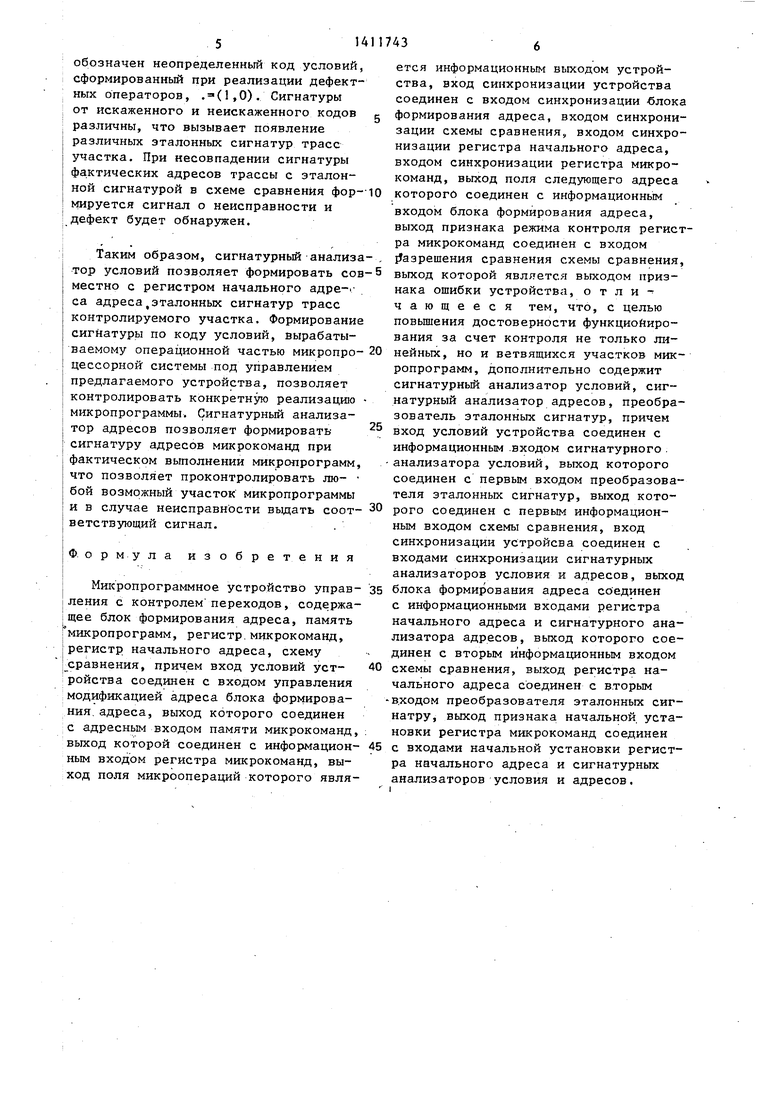

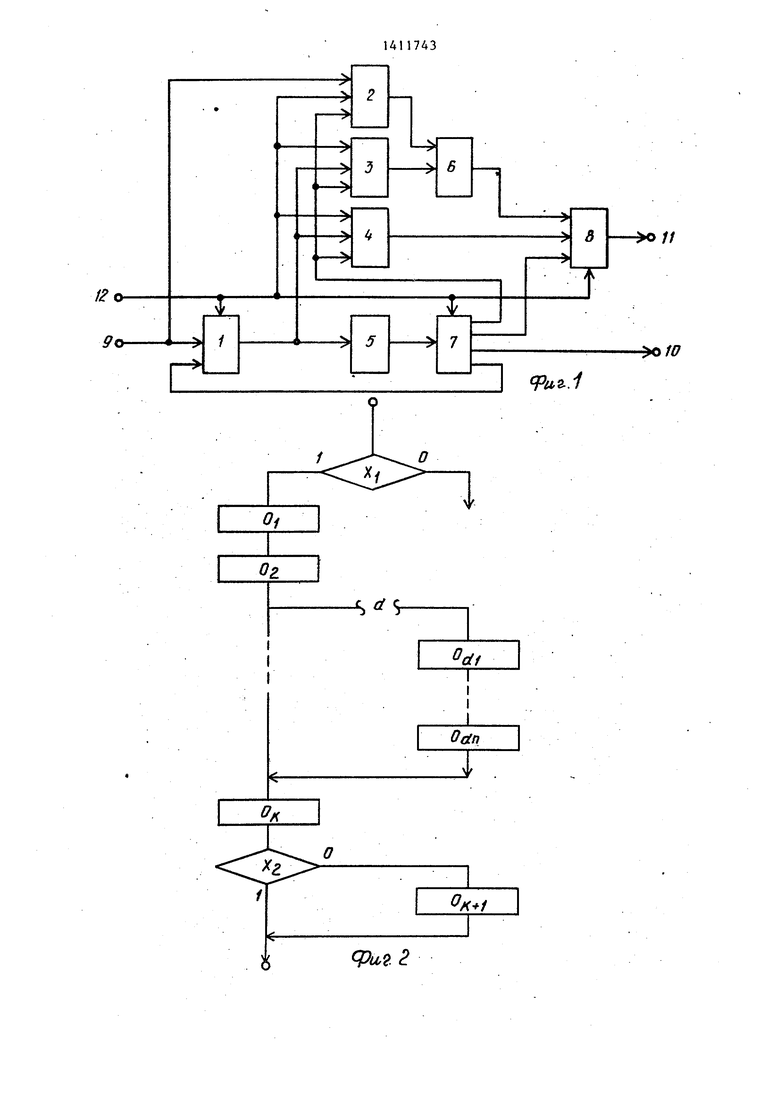

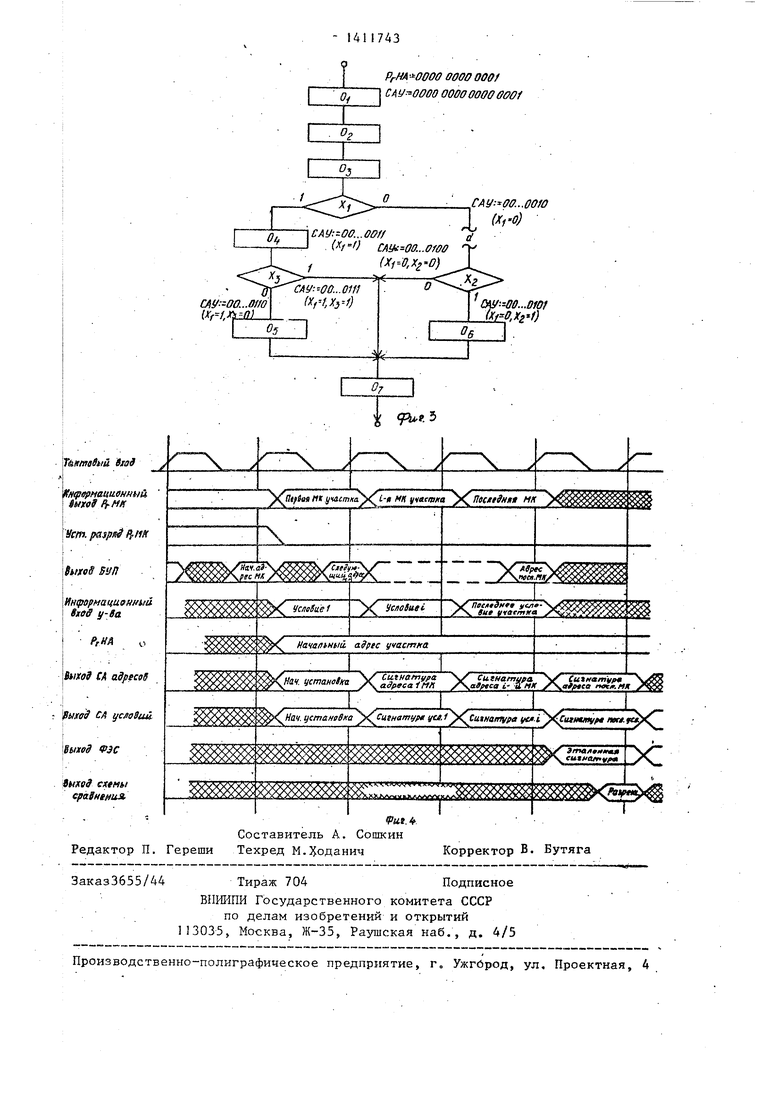

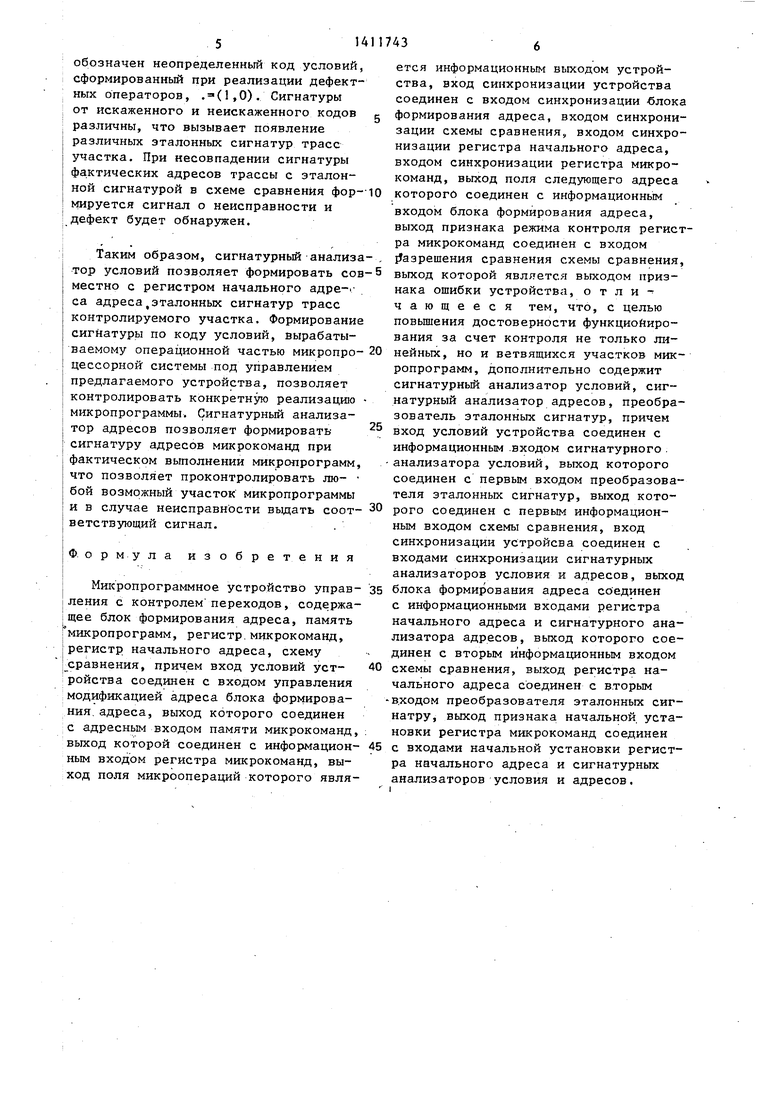

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - пример неконтролируемого участка микропрограммы в известном устройстве; на фиг. 3 - пример участка микропрограммы предлагаемого устройства; на 15 фиг. 4 - временные диаграммы работы устройства.

Микропрограммное устройство управления содержит блок 1 формирования адреса, сигнатурный анализатор 2 условий, регистр 3 начального адреса, сигнатурный анализатор 4 адресов, память 5 микропрограмм, преобразователь 6 эталонных сигнатур, регистр 7 микрокоманд, схему 8 сравнения,- вход 9 условий, информационный выход 10, выход 11 признака ошибки и вход 12 синхронизации.

На фиг. 2 и 3 символами X,Xj,Xj обозначены микрокоманды, в которых осуществляются условные переходы,, символами 0,02,0,..., 0|., - микрокоманды при корректной реализации микропрограммы, символами 0 ,

1 0 , . , . ,0 ( - микрокоманды, реализуе- с

Mbie в дефектной микропрограмме. Блок 1 формирования адреса выполняет функцию формирователя адресов микрокоманд по информационным сигналам условий, поступающим на вход 9 устройства40 из операционной части микропроцессорной системы. В качестве блока 1 формирования адреса может быть использована, например, БИС К 1804 ВУ 4, вход СС которой является внешним вхо- дом устройства, а выход У соединен с адресными входами памяти 5 микропрограмм. Обработка условий осуществля-г ется в зависимости от сигналов управления на входах инструкций БИС К 1804 ВУ 4. Сигнатурный анализатор 2 условий может быть реализован на сумматорах по модулю два и последоваг. тельном регистре и предназначен для фомирования сигнатуры по сигналам

условий, поступающи - на вход 9 устройства.

Регистр 3 начального адреса и регистр 7 микрокоманд могут быть реали,50

55

10

20

25

30

15

с

40

0

5

зованы, например, на 8-разрядных регистрах К 1804 ИР2 и предназначены соответственно для фиксации начального адреса контролируемого участка микропрограммы и слова микрокоманды, формируемого на выходе 10 устройства. Сигнатурный анализатор 4 адресов работает по паралельному принципу действия и предназначен для получения сигнатуры адресов микрокоманд, формируемых в блоке 1.

Память 5 микропрограмм реализуется ма основе любых БИС постоянной памяти, например К556 РТ6, К556 РТ7 и др. Преобразователь 6 эталонных сигнатур реализуется на программируемых логических матрицах ( ПЛМ ) типа К556 РТ1, К556 РТ2.

Схема 8 сравнения реализуется на основе серийных компараторов К555 СП1 и D-триггера, включенного на выходе схемы сравнения. При наличии сигнала разрешения по срезу синхроимпульса на С-вход D-триггера поступает импульс, по которому сигнал о совпадении или несовпадении кодов фиксируется в D-триггере и поступает на выход I1 устройства.

Устройство работает следующим образом.5

По последней микрокоманде (МК) предыдущего участка микропрограммы в регистре 7 микрокоманд (РгМК) ус-.- танавливается признак начальной установки. В блоке 1 вырабатьшается адрес первой микрокоманды контролируемого участка. По фронту первого синхроимпульса участка при наличии признака начальной установки адрес записьшает- ся в регистр 3 начального адреса (РгНА)5 сигнатурный анализатор 4 адресов (САА) и сигнатурный анализатор 2 условий (САУ), формируя их начальную установку. Признак начальной установки сбрасьгоаётся.

На каждом такте контролируемого участка на информационном входе блока 1 формирования адреса устанавливаются условия, которые обрабатьшаются в соответствии с инструкциями, установленными на информационных входах блока.

При выполнении микрокоманд участка, в сигнатурном анализаторе 4 адресов осуществляется свертка адресов этих микрокоманд . Поскольку различным значениям адресов соответствуют различные трассы при выполнении участка.

то каждому из возможных их сочетаний должна соответствовать своя эталонная сигнатура трассы. Эталонная сигнатура формируется с помощью ПЛМ в преобра- зователе 6 эталонных сигнатур как функция начального адреса участка и I сигнатуры кодов условий, имевпгах место при выполнении данного участка. В схеме 8 сравнения эталонная сигна- тура и сигнатура фактических адресов микрокоманд сравниваются. В случае совпадения сигнатур на выходе 11 формируется сигнал исправности, при несовпадении - сигнал ошибки. Формиро- вание сигнала на выходе 1 признака ошибки осуществляется при наличии уп- равляющего сигнала в регистре микрокоманд по срезу последнего синхроимпульса контролируемого участка (фиг.4).

Пример 1. Формирование Адреса эталонной сигнатуры. В блок-схеме алгоритма микропрограммного управления выделяют участки по правилу: концом участка является блок, которому предшествует слияние ветвей блок-схемы. Начало следующего участка-совпадает с концом предыдущего. Пример вьзделенного таким образом участка приведен на фиг. 3, где - операции в операционной части, а - проверяемые условия ветвления. Пусть первая микрокоманда участка, выполняющая, операцию 0 и безусловный переход к следующей, располагается в ячейке памяти микропрограмм с адресом (001)., . При вхождении в данный участок этот адрес загружается в регистр 3 начального адреса, где и хранится до окончания участка. Кроме того, сигнатурные анализаторы адресов и условий устанавливаются в начальное состояние 0001.

Поскольку различным значениям X соответствуют различные адреса микрокоманд (а значит и трассы) участка, то каждому из возможных сочетаний (сигнатур) условий соответствует эталонная С11гнатура адресов при вьтолне- НИИ участка. Таким образом, трассе с Х,0, соответствует адрес, старшие разряды которого (00) установлены в регистре начального адреса, младпше разряды адреса сигнатуры формируются в сигнатурном анализато- I ре условий. На фиг. 3 приведены значения сигнатур в сигнатурном анализаторе условий при вьшолнении контролируемого участка. Несмотря на широкий |формат адреса сигнатур1Ы (в данном примере 28 разрядов) не все возможные комбинации адреса используются, что определяется построением микропрограмм. В приведенном примере не могут совместно вьтолняться условия X 0, , , и другие сочетания. По этой причине в качестве преобразователя эталонных: сигнатур предпочтительно использовать ПЛМ по сравнению, например, с ПЗУ.

Примером 2 демонстрируется расширение функциональных возможностей предлагаемой схемы по сравнению с известной.

П р и м е р 2. Пусть микрокоманда выполняющая операцию 0 и безусловный переход к вьтолнению О-,, имеет адрес (OFF) . Этот адрес формируется и контролируется при вьтолнении условия . Пусть дефект, возможный в схеме, изменяет блок-схему алгоритма так, как показано на фиг. 3. После выполнения условия реализуется п операторов Oj 0 j , . . . ,0jj , обусловленных дефектом. По выполнению последнего оператора Оj выполнение микропрограммы продолжается и осуществляется анализ условия . Если это условие выполняется, выбирается микрокоманда с/адресом (OFF), реализующая операцию 04,

Поскольку в известном устройстве контролируется только адрес микрокоманды по вьтолнению условия Х,2. то этот дефект не будет обнаружен. Единственной возможностью обнаружения . дефекта является пошаговый контроль микропрограммы, т.е. введение контрольных точек после каждой микрокоманды, что влечет за собой увеличение блока ассоциативной памяти до размеров блока памяти микрокоманд. В реальных микропроцессорных системах такое увеличение объема оборудования нежелательно.

В предлагаемом устройстве вьшолне ние п дефектных операторов приводит к искажению кода, по которому формируется сигнатура. Поскольку каждая микрокоманда выполняется за один так то искаженный код условий при реализции микропрограммы имеет вид: 0000 0000 0000 0010....1, где точкой

п

обозначен неопределенный код условий, сформированный при реализации дефектных операторов, .(1,0), Сигнатуры от искаженного и неискаженного кодов различны, что вызывает появление различных эталонных сигнатур трасс участка. При несовпадении сигнатуры фа.ктических адресов трассы с эталонной сигнатурой в схеме сравнения формируется сигнал о неисправности и дефект будет обнаружен.

Таким образом, сигнатурный анализа тор условий позволяет формировать сов местно с регистром начального адре- - са адреса,эталонных сигнатур трасс контролируемого участка. Формирование сигнатуры по коду условий, вырабатываемому операционной частью микропро- цессорной системы под управлением предлагаемого устройства, позволяет контролировать конкретную реализацию микропрограммы. Сигнатурный анализатор адресов позволяет формировать сигнатуру адресов микрокоманд при фактическом вьтолнении микропрограмм, что позволяет проконтролировать лю- бой возможный участок микропрограммы и в случае неисправности вьщать соответствующий сигнал.

Ф. ормула изобретения

,

5

0

ется информационным выходом устройства, вход синхронизации устройства соединен с входом синхронизации блока формирования адреса, входом синхронизации схемы сравнения, входом синхронизации регистра начального адреса, входом синхронизации регистра микрокоманд, выход поля следующего адреса которого соединен с информационным входом блока формирования адреса, выход признака режима контроля регистра микрокоманд соединен с входом {Разрешения сравнения схемы сравнения, выход которой является выходом признака ошибки устройства, отличающееся тем, что, с целью повьшения достоверности функциойиро- вания за счет контроля не только линейных, но и ветвящихся участков микропрограмм, дополнительно содержит сигнатурньй анализатор условий, сигнатурный анализатор адресов, преобразователь эталонных сигнатур, причем вход условий устройства соединен с информационным .входом сигнатурного. анализатора условий, выход которого соединен с первым входом преобразователя эталонных сигнатур, выход которого соединен с первым информационным входом схемы сравнения, вход синхронизации устройсва соединен с входами синхронизации сигнатурных

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1647565A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля хода микропрограмм | 1988 |

|

SU1661772A1 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения микропро- граммируемых микропроцессорных систем. Целью изобретения является повышение достоверности функционирования за счет контроля не только линейных, но и ветвящихся участков микропрограмм, Микропрограммное устройство управления содержит блок.формирования адресов, память микропрограмм, регистр микрокоманд, схему сравнения, регистр начального адреса, сигнатурный анализатор условий, сигнатурный анализатор адресов микрокоманд и преобразователь эталонных сигнатур. Устройство обеспечивает контроль трасс выполнения микропрограмм. Введение сигнатурного анализатрра условий,- сигнатурного анализатора адресов,.преобразователя эталонных сигнатур обес- g печивает достижение поставленной це- ли. 4 ил. (Л

анализаторов условия и адресов, выход Микропрограммное устройство управ- 35 блока формирования адреса соединен

ления с контролем переходов, содержащее блок формирования адреса, память

микропрограмм, регистр, микрокоманд, регистр начального адреса, схему

сравнения, причем вход условий уст- ройства соединен с входом управления модификацией адреса блока формирования, адреса, выход которого соединен с адресным входом памяти микрокоманд, выход которой соединен с информацион- ным входом регистра микрокоманд, выход поля микроопераций которого являс информационными входами регистра начального адреса и сигнатурного анализатора адресов, выход которого соединен с вторым информационным входом схемы сравнения, выход регистра начального адреса соединен с в.торым -в.ходом преобразователя эталонных сиг- натру, выход признака начальной, установки регистра микрокоманд соединен с входами начальной установки регистра начального адреса и сигнатурных анализаторов условия и адресов.

T&itmgSiiu вгад

Ifteil tm учлстна -в HH уЧЛС1Я11аУ Л(См9ня HK

HmsepNtmueHH iu

6ЫХ09 ffMK

Ус(п. psspK

SuifeS san

KHtpofManusNH a txoff у-ва

PrifA о ВчИоЗ CA адресов

ыхвд CA gcfoSuu. SbixeS 93C

схемн epaJHSffHA

9ui.

Составитель A. Сошкин Редактор П. Гереши Техред М.}{оданич Корректор В. Вутяга

Наи tifmnualK, V CutHOfnyfa / Сигнаепцрл Л/ ,

ич. устанаит / gg ecainn i-инк пеЦ.мц

Сигнатур

I. цстанавка CutHemyft уа, f CutHairyfa ytf-Cy iuHvayft net.f

PfHA- OOOO OOffff 000/

,

/мео пеЦ.мц

Сигнатур

| Микропрограммное устройство с контролем переходов | 1977 |

|

SU711573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-19—Подача