Изобретение относится к области измерительной и вычислительной техники и может быть использовано для быстрого преобразования аналоговых электрических сигналов в цифровой код в системах, функционирующих в модулярной системе счисления.

Известно устройство (аналог) (авт.св. СССР №1368989, МКИ Н03М 1/28, БИ №3, 1988 г.), содержащее блок определения остатка по наибольшему основанию СОК, аналогово-цифровые преобразователи, сумматоры, шифраторы, блоки коррекции, коммутаторы, одновибратор, регистр, аналоговую входную шину, шину коррекции, шину управления, выходную шину «ядро числа» и выходные шины остатков по соответствующим основаниям СОК. Недостаток - ограниченная разрядность устройства.

Известно устройство (аналог) (авт.св. СССР №1372620, МКИ Н03М 1/28, БИ №5, 1988 г.), содержащее аналогово-цифровые преобразователи по модулю, сумматоры, шифраторы, блоки коррекции, счетчики, блок управления. Недостаток - ограниченная разрядность устройства.

Известно также устройство (прототип) (авт.св. СССР №1181141, МКИ Н03М 1/28, БИ №35, 1985 г.), содержащее блок определения остатка по наибольшему основанию СОК, аналогово-цифровые преобразователи, блоки коррекции, входную шину, шину коррекции, выходные шины кодов по основаниям СОК, сумматоры, шифраторы, шины кодов оснований СОК.

Недостаток прототипа - ограниченная разрядность устройства, определяющаяся разрядностью аналого-цифровых преобразователей, входящих в состав устройства. В силу несоизмеримого роста дороговизны параллельных аналого-цифровых преобразователей с увеличением разрядности их производство ограничено значением 210 уровней квантования.

Задача, на решение которой направлено заявляемое устройство, состоит в повышении точности представления формы аналогового сигнала в цифровом виде.

Технический результат выражается в возможности увеличения количества и значений оснований системы остаточных классов, в которой представлен цифровой эквивалент аналогового преобразуемого сигнала.

Технический результат достигается тем, что в аналого-цифровой преобразователь в системе остаточных классов, содержащий вход, n-1 аналого-цифровых преобразователей, n выходных шин кодов остатков в системе остаточных классов, где n - число оснований системы остаточных классов, согласно изобретению, введены n-ый аналого-цифровой преобразователь, n цифроаналоговых преобразователей, n блоков вычитания и n блоков слежения-хранения, первые входы которых объединены и являются общим входом устройства, выходы блоков слежения-хранения подключены к первым входам соответствующих блоков вычитания и входам соответствующих аналого-цифровых преобразователей, выходы которых являются соответствующими выходными шинами кодов остатков в системе остаточных классов и подключены ко входам соответствующих цифроаналоговых преобразователей, выходы которых подключены ко вторым входам соответствующих блоков вычитания, выходы i-ых блоков вычитания ( ) подключены ко вторым входам i+1-ых блоков слежения-хранения, при этом выход n-го блока вычитания подключен ко второму входу 1-го блока слежения-хранения.

) подключены ко вторым входам i+1-ых блоков слежения-хранения, при этом выход n-го блока вычитания подключен ко второму входу 1-го блока слежения-хранения.

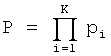

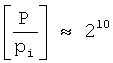

Сущность изобретения заключается в уменьшении количества уровней квантования аналогового сигнала на единичную операцию аналого-цифрового преобразования. Применение конвейерной архитектуры позволяет реализовать высокоскоростные АЦП с большой разрядностью (Уолт Кестер. Как выбрать тип АЦП для ваших приложений. - Электроника НТБ, №4/2006). Для тех же самых значений оснований СОК применение конвейерной архитектуры дает уменьшение количества уровней квантования аналогового сигнала на единичную операцию аналого-цифрового преобразования. Так в n-1 АЦП и первом АЦП блока определения остатка по наибольшему основанию СОК прототипа выполняется функция:  - целая часть от деления N на pi. При этом N∈[0, P), где

- целая часть от деления N на pi. При этом N∈[0, P), где  , К - количество оснований СОК, pi - соответствующее основание. Следовательно, количество уровней квантования, приходящихся на i-й АЦП прототипа, равняется

, К - количество оснований СОК, pi - соответствующее основание. Следовательно, количество уровней квантования, приходящихся на i-й АЦП прототипа, равняется  . При любых pi>1 и К>2 является верным выражение

. При любых pi>1 и К>2 является верным выражение  .

.

Конвейерное построение дает сокращение количества уровней квантования до pi. В таблице 1 (фиг.2) приведено количественное сравнение уровней квантования по основаниям СОК 3, 5 и 7 для элементарных АЦП в составе реализуемого устройства и элементарных АЦП прототипа, выполняющих функцию  .

.

Поскольку существует ограничение на количество уровней квантования для параллельных АЦП в составе устройства, которое составляет величину порядка 210 (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., ил., стр.649), то рассмотренный подход для АЦП в СОК позволит существенно увеличить разрядность устройства. Это можно сделать двумя путями: увеличить значения оснований и/или увеличить количество оснований. Так в прототипе для трех оснований p1=3, p2=5, р3=7 разрядность исходя из диапазона  по аналогии с позиционным представлением числа, будет находиться между 6 и 7 (26<105<27), при этом суммарное количество уровней квантования элементарных АЦП (согласно таблицы 1, фиг.2) равно не менее 74. То же количество уровней квантования в реализуемом устройстве дают, например, основания p1=19, p2=24, p3=31, при этом диапазон

по аналогии с позиционным представлением числа, будет находиться между 6 и 7 (26<105<27), при этом суммарное количество уровней квантования элементарных АЦП (согласно таблицы 1, фиг.2) равно не менее 74. То же количество уровней квантования в реализуемом устройстве дают, например, основания p1=19, p2=24, p3=31, при этом диапазон  , что по аналогии будет соответствовать разрядности между 13 и 14 (213<14136<214). Предельный для прототипа вариант, когда

, что по аналогии будет соответствовать разрядности между 13 и 14 (213<14136<214). Предельный для прототипа вариант, когда  , по трем основаниям СОК возможен уже при значениях p1=25-1=31, p2=25=32, p3=25+1=33 и ввод четвертого основания в данном случае затруднителен. Реализуемое устройство позволяет снять данное ограничение.

, по трем основаниям СОК возможен уже при значениях p1=25-1=31, p2=25=32, p3=25+1=33 и ввод четвертого основания в данном случае затруднителен. Реализуемое устройство позволяет снять данное ограничение.

В реализуемом АЦП в СОК применяются блоки слежения-хранения, которые осуществляют функцию буферизации аналогового сигнала и которые можно реализовать на основе известной схемы (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., ил., рис.3.54).

Дополнительной возможностью для тех же значений оснований при построении устройства на параллельных АЦП является сокращение аппаратных издержек (таблица 1, фиг.2). Также дополнительной возможностью является варьирование количества и значений оснований СОК, в которой работает устройство, при той же разрядности.

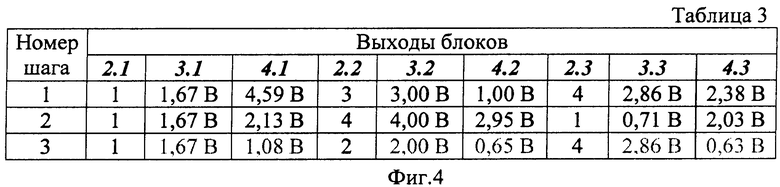

На фиг.1 представлена структурная схема АЦП в СОК, где 1.1-1.n - блоки слежения-хранения, 2.1-2.n - аналого-цифровые преобразователи, 3.1-3.n - цифроаналоговые преобразователи, 4.1-4.n - блоки вычитания, 5.1-5.n - выходные шины кодов остатков в СОК, 6 - вход.

Первые входы блоков слежения-хранения 1.1-1.n объединены и являются общим входом АЦП в СОК 6, выходы блоков слежения-хранения 1.1-1.n подключены к первым входам соответствующих блоков вычитания 4.1-4.n и входам соответствующих аналого-цифровых преобразователей 2.1-2.n, выходы которых являются соответствующими выходными шинами кодов остатков в СОК 5.1-5.n и подключены ко входам соответствующих цифроаналоговых преобразователей 3.1-3.n, выходы которых являются вторыми входами соответствующих блоков вычитания 4.1-4.n, выходы блоков вычитания 4.i ( ) подключены ко вторым входам блоков слежения-хранения 1.i+1, при этом выход блока вычитания 4.n является вторым входом блока слежения-хранения 1.1.

) подключены ко вторым входам блоков слежения-хранения 1.i+1, при этом выход блока вычитания 4.n является вторым входом блока слежения-хранения 1.1.

Работа АЦП в СОК осуществляется в течение n шагов. АЦП в СОК по n основаниям p1, p2, …, pn состоит из n блоков слежения-хранения, n АЦП, n ЦАП, n блоков вычитания, при этом количество уровней квантования АЦП 2.7-2.n и коэффициенты усиления блоков вычитания 4.1-4.n равны p1, p2, …, pn соответственно.

Первый шаг. Преобразуемое напряжение через вход 6 поступает на первый вход блоков слежения-хранения 1.1-1.n и запоминается. Далее аналоговый сигнал поступает на АЦП 2.1-2.n, где преобразуется в цифровые коды, которые поступают на соответствующие ЦАП 3.1-3.n. Данные ЦАП 3.1-3.n преобразуют коды в аналоговые сигналы, которые вычитаются блоками 4.1-4.n из входного и умножаются на коэффициенты p1, p2, …, pn соответственно. В результате на выходах блоков вычитания 4.1, 4.2, …, 4.n-1, 4.n образуются уровни сигналов, которые запоминаются блоками слежения-хранения 1.2, 1.3, …, 1.n, 1.1 соответственно.

Следующие шаги аналогичны за исключением того, что на АЦП 2.1-2.n и первые входы блоков вычитания 4.1-4.n поступают аналоговые сигналы, сохраненные в 1.1-1.n на предыдущем шаге. Таким образом, на n-ом шаге происходит оцифровка аналоговых остатков, соответствующих коду в СОК. Полученный код поступает на выходные шины 5.1-5.n.

Пример.

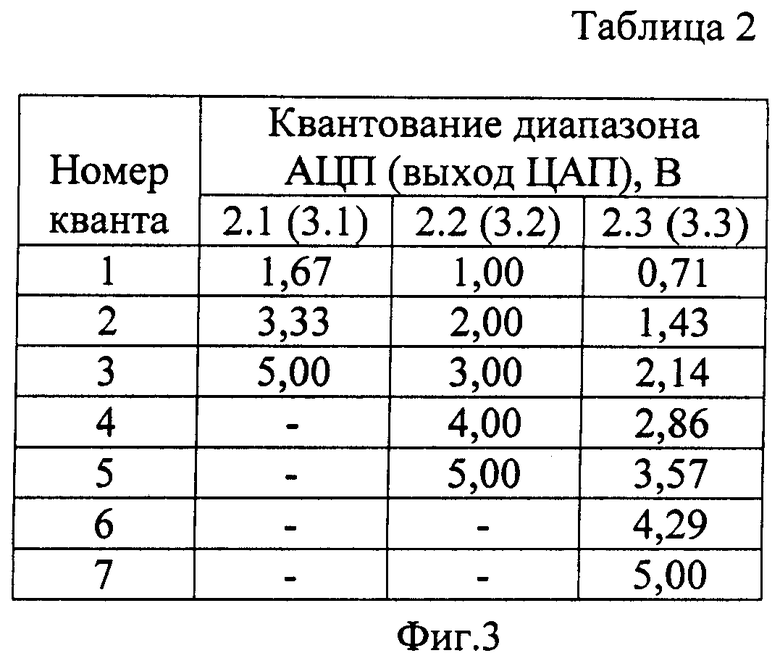

Рассмотрим устройство по трем основаниям СОК p1=3, p2=5, p3=7. Оно будет состоять из трех блоков слежения-хранения, трех АЦП, трех ЦАП, трех блоков вычитания, при этом количество уровней квантования АЦП 2.1-2.3 и коэффициенты усиления блоков вычитания 4.1-4.3 равны 3, 5 и 7 соответственно. Пусть диапазон преобразуемых АЦП 2.1-2.3 напряжений - от 0 до 5 В, т.е. E=5 В. В этом случае квантование диапазона (без смещения нуля на 1/2 младшего разряда) даст следующие значения напряжений 2.1-2.3 (таблица 2, фиг.3). Пусть преобразуемое входное напряжение Uвх.=3,2 В.

Первый шаг. Преобразуемое напряжение через вход 6 поступает на первый вход блоков слежения-хранения 1.1-1.3 и запоминается. Далее аналоговый сигнал поступает на АЦП 2.1-2.3, где преобразуется (согласно таблицы 2, фиг.3) в коды 1, 3 и 4 соответственно. Эти коды поступают на соответствующие ЦАП 3.1-3.3. ЦАП преобразуют коды в аналоговые сигналы (таблица 2, фиг.3) 1,67 В, 3,00 В и 2,86 В соответственно.

Полученные аналоговые величины вычитаются блоками 4.1-4.3 из входного и умножаются на коэффициенты 3, 5 и 7 соответственно. В результате на их выходах образуются уровни сигналов:

4.1: (3,20-1,67)·3=4,59 В,

4.2: (3,20-3,00)·5=1 В,

4.3: (3,20-2,86)·7=2,38 В,

которые запоминаются блоками слежения-хранения 1.2, 1.3 и 1.1 соответственно.

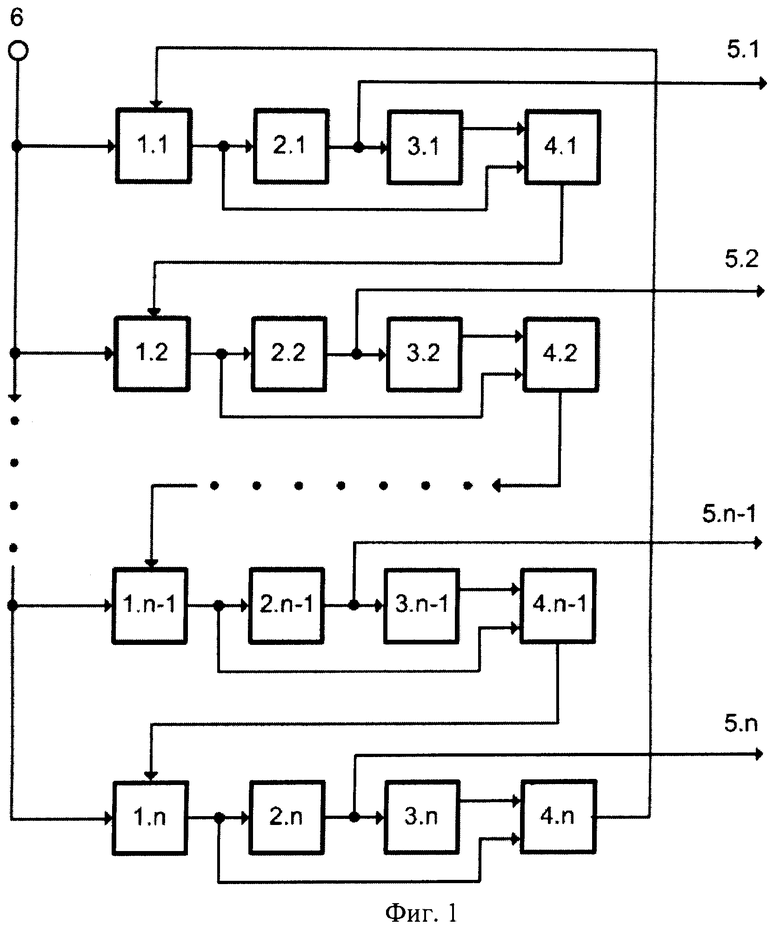

Второй и третий шаги аналогичны за исключением того, что на АЦП 2.1-2.3 и первые входы блоков вычитания 4.1-4.3 поступают аналоговые сигналы, сохраненные в 1.1-1.3 на предыдущем шаге. Значения кодов и аналоговых уровней сигнала, образующихся при работе АЦП 2.1-2.3, ЦАП 3.1-3.3 и блоков вычитания 4.1-4.3, представлены в таблице 3 (фиг.4).

Таким образом, код в СОК по основаниям p1=3, p2=5, p3=7 равен 1, 2, 4. Проверим полученный результат. Рассмотрим параллельный АЦП (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., ил., рис.9.49) (без смещения нуля на 1/2 младшего разряда), состоящего из делителя опорных напряжений, компараторов, количество которых Р=3·5·7=105, и шифратора.

Измеряемое напряжение равно 3,2 В. Получив таблицу опорных напряжений (таблица 4, фиг.5), кратных E/105, где Е=5 В, обнаруживаем, что компараторы с 1-го по 67-й установятся в «1», а все остальные в «0». Следовательно, на выходе шифратора установится код, десятичное представление которого равно 67. Целые остатки от деления числа 67 на 3, 5 и 7 соответственно равны 1, 2 и 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| АЛИАСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2589388C1 |

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1983 |

|

SU1181140A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПО МОДУЛЮ m | 2020 |

|

RU2747568C1 |

Изобретение относится к области измерительной и вычислительной техники и может быть использовано для быстрого преобразования аналоговых электрических сигналов в цифровой код в системах, функционирующих в системе остаточных классов (СОК). Техническим результатом является увеличение разрядности преобразователя. Устройство содержит блоки слежения-хранения, аналого-цифровые преобразователи, цифроаналоговые преобразователи, блоки вычитания. 5 ил.

Аналого-цифровой преобразователь в системе остаточных классов, содержащий вход, n-1 аналого-цифровых преобразователей, n выходных шин кодов остатков в системе остаточных классов, где n - число оснований системы остаточных классов, отличающийся тем, что введены n-й аналого-цифровой преобразователь, n цифроаналоговых преобразователей, n блоков вычитания и n блоков слежения-хранения, первые входы которых объединены и являются общим входом устройства, выходы блоков слежения-хранения подключены к первым входам соответствующих блоков вычитания и входам соответствующих аналого-цифровых преобразователей, выходы которых являются соответствующими выходными шинами кодов остатков в системе остаточных классов и подключены ко входам соответствующих цифроаналоговых преобразователей, выходы которых подключены к вторым входам соответствующих блоков вычитания, выходы i-х блоков вычитания

подключены ко вторым входам i+1-х блоков слежения-хранения, при этом выход n-го блока вычитания подключен ко второму входу 1-го блока слежения-хранения.

подключены ко вторым входам i+1-х блоков слежения-хранения, при этом выход n-го блока вычитания подключен ко второму входу 1-го блока слежения-хранения.

| Аналого-цифровой преобразователь в системе остаточных классов | 1983 |

|

SU1181141A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МАГНИТОДИЭЛЕКТРИКА ИЗ ПОРОШКООБРАЗНОГО МАГНИТНОГО МАТЕРИАЛА | 1945 |

|

SU69358A1 |

| Способ создания и регулирования натяга в передачах винт-гайка качения с упругой гайкой | 1983 |

|

SU1176120A1 |

| JP 1099325 A, 18.04.1989. | |||

Авторы

Даты

2011-11-10—Публикация

2010-04-12—Подача