Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления.

Известно устройство (аналог) (авт. св. СССР №1642469, МКИ G06F 11/00, Б.И. №14, 1991 г.), содержащее группу элементов ИСКЛЮЧАЩЕЕ ИЛИ, сумматор, два регистра сумматор по модулю К, формирователь дополнения вычетов, блок сравнения. Недостаток устройства - большое количество используемого оборудования.

Известно также устройство (аналог) (авт. св. СССР №1642470, МКИ G06F 11/00, Б.И. №14, 1991 г.), содержащее блок сумматоров по модулю два, два регистра, формирователь контрольного бита, элемент ИСКЛЮЧАЕЩЕЕ ИЛИ, элемент И, элемент ИЛИ и триггер. Недостаток устройства - большое количества используемого оборудования.

Наиболее близким по технической сущности (прототипом к предполагаемому изобретению) является устройство (авт. св. СССР №1608666, МКИ G06F 11/00, Б.И. №43, 1990 г.), содержащее блок свертки по модулю первый и второй блоки буферной памяти, блок контроля по модулю, блок сравнения, блок выдачи признака результата, блок постоянной памяти, блок оперативной памяти, первый и второй триггеры, абонент, первый и второй элементы ИЛИ, процессор, сумматор и блок задания смещения. Недостаток прототипа - большое количество используемого оборудования ввиду того, что вычисление и контроль проводимой операции производится различными узлами устройства.

Задача, на решение которой направлено заявленное устройство, состоит в повышении надежности перспективных образцов вычислительной техники.

Технический результат выражается в уменьшении количества используемого оборудования.

Технический результат достигается тем, что в устройство, содержащее первый блок сравнения, отличающееся тем, что в него введены (n-2)блока сравнения, где n - число вычислительных трактов ЭВМ, две группы мультиплексоров, группа блоков сложения чисел по модулю, группа демультиплексоров, группа регистров, три группы блоков элементов И, три группы блоков свертки по модулю, группа блоков сложения с константой по модулю, блок элементов И, группа блоков элементов ИЛИ и группа элементов НЕ, причем j-e входы первого операнда (j=1, n-1) соединены с первыми информационными входами соответствующих мультиплексоров первой группы, входы которых соединены с первыми входами соответствующих блоков сложения чисел по модулю группы, где операнды и результат операции представлены в модулярной системе счисления, а j-e входы второго операнда соединены с первыми информационными входами соответствующих мультиплексов второй группы, выходы которых соединены со вторыми входами соответствующих блоков сложения чисел по модулю группы, выходы которых соединены с информационными входами соответствующих демультиплексоров группы, управляющие входы которых соединены с управляющими входами мультиплексоров первой и второй групп и со входами управления устройства, первые выходы демультиплексоров группы соединены со входами соответствующих регистров группы, а их выходы соединены с первыми входами соответствующих блоков элементов И третьей группы, выходы которых являются j-ми выходами устройства, j-е входы первого и второго операндов соединены соответственно с первым и вторым входами n-го блока сложения по модулю группы, i-е входы первого и второго операндов

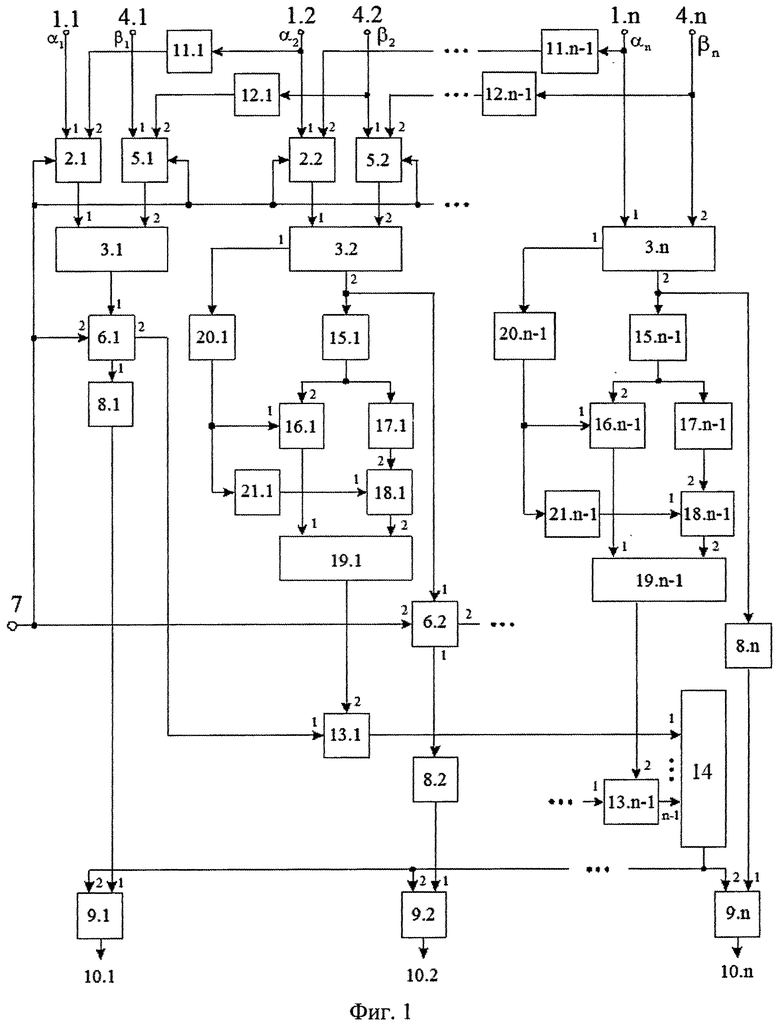

На фиг.1 представлена структурная схема предлагаемого устройства.

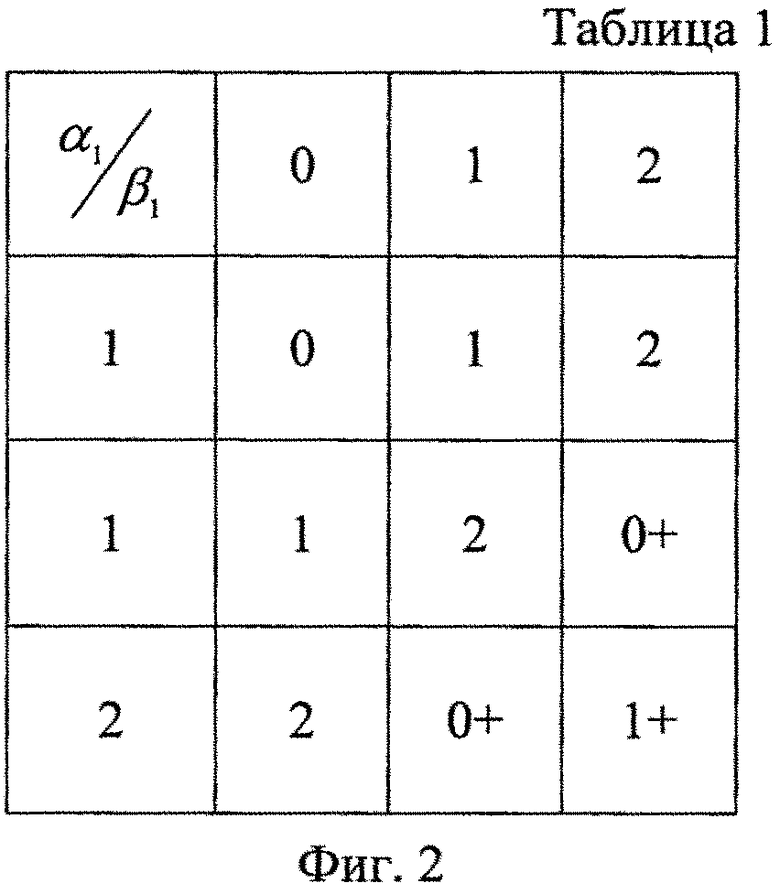

На фиг.2 приведена таблица 1 результатов операции (α1+β1)mod3.

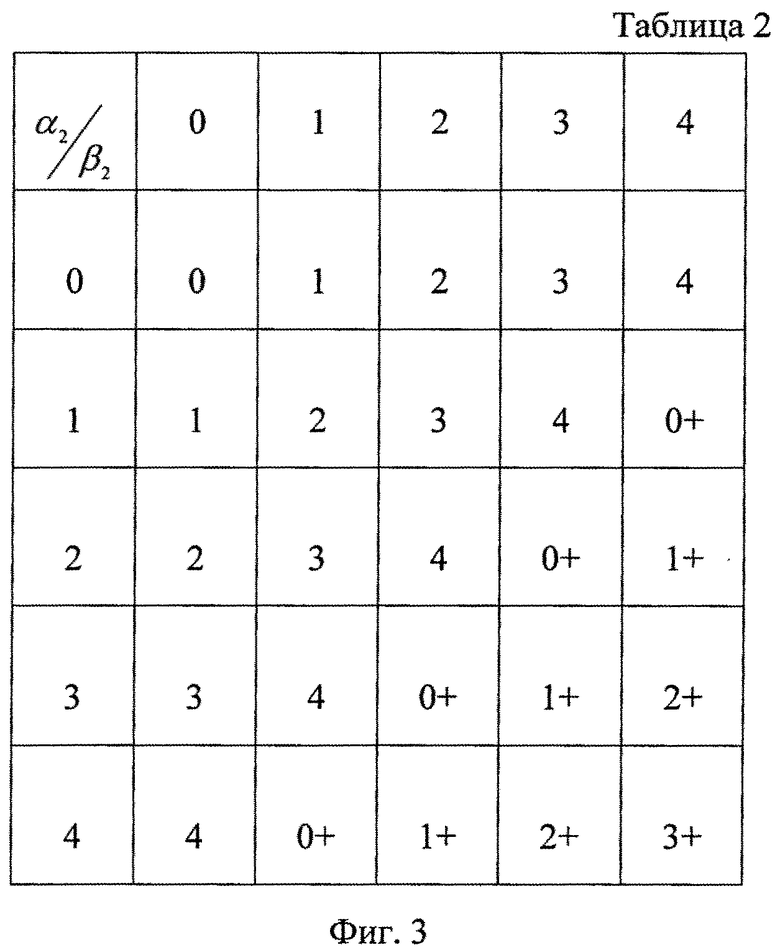

На фиг.3 приведена таблица 2 результатов операции (α2+β2)mod5.

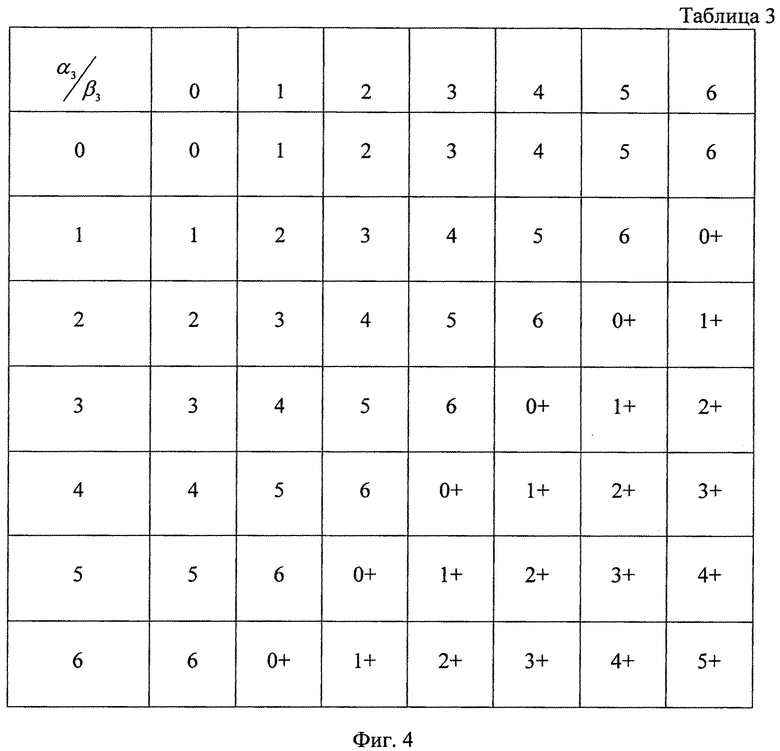

На фиг.4 приведена таблица 3 результатов операции (α3+β3)mod7.

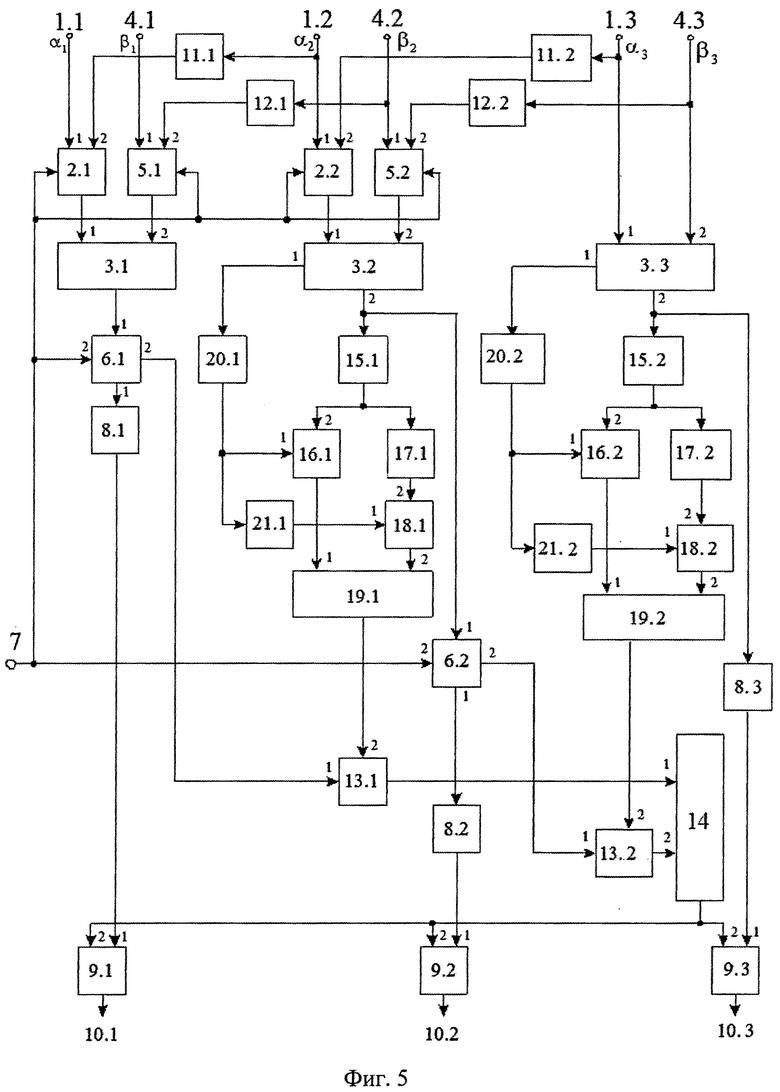

На фиг.5 представлена структурная схема предлагаемого устройства для случая трех модулей (оснований) модулярной системы счисления, т.е. n=3.

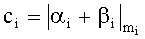

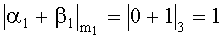

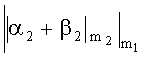

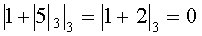

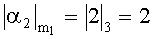

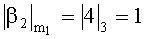

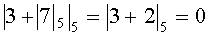

Сущность изобретения состоит в представлении операндов остатками от деления на заданные основания модулярной системы счисления (МСС) с последующим проведением операции по каждому остатку отдельно. Однако контроль работы устройства по каждому основанию производится теми же узлами, которые используются и для вычислений. Рассмотрим МСС, состоящую из трех оснований m1=3, m2=5, m3=7. В этом случае диапазон представления чисел равен m1×m2×m3×=105. Для реализации операции модульного сложения табличным методом требуется три таблицы по соответствующим основаниям (модулям) (табл.1 - табл.3 (фиг.2 - фиг.4)). Однако для их аппаратного выполнения необходимо оборудование, которое растет по квадратичному закону относительно величины модуля МСС. Следовательно, целесообразно использовать одни узлы устройства как для проведения операции, так и ее контроля, который проводиться по младшему модулю. Схематически таблицы выполнятся на двухвходовых элементах И, а клетки таблиц, отмеченные знаком «+», объединяются в выходы переполнения. Наибольшие аппаратурные затраты при реализации данного устройства приходятся на таблицы. В данном случае операция сложения выполняется в вычислительных трактах (ВТ) по модулям m1=3, m2=5, m3=7. Затем производится контроль ВТ2 (m2=5) по модулю m1=3, а ВТ3 (m3=7) по модулю m2=5. Таким образом, все вычислительные тракты, кроме первого, контролируются. В случае успешного завершения контроля результат операции поступает на выход устройства. Возможно дальнейшее совершенствование, когда старший модуль проверяется несколькими младшими. Например, ВТ3 контролируется по модулям m1=3 и m2=5. Данный подход позволит существенно увеличить глубину контроля и повысит надежность вычислений. Ввиду того что данная вычислительная схема обладает свойством самопроверяемости, то при этом повышается ее отказоустойчивость.

Представленная на фиг.1 структурная схема предлагаемого устройства содержит: 11÷1n - входы первого операнда, 2 - мультиплексоры первой группы, 3 - группа блоков сложения чисел по модулю, 41÷4n - выходы второго операнда, 5 - мультиплексоры второй группы, 6 - группа демультиплексоров, 7 - вход управления устройства, 8 - группа регистров, 9 - третья группа блоков элементов И, 101÷10n - выходы устройства, 11 - первая группа блоков свертки по модулю, 12 - вторая группа блоков свертки по модулю, 13 - группа блоков сравнения, 14 - блок элементов И, 15 - третья группа блоков свертки по модулю, 16 - первая группа блоков элементов И, 17 - группа блоков сложения с константой по модулю, 18 - вторая группа блоков элементов И, 19 - группа блоков элементов ИЛИ, 20 - группа триггеров, 21 - группа элементов НЕ.

Представленная на фиг.5 структурная схема предлагаемого устройства для случая трех модулей содержит те же узлы, как и на фиг.1.

Входы первого операнда 11÷1n-1 соединены с первыми информационными входами соответствующих мультиплексоров первой 2 группы, выходы которых соединены с первыми входами соответствующих блоков сложения чисел по модулю группы 3, где операнда и результат операции представлены в модулярной системе счисления, а входы второго операнда 41÷4n-1 соединены с первыми информационными входами соответствующих мультиплексоров второй 5 группы, выходы которых соединены со вторыми входами соответствующих блоков сложения чисел по модулю группа 3, выходы которых соединены с информационными входами соответствующих демультиплексоров группы 6, управляющие входы которых соединены с управляющими входами мультиплексоров первой 2 и второй 5 групп и со входом управления 7 устройства, первые выходы демультиплексоров группы 6 соединены со входами соответствующих регистров 8 группы, а их выходы соединены с первыми входами соответствующих блоков элементов И третьей 9 группы, выходы которых являются выходами устройства 101÷10n-1, входы первого 1n и второго 4n операндов соединены соответственно с первым и вторым входами n-го блока сложения по модулю группы 3, i-e входы первого 1i и второго 4i операндов, где

Рассмотрим работу устройства. На вход 7 управления устройством поступает первый код, который передается на управляющие входы мультиплексоров первой 2 и второй 5 групп, а также на управляющие входы группы 6 демультиплексоров. На входы 11÷1n первого операнда поступает число A=(α1, α2, …, αn), представленное в МСС по основаниям m1, m2, …, mn. На входы 41÷4n второго операнда поступает число β=(β1, β2, …, βn). Отметим, что в данном случаи первые информационные входы мультиплексоров первой 2 и второй 5 групп соединены с их выходами. Также информационные входы демультиплексоров 6 группы соединены с первыми их выходами.

Следовательно, в блоках сложения 3 чисел по модулю группы производится данная операция, результат которой помещается в группу 8 регистров. Отсутствие превышения соответствующего модуля m1 при проведении модулярного сложения фиксируется появлением единицы на выходе соответствующего триггера 20 группы путем подачи сигнала с инверсного выхода переполнения данного блока сложения 3 чисел по модулю группы на вход триггера. Затем на вход 7 управления устройством поступает второй код, который поступает на управляющие входы мультиплексоров первой 2 и второй 5 групп и группы 6 демультиплексоров. При этом вторые информационные входы мультиплексоров первой 2 и второй 5 групп подключатся к их выходам, а информационные входы демультиплексоров 6 группы подключаются к их вторым выходам. Операнды

В противном случае производится сложение

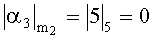

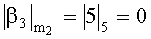

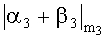

Пример. Пусть A=12, B=19. При выборе оснований m1=3, m2=3, m3=7 диапазон МСС равен m1·m2·m3=105. Операнды A и B при этом равны А=12(α1,α2,α3)=(0,2,5); В=19=(β1,β2,β3)=(1,4,5); а результат операции A+B=С=(с1,с2,с3=31=(1,1,3). В этом случае блоки сложения чисел 3 по модулю группы реализуют таблицы 1÷3 (фиг.2 - фиг.4). После поступления первого кода на вход 7 управления устройства первые информационные входы мультиплексоров первой 2 и второй 5 групп соединены с их выходами, а информационные входы демультиплексоров 6 группы соединены с их первыми выходами. Остаток чисел по модулю 3 равный α1=0 и β1=1 поступает соответственно на первый и второй входы первого блока сложения 3 чисел по модулю группы. Результат операции

Затем поступает второй код на вход 7 управления устройством, который передается на управляющие входы мультиплексоров первой 2 и второй 5 групп и группы 6 демультиплексоров, подготавливая необходимые коммутации для проведения контроля вычислений.

Результат операции

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭВМ | 2011 |

|

RU2458384C1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для вычисления элементарных функций в модулярной системе счисления | 1985 |

|

SU1291977A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ | 1999 |

|

RU2157560C1 |

| Устройство вычисления модулярного произведения Монтгомери | 2017 |

|

RU2652450C1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, функционирующих в модулярной системе счисления. Техническим результатом является уменьшение количества используемого оборудования за счет использования блоков сложения чисел по модулю для проведения вычислений и контроля операции сложения по младшему модулю. Устройство содержит: блоки сравнения, две группы мультиплексоров, группу блоков сложения чисел по модулю, группу демультиплексоров, группу регистров, три группы блоков элементов И, группу блоков сложения с константой по модулю, три группы блоков свертки по модулю, группу блоков элементов ИЛИ, блок элементов И, группу элементов НЕ, группу триггеров и связи между ними. 5 ил.

Устройство для контроля ЭВМ, содержащее первый блок сравнения, отличающееся тем, что в него введены (n-2)блока сравнения, где n - число вычислительных трактов ЭВМ, две группы мультиплексоров, группа блоков сложения чисел по модулю, группа демультиплексоров, группа регистров, три группы блоков элементов И, три группы блоков свертки по модулю, группа блоков сложения с константой по модулю, блок элементов И, группа блоков элементов ИЛИ и группа элементов НЕ, причем j-е входы первого операнда (j=1, n-1) соединены с первыми информационными входами соответствующих мультиплексоров первой группы, входы которых соединены с первыми входами соответствующих блоков сложения чисел по модулю группы, где операнды и результат операции представлены в модулярной системе счисления, a j-e входы второго операнда соединены с первыми информационными входами соответствующих мультиплексоровв второй группы, выходы которых соединены со вторыми входами соответствующих блоков сложения чисел по модулю группы, выходы которых соединены с информационными входами соответствующих демультиплексоров группы, управляющие входы которых соединены с управляющими входами мультиплексоров первой и второй групп и со входами управления устройства, первые выходы демультиплексоров группы соединены со входами соответствующих регистров группы, а их выходы соединены с первыми входами соответствующих блоков элементов И третьей группы, выходы которых являются j-ми выходами устройства, n-е входы первого и второго операндов соединены соответственно с первым и вторым входами n-го блока сложения по модулю группы, i-е входы первого и второго операндов

| Устройство для контроля ЭВМ | 1987 |

|

SU1608666A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| EP 1980943 A1, 15.10.2008 | |||

Авторы

Даты

2015-04-10—Публикация

2014-01-09—Подача