Изобретение относится к области вычислительной техники и может быть использована в блоках статических ОЗУ.

Воздействие одиночной ядерной частицы на ячейку памяти комплементарной металл-оксид-полупроводниковой структуры (далее КМОП) приводит к сбою ее состояния. Наиболее распространенным вариантом сбоеустойчивой статической КМОП ячейки памяти в настоящее время является ячейка памяти с дублированием хранения логического состояния (ячейка DICE).

Наиболее близкой по технической сущности и достигаемому результату является ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, состоящая из пар NМОП и PМОП транзисторов, соединенных между собой, с шиной источника питания, и линиями выборки и данных и размещенных на кристалле интегральной микросхемы (US Patent №5570313, кл. G11C 11/34, опублик. 1996).

Недостатком описанной ячейки является недостаточная помехоустойчивость и сниженная радиационная стойкость транзисторов ячеек памяти к воздействию одиночных ядерных частиц.

Техническим результатом, ожидаемым от использования изобретения, является повышение сбоеустойчивости к воздействию одиночных ядерных частиц без избыточного увеличения площади, занимаемой одной ячейкой памяти на кристалле в составе интегрального КМОП ОЗУ.

Указанный технический результат достигается тем, что в ячейке памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, состоящей из пар NМОП и РМОП транзисторов, соединенных между собой, с шиной источника питания, и линиями выборки и линиями данных и размещенных на кристалле интегральной микросхемы, согласно изобретению, транзисторы объединены в две группы, каждая из которых содержит одну пару NМОП и РМОП транзисторов с объединенными стоками, один NМОП транзистор и один РМОП транзистор, соединенные своими затворами с объединенными стоками этой пары, причем эти две группы транзисторов размещены на кристалле интегральной микросхемы одна от другой на расстоянии равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового.

А так же тем, что, группы транзисторов размещены на кристалле интегральной микросхемы одна за другой, при этом i-я и (i+K)-я группы транзисторов образуют i-ю ячейку памяти, где i=1, 2, …, K.

Указанная совокупность признаков позволяет снизить вероятность сбоя состояния ячейки памяти при воздействии одиночной ядерной частицы при одновременном снижении площади, занимаемой ячейкой памяти на кристалле.

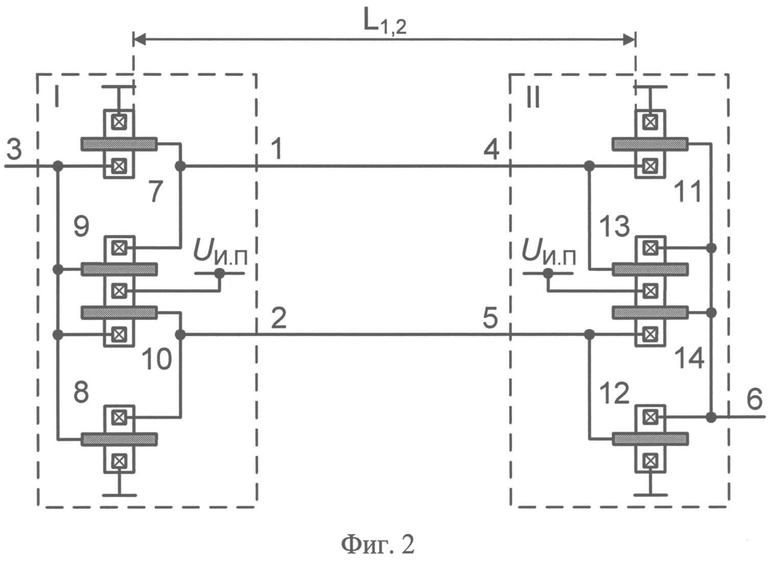

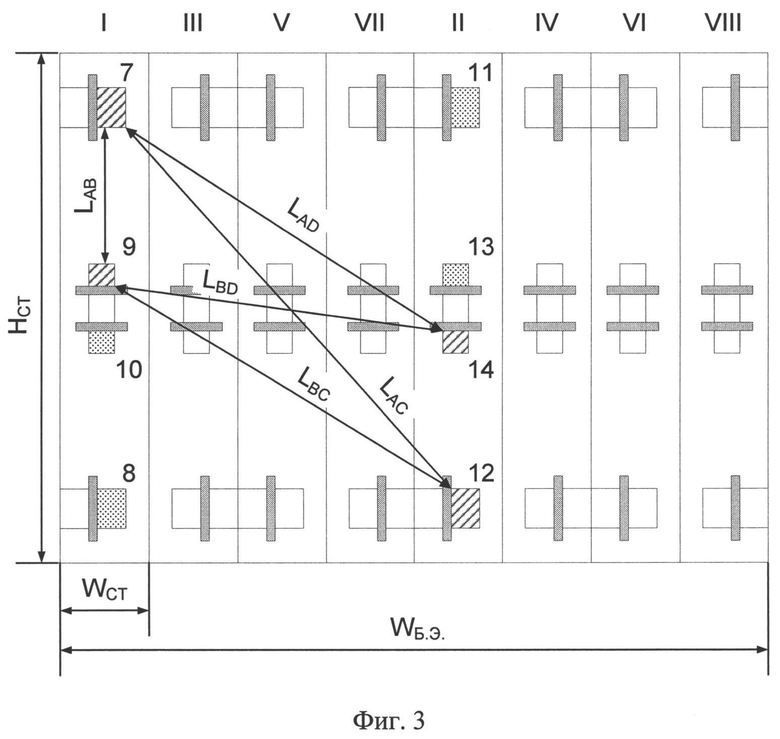

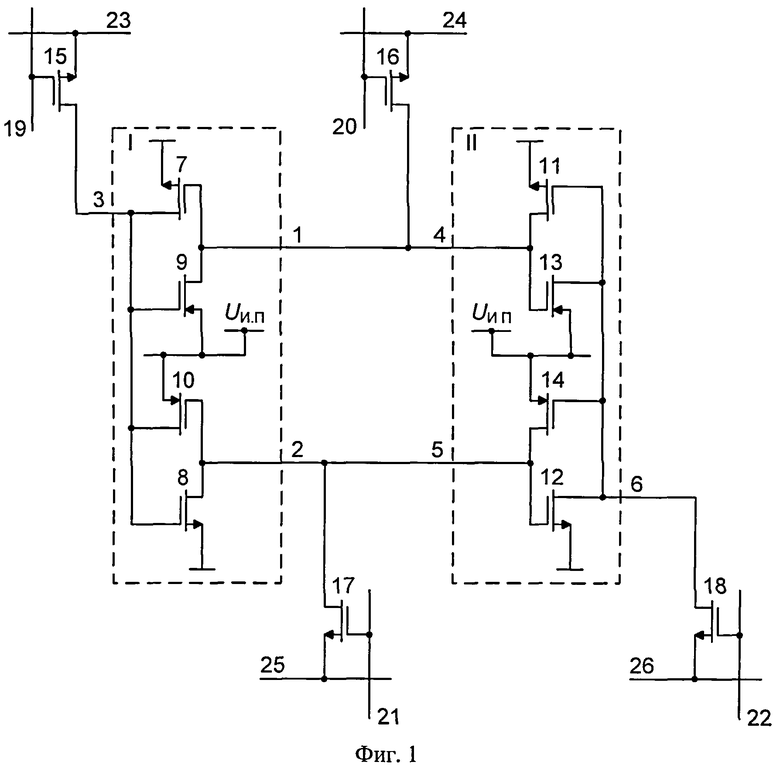

Изобретение поясняется чертежами, где на фиг.1 изображена электрическая принципиальная схема ячейки памяти, на фиг.2 изображена схема взаимного расположения групп транзисторов одной ячейки памяти, на фиг.3 изображена схема взаимного расположения восьми групп транзисторов в базовом элементе ОЗУ, содержащем четыре ячейки памяти.

Ячейка памяти содержит две группы транзисторов I и II, первая группа I имеет три вывода 1, 2, 3, вторая группа II имеет три вывода 4, 5, 6. В состав первой группы I входят два NМОП транзистора 7, 8 и два РМОП транзистора 9, 10, в состав второй группы II входят два NМОП транзистора 11, 12 и два РМОП транзистора 13, 14. Кроме того, ячейка памяти содержит четыре проходных ключа 15, 16, 17, 18, затворы проходных ключей 15, 16, 17, 18 соединены с соответствующими линиями 19, 20, 21, 22 выборки. Один из выводов проходных ключей 15, 16, 17, 18 соединен соответственно с выводом 3, 4, 2, 6 групп I и II транзисторов; другой вывод проходных ключей 15, 16, 17, 18 соединен с одной из четырех битовых линий 23, 24, 25, 26 ячейки памяти.

Расстояние между двумя группами транзисторов должно быть равным или больше порогового и определяется из выражения:

L1,2≥LПОР={(πQТР2SСБ2Dn,p//(8ΔlTP))(RВЫХ.ОТКРСУЗЛА·λНλВЫХ/QПЕР)}1/3×tgθ,

где QТР2 - заряд, образованный на отрезке трека ΔlTP, наиболее близкого ко второй группе II транзисторов;

SСБ2=ΔlCБ2×wCБ2 - площадь сбора заряда во второй группе II транзисторов;

ΔlСБ2 - размер области сбора заряда в одном направлении с направлением трека, а

wСБ2 - в поперечном направлении;

Dn,p - коэффициент амбиполярной диффузии носителей заряда;

ΔlTP - длина отрезка трека, из области которого диффундируют неравновесные носители во вторую группу II транзисторов;

RВЫХ.ОТКР - выходное сопротивление (усредненное значение) открытого МОП транзистора, соединенного его собственным стоком со стоком транзистора, собирающего заряд во второй группе II транзисторов;

QПЕР - заряд переключения транзистора второй группы II транзисторов ячейки;

θ - угол наклона трека частицы относительно нормали к поверхности кристалла;

λН=(τН/τСП)a, a=τН/(τСП-τН).

Постоянные времени нарастания τН и спада τСП импульса фототока, образованного диффузией заряда от трека частицы, зависят от постоянной времени диффузии неравновесных носителей τD из области трека до собирающей заряд области второй группы II транзисторов ячейки. Их связь определяется из следующего выражения:

τСП=τD=4r2/(π2Dn,p) и τН=τСП/9,

где Dn,p - коэффициент амбиполярной диффузии носителей заряда.

Коэффициент λВЫХ определяется как λВЫХ=(τВЫХ/τСП)a, а=τВЫХ/(τСП-τВЫХ), где τВЫХ=RВЫХ.ОТКР.2×СУЗЛА - постоянная времени перезаряда узла ячейки; СУЗЛА - емкость узла, заряд QПЕР на которой образует импульс помехи с амплитудой, переключающей ячейку памяти.

Заряд QТР2 следует из выражения:

QTP2=q×LET×ρSi×ΔlTp/Epn,

где LET - линейные потери энергии частицей;

q - заряд электрона;

ΔlTP - длина отрезка трека, из области которого диффундируют неравновесные носители;

ρSi - плотность кремния;

Ер,n - энергия образования одной электронно-дырочной пары.

Описанное устройство работает следующим образом.

Запись данных в ячейку памяти осуществляется в четыре узла, которыми являются стоки транзисторов 7 и 12 (выводы 3 и 6) и стоки транзисторов 8 и 11 (выводы 2 и 4). Запись и считывание производится через проходные ключи 15, 16, 17, 18.

Ячейка памяти может работать в одном из трех режимов: хранение, запись и чтение.

В режиме хранения на всех линиях 19, 20, 21, 22 выборки устанавливают неактивный уровень, что поддерживает все проходные ключи 15, 16, 17, 18 в закрытом состоянии. На выводах 3, 4, 5, 6 ячейки памяти хранятся уровни сигналов, соответствующих записанным данным.

При записи на битовые линии 23, 24, 25, 26 подают записываемые данные в дифференциальной форме. Установкой активного уровня на линиях 19, 20, 21, 22 выборки открывают проходные ключи 15, 16, 17, 18, пропуская записываемые данные (сигналы) на выводы 3, 4, 5, 6 ячейки памяти.

При чтении на линиях 19, 20, 21, 22 выборки устанавливают активный уровень. Проходные ключи 15, 16, 17, 18 открываются, позволяя считывать хранимые сигналы (данные) с выводов 3, 4, 5, 6 ячейки памяти на битовые линии 23, 24, 25, 26.

При воздействии на ячейку памяти одиночной ядерной частицы, когда трек частицы направлен от запертого транзистора одной группы I к запертому транзистору другой группы II, происходит образование вдоль трека частицы неравновесных носителей заряда, которые диффундируют к транзисторам, где выводятся в виде фототоков через стоковые электроды запертых транзисторов и перезаряжают емкости этих узлов, вызывая импульсы напряжения помехи, которые могут произвести сбой состояния ячейки памяти при превышении порога переключения.

Критичным для оценки стойкости ячейки памяти является сбой состояния в режиме хранения данных. Сбой логического состояния ячейки может произойти при воздействии частицы одновременно на два МОП транзистора ячейки памяти, находящихся в запертом состоянии, исключая воздействия на следующие пары транзисторов 7 и 9, 8 и 10, 11 и 13, 12 и 14 в их запертом состоянии, при котором происходит размыкание обратной связи в триггере ячейки памяти, что и сохраняет исходное логическое состояние ячейки памяти.

Сбой исходного состояния ячейки памяти возможен только при одновременном воздействии одиночной частицы на пару запертых транзисторов, один из которых относится к группе I транзисторов, а второй к группе II транзисторов, например, в одном из двух логических состояний ячейки памяти это пары транзисторов 7 и 12, 7 и 14, 9 и 12, 9 и 14.

Пример реализации изобретения

Устройство по изобретению реализовано в виде накопителя статического ОЗУ в составе КМОП СБИС микропроцессорной системы по проектной норме 65 нм. Накопитель содержит 32×64 предложенных ячеек памяти. Эскизное изображение конструкции одной ячейки памяти без проходных ключей 15, 16, 17, 18 приведено на фиг.2. Для достижения технического результата - повышения сбоеустойчивости ячейки памяти при воздействии одиночных ядерных частиц группы I и II транзисторов ячейки памяти (см. фиг.2) разнесены на расстояние L1,2=2,31 мкм.

Основой структуры накопителя статического ОЗУ на основе предложенных ячеек памяти является базовый элемент из четырех ячеек памяти, каждая из которых состоит из двух групп транзисторов (всего восемь групп транзисторов I-VIII), которые чередуются с группами транзисторов других ячеек в блоке памяти. Упрощенное изображение базового элемента накопителя приведено на фиг.3, где для обозначения групп транзисторов использовано обозначение из цифр I-VIII, нечетные цифры соответствуют первым группам транзисторов в ячейке, а четные - вторым группам транзисторов данной ячейки. Расположение транзисторов первой ячейки на фиг.3 соответствует расположению транзисторов в группах I и II на фиг.2. Расстояния между чувствительными парами обратно смещенных pn переходов сток-подложка транзисторов, находящихся при обратном смещении в одном из логических состояний ячейки, отмечены на фиг.3 обозначениями LAC, LAD, LBD, LBC, LAB. В другом логическом состоянии ячейки имеется такой же набор пар стоковых областей, отмеченных точечными метками на фиг.3, с такими же расстояниями между парами запертых транзисторов в другом логическом состоянии ячейки.

В таблице 1 приведены расстояния между стоковыми областями транзисторов, одновременно находящихся в запертом состоянии, для ячейки памяти в составе базового элемента ОЗУ из 4-х ячеек по проектной норме КМОП 65 нм, использованного в накопителе ОЗУ микросхемы.

Расстояние между транзисторами, одновременно находящимися в запертом состоянии в одной общей группе транзисторов LAB (см. фиг.2 и 3), не влияет на сбоеустойчивость ячейки памяти, поскольку одновременное воздействие частицы на эти транзисторы приводит к размыканию цепи обратной связи в ячейке памяти, это сохраняет исходное состояние ячейки, и хранящиеся данные остаются без изменения.

Сбоеустойчивость ячейки памяти при воздействии одиночных ядерных частиц обусловлена разделением транзисторов ячейки памяти на две группы и разнесением их на кристалле микросхемы на расстояние, больше или равном пороговому расстоянию, для исключения одновременного воздействия одиночной ядерной частицы на обе группы I и II транзисторов с уровнем больше порогового.

Сбой ячейки памяти при одновременном воздействии частицы на два обратно смещенных транзистора из разных групп I и II, например 7 и 14, происходит, когда на каждый из этих транзисторов выводятся заряды больше порогового значения переключения для данного транзистора QПОР (в диапазоне значений, например, QПОР=0,5-1,5 фКл для ячеек памяти по проектной норме КМОП 65 нм и QПОР=0,2-0,5 фКл для ячеек памяти по проектной норме КМОП 28 нм). Если же запертым транзистором в группе II от импульса фототока собирается заряд QСБ, меньше порогового заряда QСБ<QПОР, то независимо от значения заряда, собранного другим транзистором в группе I, сбоя ячейки памяти нет. Критичными при оценке сбоеустойчивости ячеек памяти являются воздействия частицы, когда ее трек проходит под малым углом к поверхности полупроводникового кристалла, что соответствует углам наклона трека частицы относительно нормали к поверхности кристалла θ=75°-60°. Наиболее жестким случаем оценки сбоеустойчивости является случай, когда трек частицы проходит в непосредственной близости или просто через область обратно смещенного pn перехода сток-подложка одного из запертых транзисторов в паре, например транзистора 7 из первой группы I, а на второй подвергнутый воздействию транзистор, например на транзистор 14 из второй группы II, действует заряд неосновных носителей, диффундирующих к нему от ближайшей к нему области трека частицы. Чтобы сбой ячейки памяти не произошел, расстояние L1,2 между парами МОП транзисторов из двух групп I и II должно быть равно или больше порогового значения LПОР.

В таблице 2 приведены пороговые значения расстояния LПОР между транзисторами двух групп I и II предложенной ячейки памяти по проектной норме КМОП 65 нм, обеспечивающие сбоеустойчивость к воздействию одиночных ядерных частиц с линейными потерями 40 и 60 МэВ·см2/мг для углов падения одиночной частицы θ=60° и 75° в зависимости от параметров транзисторов: IC.НАС=67-460 мкА, - RВЫХ.ОТКР=0.95-7.3 кОм при СУЗЛА=3 фФ. Чем выше потери энергии частицей, тем больше пороговое расстояние между чувствительными транзисторами групп I и II.

Моделирование показало, что предложенная ячейка памяти в составе КМОП ОЗУ на основе базового элемента из четырех ячеек памяти по проектной норме КМОП 65 нм обеспечит бессбойное хранение данных при воздействии одиночных частиц со значениями линейных потерь энергии LET до 60 МэВ×см2/мг при углах трека относительно нормали к поверхности кристалла микросхемы до 60°, поскольку расстояния между запертыми транзисторами двух групп I и II в обоих состояниях ячейки памяти в режиме хранения данных больше порогового значения L1,2>LПОР=2,31 мкм (см. данные в таблице 1 и таблице 2).

Изобретение относится к вычислительной технике. Технический результат заключается в повышении сбоеустойчивости к воздействию одиночных ядерных частиц без избыточного увеличения площади, занимаемой одной ячейкой памяти на кристалле в составе интегрального КМОП ОЗУ. Ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ состоит из пар NMOП и РМОП транзисторов, соединенных между собой, с шиной источника питания и линиями выборки и линиями данных и размещенных на кристалле интегральной микросхемы, причем транзисторы объединены в две группы, каждая из которых содержит одну пару NMOП и РМОП транзисторов с объединенными стоками, один NMOП транзистор и один РМОП транзистор, соединенные своими затворами с объединенными стоками этой пары, причем эти две группы транзисторов размещены на кристалле интегральной микросхемы одна от другой на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового. 1 з.п. ф-лы, 3 ил., 2 табл.

1. Ячейка памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, состоящая из пар NMOП и РМОП транзисторов, соединенных между собой, с шиной источника питания и линиями выборки и линиями данных и размещенных на кристалле интегральной микросхемы, отличающаяся тем, что транзисторы объединены в две группы, каждая из которых содержит одну пару NMOП и РМОП транзисторов с объединенными стоками, один NMOП транзистор и один РМОП транзистор, соединенные своими затворами с объединенными стоками этой пары, причем эти две группы транзисторов размещены на кристалле интегральной микросхемы одна от другой на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового.

2. Ячейка памяти по п.1, отличающаяся тем, что группы транзисторов размещены на кристалле интегральной микросхемы одна за другой, при этом i-я и (i+К)-я группы транзисторов образуют i-ю ячейку памяти, где i=1, 2,…, К.

| US 8014184 B1, 06.09.2011 | |||

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| US 6744661 B1, 01.06.2004 | |||

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2015-06-27—Публикация

2013-09-26—Подача