Изобретение относится к области вычислительной техники и может быть использовано в статических ОЗУ с повышенной надежностью. Воздействие одиночной ядерной частицы на ячейку памяти комплементарной металл-оксид-полупроводниковой структуры (далее КМОП) приводит к ее переходу в неравновесное (нестационарное) состояние, а при воздействии, превышающем порог переключения, к сбою исходного ее состояния и потере хранимых данных.

Известны наиболее распространенные варианты статической оперативной КМОП памяти, ими являются блоки памяти на основе 6-транзисторных ячеек памяти и считывающих усилителей (Патент US №8 773 924 В2, кл. G11C 7/12, опублик. Jul. 8. 2014; Патент US №8 559 249 В1, кл. G11C 7/00, опублик. Oct. 15. 2013) и блоки памяти с повышенной надежностью хранения данных на основе ячеек памяти DICE (DuallnterlockedStorageCell) с дублированием хранения логического состояния и считывающих усилителей (Патент US №2010/0 264 953 А1, кл. G06F 17/50, опублик. Oct. 21. 2010; Статья: Single-Event Performance and Layout Optimization of Flip-Flops in 28-nm Bulk Technology // IEEE Transactions on Nuclear Science, 2013, Vol. 60, №4, p.p. 2782-2788).

Недостатком описанных выше технических решений является недостаточная надежность хранения данных при воздействии одиночных ядерных частиц. Наиболее близким по технической сущности и достигаемому результату является блок памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, состоящий из ячеек памяти из двух групп транзисторов каждая, соединенных через проходные ключи с четырьмя битовыми линиями данных, и двух считывающих усилителей, первый и второй входы первого считывающего усилителя соединены с первой и второй битовыми линиями данных, первый и второй входы второго считывающего усилителя соединены с третьей и четвертой битовыми линиями данных (Патент US №8 605 516 В2, кл. G11C 11/34, опублик. Dec. 10. 2013). Недостатком описанного блока памяти является невозможность надежного чтения данных из ячейки памяти в режиме неравновесного (нестационарного) состояния ячейки, вызванного воздействием одиночной ядерной частицы. Задачей настоящего изобретения является обеспечение надежного чтения данных в блоке памяти на основе ячеек памяти с повышенной надежностью хранения данных.

Техническим результатом, ожидаемым от использования изобретения, является повышение надежности чтения данных из ячейки в режиме, когда ячейка памяти на основе двух групп транзисторов временно находится в неравновесном (нестационарном) состоянии, вызванном воздействием одиночной ядерной частицы.

Указанный технический результат достигается тем, что блок памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, включающий выходную шину блока памяти, ячейки памяти, состоящие из двух групп транзисторов каждая, соединенных через проходные ключи с четырьмя битовыми линиями данных, и двух считывающих усилителей, первый и второй входы первого считывающего усилителя соединены с первой и второй битовыми линиями данных, первый и второй входы второго считывающего усилителя соединены с третьей и четвертой битовыми линиями данных, согласно изобретению блок памяти снабжен первым и вторым дополнительными транзисторами и логическим элементом ИЛИ-НЕ и имеет линию смещения с напряжением на ней больше порогового значения, при этом считывающие усилители имеют отражатели тока на парах транзисторов со структурой металл-оксид-полупроводник и каналом дырочной проводимости, причем входы логического элемента ИЛИ-НЕ соединены с выходами первого и второго считывающих усилителей, с которыми соединены, соответственно, стоки первого и второго дополнительных транзисторов, затворы которых соединены с линией смещения с напряжением на ней больше порогового значения, а выход элемента ИЛИ-НЕ соединен с выходной шиной блока памяти. Указанная совокупность признаков позволяет повысить надежность чтения данных из ячейки при воздействии одиночной ядерной частицы в режиме, когда ячейки памяти на основе двух групп транзисторов находятся в неравновесном (нестационарном состоянии).

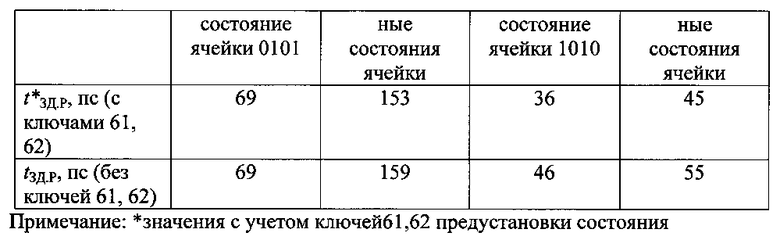

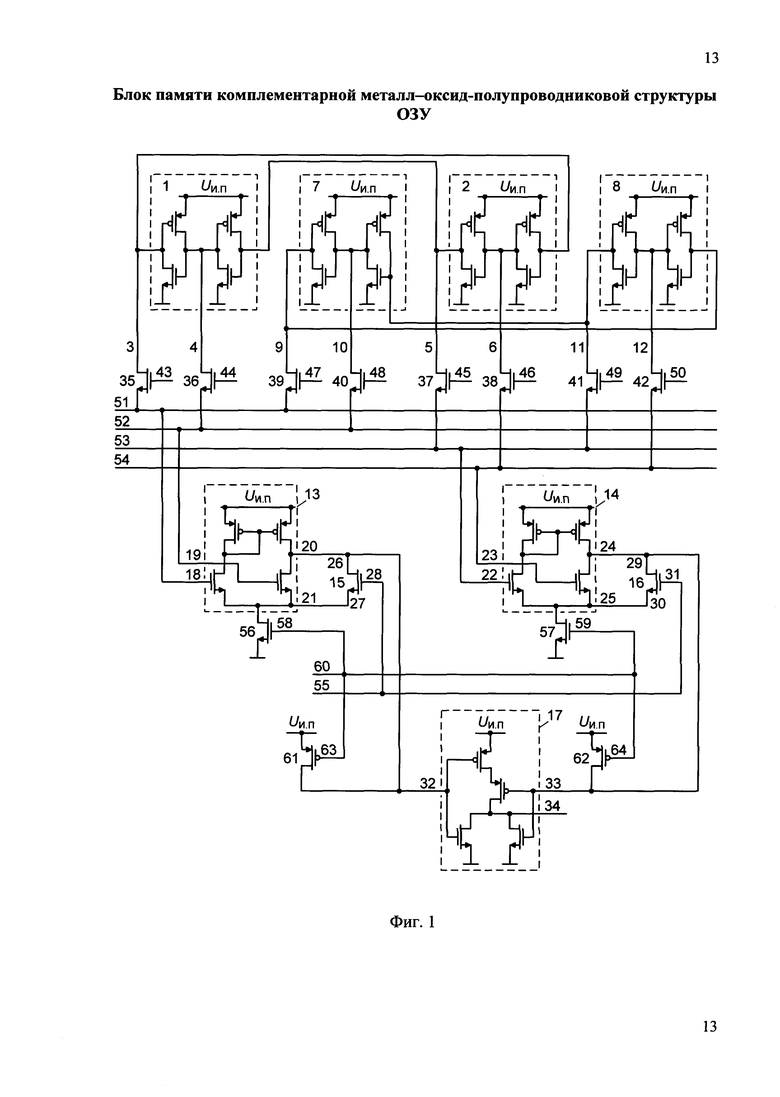

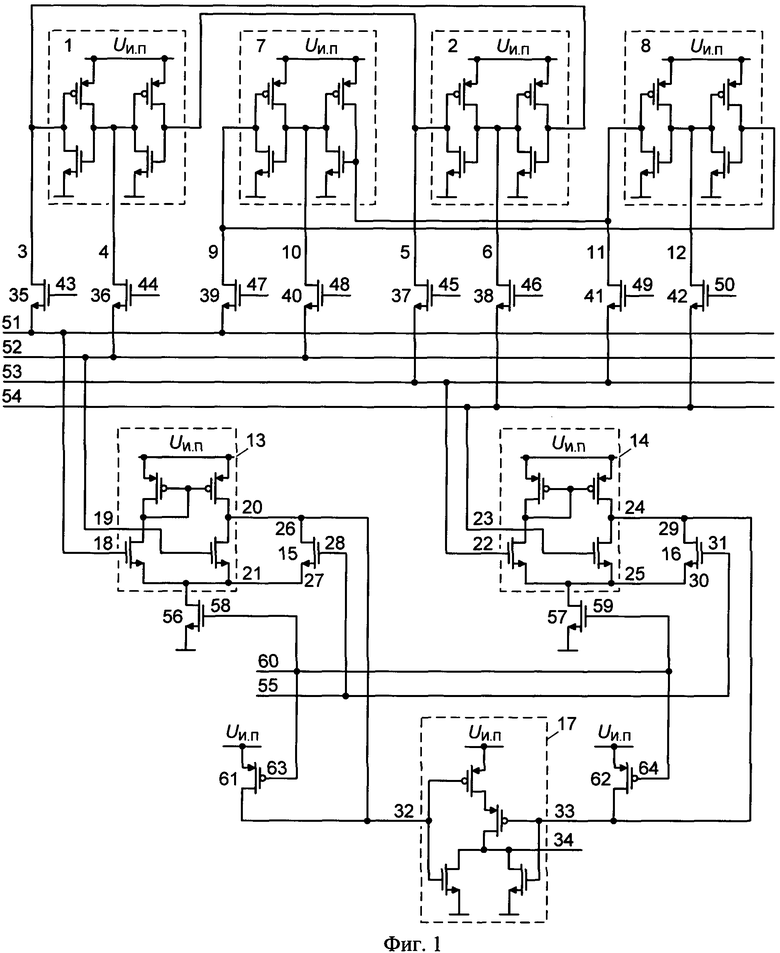

Изобретение поясняется чертежом: на фиг. 1 изображена электрическая принципиальная схема блока памяти, содержащего две ячейки памяти, каждая из которых состоит из двух групп транзисторов.

Блок памяти содержит две ячейки памяти, первая ячейка памяти из двух групп 1 и 2 транзисторов с четырьмя выводами 3, 4, 5, 6, вторая ячейка из двух групп 7 и 8 транзисторов с четырьмя выводами 9, 10, 11, 12. Блок памяти содержит два считывающих усилителя 13, 14 с отражателями тока на парах РМОП транзисторов (транзисторов со структурой металл-оксид-полупроводник и каналом дырочной проводимости, то есть Р-типа), два дополнительных транзистора 15, 16 и логический элемент ИЛИ-НЕ 17, первый считывающий усилитель 13 имеет первый и второй входы 18, 19, выход 20 и вывод 21 объединенных истоков NМОП транзисторов (транзисторов со структурой металл-оксид-полупроводник и каналом электронной проводимости, то есть TV-типа), второй считывающий усилитель 14 имеет первый и второй входы 22, 23, выход 24 и вывод 25 объединенных истоков двух NМОП транзисторов, первый дополнительный транзистор 15 имеет выводы стока 26, истока 27 и затвора 28, второй дополнительный транзистор 16 имеет выводы стока 29, истока 30 и затвора 31, логический элемент 17 ИЛИ-НЕ имеет два входа 32, 33 и выход 34. Кроме того, блок памяти содержит четыре проходных ключа 35, 36, 37, 38 групп 1 и 2 транзисторов первой ячейки памяти и четыре проходных ключа 39, 40, 41, 42 групп 3 и 4 транзисторов второй ячейки памяти, затворы проходных ключей 35, 36, 37, 38, 39, 40, 41, 42 соединены с соответствующими линиями 43, 44, 45, 46, 47, 48, 49, 50 выборки. Один из выводов проходных ключей 35, 36, 37, 38 соединен, соответственно, с выводом 3, 4, 5,6 двух групп 1 и 2 транзисторов; другой вывод проходных ключей 35, 36, 37, 38 соединен с одной из четырех битовых линий 51, 52, 53, 54 данных блока памяти таким образом, что вывод ключа 35 соединен с первой битовой линией 51 данных, вывод ключа 36 - с второй битовой линией 52 данных, вывод ключа 37 - с третьей битовой линией 53 данных, вывод ключа 38 - с четвертой битовой линией 54 данных. Кроме того, первый и второй входы 18, 19 первого считывающего усилителя 13 соединены с первой и второй (битовыми) линиями 51, 52 данных, первый и второй входы 22, 23 второго считывающего усилителя 14 соединены с третьей и четвертой битовыми линиями 53, 54 данных, выводы 26, 27 стока и истока первого дополнительного транзистора 15 соединены, соответственно, с выходом 20 первого считывающего усилителя 13 и с выводом 2 объединенных истоков NМОП транзисторов первого усилителя 13, выводы 29, 30 стока и истока второго дополнительного транзистора 16 соединены, соответственно, с выходом 24 второго считывающего усилителя 14 и с выводом 25 объединенных истоков NМОП транзисторов второго усилителя, выводы 28, 31 затворов первого и второго дополнительных транзисторов 15, 16 соединены с линией 55 смещения с напряжением на ней больше порогового значения, выходы 20, 24 первого и второго считывающих усилителей 13, 14 соединены с первым и вторым входами 32, 33 логического элемента 17 ИЛИ-НЕ, выход 34 которого является выходной шиной блока памяти. Кроме того, блок памяти содержит два ключа 56, 57 выборки чтения, входы 58, 59 управления которых соединены с линией 60 управления чтением, а выходы соединены с выводами 21 и 25 объединенных истоков NМОП транзисторов, соответственно, считывающих усилителей 13 и 14, и два ключа 61, 62 предустановки состояния, входы 63, 64 управления которых соединены с линией 60 управления чтением. Описанное устройство работает следующим образом.

Блок памяти может работать в одном из трех режимов: запись данных в ячейки памяти, хранение и чтение данных из ячеек памяти.

Запись данных в каждую ячейку памяти блока памяти осуществляется через ее выводы, соединенные проходными ключами с битовыми линиями 51, 52, 53, 54 данных блока памяти. Далее работа устройства рассматривается на примере записи, хранения и чтения данных ячейки памяти из двух групп 1 и 2 транзисторов. Запись и считывание производится через выводы 3, 4, 5, 6 двух групп 1 и 2 транзисторов ячейки через проходные ключи 35, 36, 37, 38 этой ячейки памяти.

При записи данных в ячейку памяти на битовые линии 51, 52, 53, 54 данных подают записываемые данные в дифференциальной форме, а именно на первую и третью линии 51, 53 в нормальном виде, а на вторую и четвертую линии 52, 54 - в инверсном. Установкой активного уровня на линиях 43, 44, 45, 46 выборки открывают проходные ключи 35, 36, 37, 38 ячейки памяти, пропуская записываемые данные (сигналы) на выводы 3, 4, 5, 6 ячейки памяти. В режиме записи на линию 60 управления чтением может быть установлен как неактивный уровень или активный уровень, во втором случае можно одновременно осуществить чтение записываемых данных.

В режиме хранения на линиях 43, 44, 45, 46 выборки устанавливают неактивный уровень, что поддерживает проходные ключи 35, 36, 37, 38 в закрытом состоянии. На выводах 3, 4, 5, 6 ячейки памяти хранятся уровни сигналов, соответствующих записанным данным. На линию 60 управления чтением устанавливают уровень, переводящий ключи 56, 57 выборки чтения в закрытое состояние, а ключи 61, 64 предустановки состояния в открытое состояние. Это переводит считывающие усилители 13, 14 в неактивное состояние и устанавливает смещение на выходы 20, 24 считывающих усилителей 13, 14 и входы 32, 33 элемента 17 ИЛИ-НЕ, равное напряжению питания, что обеспечивает неизменное состояние на выходе 34 элемента 17 ИЛИ-НЕ в режиме хранения, компенсируя изменение выходных токов считывающих усилителей в неактивном состоянии.

При чтении данных из ячейки памяти на линиях 43, 44, 45, 46 выборки устанавливают активный уровень. Проходные ключи 35, 36, 37, 38 открываются, позволяя считывать хранимые данные с выводов 3, 4, 5, 6 ячейки памяти на битовые линии 51, 52, 53, 54 данных. На линию 60 управления чтением устанавливают уровень, переводящий ключи 61, 62 предустановки состояния в закрытое состояние, а ключи 56, 57 в активное состояние, что переводит считывающие усилители 13, 14 в активное состояние для чтения с битовых линий 51, 52, 53, 54 данных.

При воздействии на ячейку памяти одиночной ядерной частицы образованные вдоль трека неравновесные носители заряда диффундируют к транзисторам ячейки и выводятся в виде импульсов тока на выводы, перезаряжая емкости этих узлов. Этот процесс сопровождается образованием импульсов напряжений помехи на выводах, которые переводят триггер ячейки памяти из двух групп 1 и 2 транзисторов в неустойчивое (нестационарное) состояние, которое может завершиться возвращением в исходное стационарное состояние ячейки с сохранением данных или завершиться сбоем состояния ячейки памяти в случае превышении порога переключения.

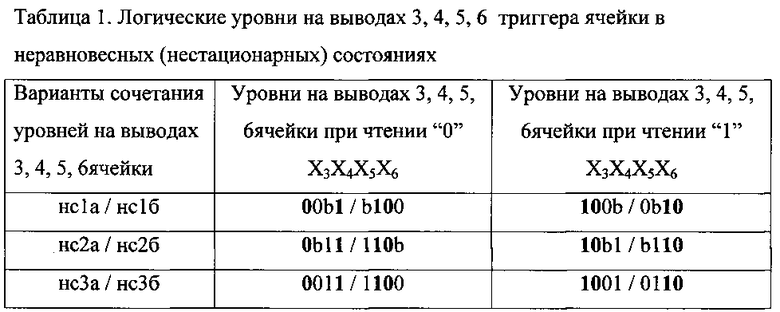

Для ячеек памяти при проектно-технологических нормах 65 нм и менее с разделенными на две группы транзисторами (которые разнесены на кристалле ОЗУ на расстояние, снижающее вероятность сбоя триггера ячейки памяти при воздействии одиночных ядерных частиц) длительность неравновесного (нестационарного)состояния может достигать 1 нс. В этом состоянии можно осуществлять надежное чтение данных, определяя два (из четырех) вывода триггера ячейки, которые сохраняют свои исходные состояния до воздействия. Варианты сочетания логических уровней Х3Х4Х5Х6 (и напряжений, пропорциональных логическим уровням и значению напряжения питания UИ.П) на выводах 3, 4, 5, 6 двух групп 1 и 2 транзисторов ячейки в нестационарных состояниях приведены в таблице 1.

Жирным шрифтом в таблице 1 отмечены уровни на выводах 3, 4, 5, 6, сохраняющих значения, соответствующие исходным уровням в стационарном состоянии ячеек при хранении "0" (0101) и "1" (1010). На одном из выводов 3, 4, 5, 6 ячейки памяти, который в неравновесном (нестационарном) состоянии оказывается с двумя открытыми транзисторами, устанавливается напряжение UИ.П×b, и его нормированный уровень будет иметь некое промежуточное значение b. Значение b зависит от соотношения крутизны характеристик РМОП и NМОП транзисторов и ограничено значениями 0,2<b<0,4.

Для вариантов неравновесных (нестационарных) состояний, приведенных в таблице 1, использованы следующие обозначения: нс1а и нc1б, где цифра соответствует номеру варианта состояния, а буквы "а" и "б" соответствуют двум подвариантам состояний с общим цифровым номером.

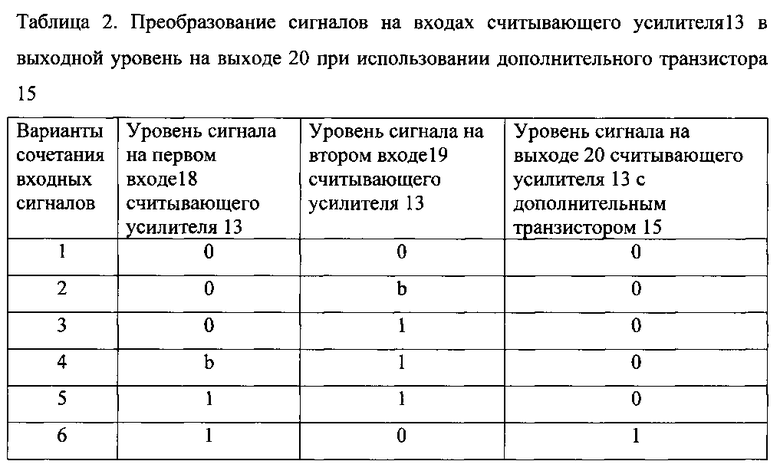

Каждый из двух считывающих усилителей 13, 14 с дополнительными транзисторами 15, 16, соединенными с их выходами 20, 24, описывается логическими функциями преобразования, связывающими уровни сигналов на их двух входах с их выходным сигналом, которые приведены в таблице 2.

Передаточные функции, приведенные в таблице 2 в качестве примера для считывающего усилителя 13 с дополнительным транзистором 15, реализуются как считывающим усилителем 13, так и усилителем 14 с дополнительными транзисторами 15, 16 при напряжении на линии 55 смещения и на выводах 28, 31 затворов дополнительных транзисторов 15, 16 напряжения смещения больше порогового значения UСМ=U55=U28=U31>UСМ.ПОР, где UСМ.ПОР≥UПОР.NМОП или UСМ.ПОР≥b×UИ.П, если b×UИ.П>UПОР.NМОП, где UПОР.NМОП - пороговое напряжение вольтамперной характеристики NMOH транзисторов.

Характеристики преобразования входных уровней по вариантам 1 и 2 в таблице 2 обеспечиваются дополнительным транзистором 15 (и 16), присоединенным к считывающему усилителю 13 (и 14), и заданием напряжения смещения на их выводы 28, 31 затворов больше порогового напряжения U55=U28=U31=UСМ>UСМ.ПОР, что задает малое значение сопротивления канала дополнительного транзистора по сравнению с сопротивлениями каналов МОП транзисторов считывающих усилителей в запертом состоянии и, соответственно, обеспечивает в этом режиме уровень логического нуля "0" на выходе 20 считывающего усилителя 13UВЫХ20=U0 на выходе 24UВЫХ24=U0 усилителя 14.

В результате включения дополнительного транзистора передаточные характеристики считывающего усилителя с отражателем тока на паре РМОП транзисторов перестают зависеть от напряжения на втором входе 19 считывающего усилителя 13 (аналогично на втором входе 23 усилителя 14) в диапазоне 0≤UВХ19≤0,35 В и 0≤UВХ23≤0,35 В при U55=U28=U31=UСМ>UСМ.ПОР, что обеспечивает возможность реализовать варианты 1, 2 логических передаточных функций, приведенных в таблице 2.

В этом случае считывающие усилители 13, 14 с дополнительными транзисторами 15, 16 реагируют на сигналы на их входах с уровнем напряжения UВХ.УСИЛИТЕЛЯ=b×UИ.П как на логический "0" и все строки в таблице 2 соответствуют логической функции преобразования входных сигналов в сигналы на выходах 20, 24 считывающих усилителей следующего вида: Y20=Х3·nХ4 и Y24=Х5·nХ6, где Х3, Х4, Х5, Х6 - логические уровни сигналов, поступающих на битовые линии 51, 52, 53, 54 данных с выводов 3, 4, 5, 6 ячейки памяти; n - обозначает инверсию логического уровня сигнала.

В предложенном блоке памяти чтение данных из ячеек памяти как в нестационарных, так и стационарных их состояниях производится двумя считывающими усилителями 13,14 с дополнительными транзисторами 15, 16 и логическим элементом 17 ИЛИ-НЕ, при этом логическая функция чтения состояний ячеек памяти по уровням сигналов на их выводах 3, 4, 5, 6 имеет следующий вид: nY34=X3·nX4+X5·nX6.

Пример реализации изобретения

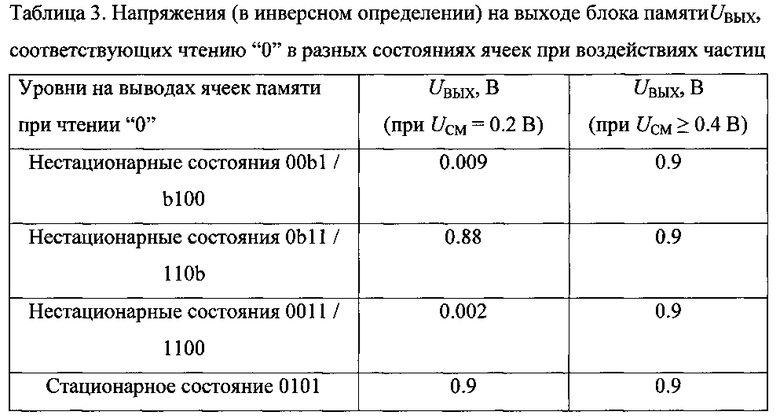

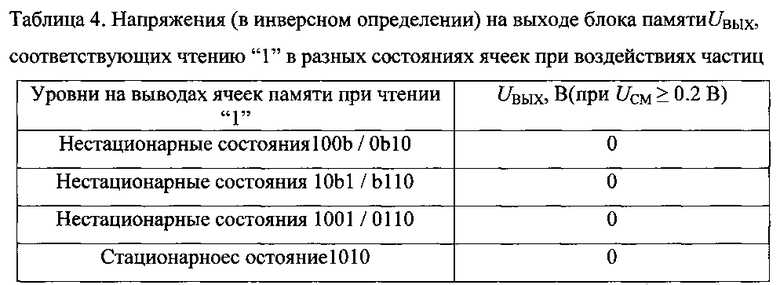

Устройство по изобретению реализовано в виде проекта блока памяти КМОП ОЗУ по проектной норме 28 нм в составе КМОП СБИС микропроцессорной системы. Накопитель содержит 32×64 ячеек памяти. Результаты моделирования результатов чтения данных из блока памяти по проектно-технологической норме объемный КМОП TSMC 28 нм приведены в таблицах 3 и 4.

В таблицах 3 и 4 приведены значения уровней напряжения на выходе 34 блока памяти на КМОП транзисторах с проектной нормой 28 нм в неравновесных (нестационарных) и стационарных состояниях в зависимости от напряжения смещения дополнительных транзисторов 15, 16 на линии 55 смещения при чтении логического "0" и логической "1" при напряжении питания блока UИ.П=0.9 В.

Чтение логического "0" во всех неравновесных (нестационарных) состояниях дает истинные значения (в инверсном их определении при использовании логического элемента ИЛИ-НЕ) при напряжениях смещения UСМ≥0.3 В (см. таблицу 3), а чтение логической "1" - при напряжениях смещения UСМ≥0.2 В (см. таблицу 4). Эти данные определены при разбросе уровней напряжений на выводах 3, 4, 5, 6 групп 1 и 2 транзисторов ячейки памяти, соответствующих логическим "0" и "1" в диапазонах U0=0-0.3 В и U1=0.6-0.9 В.

Блок памяти на основе считывающих усилителей с отражателем тока на паре РМОП транзисторов без использования дополнительных транзисторов 15, 16 не обеспечивает правильное чтение логического "0" из ячейки памяти, когда напряжения на выводах 3, 4, 5, 6 двух групп 1 и 2 транзисторов имеют уровни: U3=0, U6=0.9 В при напряжениях на других двух входах в пределах U4=(0-0.16) В и U5=(0-0.9) В. Это соответствует ложному чтению "0" в состояниях 00b1, 0011, b100 и 1100.

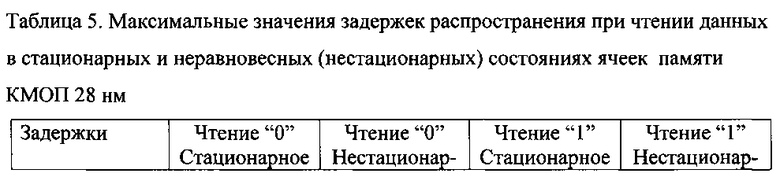

Динамические свойства блока памяти в режиме чтения характеризуют времена задержки распространения сигнала tЗД.Р, значения которых при чтении данных в разных состояниях ячеек приведены в таблице 5 для смещения на шине 55 и затворах 28, 31 дополнительных транзисторов 15, 16, равного UСМ55=0.5 В. В таблице 5 приведены данные для случаев, когда отсутствуют ключи 61, 62 предустановки состояния и когда эти ключи 61, 62 имеются. Использование ключей 61, 62 предустановки состояния снижает время задержки при чтении данных из ячеек памяти.

Изобретение относится к области вычислительной техники и может быть использовано в блоках статических КМОП ОЗУ. Техническим результатом является повышение надежности чтения данных из ячеек памяти при воздействии одиночной ядерной частицы в режиме, когда ячейка памяти на основе двух групп транзисторов временно находится в нестационарном состоянии. Устройство содержит выходную шину блока памяти, ячейки памяти, состоящие из двух групп транзисторов каждая, соединенных через проходные ключи с четырьмя битовыми линиями данных, и двух считывающих усилителей, первый и второй входы первого считывающего усилителя соединены с первой и второй битовыми линиями данных, первый и второй входы второго считывающего усилителя соединены с третьей и четвертой битовыми линиями данных, блок памяти снабжен первым и вторым дополнительными транзисторами и логическим элементом ИЛИ-НЕ, и имеет линию смещения с напряжением на ней больше порогового значения, при этом считывающие усилители имеют отражатели тока на парах транзисторов со структурой металл-оксид-полупроводник и каналом дырочной проводимости, причем входы логического элемента ИЛИ-НЕ соединены с выходами первого и второго считывающих усилителей, с которыми соединены, соответственно, стоки первого и второго дополнительных транзисторов, затворы которых соединены с линией смещения с напряжением на ней больше порогового значения, а выход элемента ИЛИ-НЕ соединен с выходной шиной блока памяти. 1 ил., 5 табл.

Блок памяти комплементарной металл-оксид-полупроводниковой структуры ОЗУ, включающий выходную шину блока памяти, ячейки памяти, состоящие из двух групп транзисторов каждая, соединенных через проходные ключи с четырьмя битовыми линиями данных, и двух считывающих усилителей, первый и второй входы первого считывающего усилителя соединены с первой и второй битовыми линиями данных, первый и второй входы второго считывающего усилителя соединены с третьей и четвертой битовыми линиями данных, отличающийся тем, что, блок памяти снабжен первым и вторым дополнительными транзисторами и логическим элементом ИЛИ-НЕ и имеет линию смещения с напряжением на ней больше порогового значения, при этом считывающие усилители имеют отражатели тока на парах транзисторов со структурой металл-оксид-полупроводник и каналом дырочной проводимости, причем входы логического элемента ИЛИ-НЕ соединены с выходами первого и второго считывающих усилителей, с которыми соединены, соответственно, стоки первого и второго дополнительных транзисторов, затворы которых соединены с линией смещения с напряжением на ней больше порогового значения, а выход элемента ИЛИ-НЕ соединен с выходной шиной блока памяти.

| US 8605516 B2, 10.12.2013 | |||

| US 2013258790 A1, 03.10.2013 | |||

| US 2007109865 A1, 17.05.2007 | |||

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

Авторы

Даты

2016-04-10—Публикация

2015-04-07—Подача