Изобретение относится к области вычислительной техники и может быть использовано в блоках декодеров помехоустойчивого кодирования данных.

Основой декодеров помехоустойчивого кодирования данных являются комбинационные логические элементы, воздействие отдельных ядерных частиц на которые приводит к возникновению импульсов помех - временных изменений логического состояния (single event transients - SET) таких элементов. Снижение проектно-технологических норм КМОП СБИС до уровня менее 100 нм сопровождается ростом частоты одиночных сбоев (soft error rate - SER) КМОП элементов комбинационной логики под действием одиночных ядерных частиц.

Декодер помехоустойчивого кодирования данных содержит в своем составе блок вычисления вектора ошибки, на выходные сигналы которого корректируют ошибки в кодовом слове при чтении данных из ОЗУ. Блок вычисления вектора ошибки декодера является наиболее чувствительным блоком по последствиям воздействия на него одиночных ядерных частиц. Необходимо исключить возможность внесения погрешностей в выходные логические уровни блока вычисления вектора ошибки декодера при воздействии частиц на многовходовые логические элементы в его составе.

Одним из вариантов многовходовых логических элементов в составе декодера помехоустойчивого кодирования данных в настоящее время является статический многовходовой элемент 8ИЛИ-НЕ (High-Speed 64-Bit Binary Comparator using Three Stages with CMOS Logic Style / International Journal of Computer Applications, 2013, Vol. 67, №14, p.p. 8-15, фиг. 18) и динамический многовходовой элемент 8ИЛИ-НЕ (Патент US 7221188 В2, кл. H03K 19/096, опублик. May 22, 2007, фиг. 3).

Наиболее близким по технической сущности и достигаемому результату является многовходовой логический элемент комплементарной металл-оксид-полупроводниковой структуры декодера, состоящий из статических элементов ИЛИ-НЕ и статических элементов И-НЕ, соединенных между собой в цепочки чередующихся элементов так, что выходы элементов ИЛИ-НЕ соединены с входами последующих в цепочке элементов И-НЕ, выходы элементов И-НЕ соединены с входами последующих в цепочке элементов ИЛИ-НЕ, и размещенных на кристалле интегральной микросхемы (Патент US №6668344 В1, кл. G11C 29/00, опублик. Dec. 23, 2003, фиг. 42).

Недостатком описанного решения является недостаточная помехоустойчивость элемента (надежность выполнения логической функции) при воздействии одиночной ядерной частицы на внутренние узлы логического элемента.

Задачей настоящего изобретения является повышение надежности логического элемента при воздействии одиночной ядерной частицы.

Техническим результатом, ожидаемым от использования изобретения, является повышение помехоустойчивости (надежности выполнения логической функции) многовходового логического элемента при воздействии одиночной ядерной частицы.

Указанный технический результат достигается тем, что многовходовой логический элемент комплементарной металл-оксид-полупроводниковой структуры декодера, состоящий из статических элементов ИЛИ-НЕ и статических элементов И-НЕ, соединенных между собой в цепочки чередующихся элементов так, что выходы элементов ИЛИ-НЕ соединены с входами последующих в цепочке элементов И-НЕ, выходы элементов И-НЕ соединены с входами последующих в цепочке элементов ИЛИ-НЕ, и размещенных на кристалле интегральной микросхемы, согласно изобретению, снабжен компенсирующими транзисторами с каналами электронной проводимости и компенсирующими транзисторами с каналами дырочной проводимости, выводы затворов компенсирующих транзисторов с каналами электронной проводимости соединены с выходами элементов И-НЕ и с входами последующих в цепочке элементов ИЛИ-НЕ, а выводы их стоков - с выходами последующих в цепочке элементов ИЛИ-НЕ, при этом, выводы затворов компенсирующих транзисторов с каналами дырочной проводимости соединены с выходами элементов ИЛИ-НЕ и с входами последующих в цепочке элементов И-НЕ, а выводы их стоков - с выходами последующих в цепочке элементов И-НЕ и с входами последующих в цепочке элементов ИЛИ-НЕ, причем стоковые области каждого компенсирующего транзистора размещены на кристалле интегральной микросхемы относительно стоковых областей транзисторов с каналами такой же проводимости каждого из предшествующих в цепочке элементов на расстоянии, обеспечивающем одновременное воздействие одиночной ядерной частицы на указанные области транзисторов.

А также тем, что транзисторы с каналами электронной проводимости элементов И-НЕ и транзистор с каналом электронной проводимости последующего в цепочке элемента ИЛИ-НЕ, вход которого соединен с выводом затвора этого транзистора и с выходом элемента И-НЕ, образуют группы транзисторов с каналами электронной проводимости, стоковые области которых размещены на кристалле интегральной микросхемы на расстоянии друг от друга, обеспечивающем одновременное воздействие одиночной ядерной частицы на них, транзисторы с каналами дырочной проводимости одного из элементов ИЛИ-НЕ и транзистор с каналом дырочной проводимости одного из элементов И-НЕ, вход которого соединен с выводом затвора этого транзистора и с выходом одного из элементов ИЛИ-НЕ, образуют группы транзисторов с каналами дырочной проводимости, стоковые области которых размещены на кристалле интегральной микросхемы на расстоянии друг от друга, обеспечивающем одновременное воздействие одиночной ядерной частицы на них.

А также тем, что указанное расстояние, обеспечивающее одновременное воздействие одиночной ядерной частицы на указанные стоковые области транзисторов, равно минимальному расстоянию между указанными транзисторами, выбранному в соответствии с технологическим допуском.

Указанная совокупность признаков позволяет снизить вероятность сбоя логического состояния (повысить надежность) многовходового логического элемента при воздействии одиночной ядерной частицы.

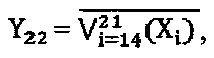

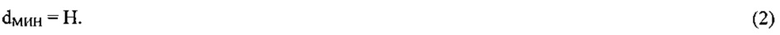

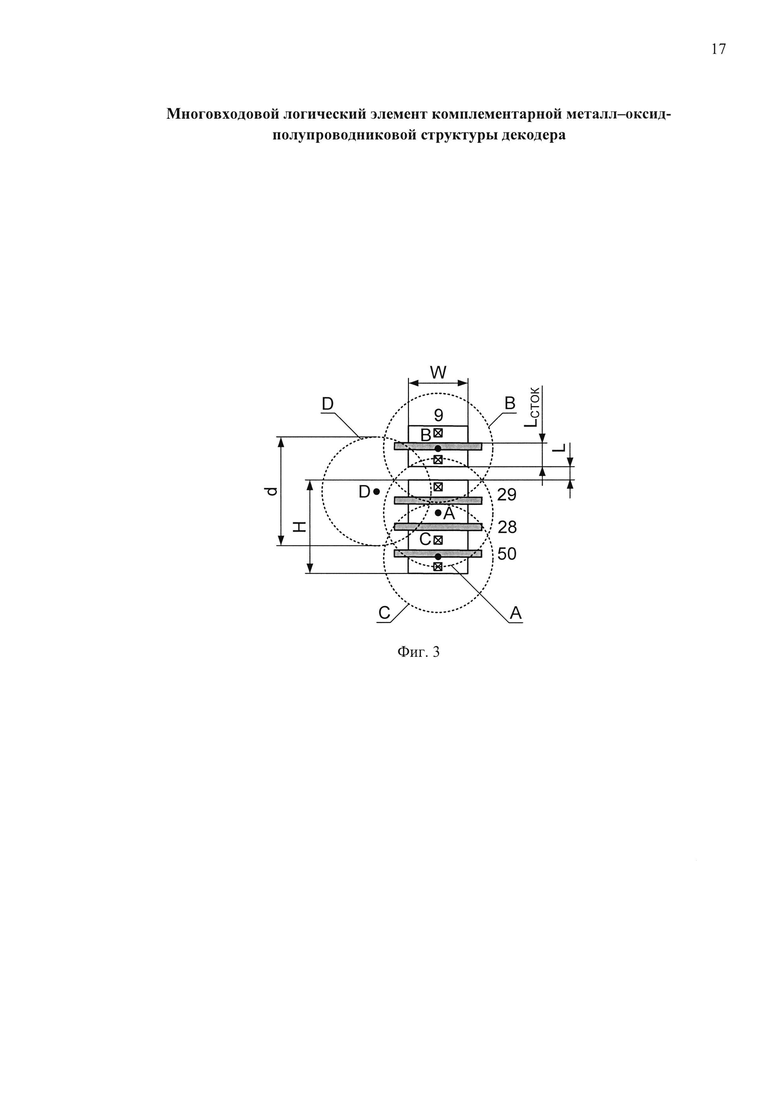

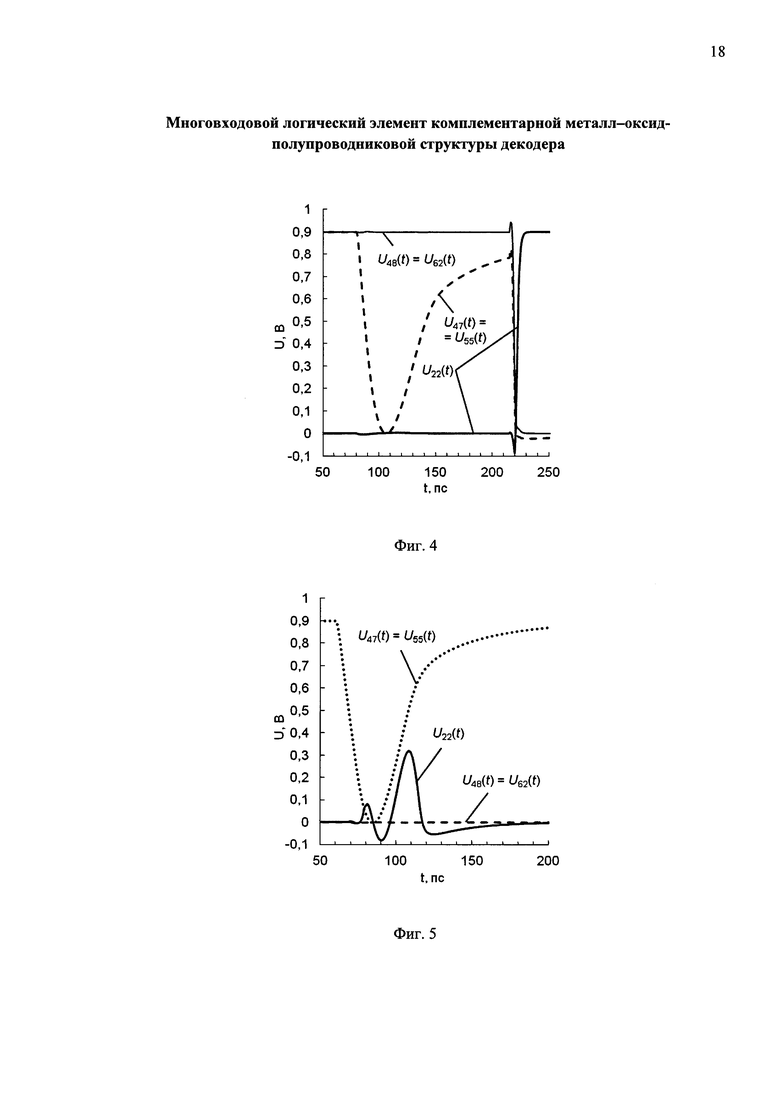

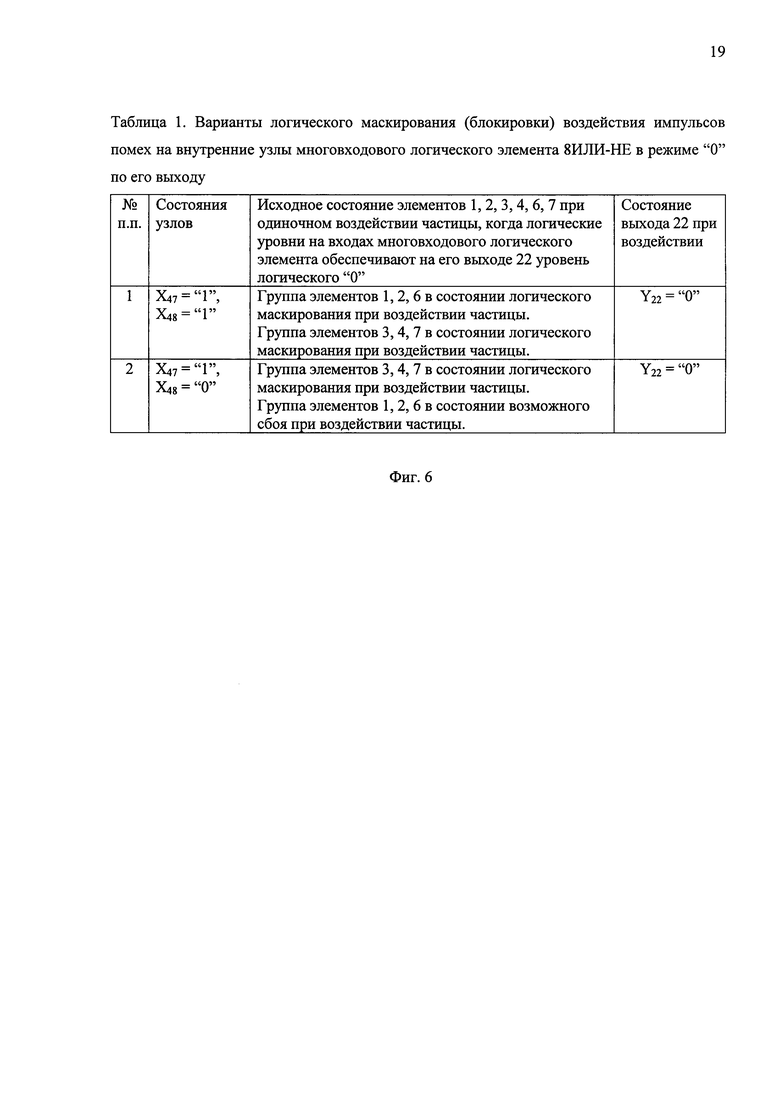

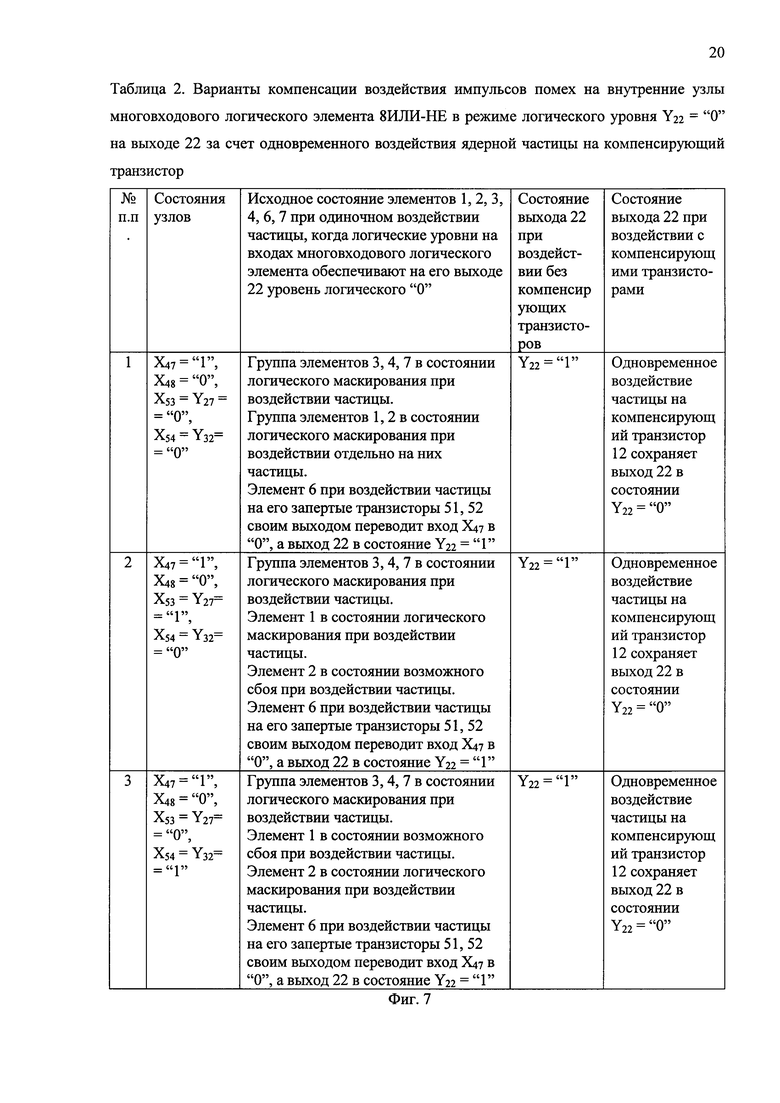

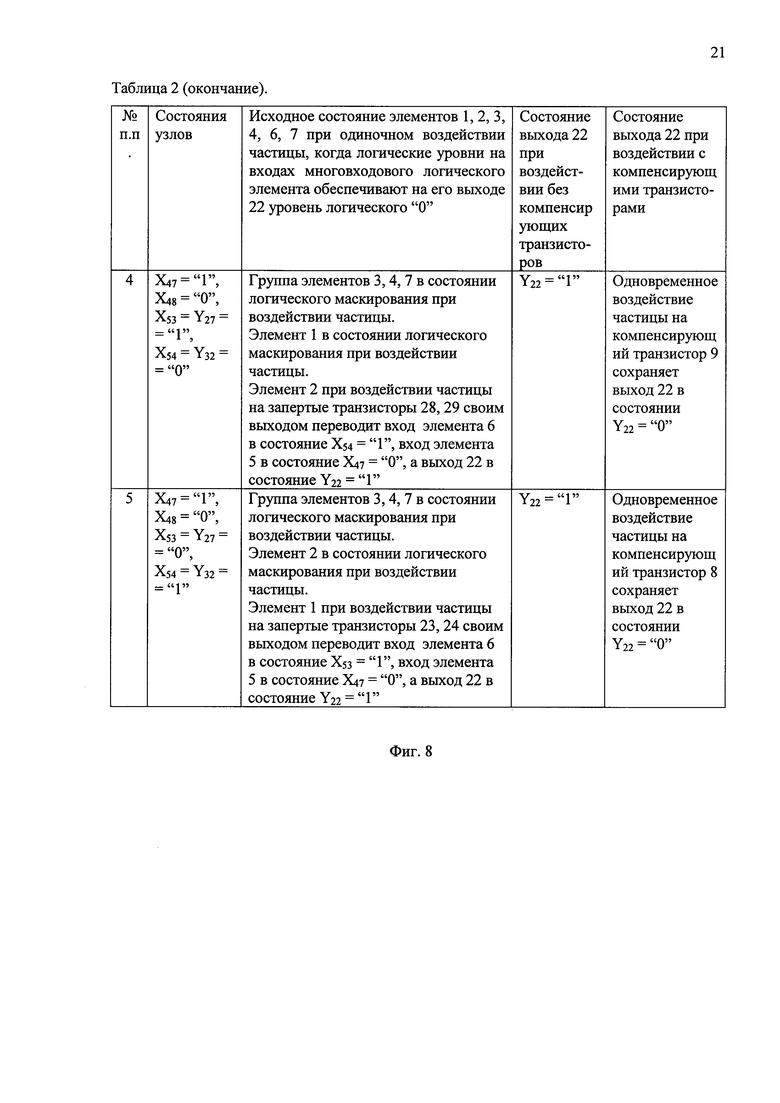

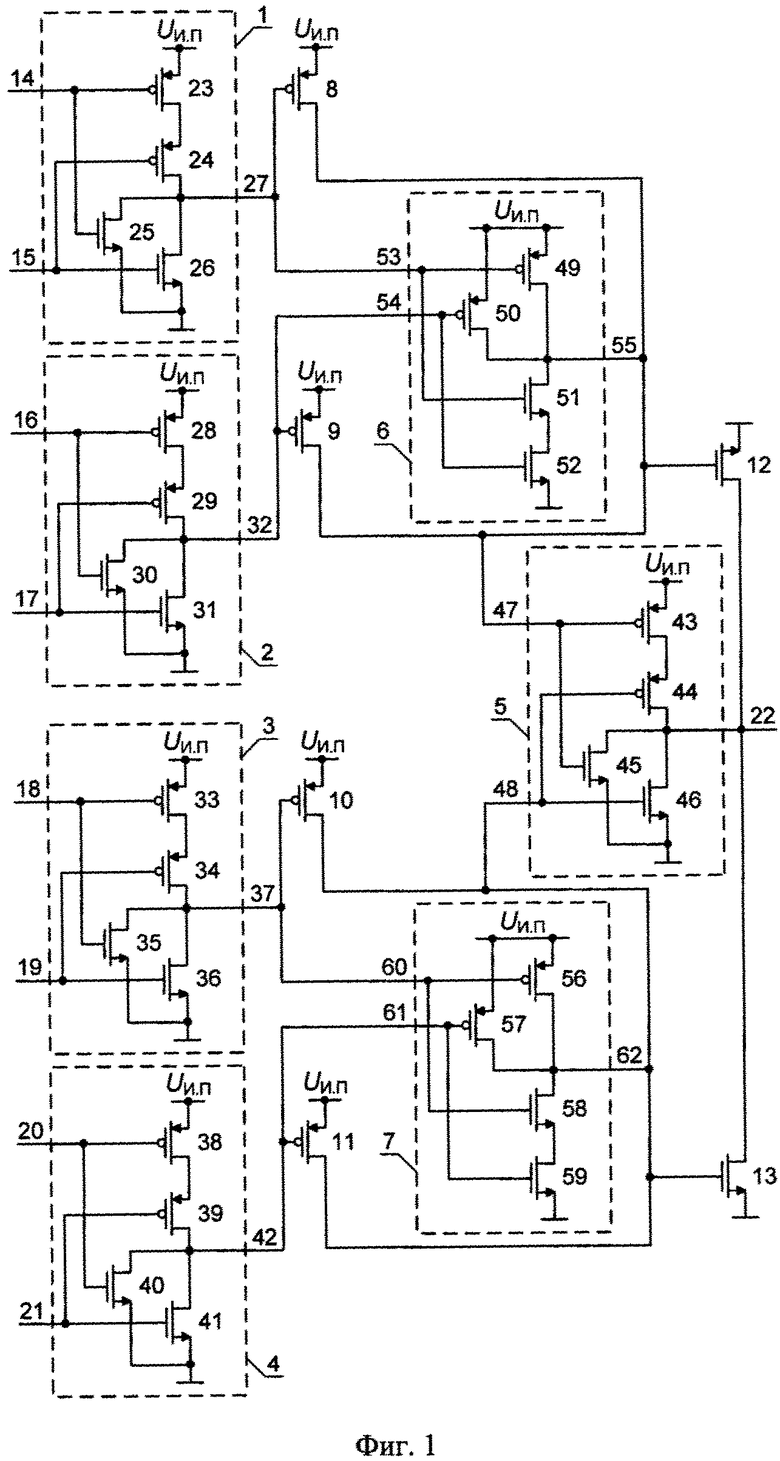

Изобретение поясняется чертежами, где на фиг. 1 изображена электрическая принципиальная схема многовходового логического элемента, на фиг. 2 изображена схема взаимного расположения транзисторов многовходового логического элемента, на фиг. 3 изображена схема взаимного расположения транзисторов в группе транзисторов совместно с расположением соответствующего компенсирующего транзистора относительно группы, а также приведены примеры прохождения трека одиночной ядерной частицы через область многовходового логического элемента на кристалле интегральной микросхемы и расположение соответствующих областей (пятен) диффузионного "растекания" неравновесных носителей заряда, на фиг. 4 и фиг. 5 представлены результаты моделирования, демонстрирующие технический результат использования изобретения, на фиг. 6 - таблица 1 - Варианты логического маскирования (блокировки) воздействия импульсов помех на внутренние узлы многовходового логического элемента 8ИЛИ-НЕ в режиме "0 по его выходу, на фиг. 7 - таблица 2 - Варианты компенсации воздействия импульсов помех на внутренние узлы многовходового логического элемента 8ИЛИ-НЕ в режиме логического уровня Y22="0" на выходе 22 за счет одновременного воздействия ядерной частицы на компенсирующий транзистор, на фиг. 8 - продолжение таблицы 2, на фиг. 9 - таблица 3 - Типовые размеры W, H, LСТОК транзисторов и рекомендуемые расстояния L между компенсирующим транзистором и сопряженной с ним группой транзисторов.

В одном из воплощений патентуемого изобретения многовходовой логический элемент, например, 8ИЛИ-НЕ содержит пять логических элементов ИЛИ-НЕ 1, 2, 3, 4, 5, два логических элемента И-НЕ 6, 7, компенсирующие транзисторы 8, 9, 10, 11 с каналами дырочной проводимости, компенсирующие транзисторы 12, 13 с каналами электронной проводимости. Многовходовой логический элемент имеет входы 14, 15, 16, 17, 18, 19, 20, 21, являющиеся входами логических элементов ИЛИ-НЕ 1, 2, 3, 4, и выход 22, являющийся выходом логического элемента ИЛИ-НЕ 5.

Логический элемент ИЛИ-НЕ 1 на транзисторах 23, 24, 25, 26 имеет два входа 14, 15 и выход 27, логический элемент ИЛИ-НЕ 2 на транзисторах 28, 29, 30, 31 имеет два входа 16, 17 и выход 32, логический элемент ИЛИ-НЕ 3 на транзисторах 33, 34, 35, 36 имеет два входа 18, 19 и выход 37, логический элемент ИЛИ-НЕ 4 на транзисторах 38, 39, 40, 41 имеет два входа 20, 21 и выход 42, логический элемент ИЛИ-НЕ 5 на транзисторах 43, 44, 45, 46 имеет два входа 47, 48 и выход 22, логический элемент И-НЕ 6 на транзисторах 49, 50, 51, 52 имеет два входа 53, 54 и выход 55, логический элемент И-НЕ 7 на транзисторах 56, 57, 58, 59 имеет два входа 60, 61 и выход 62. Выходы 27 и 32 логических элементов ИЛИ-НЕ 1 и 2 соединены, соответственно, с входами 53 и 54 логического элемента И-НЕ 6, выходы 37 и 42 логических элементов ИЛИ-НЕ 3 и 4 соединены, соответственно, с входами 60 и 61 логического элемента И-НЕ 7. Выходы 55 и 62 логических элементов И-НЕ 6 и 7 соединены, соответственно, с входами 47 и 48 логического элемента ИЛИ-НЕ 5. Кроме того, выводы затворов компенсирующих транзисторов 8, 9, 10, 11 с каналами дырочной проводимости соединены, соответственно, с выходами 27, 32, 37, 42 логических элементов ИЛИ-НЕ 1, 2, 3, 4, выводы стоков компенсирующих транзисторов 8 и 9 соединены с выходом 55 логического элемента И-НЕ 6, выводы стоков компенсирующих транзисторов 10 и 11 соединены с выходом 62 логического элемента И-НЕ 7, выводы истоков компенсирующих транзисторов 8, 9, 10, 11 соединены с шиной питания. Кроме того, выводы затворов компенсирующих транзисторов 12 и 13 с каналами электронной проводимости соединены, соответственно, с выходами 55 и 62 логических элементов И-НЕ 6 и 7, выводы стоков компенсирующих транзисторов 12 и 13 соединены с выходом 22 логического элемента ИЛИ-НЕ 7, выводы истоков компенсирующих транзисторов 12 и 13 соединены с общей шиной.

Кроме того, транзисторы многовходового элемента на кристалле микросхемы объединены в группы 63, 64, 65, 66, 67, 68 транзисторов по три транзистора, а именно, две группы 63, 64 транзисторов с каналами электронной проводимости состоят, соответственно, из транзисторов 45, 51, 52 и 46, 58, 59, а четыре группы 65, 66, 67, 68 транзисторов с каналами дырочной проводимости состоят, соответственно, из транзисторов 28, 29, 50; 23, 24, 49; 33, 34, 56 и 38, 39, 57.

Описанное устройство работает следующим образом.

Для многовходового логического элемента на фиг. 1 с итоговой логикой типа "ИЛИ-НЕ" выходной логический уровень Y22 вычисляются как инверсия дизъюнкции логических уровней Xi на входах i многовходового логического элемента

где i номер позиции входа от позиции 14 до позиции 21 многовходового логического элемента. Соответственно, выходной логический уровень, равный "1", т.е. Y22="1", будет только тогда, когда логические уровни на всех входах многовходового логического элемента равны "0", т.е. Xi="0", где i=14, 15, 16, 17, 18, 19, 20, 21. При всех остальных комбинациях логических уровней "0" и "1" на входах многовходового логического элемента выходной логический уровень будет "0", т.е. Y22="0".

В декодере помехоустойчивого декодирования данных многовходовые логические элементы являются основой блока вычисления вектора ошибки, на выходах которых формируются логические уровни либо сохраняющие биты в кодовом слове, либо исправляющие их как ошибки в кодовом слове при чтении данных из ОЗУ. Число многовходовых логических элементов в декодере (разрядность декодера) совпадает с разрядностью N кодового слова, распространенное значение которой для случая применения в микропроцессорных СБИС составляет N=72. Входы каждого многовходового логического элемента управляются вектором синдромов ошибки, сформированным для каждого разряда данных. На всех N выходах многовходовых логических элементов в блоке вычисления вектора ошибки должен сохраняться уровень логического "0" для тех разрядов кодового слова, которые не должны исправляться в блоке коррекции декодера. Если в считываемом из ОЗУ кодовом слове есть ошибка в одном из его разрядов, то значение разряда вектора ошибки, определенного в блоке вычисления вектора ошибки (то есть на выходе соответствующего этому разряду многовходового логического элемента), будет равно "1" и такой разряд кодового слова исправляется (корректируется). Многовходовых логических элементов в декодере, находящихся в состоянии "0", подавляющее большинство (не менее N-2=70 из N=72) и их состояние при выходном уровне, равном "0", должно быть максимально помехоустойчиво к воздействиям одиночных ядерных частиц.

Многовходовой логический элемент имеет структуру "дерева связей" (см. фиг. 1), отдельные ветви такого "дерева связей" образованы последовательностями элементов ИЛИ-НЕ → И-НЕ → ИЛИ-НЕ (цепочки чередующихся элементов). Для таких структур характерно логическое маскирование части импульсов помех, воздействующих на их узлы (logical masking), в частности. Тогда воздействие отдельной ядерной частицы на чувствительные области транзисторов в составе логических элементов ИЛИ-НЕ 1, 2, 3, 4, 5 или логических элементов И-НЕ 6 и 7, не приводит к изменению логического уровня на выходе многовходового логического элемента. Логическое маскирование зависит от конкретного сочетания логических уровней сигналов на входах многовходового логического элемента и входах составляющих его логических элементов ИЛИ-НЕ 1, 2, 3, 4, 5 или логических элементов И-НЕ 6 и 7.

В таблице 1 (фиг. 6) приведены все варианты сочетания значений логических уровней на входах 47, 48 выходного элемента ИЛИ-НЕ 5 многовходового логического элемента, при сочетании которых осуществляется логическое маскирование помех с выходов 55, 62 элементов И-НЕ 6, 7, и соответственно, это варианты состояний входов 47, 48, при которых элемент ИЛИ-НЕ 5 будет нечувствителен к воздействию помех по его входам.

Элемент, состоящий из двух элементов И-НЕ 6, 7 и одного элемента ИЛИ-НЕ 5 (см. фиг. 1), при состоянии "1" второго входа 48 Х48="1" элемента ИЛИ-НЕ 5, блокирует передачу импульса помехи (noise pulse, SET), воздействующего на первый вход 47 и переводящего вход 47 из состояния "1" в состояние "0" (либо из состояния "0" в "1").

Если же вход 48 элемента ИЛИ-НЕ 5 находится в состоянии Х48="0", то логическое маскирование импульса помехи, воздействующего на выход 55 элемента И-НЕ 6, переводящего вход 47 из состояния Х47="1" в состояние Х47="0", невозможно в силу логических свойств элемента. В таком логическом состоянии элемента ИЛИ-НЕ 5 передача импульса помехи, возникшего на его входе 47 под воздействием заряда электронов с трека одиночной частицы на обратно смещенные стоковые pn-переходы NMΟΠ транзисторов 51, 52 предыдущего в цепочке элемента И-НЕ 6 (на его выходе образуется импульс помехи отрицательной полярности), может быть ослаблена при одновременном воздействии заряда с трека и на стоковую область (стоковый pn-переход) компенсирующего транзистора 12 с каналом электронной проводимости, соединенным выводом затвора с входом 47 логического элемента ИЛИ-НЕ 5, а выводом стока с выходом 22 этого элемента ИЛИ-НЕ 5. При логическом состоянии первого входа 47 Х47="1" и состоянии второго входа 48 Х48="0" переключательная характеристика элемента ИЛИ-НЕ 5 по входу 47 подобна характеристике инвертора, поэтому импульс помехи с входа 47 при передаче его на выход 22 элемента ИЛИ-НЕ 5 переводит этотвыход 22 во временное состояние "1" с обоими запертыми NMOП транзисторами 45, 46 элемента ИЛИ-НЕ 5. Одновременно заряд с трека ядерной частицы, воздействующий на обратно смещенный стоковый pn-переход компенсирующего транзистора 12, возвращает выход 22 этого элемента ИЛИ-НЕ 5 в состояние Y22="0".

В изложенном примере суть эффекта компенсации воздействием одиночной ядерной частицы заключается в одновременном воздействии на обратно смещенные pn-переходы стоковых областей транзисторов 51, 52 с электронной проводимостью каналов элемента И-НЕ 6 и n-области стока компенсирующего транзистора 12 с электронной проводимостью канала, если конструктивно обеспечено необходимое взаимное расположение (как в приведенном примере на фиг. 2) n-области стока компенсирующего транзистора 12 и стоковых областей транзисторов 51, 52 элемента И-НЕ 6. Этот пример соответствует вариантам компенсации, соответствующим логическим состояниям элементов 1, 2, 5 и 6, представленным пунктами 1, 2 и 3 в таблице 2 (фиг. 7 и 8).

Возможен другой случай компенсации при воздействии частицы на логический элемент ИЛИ-НЕ 2, находящийся в исходном логическом состоянии "0", т.е. на входе 54 логического элемента И-НЕ 6 логический уровень Х54="0". При этом группа элементов 3, 4, 7 находится в состоянии логического маскирования и сохраняет на входе 48 элемента ИЛИ-НЕ 5 логическое состояние Х48="0". На входе 47 элемента ИЛИ-НЕ 5 логический уровень Х47="1", что поддерживает выход 22 элемента ИЛИ-НЕ в состоянии Y22="0". Элемент ИЛИ-НЕ 1 находится в логическом состоянии "1", при этом на входе 53 логического элемента И-НЕ 6 логический уровень Х53="1". Элемент ИЛИ-НЕ 2 при воздействии частицы на стоковые переходы его запертых транзисторов 28, 29 переходом логического состояния своего выхода на логический уровень "1" переводит вход 54 элемента И-НЕ 6 в состояние Х54="1", что переводит выход 55 элемента И-НЕ 6 в состояние "0" и соответственно вход 47 элемента ИЛИ-НЕ 5 в состояние Х47="0", а выход 22 элемента ИЛИ-НЕ 5 в состояние Y22="1". Одновременно с воздействием на транзисторы 28 и 29 элемента ИЛИ-НЕ 2 заряд с трека ядерной частицы воздействует на обратно смещенный стоковый pn-переход компенсирующего транзистора 9, что возвращает выход 55 логического элемента И-НЕ 6 в состояние логической "1", соответственно, вход 47 элемента ИЛИ-НЕ 5 в состояние Х47="1", а выход 22 этого элемента ИЛИ-НЕ 5 в состояние Y22="0".

Этот пример соответствует вариантам компенсации, соответствующим логическим состояниям элементов 1, 2, 5 и 6, представленным пунктом 4 в таблице 2. В таблице 2 приведены все варианты компенсации воздействия импульсов помех на внутренние узлы многовходового логического элемента 8ИЛИ-НЕ в состоянии Y22="0" по его выходу 22.

Замена в таблице 2 номеров элементов 3, 4, 7 на 1, 2, 6 и соответственно номеров элементов 1, 2, 6 на 3, 4, 7 совместно с сопутствующей заменой номеров выходов и номеров компенсирующих транзисторов приводит к описанию результатов воздействия частицы для случаев, когда постоянный эффект логического маскирования обеспечивают элементы 3, 4, 7, сохраняя вход 47 элемента ИЛИ-НЕ 5 в состоянии Х47="0" и задавая на входе 48 логического элемента ИЛИ-НЕ 5 исходное состояние Х48="1". В этом случае при образовании помехи от ядерной частицы на выходе 62 элемента ИЛИ-НЕ 7 и одновременно на n-области стока компенсирующего транзистора 13 с электронной проводимостью канала на выходе 22 многовходового логического элемента сохраняется логический уровень Y22="0".

Таким образом, для обеспечения помехоустойчивости логических состояний Y22="0" на выходе 22 многовходового логического элемента при воздействии импульсов помех, возникающих при воздействии одиночных ядерных частиц, надо дополнительно к логическому маскированию обеспечить компенсацию импульсов помех на входах элемента ИЛИ-НЕ 5 с переходом от уровня UИ.П к уровню 0 за счет одновременного воздействия заряда от одиночной ядерной частицы на n-области стоков компенсирующих транзисторов 12 или 13 с электронной проводимостью каналов и транзисторов с электронной проводимостью каналов предыдущего элемента И-НЕ 6 или 7 в цепочке (ветви дерева связей). А также надо обеспечить компенсацию импульсов помех, возникающих на входах 53, 54, 60, 61 элементов И-НЕ 6 или 7 с переходом от уровня 0 до уровня UИ.П, обеспечением максимально общей области воздействия заряда от одиночной ядерной частицы одновременно на стоковые p-области пар транзисторов 23 и 24, 28 и 29, 33 и 34, 38 и 39 с дырочной проводимостью канала соответственно элементов ИЛИ-НЕ 1, 2, 3, 4 в цепочке (ветви дерева связей) и на соответствующие им компенсирующие транзисторы 8, 9, 10, 11 с дырочной проводимостью канала.

Пример реализации изобретения

Устройство по изобретению реализовано в виде логического элемента для задач автоматизированного синтеза декодеров помехоустойчивого кодирования данных в составе системы на кристалле по проектной норме 65 нм. Схема расположения транзисторов многовходового логического элемента на кристалле микросхемы приведена на фиг. 2. Для достижения технического результата - повышения помехоустойчивости (надежности выполнения логической функции) при воздействии одиночной ядерной частицы - компенсирующие транзисторы 8, 9, 10, 11 с каналами дырочной проводимости размещены на кристалле интегральной микросхемы на минимальном расстоянии, выбранным в соответствии с технологическим допуском и, например, равным ему по данной проектной норме относительно соответствующих пар транзисторов 23 и 24, 28 и 29, 33 и 34, 38 и 39 элементов ИЛИ-НЕ 1, 2, 3, 4 и обеспечивающим надежное одновременное воздействие одиночной ядерной частицы на них. Подобным образом, компенсирующие транзисторы 12, 13 с каналами электронной проводимости размещены, соответственно, на кристалле интегральной микросхемы относительно пар транзисторов 51 и 52, 58 и 59 элементов И-НЕ 6, 7 на минимальном расстоянии, выбранном в соответствии с технологическим допуском и, например, равным ему и обеспечивающим надежное одновременное воздействие одиночной ядерной частицы на них.

Варианты воздействия одиночной ядерной частицы на конкретную область кристалла микросхемы отображены на фиг. 3 в виде положения следа трека частицы, отмеченного "жирными" точками с метками А, В, С, D, и окружающего этот след цилиндрического пятна диффузионного распределения (растекания) неравновесных носителей заряда (электронно-дырочных пар), образованных вокруг трека частицы, с диаметром d. В зависимости от энергии частиц в большинстве случаев диаметр диффузионного пятна воздействия составляет d=0.5-2 мкм.

Варианты возможного воздействия одиночной частицы на фиг. 3 приведены для группы транзисторов 28, 29, 50 с дырочной проводимостью канала для случаев направления треков частицы перпендикулярно плоскости кристалла микросхемы и расположенного рядом относительно транзисторов 28, 29 на минимальном расстоянии, например, равном технологическому допуску компенсирующего транзистора 9 с дырочной проводимостью канала. "Жирные" точки с метками А, В, С, D отображают след от вертикального прохождения трека через плоскость кристалла. Круговые области с центрами, соответствующими следам прохождения треков, иллюстрируют варианты возможного положения пятна диффузионного "растекания" неравновесных носителей заряда, образованных под действием энергии, переданной частицей кристаллу вдоль ее трека.

Примеры на фиг. 3 прохождения трека частицы через область элемента на кристалле интегральной микросхемы: А - через область стока транзистора 28; В - через область стока компенсирующего транзистора 9; С - через область стока транзистора 50; D - вблизи области затвора транзистора 29 вне области стоков. На фиг. 3 не показан пример варианта воздействия симметричного воздействию на точку D, но с правой стороны относительно точки А. Результат этого воздействия такой же, как на точку D. Приведенные варианты воздействий на группу транзисторов 28, 29, 50 с дырочной проводимостью каналов и компенсирующий транзистор 9 с дырочной проводимостью канала соответствуют случаям компенсации воздействия одиночной ядерной частицы на транзисторы 28, 29 одновременным воздействием на область стока компенсирующего транзистора 9, либо на область стока транзистора 50.

Варианты воздействий частицы, приведенные на фиг. 3 для группы транзисторов 28, 29, 50 с дырочной проводимостью канала и компенсирующего транзистора 9, можно использовать для описания аналогичных случаев воздействия на другие пять групп (из общего количества из шести групп) транзисторов многовходового элемента, а именно еще трех групп транзисторов с каналами дырочной проводимости на транзисторах 23, 24, 49; 33, 34, 56 и 38, 39, 57, а также двух групп транзисторов с каналами электронной проводимости на транзисторах 45, 51, 52 и 46, 58, 59 соответственно в сочетании этих групп с компенсирующими транзисторами 8, 10, 11, 12, 13, расположенных от соответствующей группы на минимальном расстоянии равном технологическому допуску со стороны противоположной расположению транзисторов 45, 46, 49, 50, 56, 57.

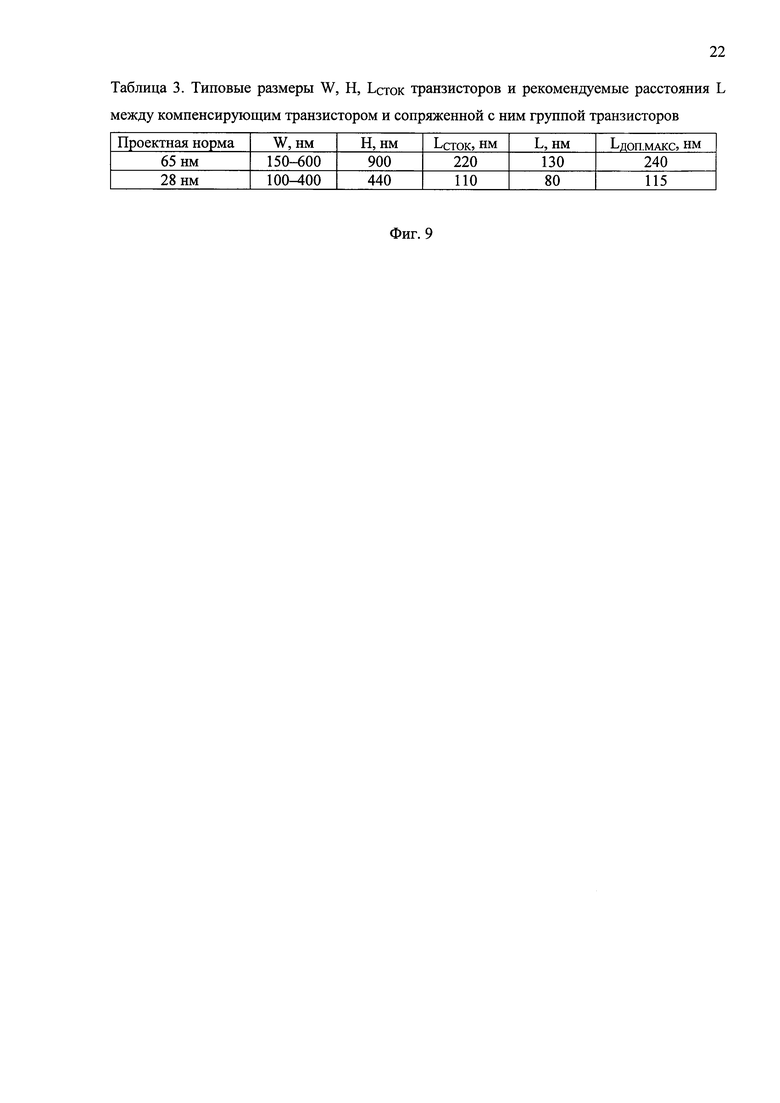

В таблице 3 приведены типовые значения ширины W каналов каждого транзистора в группе транзисторов и ширины компенсирующих транзисторов, значения длины H группы из транзисторов (например, на фиг. 3 обозначенных номерами позиций 28, 29, 50), а также длины каждой диффузионной области стока транзисторов LСТОК как с электронной, так и с дырочной проводимости и расстояния L между компенсирующим транзистором и сопряженной с ним группой транзисторов, соответствующие минимальным расстояниям равным технологическому допуску для проектно-технологических норм 65 нм и 28 нм. Все данные приведены для транзисторов микросхем, изготавливаемых по проектно-технологическим нормам 65 нм и 28 нм.

Диапазоны значений параметров в таблице 3 учитывают как размеры транзисторов с электронной, так и дырочной проводимостью каналов. Расстояние L между компенсирующим транзистором и сопряженной с ним группой транзисторов, соответствующее минимальному расстоянию равному технологическому допуску для расположения транзисторов многовходового логического элемента, приведенного на фиг. 2, и его фрагмента на фиг. 3 определяются требованием обеспечить эффект практически одновременного воздействия неосновных носителей заряда с пятна диффузионного растекания заряда на транзистор соответствующего элемента ИЛИ-НЕ или И-НЕ, находящегося в запертом состоянии и подвергнутого воздействию одиночной ядерной частицы, и на соответствующий компенсирующий транзистор. Значение L равно минимальному расстоянию равному технологическому допуску конкретной проектно-технологической норме. Технологический допуск ограничивает минимальное расстояние между двумя транзисторами на кристалле интегральной микросхемы для исключения возможного смыкания их областей в ходе технологического процесса изготовления (Sung-Mo (Steve) Kang, Leblebici Y. CMOS Digital Integrated Circuits Analysis & Design. 3rd Edition. - Boston: McGraw-Hill, 2003. - 658 p., стр. 37-39, фиг. 2.12).

Два крайних случаев положения пятна диффузионного "растекания", ограничивающих размеры области компенсации включают следующие два случая воздействия частицы. Первый случай, отображенный на фиг. 3, когда пятно покрывает стоковые области транзисторов 28, 29 и стоковую область компенсирующего транзистора 9, и второй случай, когда пятно покрывает всю группу транзисторов 28, 29 и 50, который в этом случае в расположении транзисторов на фиг. 2 выполняет роль компенсирующего транзистора.

Для двух крайних случаев положения пятна диффузионного "растекания", когда максимален компенсирующий эффект, можно оценить связь минимального диаметра dМИН диффузионного пятна воздействия частицы с геометрическими параметрами H группы транзисторов 28, 29, 50, длины LСТОК диффузионной области стока компенсирующего транзистора 9, а также максимального допустимого расстояния KДОП.МАКС между компенсирующим транзистором и сопряженной с ним группой транзисторов, следующими выражениями:

Выражения (1), (2), характеризующие крайние положения диффузионного пятна воздействия частицы, не противоречат друг другу. При условии dМИН=Н, следующего из (2), выражение для оценки расстояния LДОП.МАКС имеет вид

Оценочные значения пороговых расстояний LДОП.МАКС приведены в таблице 3 для двух проектно-технологических норм изготовления микросхем. Из сопоставления этих данных следует, что минимальные расстояния L, равные технологическому допуску, находятся в пределах максимально допустимых значений расстояний группы транзисторов до компенсирующего транзистора L≤LДОП.МАКС, когда гарантированно сохраняется компенсирующий эффект.

На фиг. 4 представлены результаты моделирования результата логического маскирования помехи на входе 47 элемента ИЛИ-НЕ 5. На фиг. 5 приведены результаты моделирования компенсации помехи от ядерной частицы, образованной стоковой областью транзисторов 51, 52 на выходе 55 элемента И-НЕ 6 и поступающей на вход 47 элемента ИЛИ-НЕ 5. Компенсация действия помехи происходит за счет одновременного воздействия заряда с трека частицы на компенсирующий транзистор 12 и формирования им импульса противоположной полярности на выход 22 элемента ИЛИ-НЕ по отношению к импульсу, возникающему от действия помехи со входа 47. Вывод заряда из объема полупроводника моделировался импульсом тока с постоянными временем нарастания 3 пс и спада 100 пс; моделирование осуществлялось с использованием САПР Cadence. Как показано на фиг. 4, при логическом маскировании изменение напряжения U47(t)=U55(t) на входе 47 не влияет на изменение напряжения U22=0 на выходе 22 логического элемента ИЛИ-НЕ 5 в интервале до 200 пс, т.е. пока напряжение на входе 48 элемента ИЛИ-НЕ 5 находится на уровне U48(t)=UИ.П=0.9 В. На фиг. 5 приведен пример, когда при состоянии U47="1" на входе 47 и состоянии U48="0" на входе 48 логического элемента ИЛИ-НЕ 5, когда логическое маскирование помехи по входу 47 с переходом от уровня U47=UИ.П к уровню U47=0 невозможно, повысить помехоустойчивость многовходового логического элемента позволяет компенсация помехи от воздействия одиночной частицы на стоковые pn-области запертых транзисторов 51 и 52 (или одного из них) за счет практически одновременного воздействия и на стоковую pn-область запертого компенсирующего транзистора 12. Это проиллюстрировано на фиг. 5. В обоих случаях результатом является сохранение состояния выхода 22 логического элемента ИЛИ-НЕ 5 на логическом уровне Y22=0. Всплеск сигнала U22(t) на выходе 22 (см. фиг. 5) амплитудой 0,3 В и длительностью 15 пс по уровню 0,1 В находится в диапазоне ниже уровня 0,5 В, который соответствует порогу переключения последующего логического элемента, что не влияет на состояние следующих за ним логических элементов. К тому же длительность импульса всплеска меньше типового значения задержки переключения логического элемента tЗ.ПЕР=15…25 пс.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры | 2018 |

|

RU2693685C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580071C1 |

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2013 |

|

RU2554849C2 |

| ТРИГГЕР КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ МИКРОСХЕМЫ | 2013 |

|

RU2541894C1 |

| БЛОК ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580072C1 |

| БАЗОВЫЙ ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1667574A1 |

| ВЫСОКОВОЛЬТНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР СО СТАТИЧЕСКОЙ ИНДУКЦИЕЙ | 2023 |

|

RU2805777C1 |

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079986C1 |

Изобретение относится к области вычислительной техники. Технический результат - повышение помехоустойчивости многовходового логического элемента при воздействии одиночной ядерной частицы. Для этого предложен многовходовой логический элемент комплементарной металл-оксид-полупроводниковой структуры декодера, который состоит из статических элементов ИЛИ-НЕ и статических элементов И-НЕ, соединенных между собой в цепочки чередующихся элементов так, что выходы элементов ИЛИ-НЕ соединены с входами последующих в цепочке элементов И-НЕ, выходы элементов И-НЕ соединены с входами последующих в цепочке элементов ИЛИ-НЕ. Многовходовой логический элемент снабжен компенсирующими транзисторами с каналами электронной проводимости и компенсирующими транзисторами с каналами дырочной проводимости. Стоковые области каждого компенсирующего транзистора размещены на кристалле интегральной микросхемы относительно стоковых областей транзисторов с каналами такой же проводимости каждого из предшествующих в цепочке элементов на расстоянии, обеспечивающем одновременное воздействие одиночной ядерной частицы на указанные области транзисторов. 2 з.п. ф-лы, 9 ил.

1. Многовходовой логический элемент комплементарной металл-оксид-полупроводниковой структуры декодера, состоящий из статических элементов ИЛИ-НЕ и статических элементов И-НЕ, соединенных между собой в цепочки чередующихся элементов так, что выходы элементов ИЛИ-НЕ соединены с входами последующих в цепочке элементов И-НЕ, выходы элементов И-НЕ соединены с входами последующих в цепочке элементов ИЛИ-НЕ, и размещенных на кристалле интегральной микросхемы, отличающийся тем, что он снабжен компенсирующими транзисторами с каналами электронной проводимости и компенсирующими транзисторами с каналами дырочной проводимости, выводы затворов компенсирующих транзисторов с каналами электронной проводимости соединены с выходами элементов И-НЕ и с входами последующих в цепочке элементов ИЛИ-НЕ, а выводы их стоков - с выходами последующих в цепочке элементов ИЛИ-НЕ, при этом выводы затворов компенсирующих транзисторов с каналами дырочной проводимости соединены с выходами элементов ИЛИ-НЕ и с входами последующих в цепочке элементов И-НЕ, а выводы их стоков - с выходами последующих в цепочке элементов И-НЕ и с входами последующих в цепочке элементов ИЛИ-НЕ, причем стоковые области каждого компенсирующего транзистора размещены на кристалле интегральной микросхемы относительно стоковых областей транзисторов с каналами такой же проводимости каждого из предшествующих в цепочке элементов на расстоянии, обеспечивающем одновременное воздействие одиночной ядерной частицы на указанные области транзисторов.

2. Многовходовой логический элемент по п. 1, отличающийся тем, что транзисторы с каналами электронной проводимости элементов И-НЕ и транзистор с каналом электронной проводимости последующего в цепочке элемента ИЛИ-НЕ, вход которого соединен с выводом затвора этого транзистора и с выходом элемента И-НЕ, образуют группы транзисторов с каналами электронной проводимости, стоковые области которых размещены на кристалле интегральной микросхемы на расстоянии друг от друга, обеспечивающем одновременное воздействие одиночной ядерной частицы на них, транзисторы с каналами дырочной проводимости одного из элементов ИЛИ-НЕ и транзистор с каналом дырочной проводимости одного из элементов И-НЕ, вход которого соединен с выводом затвора этого транзистора и с выходом одного из элементов ИЛИ-НЕ, образуют группы транзисторов с каналами дырочной проводимости, стоковые области которых размещены на кристалле интегральной микросхемы на расстоянии друг от друга, обеспечивающем одновременное воздействие одиночной ядерной частицы на них.

3. Многовходовой логический элемент по п. 1, отличающийся тем, что указанное расстояние, обеспечивающее одновременное воздействие одиночной ядерной частицы на указанные стоковые области транзисторов, равно минимальному расстоянию между указанными транзисторами, выбранному в соответствии с технологическим допуском.

| US 6668344 B1, 23.12.2003 | |||

| ТРИГГЕР КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ МИКРОСХЕМЫ | 2013 |

|

RU2541894C1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| Кабелеподвод к электротрактору | 1952 |

|

SU110543A1 |

Авторы

Даты

2017-04-12—Публикация

2015-12-25—Подача