Изобретение относится к области вычислительной техники и может быть использовано для реализации оперативной памяти в отказоустойчивых, радиационно-стойких микропроцессорных системах.

Известна ячейка статической оперативной памяти, содержащая два n-МОП транзистора, два p-МОП транзистора и два передающих транзистора - записи бита и записи инверсии бита (Two port 6T CMOS SRAM cell structure for low voltage VLSI SRAM with single-bit-line simultaneous read-and write access - SBLSRWA capability. Патент США №6118 689, 12.09.2000 г.).

Недостатком такого устройства является низкая отказо- и сбоеустойчивость в условиях радиации.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является ячейка статической оперативной памяти, содержащая группу из четырех транзисторов n-МОП, включающая первый, второй, третий, четвертый триггеры, группу из четырех транзисторов p-МОП, включающая первый, второй, третий, четвертый триггеры, первый и второй передающие транзисторы записи бита, первый и второй передающие транзисторы записи инверсии бита, вход напряжения питания, вход «Ноль вольт», вход значения бита, вход значения инверсии бита, вход записи, первый и второй выходы данных,

причем стоки всех четырех транзисторов группы транзисторов n-МОП объединены и подключены ко входу напряжения питания, истоки всех четырех транзисторов группы транзисторов p-МОП объединены и подключены ко входу «Ноль вольт», истоки всех четырех транзисторов группы транзисторов n-МОП подключены к стокам соответствующих четырех транзисторов группы транзисторов p-МОП, затвор первого транзистора из группы транзисторов n-МОП подключен к истоку второго транзистора этой группы, затвор второго транзистора из группы транзисторов n-МОП подключен к истоку третьего транзистора группы, затвор третьего транзистора из группы транзисторов n-МОП подключен к истоку четвертого транзистора группы, затвор четвертого транзистора из группы транзисторов n-МОП подключен к истоку первого транзистора группы, затвор первого транзистора из группы транзисторов p-МОП подключен к стоку первого передающего транзистора записи бита и стоку четвертого транзистора из группы транзисторов p-МОП, затвор второго транзистора из группы транзисторов p-МОП подключен к стоку первого передающего транзистора записи инверсии бита и стоку первого транзистора из группы транзисторов p-МОП, затвор третьего транзистора из группы транзисторов p-МОП подключен к стоку второго передающего транзистора записи бита и стоку второго транзистора из группы транзисторов p-МОП, затвор четвертого транзистора из группы транзисторов p-МОП подключен к стоку второго передающего транзистора записи инверсии бита и стоку третьего транзистора из группы транзисторов p-МОП, затворы первого и второго передающих транзисторов записи бита, первого и второго передающих транзисторов записи инверсии бита объединены и являются входом записи устройства, истоки первого и второго передающих транзисторов записи бита, являются соответственно входом значения бита, истоки первого и второго передающих транзисторов записи инверсии бита являются входом значения инверсии бита, стоки второго и четвертого транзисторов из группы транзисторов p-МОП являются соответственно первым и вторым выходами данных.

Недостатком известного устройства, принятого за прототип, является низкая отказоустойчивость относительно необратимых отказов транзисторов.

Это обусловлено следующими обстоятельствами.

Технические средства прототипа ориентированы (в случае попадания тяжелых заряженных частиц внутрь микросхемы при радиационном воздействии) на парирование сбоев памяти - SEU (Single Event Upset), кратковременно изменяющих состояние логических элементов. Для этого используется дублирование элементов памяти - DICE (Dual Inter_locked Storage).

При этом используются четыре инвертора вместо двух и обратная связь соответствующих двух триггеров заводится не со своего выхода, а с выхода дублирующего триггера.

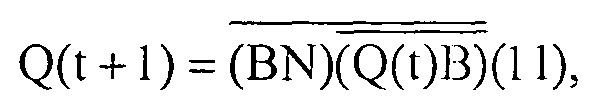

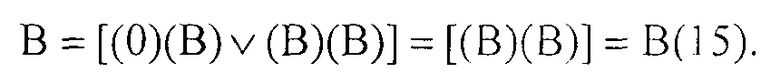

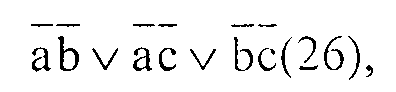

Для этого в каждом инверторе входы транзисторов n и p проводимостей «разнесены» в соответствие с выражением

где X - входной сигнал инвертора, причем, чтобы выход инвертора стал равен логической 1, необходимо N=P=0, для того, чтобы выход инвертора стал равен логическому 0, необходимо N=P=1. Противоположные значения N и Р запрещены, так как, при N=1, Р=0 оба транзистора инвертора закрыты и на выходе имеет место третье состояние (высокоимпедансное). При N=0, Р=1 оба транзистора открыты, что приводит к подключению шины питания на шину «0» вольт (Ground) - это короткое замыкание.

Таким образом, управление каждым инвертором ячейки-прототипа дублировано - как бы по N и по Р, с двух разных других инверторов, чтобы кратковременное изменение одного не привело к запоминанию неправильного значения, то есть необходимы одинаковые сигналы по N и по Р, чтобы изменить состояние ячейки.

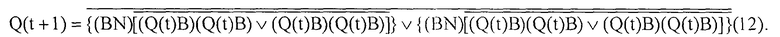

Каждый инвертор по своему выходу управляет двумя и управляется этими же двумя - Табл.1, система уравнений (2):

где Q′1(t) - функция выхода первого инвертора, Q1(t) - функция выхода второго инвертора, Q′2(t) - функция выхода третьего инвертора, Q2(t) - функция выхода четвертого инвертора.

Поэтому прототип, как дублированный триггер (DICE-SRAM) описывается двумя функциями переходов:

где Q1(t+1), Q2(t+1) - функции переходов первого (первый и второй инверторы) и второго (третий и четвертый инверторы) триггеров, Q1 - выход первого триггера, Q2 - выход второго триггера, B1, B2 - значения записываемого бита, BN1, BN2 - значения инверсии бита.

В случае сбоя одного из транзисторов одного из инверторов, «левое» или «правое» «плечо» выражений 3, 4 кратковременно принимает противоположное значение, но за счет обратной связи сбой не запоминается и состояние элемента восстанавливается.

Однако при воздействии заряженных частиц на КМОП транзисторы кроме сбоев, как восстанавливаемых обратимых событий - SEU (Single Event Upset - сбой триггера памяти), SET (Single Event Transient - кратковременное изменение состояния выхода логического элемента), возможны события типа - SEL (Single Event Latch) - тиристорного эффекта, требующего для восстановления обязательного снятия питания, а также возможны необратимые события - SEGR (Single Event Gate Rupture - «разрыв» вентиля, вызванный ионизацией вследствие тиристорного эффекта), SHE (Single Event Hard Error - необратимое изменение триггеров памяти).

Технические средства прототипа не позволяют парировать такие отказы.

Так, один из членов дизъюнкции, например (4), за счет отказа транзистора N или Р (выражение 1) может принять необратимое значение 0 или 1, что приводит к изменению функции, например:

Например,

здесь по закону поглощения «короткая» конъюнкция поглощает «длинную».

Задачей изобретения является повышение отказоустойчивости относительно необратимых отказов транзисторов.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем

группу из четырех транзисторов n-МОП, включающую первый, второй, третий, четвертый триггеры, группу из четырех транзисторов p-МОП, включающую первый, второй, третий, четвертый триггеры, первый и второй передающие транзисторы записи бита, первый и второй передающие транзисторы записи инверсии бита, вход напряжения питания, вход «Ноль вольт», вход значения бита, вход значения инверсии бита, вход записи, выход данных, причем стоки первого и третьего транзисторов из группы четырех транзисторов n-МОП объединены и подключены ко входу напряжения питания, истоки второго и четвертого транзисторов из группы четырех транзисторов n-МОП объединены и подключены к объединенным стокам первого и третьего транзисторов из группы четырех транзисторов p-МОП и являются вторым, инверсным выходом данных, истоки второго и четвертого транзисторов из группы четырех транзисторов p-МОП объединены и подключены ко входу «Ноль вольт», истоки первого и второго передающих транзисторов записи бита объединены и являются входом значения бита, истоки первого и второго передающих транзисторов записи инверсии бита объединены и являются входом значения инверсии бита, затворы первого и второго передающих транзисторов записи бита, первого и второго передающих транзисторов записи инверсии бита объединены и являются входом записи устройства,

дополнительно введены вторая группа из четырех транзисторов n-МОП, вторая группа из четырех транзисторов p-МОП, третий и четвертый передающие транзисторы записи бита, третий и четвертый передающие транзисторы записи инверсии бита, второй, инверсный, выход данных,

причем затворы третьего и четвертого передающих транзисторов записи бита, третьего и четвертого передающих транзисторов записи инверсии бита объединены и подключены ко входу записи устройства,

исток третьего передающего транзистора записи бита подключен к стоку первого передающего транзистора записи бита, а сток третьего передающего транзистора записи бита подключен к объединенным затворам транзисторов из группы четырех транзисторов p-МОП и группы четырех транзисторов n-МОП, которые подключены к выходу устройства, исток четвертого передающего транзистора записи бита подключен к стоку второго передающего транзистора записи бита, а его сток - к стоку третьего передающего транзистора записи бита, исток третьего передающего транзистора записи инверсии бита подключен к стоку первого передающего транзистора записи инверсии бита, а сток третьего передающего транзистора записи инверсии бита подключен к объединенным затворам транзисторов из второй группы четырех транзисторов p-МОП и второй группы четырех транзисторов n-МОП, которые подключены ко второму, инверсному выходу устройства, исток четвертого передающего транзистора записи инверсии бита подключен к стоку второго передающего транзистора записи инверсии бита, а его сток - к стоку третьего передающего транзистора записи бита, истоки первого и третьего транзисторов из второй группы четырех транзисторов n-МОП объединены и подключены к стокам второго и четвертого транзисторов из группы четырех транзисторов n-МОП, истоки первого и третьего транзисторов из группы четырех транзисторов p-МОП подключены к стокам второго и четвертого транзисторов из группы четырех транзисторов p-МОП, истоки первого и третьего транзисторов из второй группы четырех транзисторов p-МОП подключены к стокам второго и четвертого транзисторов из второй группы четырех транзисторов p-МОП, истоки которых объединены и подключены ко входу «Ноль вольт» устройства, стоки первого и третьего транзисторов из второй группы четырех транзисторов p-МОП объединены и подключены к первому выходу устройства и истокам второго и четвертого транзисторов из второй группы четырех транзисторов n-МОП, стоки которых объединены и подключены к истокам первого и третьего транзисторов из второй группы четырех транзисторов n-МОП, стоки которых объединены и подключены ко входу напряжения питания устройства.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения:

содержит группу из четырех транзисторов n-МОП, включающую первый, второй, третий, четвертый триггеры, группу из четырех транзисторов p-МОП, включающую первый, второй, третий, четвертый триггеры, первый и второй передающие транзисторы записи бита, первый и второй передающие транзисторы записи инверсии бита, вход напряжения питания, вход «Ноль вольт», вход значения бита, вход значения инверсии бита, вход записи, выход данных.

Признаки заявляемого технического решения, отличительные от прототипа: содержит вторую группу из четырех транзисторов n-МОП, вторую группу из четырех транзисторов p-МОП, третий и четвертый передающие транзисторы записи бита, третий и четвертый передающие транзисторы записи инверсии бита, второй, инверсный, выход данных.

Отличительные признаки в сочетании с известными позволяют повысить отказоустойчивость устройства относительно необратимых отказов транзисторов, путем реализации логических функций, толерантных к константным или инверсным отказам одной переменной.

Введение второй группы из четырех транзисторов n-МОП позволяет реализовать отказо- и сбоеустойчивое подключение шины (входа) напряжения питания на выход второго триггера - выход данных ячейки памяти путем реализации функции

где x - переменные состояния 1, 2, 3, 4 транзисторов группы. Отказ одного любого транзистора не изменяет функцию (7).

Введение второй группы из четырех транзисторов p-МОП позволяет реализовать отказо- и сбоеустойчивое подключение на выход второго триггера - выход данных ячейки памяти шины (входа) «Ноль вольт», путем реализации функции, двойственной функции (7);

где y - переменные состояния 1, 2, 3, 4 транзисторов второй группы из четырех транзисторов p-МОП. Отказ одного любого транзистора не изменяет функцию (8) и обеспечивает ортогональность выражений (7), (8), необходимую доля функционирования КМОП вентиля.

Введение новых связей для первой группы из четырех транзисторов n-МОП, включающей первый, второй, третий, четвертый триггеры, позволяет реализовать отказо- и сбоеустойчивое подключение шины (входа) напряжения питания на выход первого триггера - на второй, инверсный выход данных ячейки памяти путем реализации функции, подобной (7).

Введение новых связей для первой группы из четырех транзисторов p-МОП, включающей первый, второй, третий, четвертый триггеры, позволяет реализовать отказо- и сбоеустойчивое подключение на выход второго триггера - выход данных ячейки памяти шины (входа) «Ноль вольт», путем реализации функции, подобной (8).

Введение третьего и четвертого передающих транзисторов записи бита и новых связей для первого и второго транзисторов записи бита позволяет реализовать отказо- и сбоеустойчивое подключение на вход первого инвертора входа значения бита путем реализации функции

где b = переменные состояния 1, 2, 3, 4 транзисторов записи бита.

Отказ одного любого транзистора не изменяет функцию (9) и позволяет даже в условиях отказа одного любого транзистора обеспечить подачу информации значения бита на вход первого инвертора ячейки.

Введение третьего и четвертого передающих транзисторов записи инверсии бита и новых связей для первого и второго транзисторов записи инверсии бита позволяет реализовать отказо- и сбоеустойчивое подключение на вход первого инвертора входа значения инверсии бита путем реализации функции

где b' = переменные состояния 1, 2, 3, 4 транзисторов записи инверсии бита.

Таким образом, введение новых элементов и связей позволяет реализовать на первом инверторе (первая группа из четырех транзисторов n-МОП, первая группа из четырех транзисторов p-МОП) и втором инверторе (вторая группа из четырех транзисторов n-МОП, вторая группа из четырех транзисторов p-МОП) SR триггер - ячейку статической оперативной памяти, которая может функционировать при шести одновременных отказах:

1.) невосстанавливаемый отказ одного транзистора в первой группе из четырех транзисторов n-МОП;

2.) невосстанавливаемый отказ одного транзистора в первой группе из четырех транзисторов p-МОП;

3.) невосстанавливаемый отказ одного транзистора во второй группе из четырех транзисторов n-МОП;

4.) невосстанавливаемый отказ одного транзистора во второй группе из четырех транзисторов p-МОП;

5.) невосстанавливаемый отказ одного из четырех транзисторов записи бита;

6.) невосстанавливаемый отказ одного из четырех транзисторов записи инверсии бита.

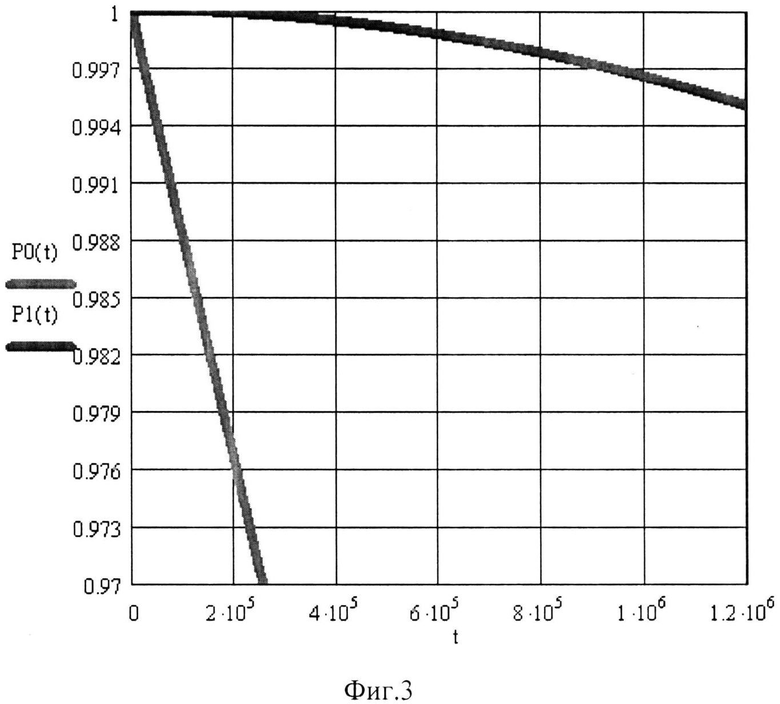

На Фиг.1 изображена схема электрическая структурная предлагаемой ячейки статической оперативной памяти.

На Фиг. 2 изображены графики изменения вероятности бессбойной работы прототипа и вероятности бессбойной работы предлагаемого устройства при интенсивности сбоев λс=10-3.

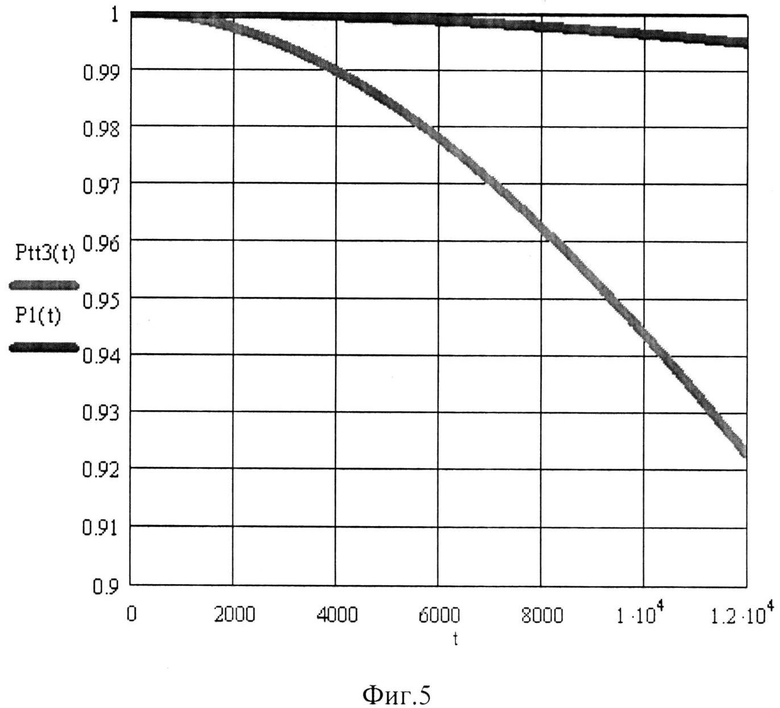

На Фиг. 3 изображены графики изменения вероятности безотказной работы (при невосстанавливаемых отказах) прототипа и вероятности безотказной работы предлагаемого устройства при интенсивности отказов λо=10-8.

На Фиг. 4 изображены графики изменения вероятностей безотказной работы троированной шеститранзисторной ячейки с мажоритарным элементом (Ptt) и предлагаемой ячейки (Р1) при интенсивности отказов транзистора λт=10-8.

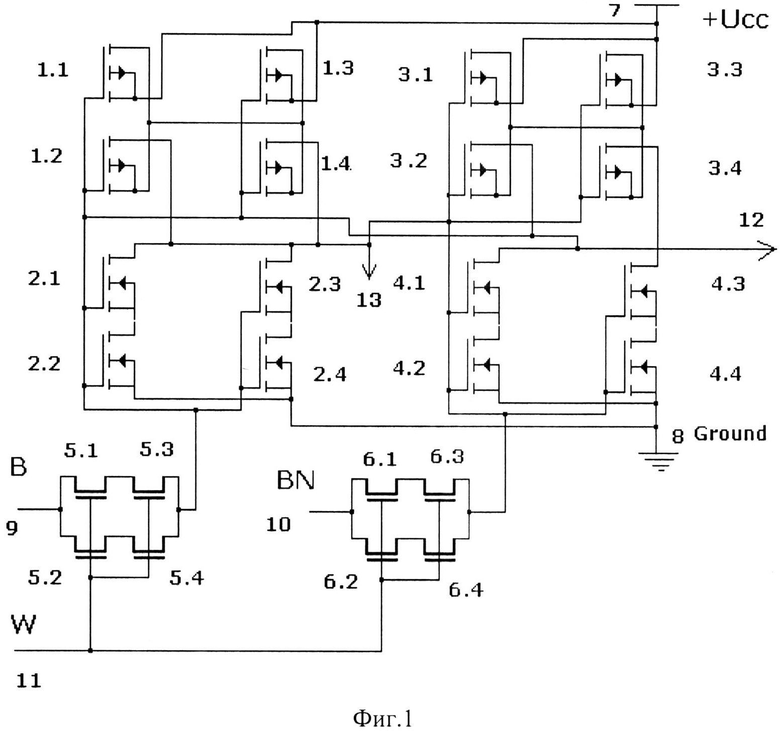

На Фиг. 5 изображены графики изменения вероятностей безотказной работы троированной шеститранзисторной ячейки с тремя мажоритарными элементами (Ptt3) и предлагаемой ячейки (Р1) при интенсивности отказов транзистора λт=10-8.

Ячейка статической оперативной памяти, содержит

группу 1 из четырех транзисторов n-МОП, включающую первый 1.1, второй 1.2, третий 1.3, четвертый 1.4 транзисторы, группу 2 из четырех транзисторов n-МОП, включающую первый 2.1, второй 2.2, третий 2.3, четвертый 2.4 транзисторы, вторую группу из четырех транзисторов n-МОП 3, включающую первый 3.1, второй 3.2, третий 3.3, четвертый 3.4 транзисторы, вторую группу из четырех транзисторов p-МОП 4, включающую первый 4.1, второй 4.2, третий 4.3, четвертый 4.4 транзисторы, первый 5.1, второй 5.2, третий 5.3 и четвертый 5.4 передающие транзисторы записи бита, первый 6.1, второй 6.2 третий 6.3 и четвертый 6.4 передающие транзисторы записи инверсии бита, вход напряжения питания 7, вход «Ноль вольт» 8, вход значения бита 9, вход значения инверсии бита 10, вход записи 11, выход данных 12, второй, инверсный, выход данных 13.

Стоки первого 1.1 и третьего 1.3 транзисторов из группы 1 четырех транзисторов n-МОП объединены и подключены ко входу напряжения питания 7. Истоки второго 1.2 и четвертого 1.4 транзисторов из группы 1 четырех транзисторов n-МОП объединены и подключены к объединенным стокам первого 2.1 и третьего 2.3 транзисторов из группы 2 четырех транзисторов p-МОП и являются вторым, инверсным выходом устройства 13.

Истоки второго 2.2 и четвертого 2.4 транзисторов из группы 2 четырех транзисторов p-МОП объединены и подключены ко входу «Ноль вольт» 8.

Истоки первого 5.1 и второго 5.2 передающих транзисторов записи бита объединены и являются входом значения бита 9.

Истоки первого 6.1 и второго 6.2 передающих транзисторов записи инверсии бита объединены и являются входом значения инверсии бита 10.

Затворы первого 5.1 и второго 5.2 передающих транзисторов записи бита, первого 6.1 и второго 6.2 передающих транзисторов записи инверсии бита объединены и являются входом записи устройства 11.

Затворы третьего 5.3 и четвертого 5.4 передающих транзисторов записи бита, третьего 6.3 и четвертого 6.4 передающих транзисторов записи инверсии бита объединены и также подключены ко входу записи устройства 11.

Исток третьего передающего транзистора записи бита 5.3 подключен к стоку первого передающего транзистора 5.1 записи бита. Сток третьего передающего транзистора 5.3 записи бита подключен к объединенным затворам транзисторов 2.1, 2.2, 2.3, 2.4 из группы 2 четырех транзисторов p-МОП и затворам транзисторов 1.1, 1.2, 1.3, 14 группы 1 четырех транзисторов n-МОП, которые подключены к выходу устройства 12.

Исток четвертого передающего транзистора записи бита 5.4 подключен к стоку второго передающего транзистора записи бита 5.2, а его сток - к стоку третьего передающего транзистора записи бита 5.3.

Исток третьего передающего транзистора записи инверсии бита 6.3 подключен к стоку первого передающего транзистора записи инверсии бита 6.1, а сток третьего передающего транзистора записи инверсии бита 6.3 подключен к объединенным затворам транзисторов 4.1, 4.2, 4.3, 4.4 из второй группы 4 четырех транзисторов p-МОП и транзисторов 3.1, 3.2, 3.3, 3.4 второй группы 3 четырех транзисторов n-МОП, которые подключены ко второму инверсному выходу устройства 13.

Исток четвертого передающего транзистора записи инверсии бита 6.4 подключен к стоку второго передающего транзистора записи инверсии бита 6.2, а его сток - к стоку третьего передающего транзистора записи бита 6.3.

Стоки первого 4.1 и третьего 4.3 транзисторов из второй группы 4 четырех транзисторов n-МОП объединены и подключены к истокам второго 3.2 и четвертого 3.4 транзисторов из второй группы 3 четырех транзисторов n-МОП.

Истоки первого 2.1 и третьего 2.3 транзисторов из группы четырех транзисторов p-МОП подключены к стокам соответственно второго 2.2 и четвертого 2.4 транзисторов из группы четырех транзисторов p-МОП.

Истоки первого 4.1 и третьего 4.3 транзисторов из второй группы четырех транзисторов p-МОП подключены соответственно к стокам второго 4.2 и четвертого 4.4 транзисторов из второй группы 4 четырех транзисторов p-МОП, истоки которых объединены и подключены ко входу «Ноль вольт» 8 устройства.

Стоки первого 4.1 и третьего 4.3 транзисторов из второй группы 4 четырех транзисторов p-МОП объединены и подключены к первому выходу устройства 12 и истокам второго 3.2 и четвертого 3.4 транзисторов из второй группы 3 четырех транзисторов n-МОП, стоки которых объединены и подключены соответственно к истокам первого 3.1 и третьего 3.3 транзисторов из второй группы 3 четырех транзисторов n-МОП, стоки которых объединены и подключены ко входу напряжения питания 7 устройства.

Устройство работает в следующих режимах.

1. Запись информации «0», «1». В этом режиме на вход записи 11 поступает сигнал логической единицы. Предварительно на входе значения бита 9 устанавливается значение бита, на вход инверсии бита 10 - значение инверсии бита. Сигнал записи 11 активирует затворы первого 5.1, второго 5.2, третьего 5.3 и четвертого 5.4 передающих транзисторов записи бита, первого 6.1, второго 6.2 третьего 6.3 и четвертого 6.4 передающих транзисторов записи инверсии бита. Вследствие этого значение бита поступает на вход первого инвертора (первая группа 1 из четырех транзисторов n-МОП, первая группа 2 из четырех транзисторов p-МОП), а значение инверсии бита - на вход второго инвертора (вторая группа 3 из четырех транзисторов n-МОП, вторая группа 4 из четырех транзисторов p-МОП). В условиях воздействия заряженных частиц в случае восстанавливаемого или невосстанавливаемого отказа одного передающего транзистора записи бита: 5.1 или 5.2 или 5.3 или 5.4 и/или восстанавливаемого или невосстанавливаемого отказа одного передающего транзистора записи инверсии бита 6.1 или 6.2 или 6.3 или 6.4 за счет реализации логических функций (7), (8) требуемые сигналы все равно поступят на вход первого и второго инверторов. Поэтому устройство как автомат Мура реализует требуемую функцию переходов:

Где: Q(t+1) - последующее состояние, Q(t) - текущее состояние, BN - значение инверсии бита на входе 10, В - значение бита на входе 9; Q(t)B,  - монтажное «И» на входах инверторов (первый инвертор - группы 1, 2; второй инвертор - группы 3, 4). С учетом (7) функция (11) представляет собой выражение:

- монтажное «И» на входах инверторов (первый инвертор - группы 1, 2; второй инвертор - группы 3, 4). С учетом (7) функция (11) представляет собой выражение:

причем, с учетом (9), (10):

В выражении (12) переменным BN соответствуют транзисторы 6.1…6.4, а переменным В - транзисторы 5.1…5.4.

Таким образом, любое изменение одного транзистора 6.1…6.4 и/или одного транзистора 5.1…5.4 не изменит (12)-(14).

Допустим, транзистор 5.1 будет постоянно закрыт, тогда:

Допустим, транзистор 5.4 будет постоянно открыт, тогда:

В выражении (10) члену в квадратных скобках

соответствуют транзисторы 1.1…1.4 в схеме первого инвертора, для подключения напряжения питания 7 на второй инверсный выход 13 и транзисторы 2.1…2.4 для подключения шины «Ноль вольт» 8. Аналогично вышеописанному любое изменение одного транзистора 1.1…1.4 и/или одного транзистора 2.1…2.4 не изменит (13).

Выражению учетверенной инверсии (фигурные скобки в (12)):

соответствуют транзисторы 3.1…3.4 в схеме второго инвертора, для подключения напряжения питания 7 на выход 12 и транзисторы 4.1…4.4 для подключения шины «Ноль вольт» 8.

Аналогично вышеописанному любое изменение одного транзистора 3.1…3.4 и/или одного транзистора 4.1…4.4 не изменит (10).

Таким образом, может быть одновременно 6 транзисторов с отказами и сбоями.

Допустим Q(t) - текущее состояние равно 0, BN - значение инверсии бита на входе 10 равно 0, В - значение бита на входе 9 равно 1.

Тогда с учетом (11):

то есть ячейка памяти установится в состояние логической единицы.

При записи логического нуля, если Q(t) - текущее состояние равно 1, BN - значение инверсии бита на входе 10 равно 1, В - значение бита на входе 9 равно 0, получаем

2. Хранение информации «0», «1».

В этом режиме на затворы первого 5.1, второго 5.2, третьего 5.3 и четвертого 5.4 передающих транзисторов записи бита, первого 6.1, второго 6.2 третьего 6.3 и четвертого 6.4 передающих транзисторов записи инверсии бита подан сигнал логического нуля, поэтому в выражении

исключается монтажное «И» на входах инверторов (первый инвертор - группы 1, 2; второй инвертор - группы 3, 4), то есть функция переходов примет вид:

Допустим, в устройство записана логическая единица, тогда на выходе 12 (Q) установлена логическая единица, которая удерживается на входе первого инвертора (группы транзисторов 1, 2), обеспечивая формирование на его выходе и на втором инверсном выходе устройства 13 логического нуля, который, в свою очередь, поступая на вход второго инвертора (группы транзисторов 3, 4), удерживает на его выходе логическую единицу.

В случае если в устройство записан логический ноль, тогда на выходе 12 (Q) установлен логический ноль, который удерживается на входе первого инвертора (группы транзисторов 1, 2), обеспечивая формирование на его выходе и на втором инверсном выходе устройства 13 логической единицы, которая, в свою очередь, поступая на вход второго инвертора (группы транзисторов 3, 4), удерживает на его выходе логический ноль.

Аналогично вышеописанному, в режиме хранения, любой отказ, в том числе невосстанавливаемый, фатальный, одного транзистора 3.1…3.4 и/или одного транзистора 4.1…4.4; одного транзистора 6.1…6.4 и/или одного транзистора 5.1…5.4 (всего четыре отказа в режиме хранения) - не изменит информации в ячейке.

Оценка технико-экономической эффективности

Технические средства прототипа обеспечивают парирование сбоев памяти - SEU (Single Event Upset), кратковременно изменяющих состояние логических элементов, то есть обеспечивают вероятность правильной записи и хранения информации при сбое одного транзистора:

где λс - интенсивность сбоев, и не обеспечивает парирование отказов:

где λо - интенсивность отказов.

Как показано выше в разделе функционирования устройства, для того, чтобы изменилось состояние триггера (ячейки памяти) Q (выход 12), либо инверсии Q (второй, инверсный выход 13) необходимо, чтобы одновременно возникли отказы (сбои) двух и более транзисторов 1.1…1.4 или 2.1…2.4 или 3.1…3.4 или 4.1…4.4 или 5.1…5.4 или 6.1…6.4, то есть предлагаемое устройство обеспечивает парирование как сбоев, так и отказов с вероятностями бессбойной и безотказной работы:

Сравнение вероятности бессбойной работы прототипа - выражений (21) и предлагаемого устройства (23) - представлено на Фиг 2 при λс=10-3.

Сравнение вероятности безотказной работы (при невосстанавливаемых отказов) прототипа - выражений (22) и вероятности безотказной работы предлагаемого устройства (24) представлено на Фиг 2 при λо=10-8.

Таким образом, предлагаемое устройство обеспечивает большую отказоустойчивость относительно необратимых отказов транзисторов.

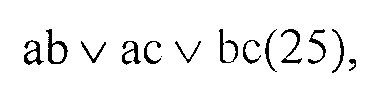

Покажем, что предлагаемое устройство обеспечивает выигрыш и относительно троированной шеститранзисторной ячейки - TMR (Triple Modular Redundancy), которое также позволяет парировать не только сбои - SEU (Single Event Upset), но и отказы SEE (Single Event Effect) - в одном из трех каналов.

TMR или троирование или мажоритирование шеститранзисторной ячейки требует 6×3=18 транзисторов.

Необходима дополнительно схема мажоритирования, то есть реализации мажоритарной функции:

где a, b, c - выходы трех каналов - трех ячеек, что требует, в лучшем случае, 12 транзисторов для реализации инверсного мажоритара:

(подобные имеются в библиотеках базовых матричных кристаллов -БМК) и 2 транзистора для выходного инвертора - всего 32 транзистора, путь сигнала 2+2+1+3=8 транзисторов.

При реализации мажоритара на элементах 2И-НЕ получим 14+24=38 транзисторов, путь 2+2+1+8=13 транзисторов.

Для предлагаемой ячейки получаем 24 транзистора. Путь 4+4+2=10 транзисторов.

Сравним предлагаемое устройство и троированную шеститранзисторную ячейку - TMR (Triple Modular Redundancy).

Зададим λт - интенсивность отказов (сбоев) транзисторов.

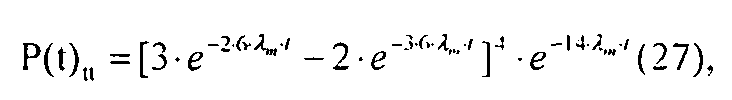

Тогда для троированной схемы с одним мажоритарным элементом (мажоритаром):

где λт - интенсивность отказов транзистора.

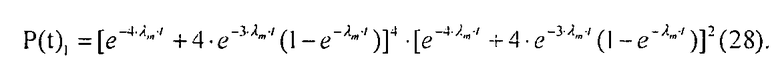

Для предлагаемой ячейки получаем:

Сравнение вероятностей безотказной (бессбойной) работы троированной шеститранзисторной ячейки с мажоритарным элементом (Ptt) и предлагаемой ячейки (Р1) показан на Фиг.4

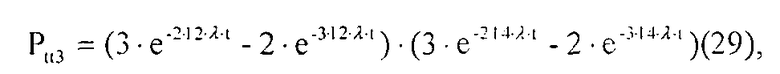

Для увеличения вероятности безотказной работы используют три мажоритара для увеличения:

Сравнение вероятностей безотказной (бессбойной) работы троированной шеститранзисторной ячейки с тремя мажоритарными элементами (Ptt3) и предлагаемой ячейки (Р1) показан на Фиг.5.

Таким образом, предложенная ячейка статической оперативной памяти выигрывает не только по отношению к прототипу, но и у троированных вариантов TMR (Triple Modular Redundancy) как по сложности, так и по вероятности безотказной работы, незначительно проигрывая по задержке.

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2010 |

|

RU2438234C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2012 |

|

RU2496227C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении отказоустойчивости относительно необратимых отказов транзисторов. Ячейка статической оперативной памяти содержит группу из четырех транзисторов n-МОП, включающую первый, второй, третий, четвертый триггеры, группу из четырех транзисторов p-МОП, включающую первый, второй, третий, четвертый триггеры, первый и второй передающие транзисторы записи бита, первый и второй передающие транзисторы записи инверсии бита, вход напряжения питания, вход «Ноль вольт», вход значения бита, вход значения инверсии бита, вход записи, выход данных, причем дополнительно введены вторая группа из четырех транзисторов n-МОП, вторая группа из четырех транзисторов p-МОП, третий и четвертый передающие транзисторы записи бита, третий и четвертый передающие транзисторы записи инверсии бита, второй инверсный выход данных. 5 ил., 1 табл.

Ячейка статической оперативной памяти, содержащая

группу из четырех транзисторов n-МОП, включающую первый, второй, третий, четвертый триггеры, группу из четырех транзисторов p-МОП, включающую первый, второй, третий, четвертый триггеры, первый и второй передающие транзисторы записи бита, первый и второй передающие транзисторы записи инверсии бита, вход напряжения питания, вход «Ноль вольт», вход значения бита, вход значения инверсии бита, вход записи, выход данных, причем стоки первого и третьего транзисторов из группы четырех транзисторов n-МОП объединены и подключены ко входу напряжения питания, истоки второго и четвертого транзисторов из группы четырех транзисторов n-МОП объединены и подключены к объединенным стокам первого и третьего транзисторов из группы четырех транзисторов p-МОП и являются вторым инверсным выходом данных, истоки второго и четвертого транзисторов из группы четырех транзисторов p-МОП объединены и подключены ко входу «Ноль вольт», истоки первого и второго передающих транзисторов записи бита объединены и являются входом значения бита, истоки первого и второго передающих транзисторов записи инверсии бита объединены и являются входом значения инверсии бита, затворы первого и второго передающих транзисторов записи бита, первого и второго передающих транзисторов записи инверсии бита объединены и являются входом записи устройства,

отличающаяся тем, что, с целью повышения отказоустойчивости относительно необратимых отказов транзисторов, дополнительно введены вторая группа из четырех транзисторов n-МОП, вторая группа из четырех транзисторов p-МОП, третий и четвертый передающие транзисторы записи бита, третий и четвертый передающие транзисторы записи инверсии бита, второй инверсный выход данных, причем затворы третьего и четвертого передающих транзисторов записи бита, третьего и четвертого передающих транзисторов записи инверсии бита объединены и подключены ко входу записи устройства, исток третьего передающего транзистора записи бита подключен к стоку первого передающего транзистора записи бита, а сток третьего передающего транзистора записи бита подключен к объединенным затворам транзисторов из группы четырех транзисторов p-МОП и группы четырех транзисторов n-МОП, которые подключены к выходу устройства,

исток четвертого передающего транзистора записи бита подключен к стоку второго передающего транзистора записи бита, а его сток - к стоку третьего передающего транзистора записи бита, исток третьего передающего транзистора записи инверсии бита подключен к стоку первого передающего транзистора записи инверсии бита, а сток третьего передающего транзистора записи инверсии бита подключен к объединенным затворам транзисторов из второй группы четырех транзисторов p-МОП и второй группы четырех транзисторов n-МОП, которые подключены ко второму, инверсному выходу устройства, исток четвертого передающего транзистора записи инверсии бита подключен к стоку второго передающего транзистора записи инверсии бита, а его сток - к стоку третьего передающего транзистора записи бита, истоки первого и третьего транзисторов из второй группы четырех транзисторов n-МОП объединены и подключены к стокам второго и четвертого транзисторов из группы четырех транзисторов n-МОП, истоки первого и третьего транзисторов из группы четырех транзисторов p-МОП подключены к стокам второго и четвертого транзисторов из группы четырех транзисторов p-МОП, истоки первого и третьего транзисторов из второй группы четырех транзисторов p-МОП подключены к стокам второго и четвертого транзисторов из второй группы четырех транзисторов p-МОП, истоки которых объединены и подключены ко входу «Ноль вольт» устройства, стоки первого и третьего транзисторов из второй группы четырех транзисторов p-МОП объединены и подключены к первому выходу устройства и истокам второго и четвертого транзисторов из второй группы четырех транзисторов n-МОП, стоки которых объединены и подключены к истокам первого и третьего транзисторов из второй группы четырех транзисторов n-МОП, стоки которых объединены и подключены ко входу напряжения питания устройства.

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| US 8014184 B1, 06.09.2011 | |||

| US 7251150 B2, 31.07.2007 | |||

| Насадка на краскораспылительную головку для окраски внутренних глухих полостей цилиндрических изделий | 1957 |

|

SU111279A1 |

Авторы

Даты

2016-01-20—Публикация

2014-03-21—Подача