Область техники, к которой относится изобретение

Изобретение относится к радиотехнике, автоматике и вычислительной технике и может быть использовано для формирования высокостабильных и высокоточных сигналов с перестраиваемыми параметрами.

Уровень техники

Известен цифровой формирователь сигнала с линейной частотной модуляцией (авторское свидетельство СССР №1099407, М. Кл. H04L 27/12, опубл. 23.06.1984 г.), основанный на предварительном формировании прямоугольных импульсов соответствующей длительности и их последующей фильтрации. Недостатком такого формирователя является низкая точность, не предусмотрена возможность получения когерентных квадратурных сигналов.

Известен цифровой вычислительный синтезатор с квадратурными выходами (патент РФ №2294054, М. Кл. H03L 7/18, опубл. 20.02.2007), основанный на предварительном формировании ступенчатых сигналов треугольной формы с последующей аналоговой фильтрацией. Недостатком такого формирователя является низкая точность.

Наиболее близким к предлагаемому техническому решению является техническое решение, представленное в патенте ЕР 0528565 "Digital chirp generator systems", G06F 1/03, H03B 23/00, опубл. 30.07.1992, в котором заранее вычислены и записаны в постоянные запоминающие устройства отсчеты гармонических сигналов, сдвинутых по фазе на π/2, ЛЧМ-сигналы в котором формируются за счет формирования при помощи двойной рекурсии соответствующей адресации памяти. Недостатком такого решения является чрезмерно большой объем памяти для обеспечения высокой точности, сложность перестройки параметров ЛЧМ-сигнала.

Сущность изобретения

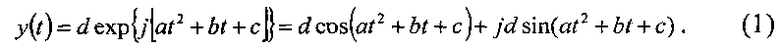

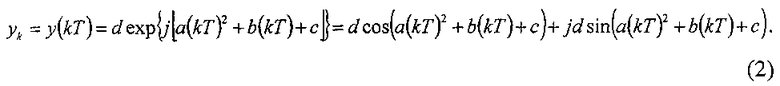

Предлагаемое устройство предназначено для вычисления отсчетов ЛЧМ-сигнала

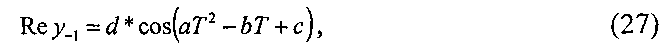

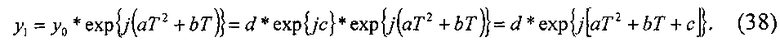

с интервалом дискретизации T в виде

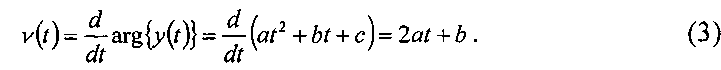

Мгновенная частота генерируемого сигнала v(t) изменяется по линейному закону:

Мгновенная амплитуда сигнала равна d. Начальная фаза равна с.

Начальная мгновенная частота формируемого ЛЧМ-сигнала равна

Длительность сигнала равна τ.

Конечная мгновенная частота равна

Соответственно девиация равна

а база сигнала равна

С учетом дискретизации по времени длительность сигнала равна

где

- целая часть от деления τ на T (число вычисляемых отсчетов сигнала).

Цифровой рекурсивный формирователь сигналов с линейной частотной модуляцией содержит первый и второй регистры, соединенные соответственно с первым и вторым ключами, которые соединены соответственно с входами установки начальных условий первого и второго блоков задержки на один интервал дискретизации. Перед началом работы формирователя в эти блоки задержки из первого и второго регистров переписываются начальные условия, равные соответственно

Эти начальные условия представляют собой действительную и мнимую часть комплексного числа

Эти числа переписываются в первый и второй блоки задержки из первого и второго регистров путем замыкания первого и второго ключей, которые после записи размыкаются.

Выход первого блока задержки соединен с первыми входами первого и второго блоков умножения, а выход второго блока задержки соединен с первыми входами третьего и четвертого блоков умножения. В состав формирователя входят также третий регистр, выход которого соединен с вторыми входами первого и третьего блоков умножения, а также четвертый регистр, выход которого соединен с вторыми входами второго и четвертого блоков умножения.

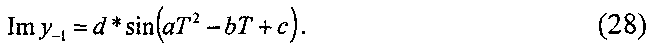

Первый блок задержки предназначен для циклического хранения отсчетов Rewk (k=0, 1, …, N), являющихся действительной частью комплексных отсчетов wk (k=0, 1, …, N). Второй блок задержки предназначен для циклического хранения отсчетов Imwk (k=0, 1, …, N), являющихся мнимой частью комплексных отсчетов wk (k=0, 1, …, N).

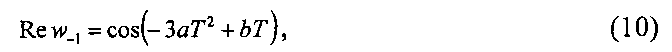

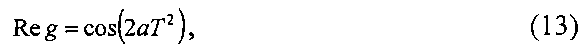

В третьем и четвертом регистрах хранятся числа, равные соответственно

Эти числа представляют собой действительную и мнимую части комплексного числа

На выходе первого блока умножения циклически вычисляется произведение

На выходе второго блока умножения циклически вычисляется произведение

На выходе третьего блока умножения циклически вычисляется произведение

На выходе четвертого блока умножения циклически вычисляется произведение

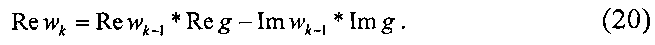

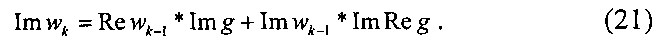

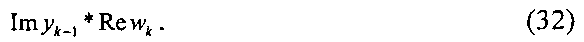

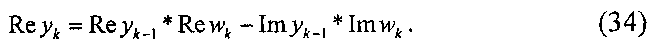

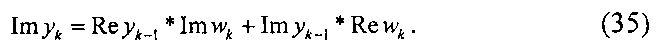

Выход первого блока умножения соединен с суммирующим входом первого блока вычитания, а выход четвертого блока умножения соединен с входом вычитания первого блока вычитания. Первый блок вычитания вычисляет действительную часть комплексного отсчета wk (k=0, 1, …, N):

Выход третьего блока умножения соединен с первым входом первого сумматора, а выход второго блока умножения соединен с вторым входом первого сумматора. Первый сумматор вычисляет мнимую часть комплексного отсчета wk (k=0, 1, …, N):

Выход первого блока вычитания соединен с информационным входом первого блока задержки, а выход первого сумматора соединен с информационным входом второго блока задержки.

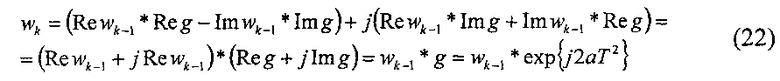

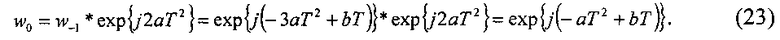

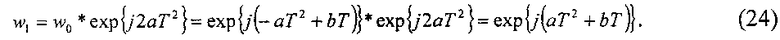

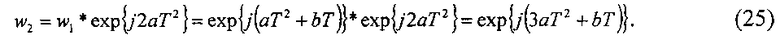

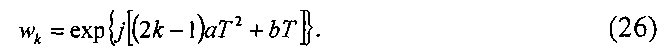

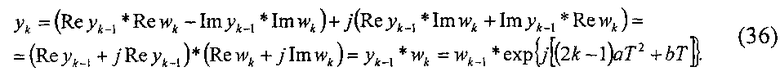

Таким образом, на выходе первого блока вычитания и на выходе первого сумматора в цикле вычисляются соответственно действительная и мнимая части комплексных отсчетов, равных

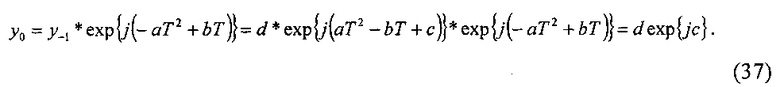

Если k=0, то

Если k=1, то

Если k=2, то

В общем случае

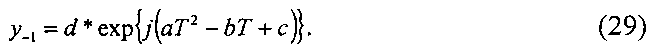

Цифровой рекурсивный формирователь сигналов с линейной частотной модуляцией содержит также пятый и шестой регистры, соединенные соответственно с третьим и четвертым ключами, которые соединены соответственно с входами установки начальных условий третьего и четвертого блоков задержки на один интервал дискретизации. Перед началом работы формирователя в эти блоки задержки из пятого и шестого регистров переписываются начальные условия, равные соответственно

Эти начальные условия представляют собой действительную и мнимую часть комплексного числа

Эти числа переписываются в третий и четвертый блоки задержки из пятого и шестого регистров путем замыкания третьего и четвертого ключей, которые после записи размыкаются.

Выход третьего блока задержки соединен с первыми входами пятого и шестого блоков умножения, а выход четвертого блока задержки соединен с первыми входами седьмого и восьмого блоков умножения. Выход первого блока вычитания соединен с вторыми входами пятого и седьмого блоков умножения, а выход первого сумматора соединен с вторыми входами шестого и восьмого блоков умножения.

Третий блок задержки предназначен для циклического хранения отсчетов Reyk (k=0, 1, …, N), являющихся действительной частью комплексных отсчетов yk (k=0, 1, …, N). Четвертый блок задержки предназначен для циклического хранения отсчетов Imyk (k=0, 1, …, N), являющихся мнимой частью комплексных отсчетов yk (k=0, 1, …, N).

На выходе пятого блока умножения циклически вычисляется произведение

На выходе шестого блока умножения циклически вычисляется произведение

На выходе седьмого блока умножения циклически вычисляется произведение

На выходе восьмого блока умножения циклически вычисляется произведение

Выход пятого блока умножения соединен с суммирующим входом второго блока вычитания, а выход восьмого блока умножения соединен с входом вычитания первого блока вычитания. Первый блок вычитания вычисляет действительную часть комплексного отсчета yk (k=0, 1, …, N):

Выход седьмого блока умножения соединен с первым входом второго сумматора, а выход шестого блока умножения соединен с вторым входом второго сумматора. Первый сумматор вычисляет мнимую часть комплексного отсчета wk (k=0, 1, …, N):

Выход второго блока вычитания соединен с входом третьего блока задержки, а выход второго сумматора соединен с информационным входом четвертого блока задержки.

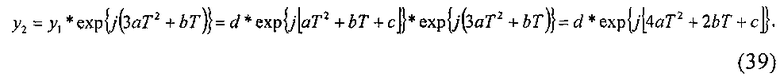

Таким образом, на выходе второго блока вычитания и на выходе второго сумматора в цикле вычисляются соответственно действительная и мнимая части комплексных отсчетов, равных

Если k=0, то

Если k=1, то

Если k=2, то

В общем случае

Таким образом, на выходе второго блока вычитания формируются отсчеты синфазной составляющей комплексного ЛЧМ-сигнала

а на выходе второго сумматора формируются отсчеты квадратурной составляющей комплексного ЛЧМ-сигнала

Техническим результатом описываемого технического решения является уменьшение объема памяти предлагаемого устройства, подлежащего изменению при перестройке параметров, и, тем самым, увеличение скорости перестройки. Объем памяти предлагаемого устройства всего шесть регистров, в то время как в прототипе объем памяти определяется дискретом представления синусоидального и косинусоидального сигналов, записанных в табличную память, при необходимости перестройки параметров сигнала необходимо пересчитывать и переписывать всю табличную память, в то время как в предлагаемом техническом решении необходимо переписать только содержимое шести регистров, этого достаточно для изменения всех параметров сигнала с линейной частотной модуляцией, таким образом достигается высокая скорость перестройки формирователя.

Краткое описание чертежа

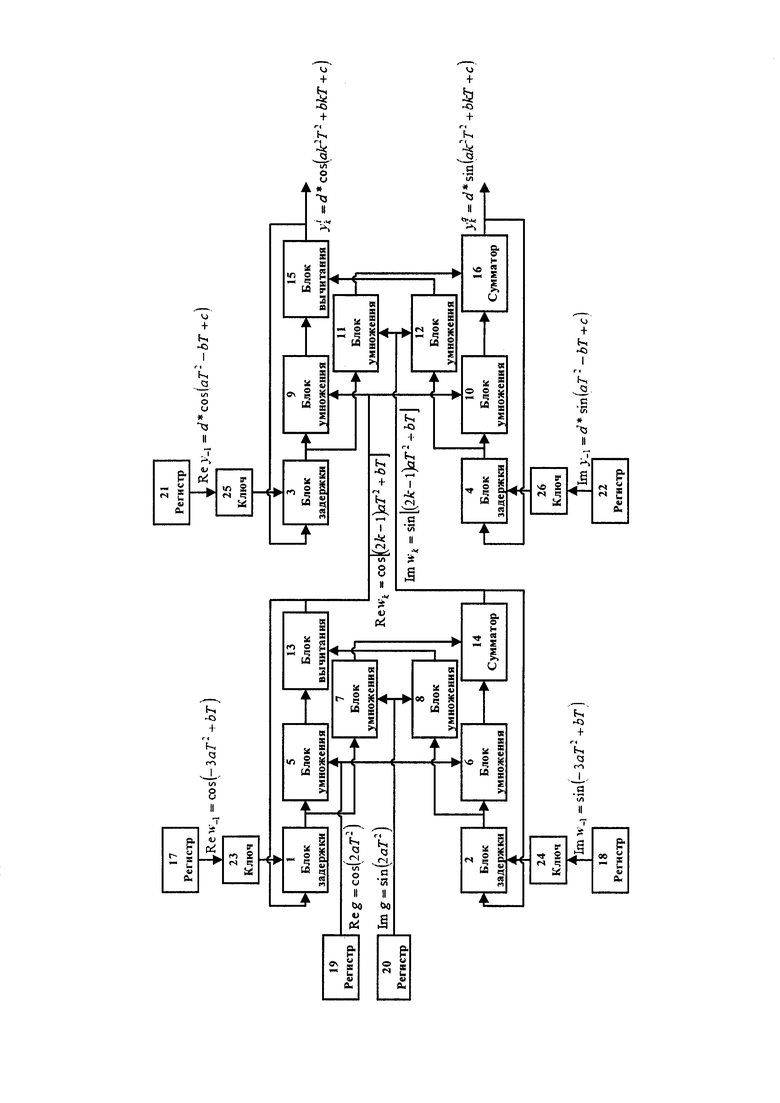

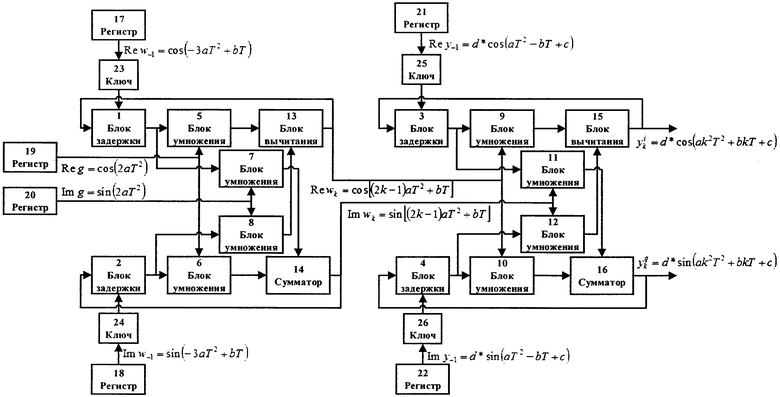

На чертеже представлены:

- первый (1), второй (2), третий (3) и четвертый (4) блоки задержки;

- первый (5), второй (6), третий (7), четвертый (8), пятый (9), шестой (10), седьмой (11) и восьмой (12) блоки умножения;

- первый блок вычитания 13 и первый сумматор 14, второй блок вычитания 15 и второй сумматор 16;

- первый (17), второй (18), третий (19), четвертый (20), пятый (21) и шестой (22) регистры;

- первый (23), второй (24), третий (25) и четвертый (26) ключи.

Выходы первого (23), второго (24), третьего (25) и четвертого (26) ключей соединены соответственно с входами установки начальных условий первого (1), второго (2), третьего (3) и четвертого (4) блоков задержки, а выходы первого блока вычитания 13, первого сумматора 14, второго блока вычитания 15 и второго сумматора 16 соединены соответственно с информационными входами первого (1), второго (2), третьего (3) и четвертого (4) блоков задержки.

Осуществление изобретения

Изобретение может быть осуществлено на основе программируемой логической интегральной схемы FPGA.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ГЛУБИНЫ РАСПОЛОЖЕНИЯ ОБЪЕКТОВ С ЛЕТАТЕЛЬНОГО АППАРАТА | 2007 |

|

RU2349937C1 |

| Цифровой анализатор мгновенного спектра комплексного сигнала | 1986 |

|

SU1406507A2 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Коррелятор вибросейсмических данных | 1989 |

|

SU1665326A1 |

| СПОСОБ ФОРМИРОВАНИЯ КВАДРАТУРНЫХ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2168281C2 |

| Цифровой автокоррелятор | 1985 |

|

SU1280387A1 |

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

| Процессорный элемент устройства для быстрого преобразования Фурье | 1985 |

|

SU1288716A1 |

| СПОСОБ ИЗМЕРЕНИЯ ВЫСОТЫ МОРСКИХ ВОЛН С ЛЕТАТЕЛЬНОГО АППАРАТА НА ПЛАВУ | 1996 |

|

RU2112925C1 |

| СПОСОБ МНОГОПАРАМЕТРИЧЕСКОГО СЛЕЖЕНИЯ ЗА НАВИГАЦИОННЫМИ СИГНАЛАМИ И ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С МНОГОПАРАМЕТРИЧЕСКИМ УСТРОЙСТВОМ СЛЕЖЕНИЯ ЗА СЛАБЫМИ СИГНАЛАМИ В УСЛОВИЯХ СВЕРХВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2012 |

|

RU2551805C2 |

Изобретение относится к радиотехнике, автоматике и вычислительной технике и может быть использовано для формирования высокостабильных и высокоточных сигналов с перестраиваемыми параметрами. Технический результат заключается в увеличении скорости перестройки параметров формирователя, уменьшении объема памяти с высокой точностью вычисления отсчетов сигнала. Устройство содержит блоки задержки, блоки вычитания, сумматоры, блоки умножения, регистры, ключи. Причем выходы регистров 17, 18, 21 и 22 соединены с входами ключей 23, 24, 25 и 26, соединенных с входами установки начальных условий блоков задержки 1, 2, 3 и 4, связанных через блоки умножения 5, 6, 9 и 10 соответственно с первыми входами блока вычитания 13, сумматора 14, блока вычитания 15 и сумматора 16, выходы которых соединены с информационными входами блоков задержки 1, 2, 3 и 4, выходы которых соединены с первыми входами блоков умножения 7, 8, 11 и 12, выходы которых соединены соответственно с вторым входом сумматора 14, входом вычитания блока вычитания 13, вторым входом сумматора 16, входом вычитания блока вычитания 15, выход регистра 19 соединен с вторыми входами блоков умножения 5 и 6, выход регистра 20 соединен с вторыми входами блоков умножения 7 и 8, выход блока вычитания 13 соединен с вторыми входами блоков умножения 9 и 10, выход сумматора 14 соединен с вторыми входами блоков умножения 11 и 12, выходы блока вычитания 15 и сумматора 16 являются выходами отсчетов синфазной и квадратурной составляющих ЛЧМ-сигнала. 1 ил.

Рекурсивный цифровой формирователь отсчетов сигналов с линейной частотной модуляцией, содержащий первый и второй регистры и первый и второй сумматоры, отличающийся тем, что он содержит первый, второй, третий и четвертый блоки задержки, первый и второй блоки вычитания, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки умножения, третий, четвертый, пятый и шестой регистры, первый, второй, третий и четвертый ключи, причем выход первого блока задержки соединен с первыми входами первого и второго блоков умножения, выход второго блока задержки соединен с первыми входами третьего и четвертого блоков умножения, выход третьего блока задержки соединен с первыми входами пятого и шестого блоков умножения, выход четвертого блока задержки соединен с первыми входами седьмого и восьмого блоков умножения, выходы первого и пятого блоков умножения присоединены соответственно к входам суммирования первого и второго блоков вычитания, выходы третьего и седьмого блоков умножения соединены соответственно к первым входам первого и второго сумматоров, выходы четвертого и восьмого умножителей соединены с входами вычитания соответственно первого и второго блоков вычитания, выходы второго и шестого блоков умножения соединены соответственно с вторыми входами первого и второго сумматоров, выходы первого и второго блоков вычитания соединены с информационными входами первого и третьего блоков задержки соответственно, выходы первого и второго сумматоров соединены с информационными входами второго и четвертого блоков задержки соответственно, выходы первого, второго, пятого и шестого регистров соединены соответственно с входами первого, второго, третьего и четвертого ключей, выходы первого, второго, третьего и четвертого ключей соединены соответственно с входами установки начальных условий первого, второго, третьего и четвертого блоков задержки, выход третьего регистра соединен с вторыми входами первого и третьего блоков умножения соответственно, выход четвертого регистра соединен со вторыми входами второго и четвертого блоков умножения, выход первого блока вычитания соединен с вторыми входами пятого и седьмого блоков умножения соответственно, выход первого сумматора соединен с вторыми входами шестого и восьмого умножителей, выход второго блока вычитания является выходом отсчетов синфазной составляющей сигнала с линейной частотной модуляцией, выход второго сумматора является выходом отсчетов квадратурной составляющей сигнала с линейной частотной модуляцией.

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

| Последовательное арифметическое устройство | 1974 |

|

SU528565A1 |

| US 6208285B1, 27.03.2001 | |||

| EP 1883193A2, 30.01.2008. | |||

Авторы

Даты

2016-03-20—Публикация

2015-02-17—Подача