Изобретение относится к цифровой вычислительной технике и предназначено для решения задачи обнаружения случайных срывов процессора микроЭВМ с заданной программы функционирования, что может быть вызвано действием случайных помех.

Известен способ повышения надежности микроЭВМ, представленный, например, в [1].

Данный способ заключается в том, что к n-разрядному основному (программному) запоминающему устройству микроЭВМ предварительно добавляют дополнительное однобитовое запоминающее устройство, которые в рабочем режиме образуют единое (n+1)-разрядное запоминающее устройство, затем в n-разрядные ячейки основного запоминающего устройства загружают программу работы процессора в виде машинных кодов, после чего в каждую однобитовую ячейку дополнительного запоминающего устройства записывают единицу или ноль таким образом, чтобы сумма единичных значений в кодах каждой (n+1)-разрядной ячейки основного и дополнительного запоминающих устройств была бы четной, что в режиме работы при чтении данных из основного и дополнительного запоминающих устройств автоматически проверяют многовходовым сумматором по модулю 2, сигнал с выхода которого подают на вход прерывания процессора, который переходит на подпрограмму обработки прерывания в случае неверного чтения кодов из основного и дополнительного запоминающих устройств.

Данный способ, известный более как «контроль четности», повышает надежность функционирования микроЭВМ за счет оперативного обнаружения случайных и/или фиксированных единичных искажений данных, считываемых из основного и дополнительного запоминающих устройств.

Недостатком данного способа повышения надежности является невозможность обнаружения фактов возникновения случайных «блужданий» процессора микроЭВМ. Случайные «блуждания» процессора возникают тогда, когда он срывается с заданной программы функционирования, интерпретируя машинные коды данных как коды команд, а коды команд - как операнды или как коды их адресов. Такого рода срывы процессора могут быть следствием негативного воздействия помех на шины адреса процессора или сбоев счетчика команд.

Наиболее близким по технической сути является способ повышения надежности микроЭВМ [2], заключающийся в том, что к n-разрядному основному (программному) запоминающему устройству микроЭВМ предварительно добавляют дополнительное однобитовое запоминающее устройство, которые в рабочем режиме образуют единое (n+1)-разрядное запоминающее устройство, затем в n-разрядные ячейки основного запоминающего устройства загружают программу работы процессора в виде машинных кодов, после чего в каждую однобитовую ячейку дополнительного запоминающего устройства записывают единицу или ноль таким образом, чтобы в (n+1) битах дополнительного запоминающего устройства и основного запоминающего устройства, в ячейках которого содержатся коды команд, сумма единичных значений была бы нечетной, а в ячейках которого содержатся все остальные коды - четной, при этом в режиме работы микроЭВМ при чтении данных из основного и дополнительного запоминающих устройств считанные данные и однобитовый признак чтения кода команды, автоматически формируемый микроЭВМ, проверяют на четность сумматором по модулю два, сигнал с выхода которого подают на вход прерывания процессора, который переходит на подпрограмму обработки прерывания в случае нечетности данных, поступающих на входы сумматора по модулю два, при этом на n входов сумматором по модулю два одновременно подают данные из основного запоминающего устройства, на вход (n+1) - из дополнительного запоминающего устройства, а на (n+2)-й вход - признак чтения кода команды.

Данный способ во многих случаях предотвращает возникновение случайных «блужданий» процессора микроЭВМ при неверной интерпретации машинных кодов данных как кодов команд, а кодов команд - как операндов или как кодов их адресов. Однако возможны ситуации, при которых возникновение «блужданий» данным способом не может быть обнаружено.

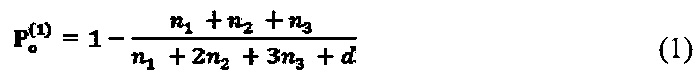

Предположим, что сбой программного счетчика происходит после правильного чтения кода однобайтной команды. Тогда возможны следующие ситуации: правильно читается код команды, но переход на нее не предусмотрен алгоритмом (не определяется данным способом); читается код операнда, который интерпретируется процессором как код следующей команды (ошибка определяется). Частоту определения ошибки при сбое выполнения однобайтной команды  можно определить как

можно определить как

где n1 - количество в программе однобайтных команд;

n2 - количество в программе двухбайтных команд;

n3 - количество в программе трехбайтных команд;

d - количество в программе различных данных.

В соотношении (1) числитель дроби определяет общее количество кодов команд в программе, а знаменатель - общий объем программы в байтах. Как следует из соотношения (1) величина  тем больше, чем больше величина d, а также от соотношения в программе двухбайтовых и трехбайтовых команд. Если же принять, что количество однобайтовых, двухбайтовых и трехбайтовых команд одинаково, a d=0, то

тем больше, чем больше величина d, а также от соотношения в программе двухбайтовых и трехбайтовых команд. Если же принять, что количество однобайтовых, двухбайтовых и трехбайтовых команд одинаково, a d=0, то

Существенно увеличить величину  можно путем вставок в программу фиктивных блоков данных, при нормальной работе программы к которым обращение невозможно. Причем эти фиктивные данные целесообразно размещать более-менее равномерно по программе и небольшими блоками.

можно путем вставок в программу фиктивных блоков данных, при нормальной работе программы к которым обращение невозможно. Причем эти фиктивные данные целесообразно размещать более-менее равномерно по программе и небольшими блоками.

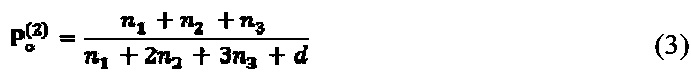

Предположим, что сбой программного счетчика происходит при выполнении двухбайтной команды после правильного чтения кода команды. В этом случае обнаружение возникновения «блуждания» может быть обеспечено только в том случае, если вместо второго байта данных будет прочитан первый байт другой команды, то есть код другой команды. Тогда частоту определения ошибки при сбое выполнения двухбайтной команды  можно определить как

можно определить как

Как следует из (3) увеличение объема фиктивных данных должно приводить к снижению эффективности данного способа обнаружения начала «блужданий». Это действительно справедливо, но только при оценке эффективности за время, не превышающее времени выполнения двухбайтной команды. Дело в том, что вторым прочитанным байтом может оказаться второй байт трехбайтной команды или байт фиктивных данных. Тогда ошибка будет обнаружена в том случае, если после выполнения неправильной двухбайтной команды процессор будет интерпретировать третий байт трехбайтной команды или следующий байт фиктивных данных как код следующей команды. При d→0 величина  →0,5.

→0,5.

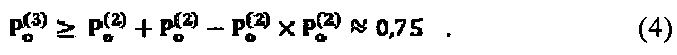

Предположим, что сбой программного счетчика происходит при выполнении трехбайтной команды после правильного чтения кода команды. В этом случае обнаружить ошибку возможно тогда, когда вместо второго и/или третьего байта данных читается код команды. Если принять, что количество однобайтных, двухбайтных и трехбайтных команд одинаково, a d→0, то

Проведенный анализ показывает, что повысить вероятность обнаружения начала «блужданий» процессора микроЭВМ возможно путем слежения за адресами обращения к программной памяти в пределах каждого цикла чтения всех байт каждой команды. Иначе говоря, если читается код однобайтной команды по адресу Ai, то следующее чтение может быть проведено по любому адресу Aj, но прочитанное по этому адресу должно интерпретироваться процессором как код команды. Если по адресу Ai читается код двухбайтной команды, то адрес читаемого второго байта всегда должен быть Ai+1. Прочитанный же из ячейки с адресом Aj следующий код должен интерпретироваться процессором как код следующей команды.

Если аналогичным образом рассуждать относительно многобайтных команд, состоящих из произвольного числа байт, то приходим к тому, что дополнительное повышение надежности микроЭВМ может быть обеспечено путем оперативного контроля в рабочем режиме за целостностью байтовой структуры команд. Под целостностью байтовой структуры команд будем понимать последовательное чтение байт многобайтных команд, при котором обращение к ячейкам памяти производится так, что адрес последующей ячейки памяти должен точно на единицу отличаться от адреса предшествующей ячейки памяти до тех пор, пока не будут прочитаны все байты многобайтной команды.

Изобретение направлено на расширение функциональных возможностей способа повышения надежности микроЭВМ за счет дополнительной возможности обнаружения факта возникновения случайных «блужданий» и адекватной реакции на них путем оперативного контроля целостности байтовой структуры исполняемых команд микроЭВМ.

Это достигается тем, что в первом такте чтения из основного запоминающего устройства кода каждой команды определяют с помощью дешифратора кода команды количество байт в данной команде, затем при единичном значении признака чтения кода команды запоминают в первом счетчике найденное количество байт в команде и одновременно с этим во втором счетчике запоминают код адреса читаемой ячейки памяти, который к этому моменту времени оказывается сформированным на шине адреса и который по истечении некоторого времени сравнивают с кодом адреса, ранее записанным во второй счетчик, и в случае их несовпадения формируют дополнительный сигнал ошибки, поступающий на вход прерывания процессора, в том же случае, если код адреса на шине адреса и код, записанный во второй счетчик, совпадут, одновременно увеличивают на единицу содержимое второго счетчика, а содержимое первого счетчика уменьшают на единицу, затем если в первом счетчике оказывается код, равный нулю, то ожидают следующего обращения к основной памяти за кодом следующей команды после чего реализуют следующий цикл обработки кода новой команды, если же в первом счетчике оказывается код, не равный нулю, то по каждому следующему сигналу чтения байт многобайтной команды проверяют на равенство код второго счетчика с кодом на шине адреса и в случае их равенства уменьшают на единицу содержимое первого счетчика и одновременно увеличивают на единицу содержимое второго счетчика и ожидают следующего сигнала чтения.

Рассмотрим осуществление заявляемого способа повышения надежности микроЭВМ.

Процессор микроЭВМ при выполнении рабочей программы должен обладать способностью формировать единичный признак чтения кода команды при обращении к основному запоминающему устройству, аналогично тому, как этот признак (Ml) формируется в широко известном микропроцессоре КР 580 ВМ 80А [3].

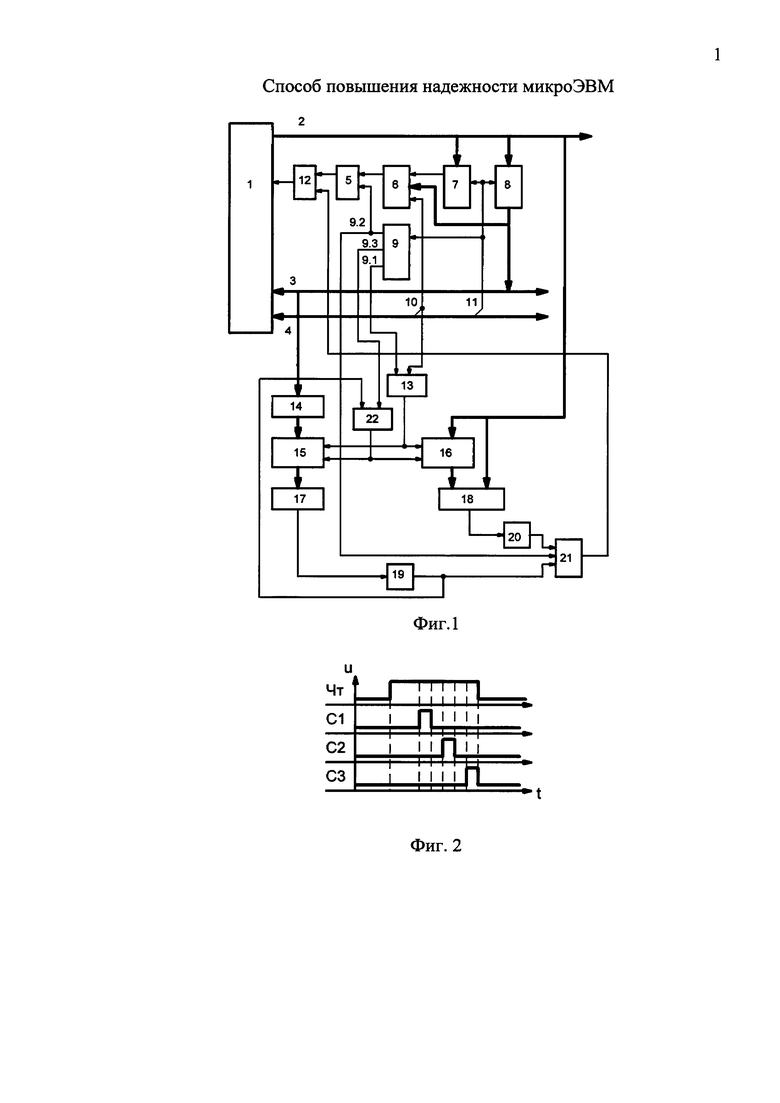

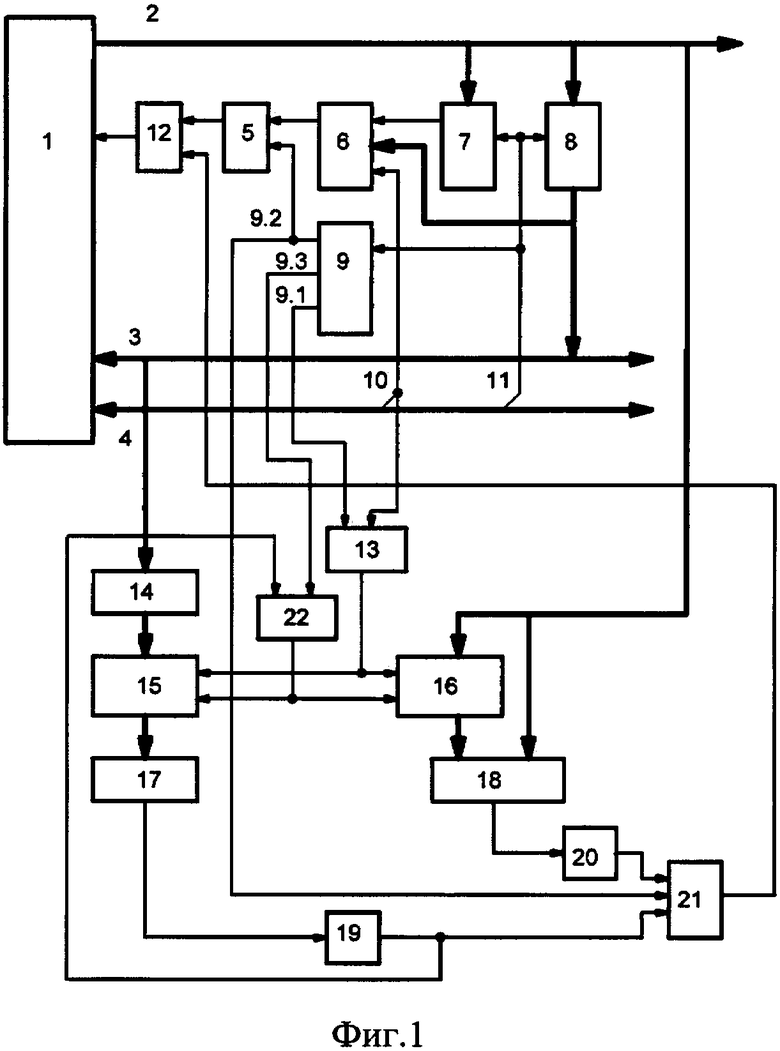

На фиг. 1 представлен фрагмент структурной схемы микроЭВМ, где 1 - процессор; 2 - однонаправленная m-разрядная шина адреса; 3 -двунаправленная n-разрядная шина данных; 4 - шина управления; 5 - первая схема «И»; 6 - сумматор по модулю 2 на (n+2) входа; 7 - дополнительное однобитовое запоминающее устройство; 8 - основное (программное) n-разрядное запоминающее устройство; 9 - формирователь стробирующих сигналов C1, С2, С3, формируемых соответственно на выходах 9.1, 9.2, 9.3; 10 - сигнал признака чтения кода команды (ЧКК); 11 - сигнал чтения основного и дополнительного запоминающих устройств (ЧТ); 12 - схема «ИЛИ»; 13 - вторая схема «И»; 14 - дешифратор кода команды; 15 - первый счетчик; 16 - второй счетчик; 17 - схема выделения нулевого состояния первого счетчика; 18 - схема сравнения m-разрядных кодов (m-разрядность шины адреса); 19 - первый инвертор; 20 - второй инвертор; 21 - третья схема «И»; 22 - четвертая схема «И».

На фиг. 2 представлена временная диаграмма, характеризующая временное соотношение между сигналом чтения (ЧТ) из основного и дополнительного запоминающего устройств и стробирующими сигналами С1, С2 и С3.

Способ осуществляется следующим образом.

На основе предварительного анализа рабочей программы процессора 1, представленной в виде двоичных кодов, определяют адреса тех ячеек основного запоминающего устройства 8, в которых будут содержаться коды команд. Для каждой такой ячейки определяется количество единичных значений, содержащихся в коде команды, при этом если количество единичных значений в коде команде четное, то в соответствующий бит дополнительного запоминающего устройства 7 должна впоследствии записываться единица (то есть код команды дополняется до нечетности). Для всех других кодовых слов рабочей программы, включая и неиспользуемые программой ячейки основного запоминающего устройства 8, кодовые слова при помощи дополнительного запоминающего устройства 7 дополняются до четности.

Затем рабочая программа процессора 1, представленная в виде двоичных кодов, загружается в основное запоминающее устройство 8, а в дополнительное запоминающее устройство 7 загружаются найденные значения бит. Загрузка информации в основное 8 и дополнительное 7 запоминающие устройства может производиться как в составе микроЭВМ, так и вне нее.

В рабочем режиме функционирования основное 8 и дополнительное 7 запоминающие устройства образуют единое (n+1) разрядное запоминающее устройство, где n-разрядность шины данных процессора 1. На адресные входы основного 8 и дополнительного 7 запоминающих устройств одновременно подаются коды адреса, формируемые процессором 1 на m-разрядной шине адреса 2. Все n выходов основного запоминающего устройства 8 стандартно подключаются к шине данных 3 и дополнительно к n входам (n+2)-входового сумматора по модулю два 6. К (n+1)-му входу сумматора 6 подключается выход дополнительного запоминающего устройства 7, а к (n+2)-му входу сумматора 6 подключается сигнал 10 признака чтения кода команды, формируемый процессором 1 при выполнении программы и передаваемый по шине управления 4. Сигнал с выхода сумматора по модулю два 6 поступает на первый вход первой схемы «И» 5, на второй вход которой поступает стробирующий сигнал С2, который в свою очередь формируется формирователем 9 на выходе 9.2 из сигнала 11 чтения (ЧТ), одновременно поступающего из шины управления 4 на соответствующие входы запоминающих устройств 7 и 8. Выход первой схемы «И» 5 подключается к первому входу схемы «ИЛИ» 12, а выход схемы «ИЛИ» 12 подключается к входу прерывания процессора 1. На первый вход второй схемы «И» 13 поступает сигнал 10 признака чтения кода команды, а на второй вход второй схемы «И» 13 поступает первый стробирующий сигнал С1, который формируется формирователем 9 на выходе 9.1 из сигнала 11 чтения (ЧТ), выход второй схемы «И» 13 подключается к первым управляющим входам первого счетчика 15 и второго счетчика 16, вторые управляющие входы которых подключены к выходу четвертой схемы «И» 22, первый вход которой подключен выходу первого инвертора 19, а второй вход к выходу 9.3 формирователя 9, который формирует на выходе 9.3 третий стробирующий сигнал С3. Входы дешифратора кода команды 14 подключены к шине данных 3, а выходы дешифратора 14 подключены к входам параллельной загрузки первого счетчика 15, выходы которого подключены к входам схемы выделения нулевого состояния первого счетчика 17, выход которой соединен со входом первого инвертора 19, выход которого подключен к третьему входу третьей схемы «И» 21, второй вход которой соединен с выходом 9.2 формирователя 9, а третий вход третьей схемы «И» 21 подключен к выходу второго инвертора 20, выход третьей схемы «И» соединен с вторым входом схемы «ИЛИ» 12. Входы параллельной загрузки второго счетчика 16 подключены к m-разрядной шине адреса 2, которые также подключены к вторым входам схемы сравнения m-разрядных кодов 18, к первым входам которой подключены выходы второго счетчика 16, а выход схемы сравнения m-разрядных кодов 18 подключен к входу второго инвертора 20.

Процессор 1 начинает свою работу с того, что устанавливает на шину адреса 2 двоичный код ячейки памяти основного 8 и дополнительного 7 запоминающих устройств, из которой будет считываться записанная в них информация. Одновременно с установкой кода на шине адреса 2 процессор 1 формирует на одной из линий шины управления 4 единичный сигнал 10, поступающий на (n+2)-й вход сумматора 6 и первый вход второй схемы «И» 13, свидетельствующий о том, что данные, считанные процессором 1 из данной ячейки основного запоминающего устройства 8, будут интерпретироваться процессором 1 как код команды. Иначе говоря, процессор формирует признак 10 чтения кода команды из ячейки основного запоминающего устройства 8. Далее, на одной из линий шины управления 4 формируется сигнал чтения 11 из ячеек с одинаковым адресом основной 8 и дополнительной 7 памяти. Одновременно с фронтом сигнала чтения 11 запускается формирователь 9, генерирующий на выходах 9.1, 9.2, 9.3 три разнесенных во времени стробирующих сигнала C1, С2, С3. С началом действия сигнала чтения на выходах основного 8 и дополнительного 7 запоминающих устройств формируются коды, записанные в их ячейках памяти. Код из основного 8 запоминающего устройства поступает в шину данных 3 и на n входов сумматора 6. На (n+1) вход сумматора 6 поступает код с дополнительного 7 запоминающего устройства. К моменту формирования фронта сигнала стробирования С2 сумматор 6 формирует на своем выходе стабильный признак четности или нечетности (n+2) разрядного входного кода. Сигнал с выхода сумматора 6 поступает на первый вход первой схемы «И» 5. При единичном значении стробирующего сигнала С2, поступающего на второй вход первой схемы «И» 5, проверяется значение сигнала с выхода сумматора 6. Если на выходе сумматора 6 сформирован «0», то это свидетельствует о том, что код, считанный из основного 8 и дополнительно 7 запоминающих устройств, не имеет единичных искажений и правильно интерпретируется процессором 1. Если на выходе сумматора 6 сформирована «1», то это свидетельствует о том, что код, считанный из основного 8 и дополнительно 7 запоминающих устройств, либо имеет единичные искажения, либо этот код неправильно интерпретируется процессором 1, при этом на выходе первой схемы «И» 5 будет сформирован единичный сигнал, по длительности примерно равный стробирующему сигналу С2 и вызывающий прерывание процессора при прохождении через схему «ИЛИ» 12.

Параллельно с контролем единичных искажений считываемых из основного 8 и дополнительного 7 запоминающих устройств данных и правильности интерпретации кодов команд производится проверка целостности байтовой структуры команды процессора. Для этого предварительно для каждой команды процессора определяется ее байтовая структура, то есть количество байт, необходимых для выполнения каждой команды. На основании такой информации синтезируется дешифратор кода команды 14. Данные, установленные на шине данных на интервале времени, равному длительности сигнала чтения 11, дешифрируются дешифратором кода команды 14, двоичный код, с выхода которого при единичном сигнале чтения кода команды 10 соответствует количеству байт данной команды. По стробирующему сигналу С1, проходящему через вторую схему «И» 13 при единичном сигнале чтения кода команды 10, код с выхода дешифратора 14 загружается в первый счетчик 15 и по тому же сигналу во второй счетчик 16 с шины адреса 2 загружается код адреса читаемой ячейки основной 8 и дополнительной 7 памяти. По истечении некоторого времени по стробирующему сигналу С2, формируемому на выходе 9.2 формирователя 9 и поступающему на второй вход третьей схемы «И» 21, опрашивается сигнал результата сравнения с выхода схемы сравнения 18, который через второй инвертор 20 поступает на первый вход третьей схемы «И» 21. С выхода третьей схемы «И» 21 сигнал прерывания процессора будет формироваться только в том случае, если на выходе схемы сравнения 18 будет сформирован сигнал, равный «0», что соответствует неравенству кодов на входе схемы сравнения 18. При этом на выходе схемы выделения нулевого состояния первого счетчика 15 должен также формироваться сигнал, равный «0», свидетельствующий о том, что первый счетчик 15 содержит код, отличный от нуля. В том случае, если на выходе схемы сравнения 18 будет сформирован сигнал, равный «1», что соответствует равенству кодов на входе схемы сравнения 18, сигнал прерывания процессора с выхода третьей схемы «И» 21 формироваться не будет. По истечении некоторого времени формирователь 9 сформирует на выходе 9.3 стробирующий сигнал С3, по которому в первом счетчике 15 код уменьшится на единицу, а во втором счетчике 16 увеличится на единицу, прогнозируя тем самым адрес следующей читаемой ячейки основной 8 и дополнительной 7 памяти для многобайтной команды. Уменьшение содержимого первого счетчика 15 и увеличение второго счетчика 16 будет продолжаться по каждому последующему сигналу чтения 11 до тех пор, пока в первом счетчике 15 не установится код, равный нулю. Далее при нормальной работе процессора цикл проверки целостности байтовой структуры повторяется для следующей команды.

Техническим результатом от использования заявляемого изобретения является расширение функциональных возможностей способа повышения надежности микроЭВМ за счет оперативного контроля в рабочем режиме за целостностью байтовой структуры многобайтных команд.

Источники информации

1. Карлащук В.И. Электронная лаборатория на IBM PC. Лабораторный практикум на базе Electronics Workbench и MATLAB. - М.: СОЛОН-Пресс, 204. - 800 с., стр. 366.

2. Патент RU 2530325 Российская Федерация, МПК G06F11/10. Способ повышения надежности микроЭВМ / М.В. Рожков, С.В. Тюрин; заявитель и патентообладатель ФБГОУ ВПО "Воронежский государственный технический университет". - №2012116018; заявл. 19.04.2012; опубл. 10.10.2014. Бюл. №28.

3. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник. В 2 т. / В.-Б.Б. Абрайтис, Н.Н. Аверьянов, А.И. Белоус и др. Под ред. В.А. Шахнова. - М.: Радио и связь, 1988. - Т. 1. - 386 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОВЫШЕНИЯ НАДЕЖНОСТИ МИКРОЭВМ | 2012 |

|

RU2530325C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для контроля хода программы | 1987 |

|

SU1451703A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

Изобретение относится к цифровой вычислительной технике. Техническим результатом от использования заявляемого изобретения является расширение функциональных возможностей за счет оперативного контроля в рабочем режиме за целостностью байтовой структуры многобайтных команд. Способ позволяет непосредственно в рабочем режиме микроЭВМ параллельно с контролем единичных искажений, считываемых из основного и дополнительного запоминающих устройств данных и правильности интерпретации процессором кодов команд, дополнительно проводить проверку целостности байтовой структуры команды процессора, под которой понимается последовательное чтение байт многобайтных команд, при котором обращение к ячейкам памяти производится так, что адрес последующей ячейки памяти должен точно на единицу отличаться от адреса предшествующей ячейки памяти до тех пор, пока не будут прочитаны все байты многобайтной команды, что повышает вероятность оперативного обнаружения факта возникновения случайных «блужданий» процессора при сбоях в шинах адреса или счетчика команд микроЭВМ. 2 ил.

Способ повышения надежности микроЭВМ, заключающийся в том, что к n-разрядному основному программному запоминающему устройству микроЭВМ предварительно добавляют дополнительное однобитовое запоминающее устройство, которые в рабочем режиме образуют единое (n+1)-разрядное запоминающее устройство, затем в n-разрядные ячейки основного запоминающего устройства загружают программу работы процессора в виде машинных кодов, после чего в каждую однобитовую ячейку дополнительного запоминающего устройства записывают единицу или ноль таким образом, чтобы в (n+1) битах дополнительного запоминающего устройства и основного запоминающего устройства, в ячейках которого содержатся коды команд, сумма единичных значений была бы нечетной, а в ячейках которого содержатся все остальные коды - четной, при этом в режиме работы микроЭВМ при чтении данных из основного и дополнительного запоминающих устройств считанные данные и однобитовый признак чтения кода команды, автоматически формируемый микроЭВМ, проверяют на четность сумматором по модулю два, сигнал с выхода которого подают на вход прерывания процессора, который переходит на подпрограмму обработки прерывания в случае нечетности данных, поступающих на входы сумматора по модулю два, при этом на n входов сумматором по модулю два одновременно подают данные из основного запоминающего устройства, на вход (n+1) - из дополнительного запоминающего устройства, а на (n+2)-й вход - признак чтения кода команды, отличающийся тем, что в первом такте чтения из основного запоминающего устройства кода каждой команды определяют с помощью дешифратора кода команды количество байт в данной команде, затем при единичном значении признака чтения кода команды запоминают в первом счетчике найденное количество байт в команде и одновременно с этим во втором счетчике запоминают код адреса читаемой ячейки памяти, который к этому моменту времени оказывается сформированным на шине адреса и который по истечении некоторого времени сравнивают с кодом адреса, ранее записанным во второй счетчик, и в случае их несовпадения формируют дополнительный сигнал ошибки, поступающий на вход прерывания процессора, в том же случае, если код адреса на шине адреса и код, записанный во второй счетчик, совпадут, одновременно увеличивают на единицу содержимое второго счетчика, а содержимое первого счетчика уменьшают на единицу, затем если в первом счетчике оказывается код, равный нулю, то ожидают следующего обращения к основной памяти за кодом следующей команды, после чего реализуют следующий цикл обработки кода новой команды, если же в первом счетчике оказывается код, не равный нулю, то по каждому следующему сигналу чтения байт многобайтной команды проверяют на равенство код второго счетчика с кодом на шине адреса и в случае их равенства уменьшают на единицу содержимое первого счетчика и одновременно увеличивают на единицу содержимое второго счетчика и ожидают следующего сигнала чтения.

| СПОСОБ ПОВЫШЕНИЯ НАДЕЖНОСТИ МИКРОЭВМ | 2012 |

|

RU2530325C2 |

| US 6950978 B2, 27.09.2005 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| US 5887146 A1, 23.03.1999. | |||

Авторы

Даты

2017-04-04—Публикация

2015-12-25—Подача