4аь СП

о

00

Изобретение относится к вычислительной технике и может быть использовано для контроля хода программы цифровых ЭВМ.

Целью изобретения является повышение оперативности контроля.

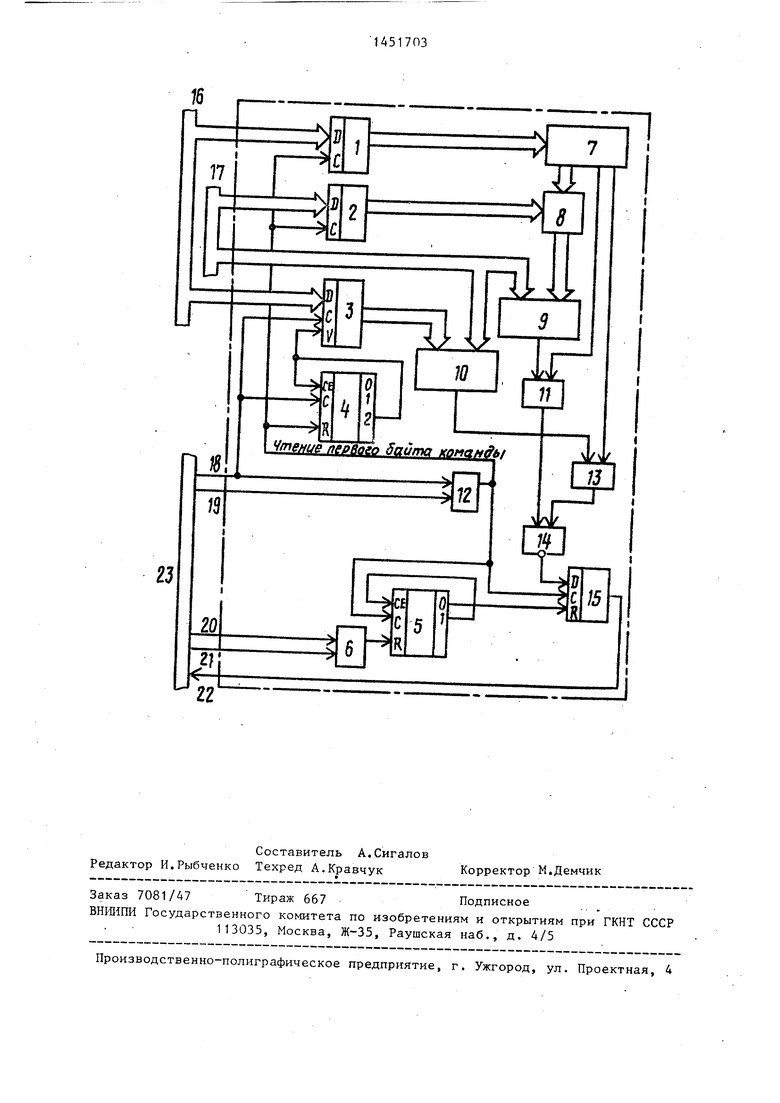

Устройство для контроля хода программ, представлено на чертеже.

Устройство .содержит регистр Т кода команды для хранения кода выполняемой команды, регистр 2 адреса команды для хранения адреса выполняемой команды, регистр 3 адреса перехода для .хранения адреса перехода, счетчик 4 слов адреса, счетчик 5 начальной установки, элемент ИЛИ 6, дешифратор 7, сумматор 8, первую схему 9 сравнения, вторую схему 10 сравнения, элементы И 11-13, элемент ИЛИ-НЕ 14, триггер 15 ошибки, информационный вход (шину данных) 16 устройства, адресный вход (адресную шину) 17 устройства, вход 18 чтения устройства, вход 19 признака первого байта команды устройства, вход 20 начальной установки в исходное состояние устройства, вход 21 подтверждения прерывания, выход 22 запроса прерывания устройства, шину 23 управ ления.

Устройство работает следующим образом.

В основу работы устройства контро

ля положен тот факт, что по ходу выполняемой команды определяется адрес следующей команды.

Все команды разделены на две группы: линейные команды, после выполне-г ния которых выполняется следующая команда; команды перехода, после выполнения которых, в зависимости от условий, выполняется следующая команда j или же команда, адрес которой указан

в команде перехода. I

выполнении очередной команды сравнивается ее адрес с ранее рассчитанными адресами. Положительный результат сравнения свидетельствует о том, что программа выполняется по адресам правильно. Отрицательный результат сравнения свидетельствует о нарушении хода выполнения программы.

Запись информации в регистр 1 ..ко- да .-команды и регистр 2 адреса команды выполняется по заднему фронту сигнала чтения первого слова команды а запись информации в регистр 3 адре

5 0 5 0

5

Q

Q

5

са перехода выполняется по заднему фронту сигнала чтения.

Счетчик 4 слов адреса предназначен для формирования сигнала запрещения счета,- поступающего на вход запрещения счета регистра 3 адреса перехода. После записи адреса перехода в регистр 3 сигнал с выхода счетчика 4 слов адреса запрещает запись информации в регистр 3 адреса перехода. После этого счетчик 4 слов адреса устанавливается в исходное состояние, разрешая запись в регистр 3 адреса перехода по чтению первого байта команды или же по сигналу Сброс. Переключение счетчик.а 4 слов адреса происходит по заднему фронту.

Счетчик 5 начальной установки предназначен для установки в исходп-. ное состояние триггера 15 ошибки. Счетчик 5 начальной установки блокирует запись в триггер 15 ошибки сигнала ошибки, который возникает при выполнении первой команды программы, а также первой команды подпрограммы обработки прерывания, поскольку в этих случаях адрес вы- палняемой команды нельзя рассчитать заранее.

Счетчик 5 начальной установки устанавливается в исходное состояние по сигналу Сброс или Подтверждение прерывания, после чего по заднему фронту сигнала Чтение первого байта команды он переключается и

самоблокируется. I

Счетчик 4 слов адреса, счетчик 5

начальной установки являются сч.етчи- ками-делителями, т.е. с дешифратором на выходе, и поэтому в текущий момент времени может быть возбужден лишь один из выходов каждого счетчика, Дешифратор 7 предназначен дл я определения длинь выполняемой команды, информация о которой поступает на вход сумматора 8, и выдачи сигналов разрешения на входы второго и третьего элементов И 11 и 13. Например, при выполнении линейной команды сигнал разрешения с выхода дешифратора 7 поступает только на второй элемент И 11, при выполнении команды условного перехода на второй и третий элементы И 11 и 13, а в случае выполнения команды безусловного перехода или вызова подпрограммы - на вход третьего элемента И 13.

.

Сумматор 8, на одни вход которого поступает адрес выполняемой команды, а на другой (с выхода дешифратора) - код длины этой команды, определяет адрес следующей команды.

Схемы 9 и 10 сравнения выполняют сравнение адреса выполняемой команды с ранее рассчитанными адресами. В случае совпадения адресов на выходах схем 9 и 10 сравнения появляются уровни 1, которые через элементы И 11 и 13 и элемент ИЛИ-НЕ 14 поступают на информационный вход триггера 15 ошибки.

Триггер 15 ошибки предназначен для фиксации результата сравнения выполняемой команды с ранее рассчитанными адресами. Начальная установка триггера 15 ошибки выполняется по сигналу с выхрда счетчика 5 начальной установки. Запись сигнала с информационного входа выполняется по переднему фронту сигнала Чтение первого байта команды. При обнаружении устройством контроля ошибки хода выполнения программы на выходе триггера 15 ошибки появляется уровень 1 , который формирует сигнал Запрос прерывания.

Рассмотрим работу устройства на примере использования контроля в микроэвм на основе микропроцессора типа К 580.

По сигналу Сброс, который возбуждается по системной управляющей магистрали 23, счетчик 5 начальной установки через вход 20 и элемент ИЛИ 6 устанавливается в исходное состояние. Установка в О счетчика 5 начальной установки вызывает появ- тение уровня 1 на входе установки ноль триггера 15 , ошибки, при этом а выходе триггера ошибки 15 устанавивается ноль.

После снятия сигнала Сброс проессор формирует сигналы Чтение, Признак первого байта команды и бращается за командой. Процессор ыставляет на адресных шинах 17 адрес улевой ячейки, а по шине 23 управле- 50 ия - сигнал 18 чтения. Содержимое улевой ячейки ПЗУ устанавливается а. шине 16 данных.

Сигналы на входах 18 и 19 устройтва для контроля формируют на выхо- 55 е элемента И 12 .1, передний фронт оторой не изменяет состояния триггеа 15 ошибки, поскольку на его входе

сч Ч g хо в

ши 10 пе ре та ки из 15 за ме ко за ды 20 пе ус са с ош

25 мо чт пос или

30 При уст

его с ш

, адр тре сче етс щае пер сам

пае на ды,

40

45

адре

сигн ды 15 о срав ране прог виль НЕ герачени

ется

0

установки в ноль сохраняется , а счетчик 4 слов адреса по сигналу Чтение первого байта команды (с вы-, g хода элемента И 12) устанавливается в ноль.

По заднему фронту сигнала с входа 18 выполняется запись информации с шины 16 данных в регистр 3 адреса 10 перехода, при этом счетчик 4 слов адреса не изменяет своего состояния, так как сигнал на его входе установки в ноль еще не принял значения О из-за задержки на элементе И 12. По 15 заднему фронту сигнала с выхода элемента И 12 выполняется запись кода команды в регистр 1 кода команды, запоминание адреса выполняемой команды в регистре 2 адреса команды и 20 переключение счетчика 5 начальной установки, который переходит в режим самоблокировки,снимая уровень Г с входа установки в ноль триггера 15 ошибки.

25 При выполнении команды процессор может выдать более одного сигнала чтения, например, для считывания последуюощх байтов команды из ПЗУ или же считывания операндов из ОЗУ.

30 При этом содержимое ячейки памяти устанавливается на шине 16 данных.

По задним .фронтам второго и третьего сигналов Чтение информация с шины данных заносится в регистр 3

адреса перехода. По заднему фронту третьего.:сигнала Чтение на выходе счетчика 4 слов адреса устанавливается уровень 1, по которому запрещается запись в регистр 3 адреса перехода, и сч етчик 4 слов адреса самоблокируется.

На один вход сумматора 8 поступает код длины выполняемой команды, на другой - адрес выполняемой команды, На выходе сумматора 8 появляется

0

5

адрес следующей команды.

При появлении переднего фронта сигнала Чтение первого байта команды с выхода элемента И 12 в триггер 15 ошибки записывается результат сравнения текущего адреса команды, с ранее рассчитанными адресами. Если программа движется по адресам правильно, то на выходе элемента ИЛК- НЕ уровень нуля и на выходе триггера 15 ошибки также сохраняется зна- чение О.

Цикл работы устройства повторяется .

Если при пыполнении программы обнаруживаются нарушения хода программы, то на выходе элемента ИЛИ-НЕ 14

14517036

соединены с информационными входами , регистра адреса команды и первой группой входов первой схемы сравнения, выходы регистра кода команды соединены с входами дешифратора, выход признака линейного хода программы которого соединен с первым входом второго элемента И, выход равенства

появляется уровень 1 и триггер -15 ошибки формирует сигнал запрос прерывания, который через выход 22 и шину 23 поступает на устройство приоритетного прерывания.

Сигнал Запрос прерывания с выхо- ю первой схемы сравнения соединен с

вторь м входом, второго элемента И,

да триггера 15 поступает в процессор, В ответ на этот сигнал процессор . формирует сигнал Подтверждение прерывания, который поступает на вход 21 подтверждения прерывания и вызывает установку в исходное состояние счетчика 5 начальной установки, а на входе установки в ноль триггера 15 ошибки появляется уровень О, и сигнал Запрос прерывания снимается. .При появлении в процессоре прерываний от других устройств сигнал Подтверждение прерывания, поступающий на вход 21 подтверждения прерывания устройства, вызывает установку в исходное состояние счетчика 5 начальной установки, предотвращая формирование триггером 15 ошибки сигнала .Запрос прерывания, который должен быть сформирован, поскольку адрес первой команды подпрограммы оС работки прерывания не совпадает с теми адресами, которые устройство контроля рассчитывает при выполнении предыдущей команды, и на выходе элемента ИЛИ-НЕ 14 .устанавливается

уровень 1... ,;

Формула изобретения Устройство для контроля хода про-; граммы, содержащее регистр хода команды, регистр адреса команды, регистр адреса перехода, дешифратор, . первую схему сравнения, два элемента- И, триггер ошибки, причем вход признака чтения устройства соединен с входом записи регистра адреса пере- хода и первым входом перво го элемен- та И, вход признака перврго байта команды устройства соединен с вторым входом первого элемента И, выход которого соединен с входом записи регистров кода команды и адреса команды и с входом синхронизации триггера ошибки, выход которого является выходом запроса прерывания устройства, информационные входы устройства соединены с информационными входами регистров кода команды и адреса перехода, адресные входы устройства

15

20

30

отличающееся тем, что, с целью повышения оперативности контроля, в устройств® введены сумматор, вторая схема сравнения, счетчик начальной установки, счетчик слов адреса, третий элемент И, элемент ИЛИ- НЕ. элемент ИЛИ., причем выходы регистра адреса команды соединены с входами первого операнда сумматора, выход кода длины команды дешифратора соединен с входами второго операнда сумматора, выходы которого соединены с второй группой входов первой схемы

2(- сравнения, адресные входы устройства и выходы регистра адреса перехода соединены соответственно с первой и второй группами входов второй схемы . сравнения, вьпсод равенства которой соединен с первым входом третьего элемента И, выход признака безусловного перехода .дешифратора соединен с вторым входом третьего элемента И, выходы третьего и второго элементов И соединены соответственно с первым

35 и вторым входами элемента ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с информационным входом триггера ошибки, входы начальной установки и подтверждения прерывания устройства соединены соответственно с первым и.вторым входами элемента ИЛИ, выход которого соединен с входом установки в исходное состояние счетчика начальной установки, первый разрядный выход

45 КОТОРОГО соединен с входом установки нуля триггера ошибки, выход первого элемента И соединен с входом исходной установки счет.чика слов адреса и с входом синхрон-изации счетчика

50 начальной установки, второй разряд-;-, ный выход которого соединен со счетным входом счетчика начальной установки, вход чтения устройства соединен с синхронизирующим входом счетг.

55 чика слов адреса, выход которого соединен с входом блокировки записи регистра адреса перехода и со счетным входом счетчика слов адреса.

40

отличающееся тем, что, с целью повышения оперативности контроля, в устройств® введены сумматор, вторая схема сравнения, счетчик начальной установки, счетчик слов адреса, третий элемент И, элемент ИЛИ- НЕ. элемент ИЛИ., причем выходы регистра адреса команды соединены с входами первого операнда сумматора, выход кода длины команды дешифратора соединен с входами второго операнда сумматора, выходы которого соединены с второй группой входов первой схемы

сравнения, адресные входы устройства и выходы регистра адреса перехода соединены соответственно с первой и второй группами входов второй схемы . сравнения, вьпсод равенства которой соединен с первым входом третьего элемента И, выход признака безусловного перехода .дешифратора соединен с вторым входом третьего элемента И, выходы третьего и второго элементов И соединены соответственно с первым

и вторым входами элемента ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с информационным входом триггера ошибки, входы начальной установки и подтверждения прерывания устройства соединены соответственно с первым и.вторым входами элемента ИЛИ, выход которого соединен с входом установки в исходное состояние счетчика начальной установки, первый разрядный выход

КОТОРОГО соединен с входом установки нуля триггера ошибки, выход первого элемента И соединен с входом исходной установки счет.чика слов адреса и с входом синхрон-изации счетчика

начальной установки, второй разряд-;-, ный выход которого соединен со счетным входом счетчика начальной установки, вход чтения устройства соединен с синхронизирующим входом счетг.

чика слов адреса, выход которого соединен с входом блокировки записи регистра адреса перехода и со счетным входом счетчика слов адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля правильности выполнения команд микропроцессорной системы | 1987 |

|

SU1513455A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля хода программ цифровых ЭВМ. Устройство позволяет повысить оперативность контроля по обнаружению ощибок хода программы. Это достигается введением в устройство сумматора, дополнительной схемы сравнения, счетчика начальной установки.и элементов логики. Введение дополнительных элементов позволяет уменьшить аппаратурные затраты за счет сокращения объемов дополнительной памяти и сократить время обнаружения ошибок хода программы с точностью до выполняемой команды. 1 ил. Ш СП

| Устройство для контроля хода программ | 1984 |

|

SU1242967A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-06-15—Подача