Изобретение относится к области автоматического регулирования, а именно к регуляторам, включающим в свой состав пропорциональное и интегральное звенья, и может быть использовано при автоматизации различных технологических процессов.

Известны регуляторы, содержащие усилители, интегратор, дифференциатор, сумматоры, релейные и нелинейные элементы, например ПД/ПИД-регулятор с системой ограничения дифференцирования [патент ПНР N73281, кл. G05B 11/42, 1975], в котором сигнал, приводящий в действие схему ограничения интегрирования, выдается лишь тогда, когда сигнал дифференцирования близок к нулю. Однако такие регуляторы обладают сложной конструкцией и не обеспечивают установку необходимого соотношения между изменениями выходных сигналов интегратора и дифференциатора в процессе ограничения выходного сигнала всего регулятора, что снижает точность процесса регулирования.

Известны также ПИД-регуляторы, содержащие параллельно соединенные интегратор и дифференциатор, а также усилитель, выходы которых подключены к входам сумматора, выход которого соединен с нелинейным ограничителем и входом релейного элемента [авт. свид. СССР N696410, кл. G05B 11/36, Бюл. изобр. N41, 1979]. Однако в регуляторах такого типа содержатся дополнительные сумматоры и нелинейный блок, с помощью которых при выходе сигнала регулятора за установленные пределы прекращается процесс интегрирования. Кроме того, когда выходной сигнал регулятора достигает одного из пределов ограничения, предотвращается дальнейшие увеличение выходного сигнала дифференциатора. В этом случае выходной сигнал дифференциатора, являющийся составной частью выходного сигнала регулятора и вызывающий срабатывание схемы ограничения интегрирования, приводит к нежелательному изменению интегральной составляющей. Это явление приводит к значительному ухудшению качества регулирования.

Наиболее близким по технической сущности (принятый за прототип) является ПИД-регулятор, принятый за прототип, содержащий первый сумматор, к первому, второму и третьему входам которого соответственно через первый блок пропорционального преобразования, блок интегрирования, блок дифференцирования подключен вход пропорционально-интегрально-дифференциального регулятора, выход первого сумматора соединен с первым входом второго сумматора непосредственно, выход второго сумматора присоединен через последовательно подключенные первый инвертор и второй блок интегрирования к второму входу сумматора, выход второго блока интегрирования соединен через последовательно подключенные второй инвертор и блок задержки с третьим входом второго сумматора, выход второго сумматора является выходом пропорционально-интегрально-дифференциального регулятора [патент РФ N1835215, кл. G05B 11/36, 1996]. Однако при использовании такой структуры построения регулятора, за счет введения в него блоков задержки, быстродействие регулятора и системы в целом уменьшается.

Задачей предлагаемого технического решения является повышение качества работы автоматической системы регулирования частоты вращения электродвигателя.

Техническим результатом предлагаемого технического решения является увеличение быстродействия системы регулирования частоты вращения электродвигателя при заданных динамических характеристиках, исключение статической и динамической ошибки регулирования частоты вращения электродвигателя.

Указанный технический результат достигается тем, что в быстродействующем адаптивном регуляторе частоты вращения, содержащем блок инвертирования, пропорциональную и интегральную части регулятора, предусмотрены следующие отличия: введены четыре блока сравнения, два блока умножения, блок единичной функции, блок выделения модуля, нелинейный ограничитель тока, подключены таким образом, что первый выход пропорциональной части регулятора соединен с входом блока выделения модуля, выход которого соединен с прямым входом четвертого блока сравнения, на инверсный вход которого подается эталонный сигнал (равный единице), а выход четвертого блока сравнения соединен с входом блока единичной функции, один из выходов которого соединен с входом первого блока умножения, второй вход которого соединен с первым выходом интегральной части регулятора, а выход первого блока умножения соединен с инверсным входом второго блока сравнения на входе интегральной части регулятора, второй выход блока единичной функции соединен с входом блока инвертирования, выход которого соединен с входом второго блока умножения, один из входов которого соединен с выходом с датчика частоты вращения, а выход второго блока умножения соединен с инверсным входом первого блока сравнения, на прямой вход которого подается сигнал задания частоты вращения, выход первого блока сравнения соединен с прямым входом второго блока сравнения, второй выход интегральной части регулятора соединен с прямым входом третьего блока сравнения, выход третьего блока сравнения соединен с входом пропорциональной части регулятора, выход которой соединен с входом нелинейного ограничителя тока.

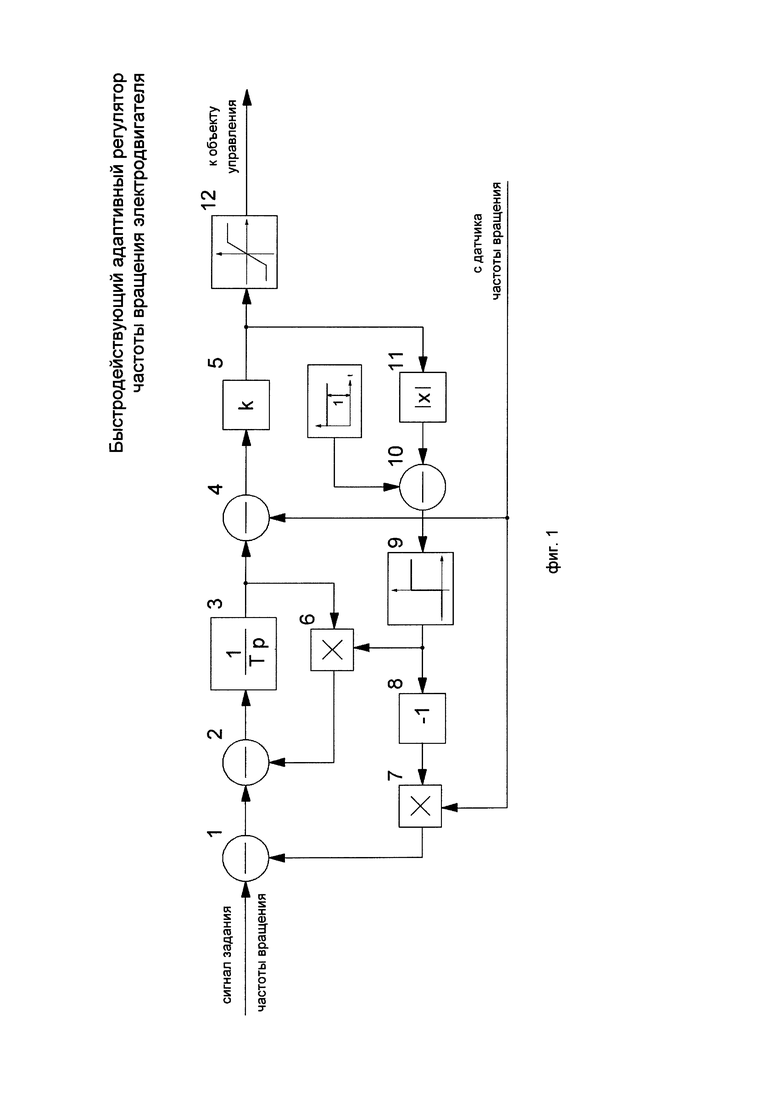

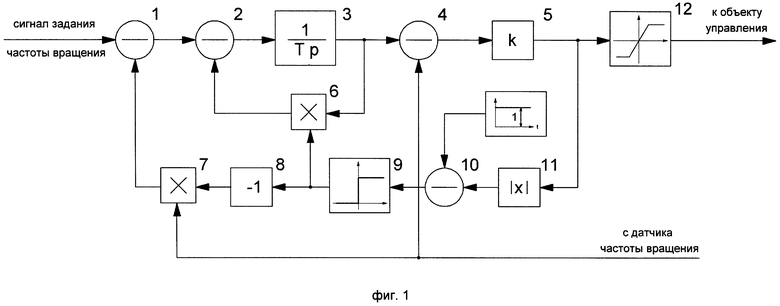

Техническая сущность и принцип действия предлагаемого технического решения поясняется чертежом, где на фиг. 1 представлена структурная схема регулятора:

1, 2, 4, 10 - блоки сравнения;

3 - интегральная часть;

5 - пропорциональная часть;

6, 7 - блок умножения;

8 - блок инвертирования;

9 - блок единичной функции;

11 - блок выделения модуля;

12 - нелинейный ограничитель тока.

Быстродействующий адаптивный регулятор скорости содержит четыре блока сравнения 1, 2, 4, 10; интегральную часть регулятора 3, пропорциональную часть регулятора 5, два блока умножения 6, 7; блок инвертирования 8, блок единичной функции 9, блок выделения модуля 11, нелинейный ограничитель 12.

Первый блок сравнения 1 последовательно соединен со вторым блоком сравнения 2, с интегральной частью регулятора 3, с третьим блоком сравнения 4, с пропорциональной частью регулятора 5 и нелинейным ограничителем тока 12, второй выход пропорциональной части регулятора 5 соединен с блоком выделения модуля 11, выход блока 11 соединен с прямым входом четвертого блока сравнения 10, на инверсный вход которого подается единица, выход четвертого блока сравнения 10 соединен с входом блока единичной функции 9, первый выход этого блока соединен с первым блоком умножения 6, также вход блока 6 соединен с выходом интегральной части регулятора 3, выход первого блока умножения 6 соединен с инверсным входом второго блока сравнения 2, второй выход блока единичной функции 9 соединен с входом блока инвертирования 8, выход которого соединен с входом второго блока умножения 7, на второй вход которого подается сигнал с датчика частоты вращения, выход второго блока умножения 7 соединен с инверсным входом первого блока сравнения 1, на инверсный вход третьего блока сравнения 4 подается сигнал с датчика частоты вращения.

Принцип действия предложенного технического решения:

Входным сигналом быстродействующего адаптивного регулятора скорости является сигнал задания частоты вращения. Входной сигнал поступает на первый блок сравнения 1, где сравнивается с сигналом датчика частоты вращения, при условии, что на выход второго блока умножения 7 от блока инвертирования 8 будет приходить сигнал равный единице. В том случае, когда на выходе блока инвертирования 8 единица, на входе первого блока умножения 6 сигнал равный нулю, это говорит о том, что обратная связь, охватывающая интегральную часть регулятора 3, не работает, и сигнал с выхода первого блока сравнения 1 проходит через второй блок сравнения 2, сравнивается с нулем, при этом работает интегральная часть регулятора 3. Сигнал с выхода интегральной части регулятора 3 поступает на вход третьего блока сравнения 4, где сравнивается с сигналом с датчика частоты вращения, дальше сигнал поступает на пропорциональную часть регулятора 5, где усиливается и дальше поступает на нелинейный ограничитель тока 12. Также сигнал с выхода пропорциональной части регулятора 5 поступает на блок выделения модуля 11, после которого в четвертом блоке сравнения 10 сигнал сравнивается с единицей и поступает на вход блока единичной функции 1, на выходе которого сигнал принимает значение «0» (может принимать значение «0» или «1»), с выхода этого блока сигнал поступает на первый блок умножения 6 и блок инвертирования 8. Схема работает по вышеописанному принципу до тех пор, пока сигнал на выходе пропорциональной части регулятора 5 будет меньше единицы по модулю, но как только сигнал превысит значение единицы, на выход блока единичной фунции 9 придет сигнал больше нуля, и на выходе этого блока сигнал примет значение «1», это приведет к тому, что на первый блок умножения 6 придет единица, и интегральную часть регулятора 3 охватит единичная обратная связь, тем самым отключив интегральную часть регулятора 3 и заменив его апериодическим звеном первого порядка. На выходе блока инвертирования 8 будет сигнал равный «0», при этом на инверсный вход первого блока сравнения 1 будет приходить «0».

Таким образом, в динамических режимах для повышения быстродействия работает пропорциональная часть регулятора, в статических режимах для повышения точности регулирования подключается интегральная часть регулятора, обеспечивающая нулевую статическую ошибку.

Правильность работы была подтверждена математическим моделированием и экспериментальной проверкой опытных образцов регулятора в системе электропривода.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2234116C1 |

| Способ регулирования частоты вращения двигателя внутреннего сгорания и устройство для его осуществления | 1983 |

|

SU1149045A1 |

| УСТРОЙСТВО ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 1987 |

|

SU1841021A1 |

| Способ защиты обмотки якоря электродвигателя от перегрева и устройство для его осуществления | 1984 |

|

SU1279010A1 |

| Импульсный регулятор | 1984 |

|

SU1170426A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ АСИНХРОННЫЙ ЭЛЕКТРОПРИВОД | 2008 |

|

RU2401502C2 |

| Способ автоматического регулирования частоты вращения ротора синхронного генератора и регулятор для его реализации | 2023 |

|

RU2823536C1 |

| Адаптивный регулятор | 1977 |

|

SU746414A1 |

| СЛЕДЯЩИЙ ЭЛЕКТРОПРИВОД С АСИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2006 |

|

RU2358382C2 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР С ОГРАНИЧЕНИЯМИ ВЫХОДНЫХ СИГНАЛОВ | 1999 |

|

RU2156992C1 |

Изобретение относится к автоматическим регуляторам электродвигателей. Быстродействующий адаптивный регулятор частоты вращения содержит блок инвертирования, пропорциональную и интегральную части регулятора, четыре блока сравнения, два блока умножения, блок единичной функции, блок выделения модуля, нелинейный ограничитель. Первый выход пропорциональной части регулятора соединен с входом блока выделения модуля, выход которого соединен с прямым входом четвертого блока сравнения, который соединен с входом блока единичной функции, один выход которого соединен с входом первого блока умножения, а второй выход соединен с входом блока инвертирования. Второй вход первого блока умножения соединен с первым выходом интегральной части регулятора, а выход соединен с инверсным входом второго блока сравнения. Выход блока инвертирования соединен с входом второго блока умножения, выход которого соединен с инверсным входом первого блока сравнения, на прямой вход которого подается сигнал задания. Выход первого блока сравнения, прямой вход второго блока сравнения, интегральная часть регулятора, прямой вход третьего блока сравнения, пропорциональная часть регулятора и нелинейный ограничитель тока соединены последовательно. Технический результат заключается в увеличении быстродействия системы регулирования частоты вращения электродвигателя. 1 ил.

Быстродействующий адаптивный регулятор частоты вращения электродвигателя, содержащий блок инвертирования, пропорциональную и интегральную части регулятора, отличающийся тем, что введены четыре блока сравнения, два блока умножения, блок единичной функции, блок выделения модуля, нелинейный ограничитель тока, подключены таким образом, что первый выход пропорциональной части регулятора соединен с входом блока выделения модуля, выход которого соединен с прямым входом четвертого блока сравнения, на инверсный вход которого подается эталонный сигнал, а выход четвертого блока сравнения соединен с входом блока единичной функции, один из выходов которого соединен с входом первого блока умножения, второй вход которого соединен с первым выходом интегральной части регулятора, а выход первого блока умножения соединен с инверсным входом второго блока сравнения на входе интегральной части регулятора, второй выход блока единичной функции соединен с входом блока инвертирования, выход которого соединен с входом второго блока умножения, а выход второго блока умножения соединен с инверсным входом первого блока сравнения, на прямой вход которого подается сигнал задания частоты вращения, выход первого блока сравнения соединен с прямым входом второго блока сравнения, второй выход интегральной части регулятора соединен с прямым входом третьего блока сравнения, выход третьего блока сравнения соединен с входом пропорциональной части регулятора, выход которой соединен с входом нелинейного ограничителя тока.

| SU 1835215 A3, 20.02.1996 | |||

| ЦИФРОВОЙ ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР | 2006 |

|

RU2325681C2 |

| Пропорционально-интегральнодифференциальный регулятор | 1977 |

|

SU696410A1 |

| US 7692397 B2, 06.04.2010. | |||

Авторы

Даты

2017-06-13—Публикация

2015-10-22—Подача