Изобретение относится к цифровой технике в области организации взаимодействия цифровой вычислительной машины (ЦВМ) с памятью и может быть использовано в космической, авиационной, кораблестроительной и других отраслях в качестве устройства для защиты зон памяти (УЗЗП) от несанкционированной записи во время штатной работы ЦВМ.

Известно устройство для защиты памяти (Авторское свидетельство СССР №1003673, с приоритетом от 1988 г.), содержащее первый блок регистров, первый блок триггеров, первый блок элементов И, первый элемент ИЛИ, триггер, регистр адреса и два дешифратора, причем входы первого дешифратора являются входами идентификатора устройства, а выходы соединены с первыми входами первого блока регистров, выходы данных первого блока регистров соединены с соответствующими входами установки триггеров первого блока триггеров, прямые выходы триггеров первого блока триггеров соединены с первыми входами первого блока элементов И, вторые входы которого соединены с прямым выходом триггера, третьи входы первого блока элементов И соединены с выходами второго дешифратора, выход элемента ИЛИ соединен с входом разрешения выдачи адреса регистра адреса и является управляющим выходом устройства.

Недостатками известного устройства являются узкие функциональные возможности и сложность схемы.

Наиболее близким к заявляемому устройству по технической сущности и достигаемому эффекту является устройство для защиты памяти (патент РФ №2020564, с приоритетом от 30.09.1994), которое содержит четыре элемента ИЛИ, два регистра, группу элементов И, элемент задержки, регистр адреса и дешифратор, блок памяти, формирователь импульсов и элемент И.

Недостатками известного устройства являются узкие функциональные возможности и сложность схемы.

Во время штатной работы ЦВМ с памятью возможна несанкционированная запись пользователем информации в зоны, предназначенные для хранения моделей памяти (программы и константы) и информации необходимой для восстановления вычислительного процесса.

Задача изобретения - разработать устройство, которое при минимальном количестве элементов обеспечит сохранность информации, записанной в оперативной и постоянной зонах памяти при несанкционированной попытке перезаписи информации во время штатной работы ЦВМ.

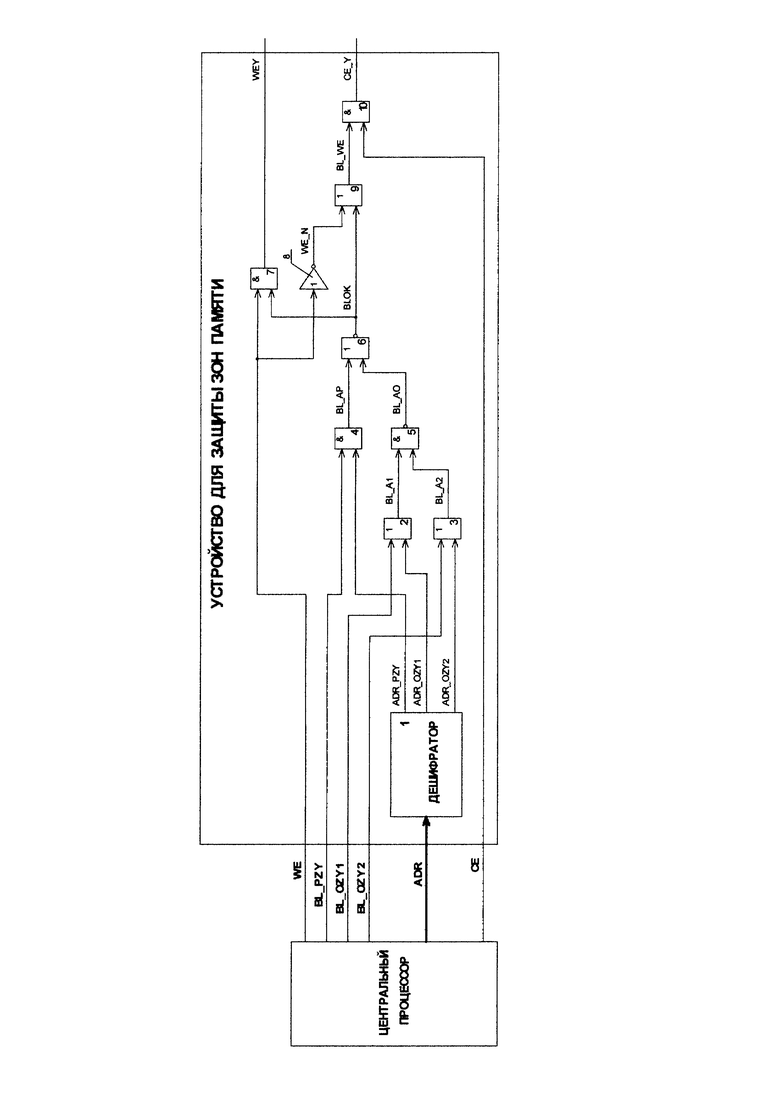

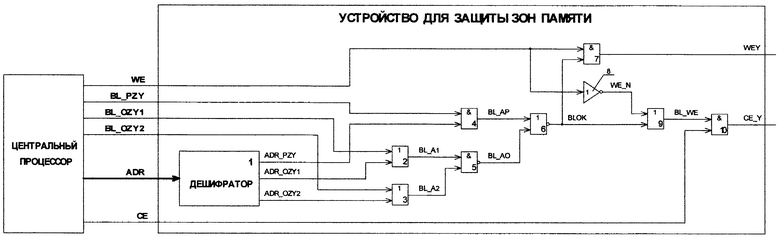

На фигуре представлена структурная схема изобретения, включающая в себя следующие элементы:

1 - дешифратор;

2, 3, 9 - первый, второй, третий элементы «ИЛИ»;

4, 7, 10 - первый, второй, третий элементы «И»;

5 - элемент «И-НЕ»;

6 - элемент «ИЛИ-НЕ»;

8 - инвертор.

Схема имеет следующие сигналы:

1. Входные:

WE - чтение/запись информации в память;

СЕ - разрешение обращения в память;

BL_PZY - блокировка зоны постоянного запоминающего устройства (ПЗУ);

BL_OZY1, BL_OZY2 - блокировка первой, второй зоны оперативного запоминающего устройства (ОЗУ);

ADR - шина адреса.

2. Внутренние:

ADR_PZY - адресация зоны ПЗУ;

ADR_OZY1, ADR_OZY2 - адресация первой, второй зоны ОЗУ;

BL_A1, BL_A2 - блокировка адреса первой, второй зоны ОЗУ;

BL_AO - блокировка адреса ОЗУ;

BL_AP - блокировка адреса ПЗУ;

BL_OK - сигнал блокировки;

WE_N - сигнал записи информации;

BL_WE - блокировка записи информации;

3. Выходные:

WEY - сигнал чтения/записи информации; CE_Y - сигнал разрешения обращения в память;

Элементы предлагаемого технического решения имеют следующие связи: На устройство для защиты зон памяти от несанкционированной записи поступают входные сигналы: шины адреса (ADR), разрешения обращения в память (СЕ), входной сигнал чтения/записи информации в память (WE), блокировок зоны ПЗУ (BL_PZY) и двух зон ОЗУ (BL_OZY1, BL_OZY2).

Дешифратор (1) принимает сигнал ADR и вырабатывает сигналы адресации зоны ПЗУ (ADR_PZY) и двух зон ОЗУ (ADR_OZY1, ADR_OZY2), которые поступают на первый элемент «И» (4) и на первый (2) и второй (3) элементы «ИЛИ» соответственно. Первый (2) и второй (3) элементы «ИЛИ» также принимают сигналы BL_OZY1 и BL_OZY2 соответственно и связаны сигналами блокировки первой (BL_A1) и второй (BL_A2) зоны ОЗУ соответственно с элементом «И-НЕ» (5), который связан сигналом блокировка адреса ОЗУ (BLAO) с элементом «ИЛИ-НЕ» (6). Первый элемент «И» (4) также принимает сигнал BL_PZY и связан сигналом блокировка адреса ПЗУ (BL_AP) с элементом «ИЛИ-НЕ» (6), который направляет сигнал блокировки (BLOK) на второй элемент «И» (7) и третий элемент «ИЛИ» (9). Второй элемент «И» (7) также принимает сигнал WE и вырабатывает сигнал чтения/записи информации (WEY). Инвертор (8) принимает сигнал WE, передавая сигнал записи информации (WE_N) на третий элемент «ИЛИ» (9), который в свою очередь связан сигналом блокировка записи информации (BL_WE) с третьим элементом «И» (10), который также принимает сигнал СЕ и вырабатывает сигнал разрешения обращения в память (CEY).

Сигналы WEY и CE_Y являются выходными и поступают на выход устройства для защиты зон памяти от несанкционированной записи.

Принцип работы УЗЗП:

Блокировка зоны ПЗУ от несанкционированной записи при штатной работе ЦВМ устанавливается в следующих случаях:

- аппаратно при отсутствии контрольно испытательного комплекса (КИК);

- аппаратно при наличии КИК после окончания начального сброса ЦВМ;

- программно после выполнения определенной команды процессора.

При установке блокировки зоны ПЗУ, процессор вырабатывает сигнал BL_PZY высоким уровнем, который поступает на элемент «И» (4). При попытке записи информации в область памяти ПЗУ на дешифратор (1) по шине адреса ADR поступает адрес соответствующей ячейки ПЗУ и на его выходе вырабатывается сигнал ADR_PZY высоким уровнем, с процессора на вход УЗЗП поступают сигналы WE и СЕ высоким уровнем. Таким образом на элемент «И» (4) приходят два сигнала высоким уровнем и на его выходе устанавливается сигнал BLAP высоким уровнем, который приходит на элемент «ИЛИ-НЕ» (6). Вне зависимости от уровня сигнала BL_AO, на выходе «ИЛИ-НЕ» (6) устанавливается сигнал BLOK низким уровнем, который приходит на элемент «И» (7) и блокирует сигнал записи в память WE - на выходе элемента «И» (7) низкий уровень. Так же сигнал BLOK приходит на вход элемента «ИЛИ» (9), где складывается с инверсией сигнала WE после инвертора (8) - WE_N низкий уровень, и на выходе элемента «ИЛИ» (9) устанавливается сигнал BL_WE низким уровнем, который приходит на вход элемента «И» (10) и блокирует сигнал разрешения обращения в память СЕ. На выходе элемента «И» (10) устанавливается низкий уровень. Таким образом на выходе УЗЗП мы имеем два сигнала WEY и CE_Y низким уровнем, которые поступают непосредственно на управляющие входы памяти (запись - высоким уровнем). Это означает что запись информации в область памяти ПЗУ не происходит. Снимается блокировка зоны ПЗУ в следующих случаях:

- аппаратно, когда ЦВМ находится в состоянии начального сброса при подключенном КИК;

- программно, после выполнения определенной команды.

Если снимается блокировка зоны ПЗУ, то на вход УЗЗП с процессора поступает сигнал BL_PZY низким уровнем, он же приходит на вход элемента «И» (4), вследствие чего на его выходе устанавливается сигнал BL_AP низким уровнем, который приходит на вход элемента «ИЛИ-НЕ» (6). При записи информации в область памяти ПЗУ на вход УЗЗП с процессора поступают сигналы WE и СЕ высоким уровнем, а на дешифраторе (1) вырабатываются сигналы ADR_PZY, ADR_OZY1, ADR_OZY2 высоким уровнем. Сигналы ADR_OZY1 и ADR_OZY2 поступают на входы элементов «ИЛИ» (2) и «ИЛИ» (3) соответственно, и устанавливают на их выходах сигналы BL_A1 и BL_A2 высоким уровнем. Сигналы BL_A1 и BL_A2 поступают на входы элемента «И-НЕ» (5) и устанавливают на его выходе сигнал BL_AO низким уровнем, который приходит на вход элемента «ИЛИ-НЕ» (6). Сигналы BL_AP и BL_AO на входе «ИЛИ-НЕ» (6) низким уровнем устанавливают на его выходе сигнал BLOK высоким уровнем, который приходит на вход элементов «И» (7) и «ИЛИ» (9). На входы элемента «И» (7) приходят два сигнала высоким уровнем WE и BLOK, что приводит к появлению на его выходе сигнала WEY высоким уровнем. На выходе элемента «ИЛИ» (9) устанавливается сигнал BL_WE высоким уровнем, т.к. на его вход пришел сигнал BLOK высоким уровнем. На входы элемента «И» (10) приходят два сигнала высоким уровнем BL_WE и СЕ, что приводит к появлению на его выходе сигнала CE_Y высоким уровнем. Таким образом на выходе УЗЗП мы имеем два сигнала WEY и CE_Y высоким уровнем, которые поступают непосредственно на управляющие входы памяти, что соответствует записи информации в адресуемую зону памяти.

Блокировки первой (сигнал BL_OZY1) и второй (сигнал BL_OZY2) зоны памяти ОЗУ от несанкционированной записи при штатной работе устанавливаются аппаратно по начальному сбросу ЦВМ. Снимаются блокировки программно и могут быть вновь установлены по определенным командам процессора. При этом блокировки обеих зон ОЗУ могут быть установлены/сняты как одновременно, так и для каждой зоны в отдельности.

По начальному сбросу ЦВМ устанавливаются блокировки обеих зон ОЗУ - на вход УЗЗП и входы первого (2) и второго (3) элементов «ИЛИ» с процессора низким уровнем поступают сигналы BL_OZY1 и BL_OZY2 соответственно. При попытке записи информации в любую из зон ОЗУ на выходе дешифратора (1) сформируется один из сигналов ADR_OZY1 или ADR_OZY2 низким уровнем в зависимости от зоны записи, а так же на вход УЗЗП с процессора поступят сигналы WE и СЕ высоким уровнем. Соответственно на выходе из первого (2), либо второго (3) элемента «ИЛИ» установится один из сигналов BL A1 или BLA2 низким уровнем, в зависимости от зоны записи, которые в свою очередь поступают на входы элемента «И-НЕ» (5), в результате чего на его выходе установится сигнал BL_AO высоким уровнем, который приходит на вход элемента «ИЛИ-НЕ» (6). Вне зависимости от уровня сигнала BL_AP, на выходе «ИЛИ-НЕ» (6) устанавливается сигнал BLOK низким уровнем.

Снимаются блокировки зон ОЗУ программным образом:

1. Если снимается блокировка первой зоны, то на вход УЗЗП с процессора поступает сигнал BL_OZY1 высоким уровнем, он поступает на вход элемента «ИЛИ» (2), на его выходе устанавливается сигнал BL A1 высоким уровнем. Сигнал BL_A1 поступает на вход элемента «И-НЕ» (5). При попытке записи информации в зону 1 ОЗУ на вход УЗЗП поступают сигналы WE и СЕ высоким уровнем, а на выходе дешифратора (1) формируются сигналы: ADR_PZY, ADR_OZY1 - низким уровнем; ADR_OZY2 - высоким уровнем. Сигнал ADR_PZY приходит на вход элемента «И» (4), на его выходе установится сигнал BL_AP низким уровнем, который поступает на вход элемента «ИЛИ-НЕ» (6). Сигнал ADR_OZY2 приходит на вход элемента «ИЛИ» (3), на его выходе установится сигнал BL_A2 высоким уровнем, который поступает на вход элемента «И-НЕ» (5). Два сигнала BL_A1 и BL_A2 высоким уровнем на входе элемента «И-НЕ» (5), установят на его выходе сигнал BL_AO низким уровнем, который поступает на вход элемента «ИЛИ-НЕ» (6). Сигналы BL_AP и BL_AO на входе «ИЛИ-НЕ» (6) низким уровнем устанавливают на его выходе сигнал BLOK высоким уровнем, в результате чего вырабатываются два сигнала WEY и CE_ высоким уровнем, что соответствует записи информации в адресуемую зону памяти ОЗУ 1, это подтверждает, что блокировка записи зоны 1 ОЗУ была снята.

2. Если снимается блокировка второй зоны, то на вход УЗЗП с процессора поступает сигнал BL_OZY2 высоким уровнем, он поступает на вход элемента «ИЛИ» (3), на его выходе устанавливается сигнал BL_A2 высоким уровнем. Сигнал BL_A2 поступает на вход элемента «И-НЕ» (5). При записи информации в зону 2 ОЗУ на вход УЗЗП с процессора поступают сигналы WE и СЕ высоким уровнем, а на выходе дешифратора (1) формируются сигналы: ADR_PZY, ADR_OZY2 - низким уровнем; ADR_OZY1 - высоким уровнем. Сигнал ADR_ZY приходит на вход элемента «И» (4), на его выходе установится сигнал BL_AP низким уровнем, который поступает на вход элемента «ИЛИ-НЕ» (6). Сигнал ADR_OZY1 приходит на вход элемента «ИЛИ» (2), на его выходе установится сигнал BL_A1 высоким уровнем, который поступает на вход элемента «И-НЕ» (5). Два сигнала BL_A1 и BL_A2 высоким уровнем на входе элемента «И-НЕ» (5), установят на его выходе сигнал BL_AO низким уровнем, который поступает на вход элемента «ИЛИ-НЕ» (6). Сигналы BL_AP и BL_AO на входе «ИЛИ-НЕ» (6) низким уровнем устанавливают на его выходе сигнал BLOK высоким уровнем, в результате чего вырабатываются два сигнала WEY и CE_Y высоким уровнем, что соответствует записи информации в адресуемую зону памяти ОЗУ 2, это подтверждает, что блокировка записи зоны 2 ОЗУ была снята.

УЗЗП было протестировано в испытательной аппаратуре с помощью, программируемой логической интегральной схемы.

Техническим результатом устройства является защита оперативной и постоянной памяти от несанкционированной записи во время штатной работы ЦВМ, при минимальном количестве элементов в схеме устройства.

Таким образом заявлено устройство для защиты зон памяти от несанкционированной записи, содержащее дешифратор (1), три элемента «ИЛИ» (2,3,9), три элемента «И» (4,7,10), отличающееся тем, что дешифратор (1) принимает входные сигналы шины адреса, с его выходов сигналы адресации зоны постоянно запоминающего устройства (ПЗУ), первой и второй зоны оперативно запоминающего устройства (ОЗУ) совместно с входными сигналами блокировок зон памяти поступают на первый элемент «И» (4) и на первый и второй элементы «ИЛИ» (2,3) соответственно; первый и второй элементы «ИЛИ» (2,3) связаны сигналами с элементом «И-НЕ» (5), связанным сигналом с элементом «ИЛИ-НЕ»(6), который также принимает сигнал от первого элемента «И» (4) и направляет сигнал на второй элемент «И» (7) и третий элемент «ИЛИ» (9); сигнал разрешения обращения в память поступает на третий элемент «И»; сигнал чтения/записи информации в память поступает на второй элемент «И» (10) и инвертор, причем, второй элемент «И» (7) направляет сигнал на выход из системы, а с инвертора (8) сигнал поступает на третий элемент «ИЛИ» (9), который в свою очередь связан сигналом с третьим элементом «И» (10), сигнал из которого идет на выход из системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| СИСТЕМА УПРАВЛЕНИЯ БОЛЬШЕГРУЗНЫМ КРАНОМ | 2001 |

|

RU2196102C1 |

| Устройство для устранения последствий случайных сбоев | 1980 |

|

SU886002A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для восстановления информации при сбоях в блоках ЦВМ | 1983 |

|

SU1124314A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

Изобретение относится к цифровой технике в области организации взаимодействия цифровой вычислительной машины (ЦВМ) с памятью и может быть использовано в космической, авиационной, кораблестроительной и других отраслях в качестве устройства для защиты зон памяти от несанкционированной записи во время штатной работы ЦВМ. Техническим результатом является обеспечение сохранности информации, записанной в определенных зонах памяти, от несанкционированной попытки переписи информации во время штатной работы ЦВМ. Заявленное изобретение представляет собой устройство, содержащее дешифратор, три элемента «И», три элемента «ИЛИ», инвертор, элементы «И-НЕ» и «ИЛИ-НЕ», при этом связи между элементами исключают возможность несанкционированной записи информации в зоны памяти. 1 ил.

Устройство для защиты зон памяти от несанкционированной записи, содержащее дешифратор, три элемента «И», три элемента «ИЛИ», отличающееся тем, что дешифратор принимает входные сигналы шины адреса, с его выходов сигналы адресации зоны постоянно запоминающего устройства (ПЗУ), первой и второй зоны оперативно запоминающего устройства (ОЗУ) совместно с входными сигналами блокировок зон памяти поступают на первый элемент «И» и на первый и второй элементы «ИЛИ» соответственно; первый и второй элементы «ИЛИ» связаны сигналами с элементом «И-НЕ», связанным сигналом с элементом «ИЛИ-НЕ», который также принимает сигнал от первого элемента «И» и направляет сигнал на второй элемент «И» и третий элемент «ИЛИ»; сигнал разрешения обращения в память поступает на третий элемент «И»; сигнал чтения/записи информации в память поступает на второй элемент «И» и инвертор, причем второй элемент «И» направляет сигнал на выход из системы, а с инвертора сигнал поступает на третий элемент «ИЛИ», который в свою очередь связан сигналом с третьим элементом «И», сигнал из которого идет на выход из системы.

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для защиты памяти | 1988 |

|

SU1508216A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2020564C1 |

| US 5784704 A, 21.07.1998. | |||

Авторы

Даты

2021-11-16—Публикация

2020-12-28—Подача