Изобретение относится к импульсной технике в частности к устройствам для задания фазового сдвига электрических сигналов и может быть использовано в цифровых системах управления полупроводниковыми преобразователями.

Известны аналоговые фазосмещающие устройства (ФСУ) различного типа /1/ наиболее совершенными из которых являются ФСУ вертикального типа.

Их недостатками являются необходимость настройки и погрешности, вызванные дрейфом и нестабильностью элементов.

Известно цифровое ФСУ вертикального типа, содержащее числовой компаратор, генератор импульсов, счетчик и узел синхронизации /2/.

Его недостатком является погрешность задания углов управления, в условиях нестабильности частоты напряжения при питании от источников ограниченной мощности.

Наиболее близким по технической сущности к изобретению является цифровое фазосмещающее устройство, содержащее формирователь прямоугольных импульсов, первый формирователь коротких импульсов, выход которого подключен к входу записи исходного числа вычитающего счетчика, логический элемент НЕ, выход которого подключен к входу второго формирователя коротких импульсов и к первому входу второго логического элемента И, связанного вторым входом с выходом генератора импульсов стабильной частоты и вторым входом первого логического элемента И, суммирующий счетчик, счетный вход которого подключен к выходу второго логического элемента И, сбросовый вход - к выходу второго формирователя коротких импульсов, а разряды выхода - к соответствующим разрядам входа исходного числа вычитающего счетчика и входа адреса первой координаты блока памяти, к разрядам входа адреса второй координаты которого подключены соответствующие разряды выхода задающего регистра, а разряды выхода блока памяти соединены с соответствующими разрядами второго входа числового компаратора, выход РАВНО которого является выходом устройства и который разрядами первого входа связан с соответствующими разрядами выхода вычитающего счетчика, вычитающий вход которого подключен к выходу первого логического элемента И, первый вход которого связан с входом логического элемента НЕ, входом первого формирователя коротких импульсов и выходом формирователя прямоугольных импульсов, вход которого через диод подключен к сети /3/.

Это устройство обеспечивает удовлетворительную погрешность, практически плавное изменение заданного угла управления и высокую его стабильность в условиях нестабильности частоты питающей сети. Однако его область эффективного функционирования распространяется лишь на однофазные сети.

Цель изобретения - расширение функциональных возможностей за счет увеличения числа каналов управления.

Цель изобретения достигается тем, что трехканальное цифровое фазо-смещающее устройство, содержащее первый формирователь прямоугольных импульсов, первый формирователь коротких импульсов, выход которого подключен к входу записи исходного числа первого вычитающего счетчика, логический элемент НЕ, выход которого подключен к входу второго формирователя коротких импульсов и к первому входу второго логического элемента И, связанного вторым входом с выходом генератора импульсов стабильной частоты и вторым входом первого логического элемента И, суммирующий счетчик, счетный вход которого подключен к выходу второго логического элемента И, сбросовый вход - к выходу второго формирователя коротких импульсов, а разряды выхода - к соответствующим разрядам входа исходного числа первого вычитающего счетчика, вычитающий вход которого подключен к выходу первого логического элемента И, первый вход которого связан с входом логического элемента НЕ, входом первого формирователя коротких импульсов и выходом первого формирователя прямоугольных импульсов, вход которого через первый диод подключен к первой фазе сети, а разряды выхода первого вычитающего счетчика подключены к соответствующим разрядам первого входа первого числового компаратора, выход РАВНО которого является первым выходом устройства и который разрядами второго входа связан с соответствующими разрядами выхода блока памяти, к разрядам входа адреса второй координаты которого подключены соответствующие разряды выхода задающего регистра, снабжено третьим и четвертым логическими элементами И, вторым и третьим вычитающими счетчиками, вторым и третьим формирователями прямоугольных импульсов, третьим и четвертым формирователями коротких импульсов, вторым и третьим диодами, вторым и третьим числовыми компараторами и регистром памяти, подключенного входом записи к выходу первого формирователя коротких импульсов, разрядами входа - к соответствующим разрядам выхода суммирующего счетчика, а разрядами выхода - к соответствующим разрядам входа адреса первой координаты блока памяти и входов исходного числа второго и третьего вычитающих счетчиков, разряды выходов которых подключены к соответствующим разрядам первых входов второго и третьего числовых компараторов соответственно, выходы РАВНО которых являются выходами второго и третьего каналов устройства соответственно, а разряды вторых входов числовых компараторов соединены с соответствующими разрядами выхода блока памяти, кроме того вторая фаза питающей сети через второй диод подключена к входу второго формирователя прямоугольных импульсов, выход которого соединен непосредственно с первым входом третьего логического элемента И, а через третий формирователь коротких импульсов с входом записи исходного числа второго вычитающего счетчика, вычитающий вход которого подключен к выходу третьего логического элемента И, связанного вторым входом с входом генератора стабильных импульсов и вторым входом четвертого логического элемента И, выход которого соединен с вычитающим входом третьего вычитающего счетчика, вход записи исходного числа которого подключен к выходу четвертого формирователя коротких импульсов, связанного входом с первым входом четвертого логического элемента И и выходом третьего формирователя прямоугольных импульсов, вход которого через третий диод подключен к третьей фазе питающей сети.

Регистр памяти обеспечивает хранение информации о длительности полупериода питающего напряжения для трех каналов. Вторые диод, формирователь прямоугольных импульсов, вычитающий счетчик, числовой компаратор, третий формирователь коротких импульсов и третий логический элемент И и их связи обеспечивают формирование сигнала на выходе второго канала. Третьи диод, формирователь прямоугольных импульсов, вычитающий счетчик, числовой компаратор, четвертый формирователь коротких импульсов и четвертый логический элемент И и их связи обеспечивают формирование сигнала на выходе третьего канала.

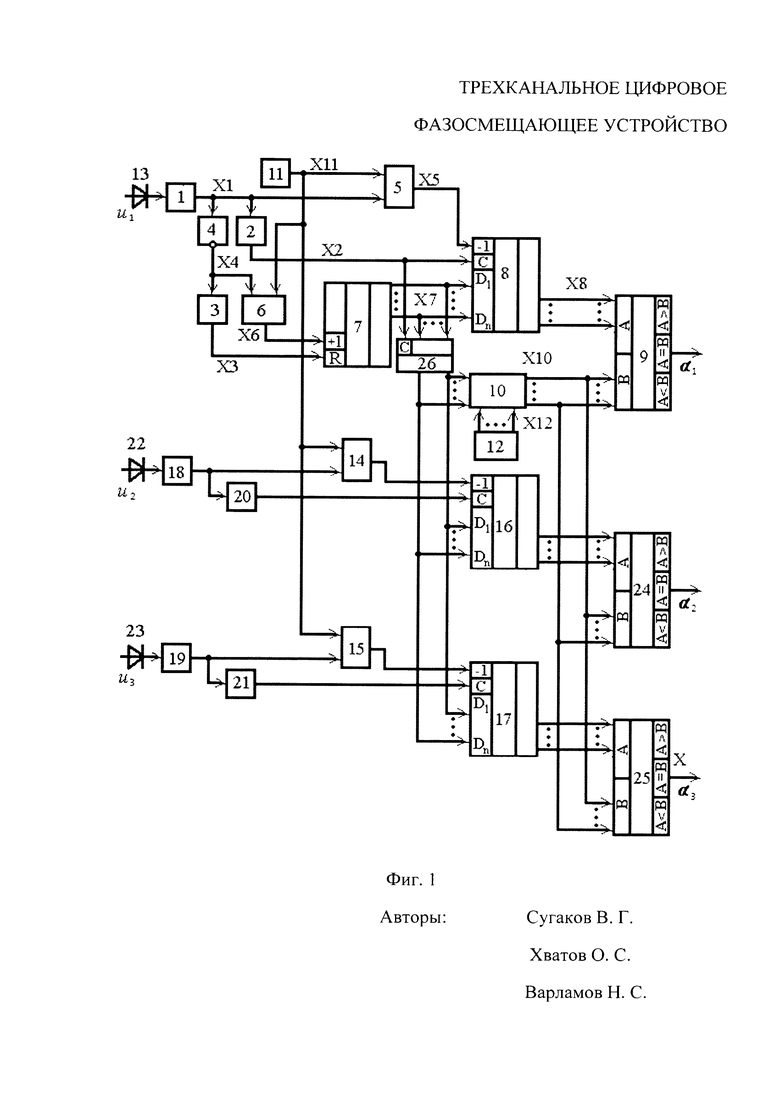

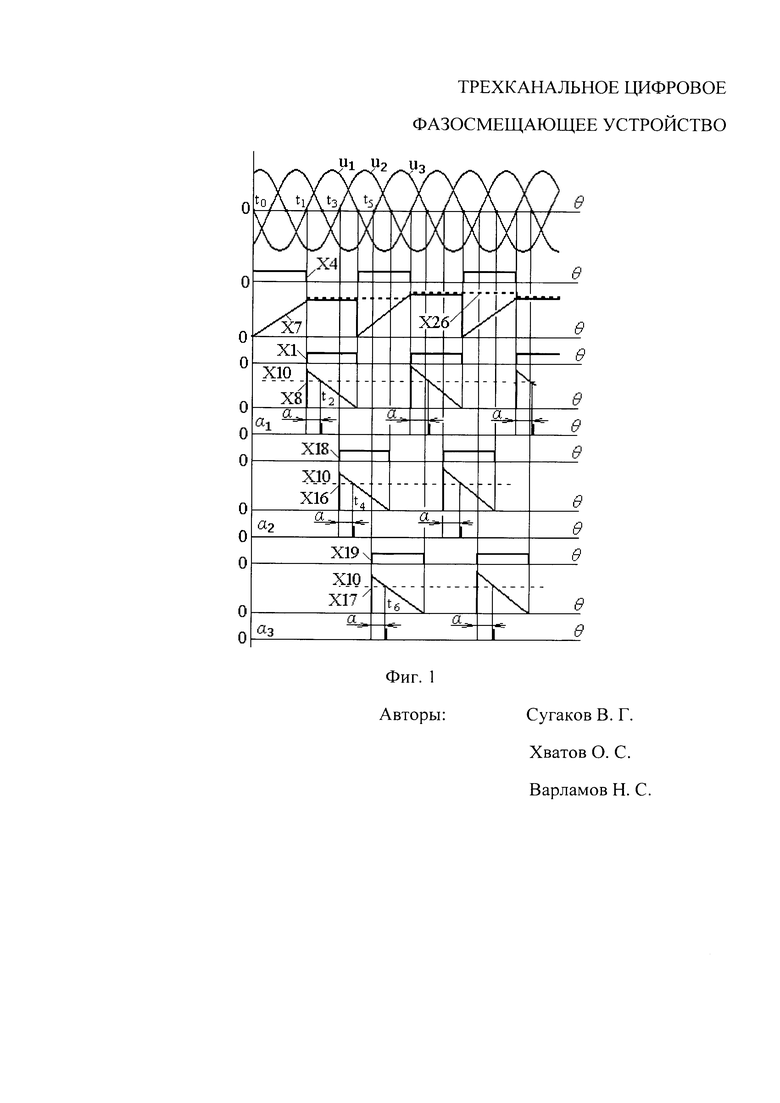

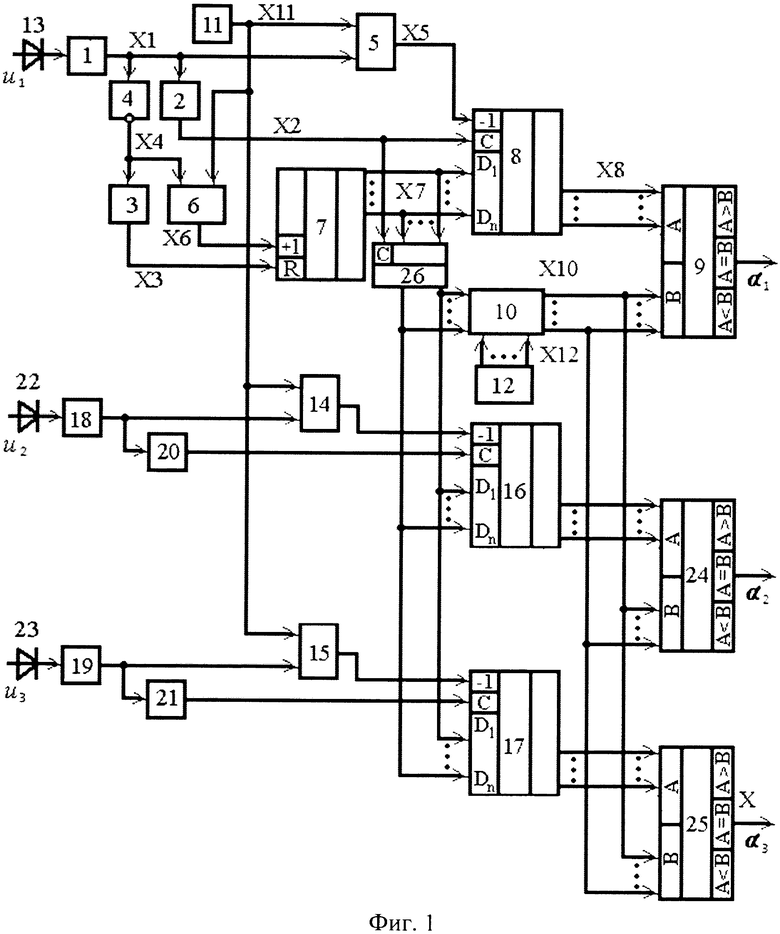

На фиг. 1 представлена схема трехканального цифрового фазосмещающего устройства, на фиг. 2 - эпюры сигналов на элементах устройства.

Цифровое фазосмещающее устройство (фиг. 1) включает формирователь прямоугольных импульсов 1, первый 2 и второй 3 формирователи коротких импульсов, логический элемент НЕ 4, первый 5 и второй 6 логический элемент И, суммирующий счетчик 7, вычитающий счетчик 8, числовой компаратор 9, блок памяти 10, генератор 11 импульсов стабильной частоты, задающий регистр 12, первый диод 13, третий 14 и четвертый 15 логические элементы И, второй 16 и третий 17 вычитающие счетчики, второй 18 и третий 19 формирователи прямоугольных импульсов, третий 20 и четвертый 21 формирователи коротких импульсов, второй 22 и третий 23 диоды, второй 24 и третий 25 числовые компараторы, регистр памяти 26. На выходе задающего регистра 12 устанавливается код угла управления. По адресам двухмерного блок памяти 10 записаны коды K10(i,j) задающего напряжения соответствующие частоте ƒc(i) питающего напряжения и заданному углу α(j) управления

К100(i,j)=K7(i)/K12(j),

где К7(i)/ - i-тый адрес по первой координате, который формируется на выходе счетчика 7 и равен коду частоты питающего напряжения К7(i)=ƒ11/(2fC(i));

ƒ11 - частота генератора 11 импульсов стабильной частоты;

ƒС(i) - i-тое значение частоты питающего напряжения, которая изменяется в диапазоне ƒном-Δƒ≤fC(i≤ƒном+Δƒ,

ƒном - номинальная частота;

Δƒ - отклонение частоты;,

i - номер адреса по первой координате i=1, 2, 3 … n, при этом ƒC(1) соответствует ƒC=ƒном+Δƒ, а ƒС(n) соответствует ƒC=ƒном-Δƒ;

К12(j) - j-тый адрес по второй координате К12(j)=π/α(j)=180°/α(j), который задается регистром 12;

j - номер адреса по второй координате j=1, 2, 3…m, при этом К12(1) соответствует α(1)=180°/m, a К12(m) соответствует α(m)=180°.

Устройство работает следующим образом. В момент времени t0 (фиг. 2) появляется отрицательной полуволна питающего напряжения т первой фазы. Сигнал X1 на выходе формирователя 1 исчезает, а на выходе логического элемента НЕ 4 сигнал Х4 появляется. По фронту импульса Х4 формирователь 3 коротких импульсов вырабатывает импульс Х3, который обнуляет счетчик 7. Одновременно импульсом Х4 с выхода элемента НЕ 4, длительность которого равна половине периода TC питающего напряжения u1, подготавливается по первому входу элемент И 6. С выхода генератора импульсов 11 через элемент И 6 на счетный вход счетчика 7 начинают поступать импульсы Х6. На его выходе начинает формироваться код Х7 полупериода TC/2 питающего напряжения. Его формирование завершается в момент времени t1 (фиг. 2), когда через диод 13 проходит на вход формирователя 1 положительная полуволна питающего напряжения u1. При этом исчезает сигнал Х4 на выходе элемента НЕ 4, предотвращая дальнейшее поступление импульсов X11 на счетчик 7, и появляется сигнал X1 на выходе формирователя 1. По фронту сигнала X1 формирователь 2 вырабатывает импульс Х2, которым в счетчик 8 и регистр памяти 26 записывается код Х7 полупериода питающего напряжения с выхода счетчика 7. Одновременно сигналом X1 с выхода формирователя 1 подготавливается элемент И 5 по первому входу. Через элемент И 5 с выхода генератора 11 на вычитающий вход счетчика 8 проходят импульсы Х5. Код Х8 на выходе счетчика 8 начинает уменьшаться. Этот код Х8 поступает на первый вход числового компаратора 9. На второй вход числового компаратора 9 подан код X10 управляющего напряжения с выхода блока памяти 10, который выбран из ячеек блока памяти 10 в зависимости от кода Х26 полупериода, сформированного на выходе счетчика 7, и кода X12 угла управления, установленного на выходе регистра 12. Коды Х8 и X10, поступающие на входы компаратора 9 сравниваются.

В момент времени t2 (фиг. 2), когда наступает равенство кодов на входных компаратора 9, на его выходе появляется управляющий сигнал α1, который с выхода первого канала поступает на выходной формирователь системы управления, который открывает соответствующий вентиль вентильного комплекта (на схеме не показаны).

При появлении положительной полуволны напряжения второй фазы u2 (момент времени t3 на фиг. 2), которая проходит через диод 22, формирователь 18 выдает прямоугольный импульс X18, подготавливающий логический элемент И 14 по первому входу. Одновременно по фронту сигнала X18 формирователь 20 выдает короткий импульс Х20, которым в вычитающий счетчик 16 заносится код 26 полупериода питающего напряжения с выхода регистра 26. Импульсы X11 с выхода генератора 11 через элемент И 14 поступают на вычитающий вход счетчика 16 и код X16 на его выходе уменьшается. Этот код X16 подается на первый вход компаратора 24, где сравнивается с кодом X10, поступающим с выхода блока памяти 10. В момент времени t4 (фиг. 2), когда коды на входах компаратора 24 становятся равными, на его выходе появляется управляющий сигнал α2. Этот сигнал α2 с выхода второго канала подается в систему управления преобразователем (на схеме не показаны).

В момент времени 15 (фиг. 2) положительная полуволна напряжения третий фазы u3, через диод 23 поступает на вход формирователя 19. По фронту сигнала с выхода формирователя 19 формирователь 21 выдает импульс, записывающий в счетчик 17 код полупериода питающего напряжения с выхода регистра 26. Вместе с тем на вычитающий вход счетчика 17 через элемент И 15 начинают поступать импульсы с выхода генератора 11. Убывающий код X17 поступает с выхода счетчика 17 на первый вход компаратора 25, где сравнивается с кодом X10 поступающим с выхода блока памяти 10. В момент совпадения кодов X17 и X10 (момент времени t6 на фиг. 2), на выходе компаратора появляется сигнал α3 выхода третьего канала, который поступает в систему управления.

Далее процесс появления сигналов α1, α2 и α3 на выходах каналов периодически повторяется, как описано ранее. При этом каждый раз во время отрицательного полупериода питающего напряжения u1 первой фазы происходит измерение длительности полупериода, код Х7 которого записывается в регистр 26 с началом положительной полуволны напряжения u1. Если период питающего напряжения изменяется, то соответственно меняется код X10 на выходе блока памяти 10, а угол управления остается неизменным и соответствует коду на выходе регистра 12.

Таким образом, предложенное устройство обеспечивает управление полупроводниковыми преобразователями, которые могут питаться от однофазной и трехфазной сети при практически плавном изменении заданного угла управления и высокой его стабильность в условиях нестабильности частоты питающей сети. Ступень Δα изменения заданного угла управления α зависит от разрядности m регистра 12 и составляет Δα=180°/m. Погрешность δα угла управления α определяется соотношением частот сети ƒC и генератора ƒ11 импульсов 11 δα<ƒ11/(2ƒC) и разрядностью k счетчиков 7, 8, 16, 17, компараторов 9, 24, 25 и блока памяти 10, которая связана с упомянутыми частотами соотношением ƒ11/(2ƒC)<2k+1-1.

Источники информации

1. Горбачев Г.Н., Чаплыгин Е.Е. Промышленная электроника: Учебник для вузов / Под ред. В.А. Лабунцова. - М: Энергоатомиздат, 1988, с. 275-287.

2. То же с. 284-285, рис. 8.7.

3. Описание изобретения к патенту RU 2612055 С1, 2017.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ФАЗОСМЕЩАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2612055C1 |

| ЦИФРОВОЕ ФАЗОСМЕЩАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2658598C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| КОРРЕКТОР НЕБАЛАНСА ФАЗНЫХ НАПРЯЖЕНИЙ | 2014 |

|

RU2580941C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

Изобретение относится к импульсной технике, в частности к устройствам для задания фазового сдвига электрических сигналов, и может быть использовано в цифровых системах управления полупроводниковыми преобразователями. Технический результат - расширение функциональных возможностей за счет увеличения числа каналов управления. Цифровое фазосмещающее устройство (фиг. 1) включает формирователь прямоугольных импульсов 1, первый 2 и второй 3 формирователи коротких импульсов, логический элемент НЕ 4, первый 5 и второй 6 логический элемент И, суммирующий счетчик 7, вычитающий счетчик 8, числовой компаратор 9, блок памяти 10, генератор 11 импульсов стабильной частоты, задающий регистр 12, первый диод 13, третий 14 и четвертый 15 логические элементы И, второй 16 и третий 17 вычитающие счетчики, второй 18 и третий 19 формирователи прямоугольных импульсов, третий 20 и четвертый 21 формирователи коротких импульсов, второй 22 и третий 23 диоды, второй 24 и третий 25 числовые компараторы, регистр памяти 26. Устройство обеспечивает управление полупроводниковыми преобразователями, которые могут питаться от однофазной и трехфазной сети при практически плавном изменении заданного угла управления и высокой его стабильности в условиях нестабильности частоты питающей сети. 2 ил.

Трехканальное цифровое фазосдвигающее устройство, содержащее первый формирователь прямоугольных импульсов, первый формирователь коротких импульсов, выход которого подключен к входу записи исходного числа первого вычитающего счетчика, логический элемент НЕ, выход которого подключен к входу второго формирователя коротких импульсов и к первому входу второго логического элемента И, связанного вторым входом с выходом генератора импульсов стабильной частоты и вторым входом первого логического элемента И, суммирующий счетчик, счетный вход которого подключен к выходу второго логического элемента И, сбросовый вход - к выходу второго формирователя коротких импульсов, а разряды выхода - к соответствующим разрядам входа исходного числа первого вычитающего счетчика, вычитающий вход которого подключен к выходу первого логического элемента И, первый вход которого связан с входом логического элемента НЕ, входом первого формирователя коротких импульсов и выходом первого формирователя прямоугольных импульсов, вход которого через первый диод подключен к первой фазе сети, а разряды выхода первого вычитающего счетчика подключены к соответствующим разрядам первого входа первого числового компаратора, выход РАВНО которого является первым выходом устройства и который разрядами второго входа связан с соответствующими разрядами выхода блока памяти, к разрядам входа адреса второй координаты которого подключены соответствующие разряды выхода задающего регистра, отличающееся тем, что с целью расширения функциональных возможностей снабжено третьим и четвертым логическими элементами И, вторым и третьим вычитающими счетчиками, вторым и третьим формирователями прямоугольных импульсов, третьим и четвертым формирователями коротких импульсов, вторым и третьим диодами, вторым и третьим числовыми компараторами и регистром памяти, подключенного входом записи к выходу первого формирователя коротких импульсов, разрядами входа - к соответствующим разрядам выхода суммирующего счетчика, а разрядами выхода - к соответствующим разрядам входа адреса первой координаты блока памяти и входов исходного числа второго и третьего вычитающих счетчиков, разряды выходов которых подключены к соответствующим разрядам первых входов второго и третьего числовых компараторов соответственно, выходы РАВНО которых являются выходами второго и третьего каналов устройства соответственно, а разряды вторых входов числовых компараторов соединены с соответствующими разрядами выхода блока памяти, кроме того, вторая фаза питающей сети через второй диод подключена к входу второго формирователя прямоугольных импульсов, выход которого соединен непосредственно с первым входом третьего логического элемента И, а через третий формирователь коротких импульсов - с входом записи исходного числа второго вычитающего счетчика, вычитающий вход которого подключен к выходу третьего логического элемента И, связанного вторым входом с входом генератора стабильных импульсов и вторым входом четвертого логического элемента И, выход которого соединен с вычитающим входом третьего вычитающего счетчика, вход записи исходного числа которого подключен к выходу четвертого формирователя коротких импульсов, связанного входом с первым входом четвертого логического элемента И и выходом третьего формирователя прямоугольных импульсов, вход которого через третий диод подключен к третьей фазе питающей сети.

| Многоканальное цифровое фазосдвигающее устройство | 1980 |

|

SU955417A1 |

| ЦИФРОВОЕ ФАЗОСМЕЩАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2612055C1 |

| Цифровое фазосдвигающее устройство | 1988 |

|

SU1622835A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2216846C2 |

| US 9306256 B2, 05.04.2016 | |||

| FR 3009442 A1, 06.02.2015. | |||

Авторы

Даты

2019-05-06—Публикация

2018-03-23—Подача