Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единичных сигналов (патент РФ 2256211, кл. G06F 7/38, 2005 г.; патент РФ 2260204, кл. G06F 5/00, 2005 г.), которые формируют двоичный код числа единичных сигналов входного кортежа (x1, …, x8), где xq ∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единичных сигналов, относится схемная сложность, обусловленная тем, что наименьшая из цен по Квайну схем упомянутых аналогов равна 60 и их схемная глубина больше 8.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип параллельный счетчик единичных сигналов (патент РФ 2518641, кл. H03K 21/10, 2014 г.), который содержит элементы И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и формирует двоичный код числа единичных сигналов входного кортежа (x1, …, x8), где xq ∈ {0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что цена по Квайну схемы прототипа равна 56 и его схемная глубина равна 6.

Техническим результатом изобретения является упрощение схемы параллельного счетчика единичных сигналов за счет уменьшения ее цены по Квайну и глубины при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единичных сигналов, содержащем семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и три элемента И, первый, второй входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И, особенность заключается в том, что в него дополнительно введены четыре мажоритарных элемента, причем i-й вход j-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И, особенность заключается в том, что в него дополнительно введены четыре мажоритарных элемента, причем i-й вход j-го  , первый, второй входы второго и первый, второй входы третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-ым входом (j-3)-го мажоритарного элемента, выходом третьего мажоритарного элемента, выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И, выходом четвертого мажоритарного элемента, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами четвертого, пятого, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, второго мажоритарных элементов, выходом первого элемента И, а первый, второй входы первого и i-й вход k-го

, первый, второй входы второго и первый, второй входы третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-ым входом (j-3)-го мажоритарного элемента, выходом третьего мажоритарного элемента, выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И, выходом четвертого мажоритарного элемента, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами четвертого, пятого, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, второго мажоритарных элементов, выходом первого элемента И, а первый, второй входы первого и i-й вход k-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно седьмым, восьмым и (3×k+i-12)-ым входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами шестого, второго, третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом третьего элемента И.

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно седьмым, восьмым и (3×k+i-12)-ым входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами шестого, второго, третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом третьего элемента И.

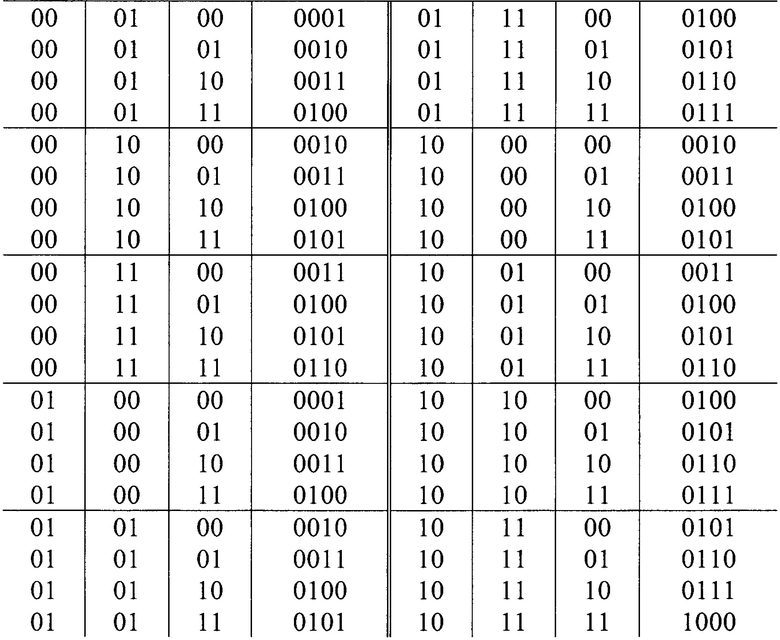

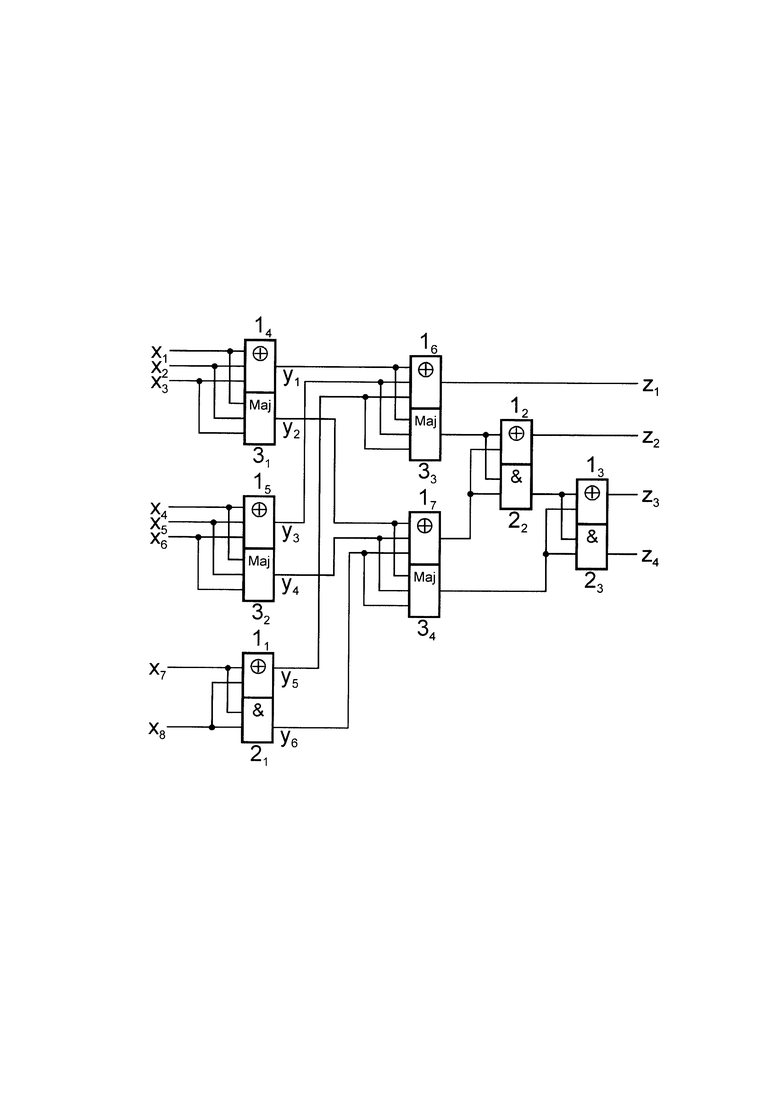

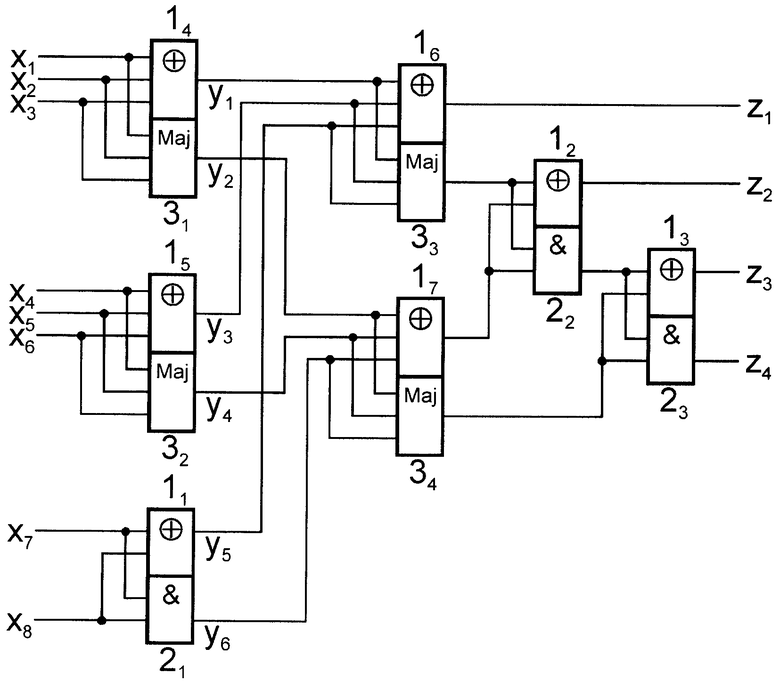

На чертеже представлена схема предлагаемого параллельного счетчика единичных сигналов.

Параллельный счетчик единичных сигналов содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, …, 17, элементы И 21, 22, 23 и мажоритарные элементы 31, …, 34, причем i-й  вход элемента 1j

вход элемента 1j  и первый, второй входы элемента 1i соединены соответственно с i-ым входом элемента 3j-3 и первым, вторым входами элемента 2i, первый, второй входы элемента 12 и первый, второй входы элемента 13 соединены соответственно с выходами элементов 33, 17 и 22, 34, первый, второй, третий входы элемента 16 и первый, второй, третий входы элемента 17 соединены соответственно с выходами элементов 14, 15, 11 и 31, 32, 21, а первый, второй входы элемента 11 и i-й вход элемента

и первый, второй входы элемента 1i соединены соответственно с i-ым входом элемента 3j-3 и первым, вторым входами элемента 2i, первый, второй входы элемента 12 и первый, второй входы элемента 13 соединены соответственно с выходами элементов 33, 17 и 22, 34, первый, второй, третий входы элемента 16 и первый, второй, третий входы элемента 17 соединены соответственно с выходами элементов 14, 15, 11 и 31, 32, 21, а первый, второй входы элемента 11 и i-й вход элемента  являются соответственно седьмым, восьмым и (3×k+i-12)-ым входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами элементов 16, 12, 13 и 23.

являются соответственно седьмым, восьмым и (3×k+i-12)-ым входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами элементов 16, 12, 13 и 23.

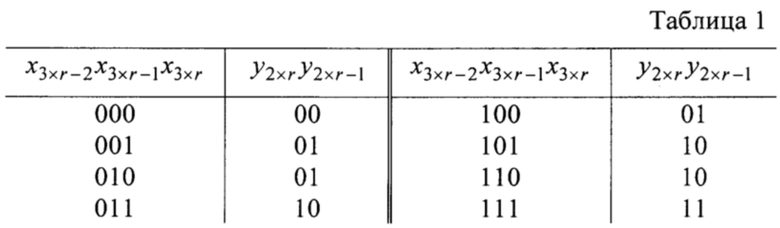

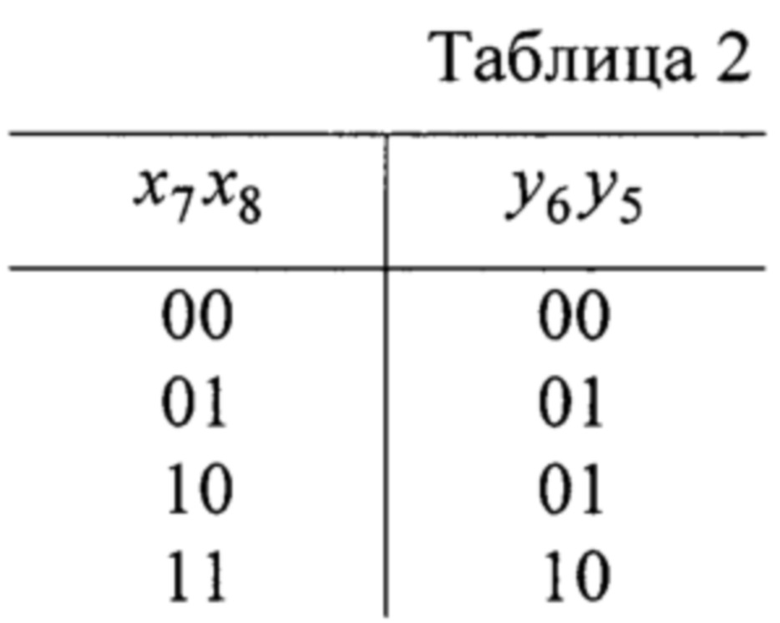

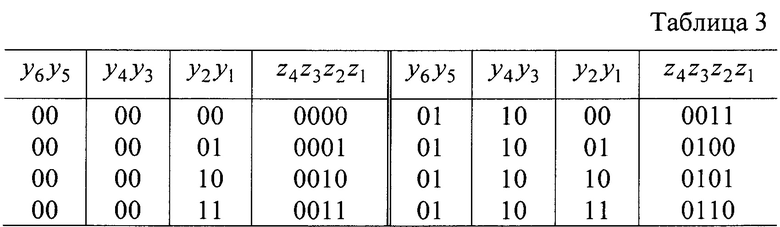

Работа предлагаемого параллельного счетчика единичных сигналов осуществляется следующим образом. На его первый, …, восьмой входы подаются соответственно подлежащие обработке сигналы x1, …, x8 ∈ {0,1}. В представленных ниже табл. 1 и табл. 2 приведены значения внутренних сигналов y2×r-1, y2×r  и y5, y6 предлагаемого счетчика, полученные с учетом работы элементов 1r+3, 3r и 11, 21 для всех возможных наборов значений соответствующих входных сигналов. В табл. 3 указаны значения его выходных сигналов z1, z2, z3, z4, полученные с учетом работы соответствующих элементов для всех возможных наборов значений сигналов y1, …, y6.

и y5, y6 предлагаемого счетчика, полученные с учетом работы элементов 1r+3, 3r и 11, 21 для всех возможных наборов значений соответствующих входных сигналов. В табл. 3 указаны значения его выходных сигналов z1, z2, z3, z4, полученные с учетом работы соответствующих элементов для всех возможных наборов значений сигналов y1, …, y6.

Согласно табл. 1, табл. 2 и табл. 3 имеем z1=β0, z2=β1, z3=β2, z4=β3, где β3β2β1β0 есть двоичный код числа единичных сигналов в кортеже (xl, …, x8).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единичных сигналов обладает функциональными возможностями прототипа, при этом его схема проще чем у прототипа, поскольку ее цена по Квайну равна 36 и схемная глубина предлагаемого счетчика равна 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЦ | 2020 |

|

RU2760252C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2013 |

|

RU2518641C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2019 |

|

RU2747107C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776922C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2700554C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2787339C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2801792C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в упрощении схемы параллельного счетчика единичных сигналов при сохранении функциональных возможностей. Параллельный счетчик единичных сигналов содержит семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (11, …, 17), три элемента И (21, 22, 23) и четыре мажоритарных элемента (31, …, 34). 1 ил.

Параллельный счетчик единичных сигналов, содержащий семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и три элемента И, причем первый, второй входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И, отличающийся тем, что в него дополнительно введены четыре мажоритарных элемента, i-й вход j-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И, отличающийся тем, что в него дополнительно введены четыре мажоритарных элемента, i-й вход j-го  , первый, второй входы второго и первый, второй входы третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-м входом (j-3)-го мажоритарного элемента, выходом третьего мажоритарного элемента, выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И, выходом четвертого мажоритарного элемента, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами четвертого, пятого, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, второго мажоритарных элементов, выходом первого элемента И, а первый, второй входы первого и i-й вход k-го

, первый, второй входы второго и первый, второй входы третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-м входом (j-3)-го мажоритарного элемента, выходом третьего мажоритарного элемента, выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И, выходом четвертого мажоритарного элемента, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами четвертого, пятого, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами первого, второго мажоритарных элементов, выходом первого элемента И, а первый, второй входы первого и i-й вход k-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно седьмым, восьмым и (3×k+i-12)-м входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами шестого, второго, третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом третьего элемента И.

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно седьмым, восьмым и (3×k+i-12)-м входами параллельного счетчика единичных сигналов, первый, второй, третий и четвертый выходы которого соединены соответственно с выходами шестого, второго, третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом третьего элемента И.

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2013 |

|

RU2518641C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2256211C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| US 5339447 A, 16.08.1994. | |||

Авторы

Даты

2020-01-14—Публикация

2019-03-11—Подача