Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единиц (см., например, патент РФ 2256211, кл. G06F 7/38, 2005 г.), которые содержат элементы И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и определяют количество единиц в восьмиразрядном двоичном числе, задаваемом восемью входными двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единиц, относятся ограниченные функциональные возможности и схемная сложность, обусловленные соответственно тем, что не допускается обработка девятиразрядного двоичного числа, задаваемого девятью входными двоичными сигналами, и цена по Квайну схемы, в частности, упомянутого аналога равна 88.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип параллельный счетчик единиц (патент РФ 2260204, кл. G06F 5/00, 2005 г.), который содержит элементы И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и определяет количество единиц в восьмиразрядном двоичном числе, задаваемом восемью входными двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности и схемная сложность, обусловленные соответственно тем, что не допускается обработка девятиразрядного двоичного числа, задаваемого девятью входными двоичными сигналами, и цена по Квайну схемы прототипа равна 60.

Техническим результатом изобретения является упрощение схемы и расширение функциональных возможностей параллельного счетчика единиц за счет соответственно уменьшения ее цены по Квайну и обеспечения определения количества единиц в девятиразрядном двоичном числе, задаваемом девятью входными двоичными сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единиц, содержащем семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, первый, второй входы i-го  и выход j-го элементов

и выход j-го элементов  ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый вход четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с пятым входом параллельного счетчика единиц, особенность заключается в том, что в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го

ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый вход четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с пятым входом параллельного счетчика единиц, особенность заключается в том, что в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го  мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-ым входом (k+2)-го, выходом седьмого и первым входом второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с (6-j)-ым входом седьмого, i-ым входом i-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и первым, (i+1)-ым выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-ым входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И.

мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-ым входом (k+2)-го, выходом седьмого и первым входом второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с (6-j)-ым входом седьмого, i-ым входом i-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и первым, (i+1)-ым выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-ым входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго элемента И.

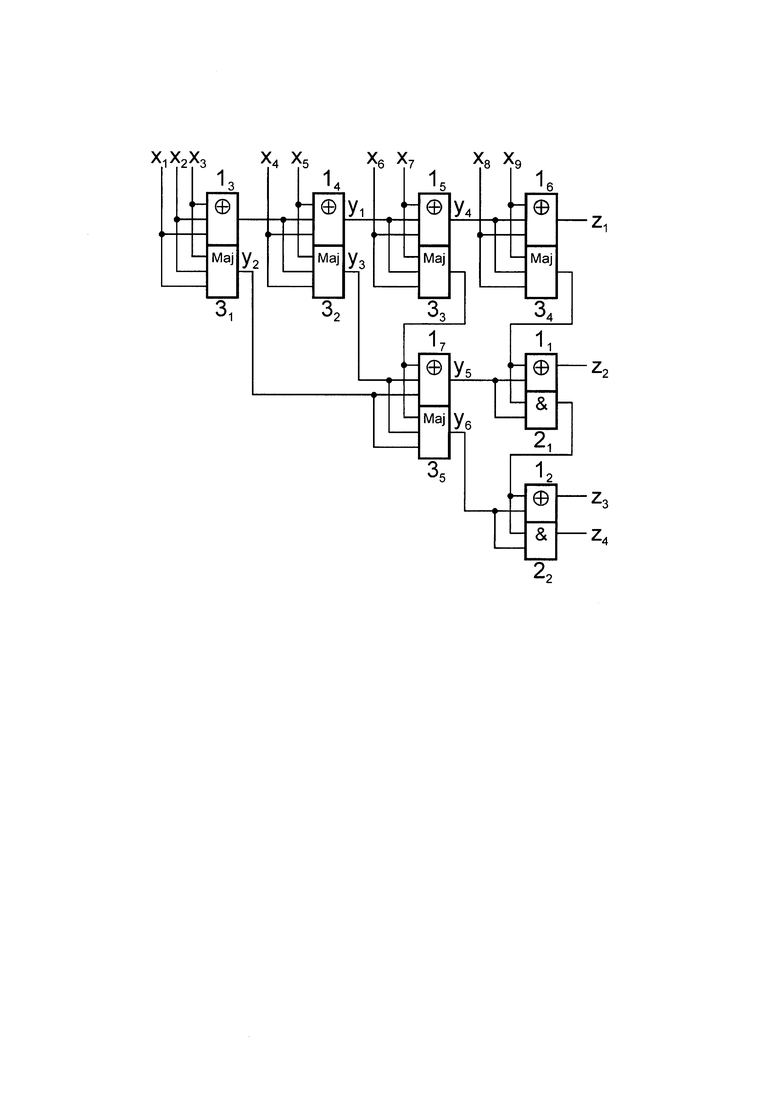

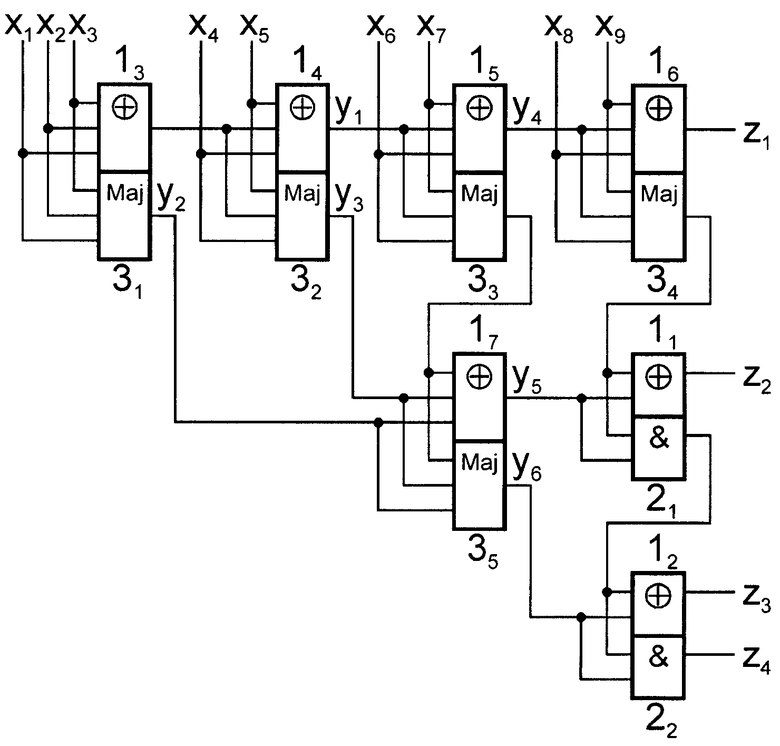

На чертеже представлена схема предлагаемого параллельного счетчика единиц.

Параллельный счетчик единиц содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11,…,17, элементы И 21, 22 и мажоритарные элементы 31,…,35, причем первый, второй входы элемента 1i  и выход элемента 1j

и выход элемента 1j  соединены соответственно с первым, вторым входами элемента 2i и вторым входом элемента 1j+1, (j-2)-й вход элемента 3k

соединены соответственно с первым, вторым входами элемента 2i и вторым входом элемента 1j+1, (j-2)-й вход элемента 3k  второй вход и выход элемента 21 соединены соответственно с (j-2)-ым входом элемента 1k+2, выходом элемента 17 и первым входом элемента 12, а выходы элементов 3j-2, 3i+3 и 16, 1i соединены соответственно с (6-j)-ым входом элемента 17, i-ым входом элемента 1i и первым, (i+1)-ым выходами параллельного счетчика единиц, (j-2)-й, (2×j-2)-й, (2×j-1)-й входы и четвертый выход которого соединены соответственно с (6-j)-ым входом элемента 13, третьим, первым входами элемента 1j+1 и выходом элемента 22.

второй вход и выход элемента 21 соединены соответственно с (j-2)-ым входом элемента 1k+2, выходом элемента 17 и первым входом элемента 12, а выходы элементов 3j-2, 3i+3 и 16, 1i соединены соответственно с (6-j)-ым входом элемента 17, i-ым входом элемента 1i и первым, (i+1)-ым выходами параллельного счетчика единиц, (j-2)-й, (2×j-2)-й, (2×j-1)-й входы и четвертый выход которого соединены соответственно с (6-j)-ым входом элемента 13, третьим, первым входами элемента 1j+1 и выходом элемента 22.

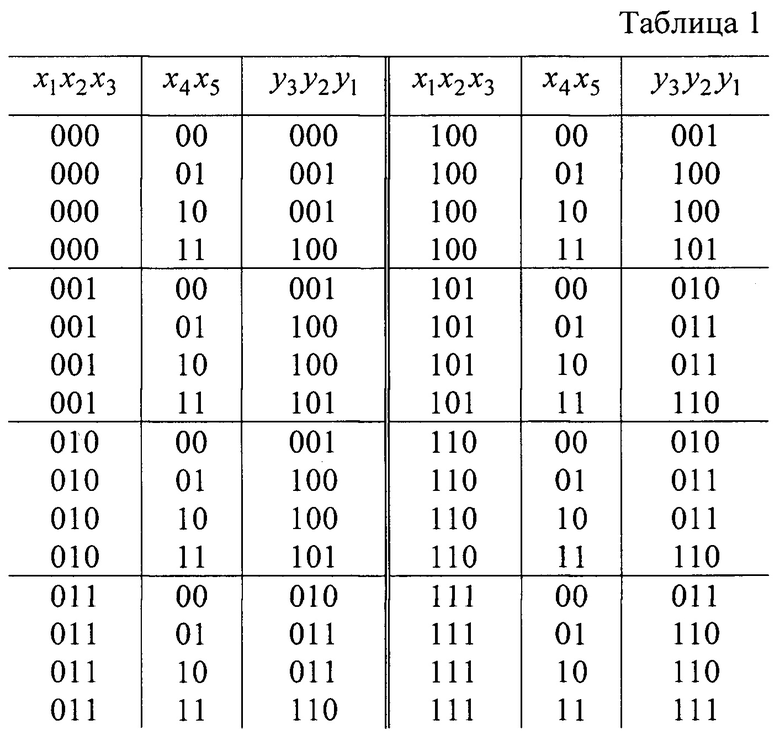

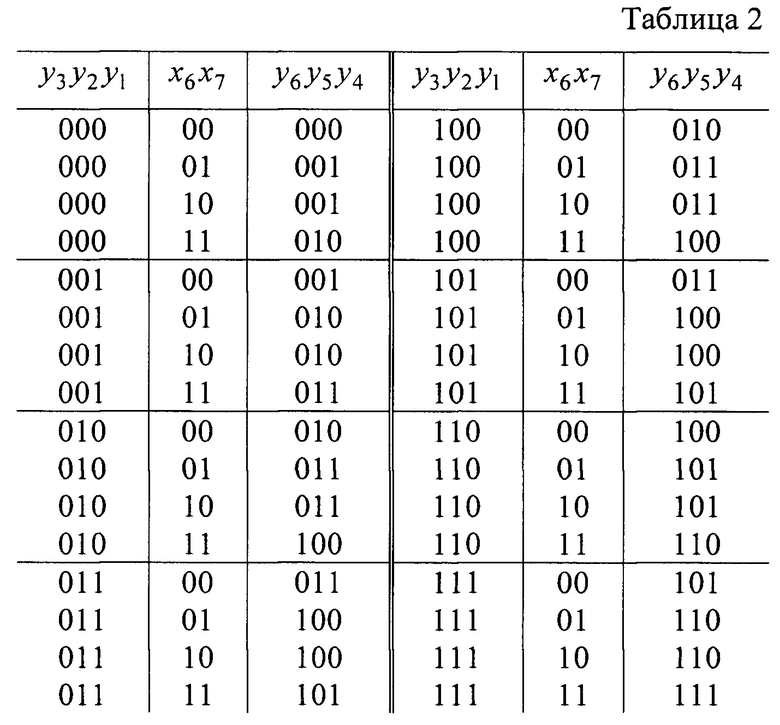

Работа предлагаемого параллельного счетчика единиц осуществляется следующим образом. На его первый,…,девятый входы подаются соответственно двоичные сигналы x1,…,х9∈{0,1}, которые задают подлежащее обработке девятиразрядное двоичное число. В представленных ниже табл. 1 (табл. 2) и табл. 3 приведены соответственно значения внутренних сигналов у1,у2,у3 (у4,у5,уб) предлагаемого параллельного счетчика единиц, полученные для всех возможных наборов значений сигналов x1,…,x5 (у1,у2,у3,х6,х7) и значения его выходных сигналов z1,…,z4, полученные для всех возможных наборов значений сигналов у4,у5,у6,х8,х9.

Согласно табл. 1, табл. 2, табл. 3 имеем z1=β0, z2=β1, z3=β2, z4=β3, где β3β2β1β0 есть двоичный код количества единиц в девятиразрядном двоичном числе, задаваемом двоичными сигналами х1,…,х9.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единиц обладает более широкими по сравнению с прототипом функциональными возможностями, так как определяет количество единиц в девятиразрядном двоичном числе, задаваемом девятью входными двоичными сигналами. При этом схема предлагаемого параллельного счетчика единиц проще, чем у прототипа, поскольку ее цена по Квайну равна 38.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2019 |

|

RU2710872C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2019 |

|

RU2747107C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2019 |

|

RU2710877C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776922C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 2018 |

|

RU2702969C1 |

| ДВОИЧНЫЙ СУММАТОР | 2020 |

|

RU2758184C1 |

| ПОРОГОВЫЙ МОДУЛЬ | 2023 |

|

RU2812688C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2022 |

|

RU2787338C1 |

Изобретение относится к параллельному счетчику. Технический результат заключается в упрощении схемы параллельного счетчика единиц. Счетчик содержит семь элементов исключающее ИЛИ и два элемента И, причем первый, второй входы i-го  и выход j-го

и выход j-го  элементов исключающее ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента исключающее ИЛИ, а первый вход четвертого элемента исключающее ИЛИ соединен с пятым входом параллельного счетчика единиц, при этом в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го

элементов исключающее ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента исключающее ИЛИ, а первый вход четвертого элемента исключающее ИЛИ соединен с пятым входом параллельного счетчика единиц, при этом в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го  мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-м входом (k+2)-го, выходом седьмого и первым входом второго элементов исключающее ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов исключающее ИЛИ соединены соответственно с (6-j)-м входом седьмого, i-м входом i-го элементов исключающее ИЛИ и первым, (i+1)-м выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-м входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов исключающее ИЛИ и выходом второго элемента И. 1 ил., 3 табл.

мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-м входом (k+2)-го, выходом седьмого и первым входом второго элементов исключающее ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов исключающее ИЛИ соединены соответственно с (6-j)-м входом седьмого, i-м входом i-го элементов исключающее ИЛИ и первым, (i+1)-м выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-м входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов исключающее ИЛИ и выходом второго элемента И. 1 ил., 3 табл.

Параллельный счетчик единиц, содержащий семь элементов исключающее ИЛИ и два элемента И, причем первый, второй входы i-го  и выход j-го

и выход j-го  элементов исключающее ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента исключающее ИЛИ, а первый вход четвертого элемента исключающее ИЛИ соединен с пятым входом параллельного счетчика единиц, отличающийся тем, что в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го

элементов исключающее ИЛИ соединены соответственно с первым, вторым входами i-го элемента И и вторым входом (j+1)-го элемента исключающее ИЛИ, а первый вход четвертого элемента исключающее ИЛИ соединен с пятым входом параллельного счетчика единиц, отличающийся тем, что в него дополнительно введены пять мажоритарных элементов, (j-2)-й вход k-го  мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-м входом (k+2)-го, выходом седьмого и первым входом второго элементов исключающее ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов исключающее ИЛИ соединены соответственно с (6-j)-м входом седьмого, i-м входом i-го элементов исключающее ИЛИ и первым, (i+1)-м выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-м входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов исключающее ИЛИ и выходом второго элемента И.

мажоритарного элемента, второй вход и выход первого элемента И соединены соответственно с (j-2)-м входом (k+2)-го, выходом седьмого и первым входом второго элементов исключающее ИЛИ, а выход (j-2)-го, выход (i+3)-го мажоритарных элементов и выходы шестого, i-го элементов исключающее ИЛИ соединены соответственно с (6-j)-м входом седьмого, i-м входом i-го элементов исключающее ИЛИ и первым, (i+1)-м выходами параллельного счетчика единиц, (j-2)-й, четвертый, шестой, седьмой, восьмой, девятый входы и четвертый выход которого соединены соответственно с (6-j)-м входом третьего, третьим входом четвертого, третьим, первым входами пятого, третьим, первым входами шестого элементов исключающее ИЛИ и выходом второго элемента И.

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2256211C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2019 |

|

RU2710872C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| DE 3716551 A1, 23.02.1989. | |||

Авторы

Даты

2021-11-23—Публикация

2020-10-28—Подача