Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы классических дифференциальных усилителей (ДУ) на комплементарных транзисторах [2-28], в т.ч. на комплементарных КМОП полевых транзисторах [3-28] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [2], которые стали основой многих серийных аналоговых микросхем. В литературе по аналоговой микроэлектронике этот класс ДУ имеет специальное обозначение – dual-input-stage [29].

Для работы при низких температурах и жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов с управляющим p-n переходом [30-32]. ДУ данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [33-35].

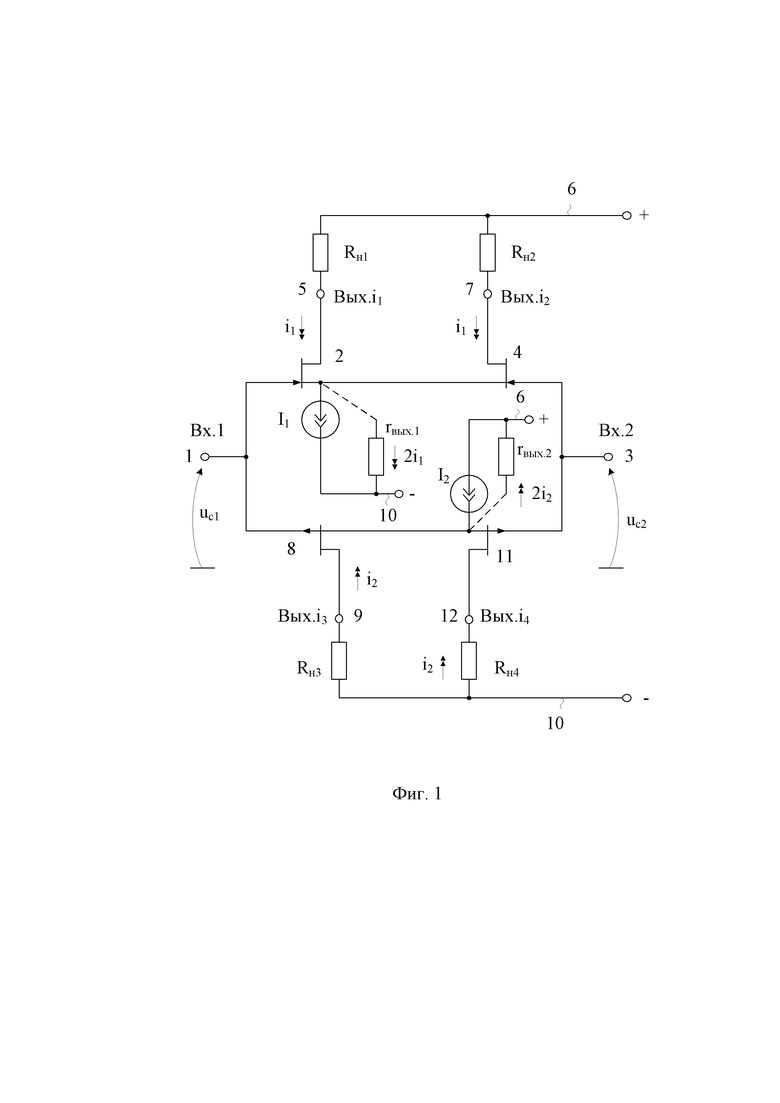

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель, описанный в патенте US 5.291.149, fig.4, 1994г., который содержит первый 1 вход устройства, соединенный с затвором первого 2 входного полевого транзистора, второй 3 вход устройства, соединенный с затвором второго 4 входного полевого транзистора, первый 5 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком первого 2 входного полевого транзистора, второй 7 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком второго 4 входного полевого транзистора, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, третий 9 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком третьего 8 входного полевого транзистора, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 3 входом устройства, четвертый 12 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком четвертого 11 входного полевого транзистора, причем исток первого 2 входного полевого транзистора соединен с истоком второго 4 входного полевого транзистора, а исток третьего 8 входного полевого транзистора подключен к истоку четвертого 11 входного полевого транзистора.

Первый существенный недостаток известного ДУ фиг. 1 состоит в том, что статический режим его входных транзисторов определяется двумя источниками опорного тока I1 (I2), которые, как правило, неидентичны из-за разных напряжений отсечки полевых транзисторов с p- и n-каналами в их структуре. Это становится источником дополнительных погрешностей при усилении малых сигналов. Во-вторых, выходные сопротивления (rвых.1, rвых.2) источников опорного тока I1, I2 в схеме фиг. 1 оказывают существенное влияние на коэффициент ослабления входных синфазных сигналов (Кос.сф) [36, 37]. Так, при изменении входного синфазного сигнала uc1=uc2=uc в схеме фиг. 1 формируются нежелательные переменные токи

i1 ≈ uc/2rвых.1,

i2 ≈ uc/2rвых.2.

Это приводит к нежелательной передаче uc в выходные цепи ДУ.

В-третьих, подавление помех по шинам питания 6 и 10 в схеме фиг. 1 оказывается небольшим, что связано с зависимостью данного параметра от численных значений rвых.1, rвых.2.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДУ фиг. 1 обеспечивается более высокая стабильность статического режима ДУ при отрицательных температурах (до -197̊С) и изменении напряжений питания (в сравнении с ДУ фиг. 1 на основе классических источников опорного тока I1, I2). Дополнительная задача – повышение коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания.

Поставленные задачи достигаются тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 вход устройства, соединенный с затвором первого 2 входного полевого транзистора, второй 3 вход устройства, соединенный с затвором второго 4 входного полевого транзистора, первый 5 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком первого 2 входного полевого транзистора, второй 7 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком второго 4 входного полевого транзистора, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, третий 9 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком третьего 8 входного полевого транзистора, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 3 входом устройства, четвертый 12 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком четвертого 11 входного полевого транзистора, причем исток первого 2 входного полевого транзистора соединен с истоком второго 4 входного полевого транзистора, а исток третьего 8 входного полевого транзистора подключен к истоку четвертого 11 входного полевого транзистора, предусмотрены новые элементы и связи – в качестве первого 2, второго 4, третьего 8 и четвертого 11 входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, кроме этого, в схему введены первый 13 и второй 14 дополнительные полевые транзисторы с управляющим p-n переходом, а также первый 15, второй 16 и третий 17 дополнительные резисторы, причем исток первого 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 2 и второго 4 входных полевых транзисторов с управляющим p-n переходом через первый 15 дополнительный резистор, его затвор подключен к стоку второго 14 дополнительного полевого транзистора с управляющим p-n переходом, его сток соединен с затвором второго 14 дополнительного полевого транзистора с управляющим p-n переходом, исток второго 14 дополнительного полевого транзистора с управляющим p-n переходом связан с объединёнными истоками третьего 8 и четвертого 11 входных полевых транзисторов с управляющим p-n переходом через второй 16 дополнительный резистор, а между стоками первого 13 и второго 14 дополнительных полевых транзисторов с управляющим p-n переходом включен третий 17 дополнительный резистор.

На чертеже фиг. 1 представлена схема ДУ-прототипа, а на чертеже фиг. 2 – схема заявляемого дифференциального усилителя на комплементарных полевых транзисторах (CJFET) в соответствии с п.1 и п.2 формулы изобретения.

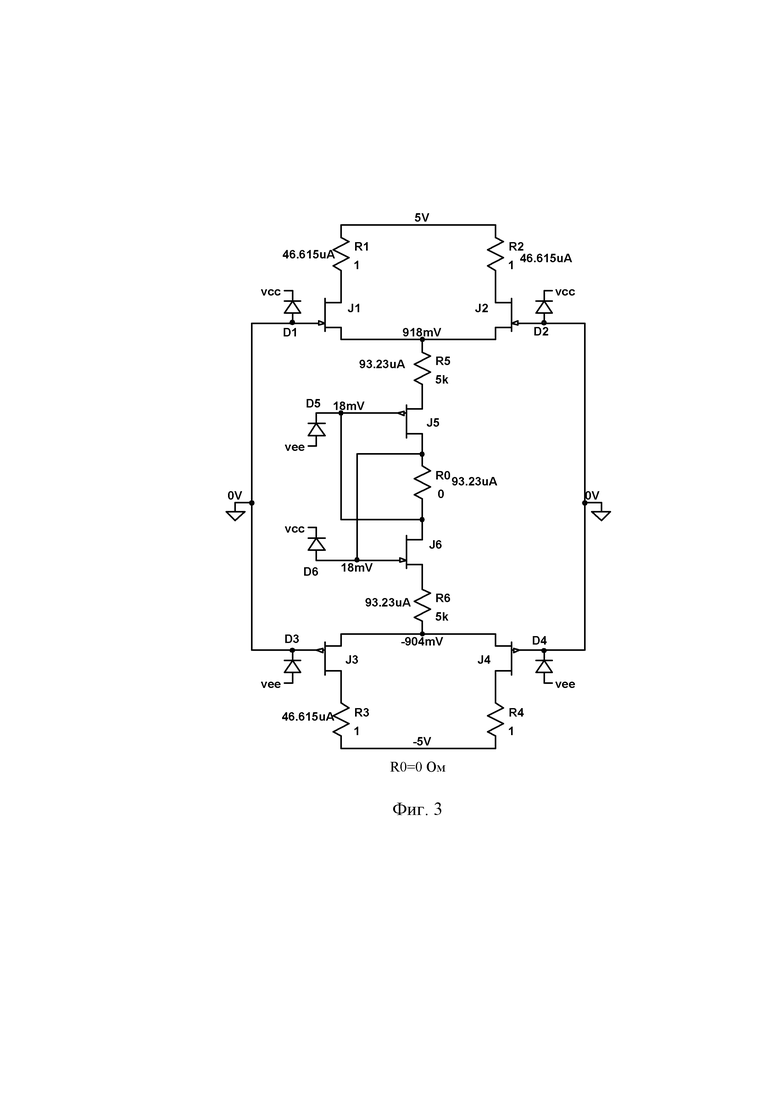

На чертеже фиг. 3 показан статический режим ДУ фиг. 2 в среде LTspice на моделях CJFet полевых транзисторов АО «Интеграл» (г. Минск) при сопротивлениях резисторов R17=R0=0 Ом, R15=R5=5 кОм, R16=R6=5 кОм.

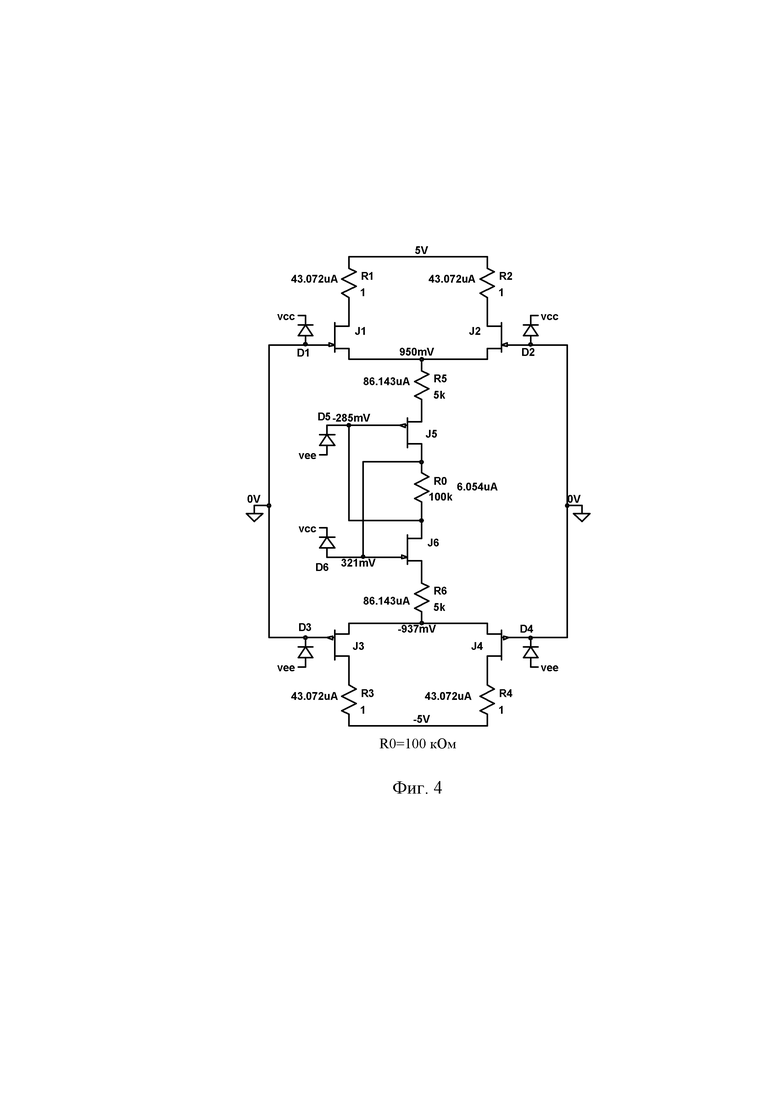

На чертеже фиг. 4 показан статический режим ДУ фиг. 2 в среде LTspice на моделях CJFet полевых транзисторов при сопротивлениях резисторов R17=R0=100 кОм, R15=R5=5 кОм, R16=R6=5 кОм.

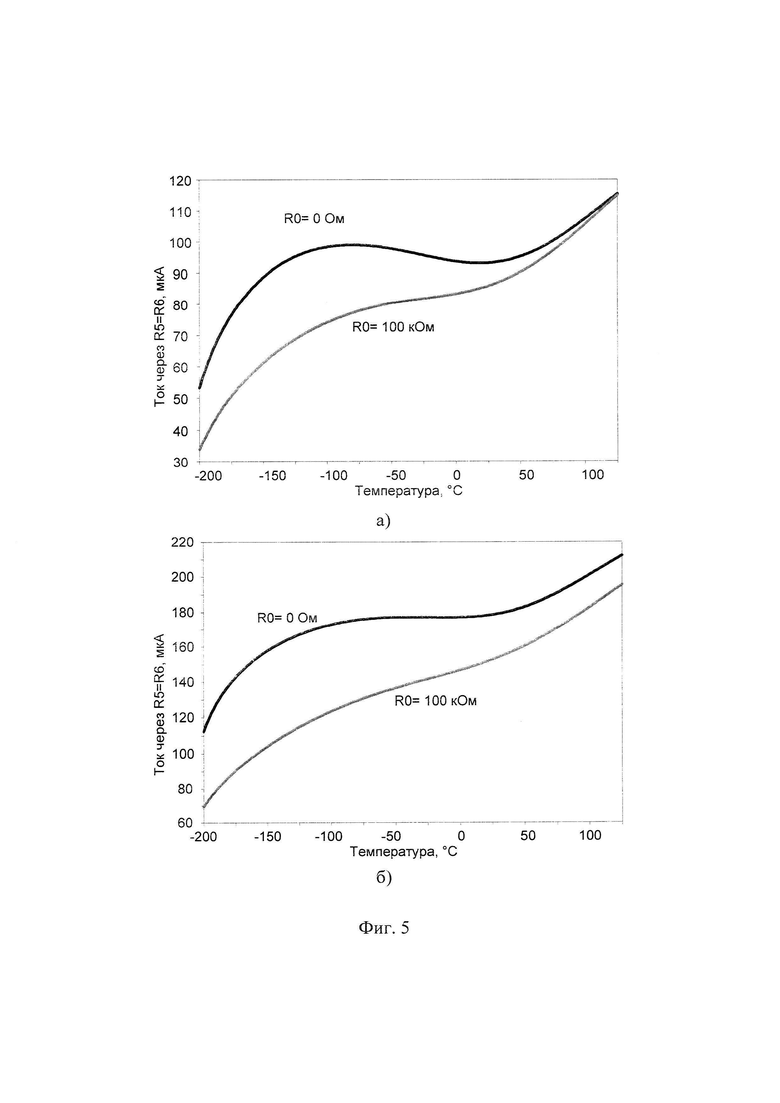

На чертеже фиг. 5 приведена зависимость тока общей истоковой цепи ДУ фиг. 3 - фиг. 4 (тока в резисторах R15=R5=5 кОм, R16=R6=5 кОм) от температуры при разной ширине (w) канала применяемых полевых транзисторов.

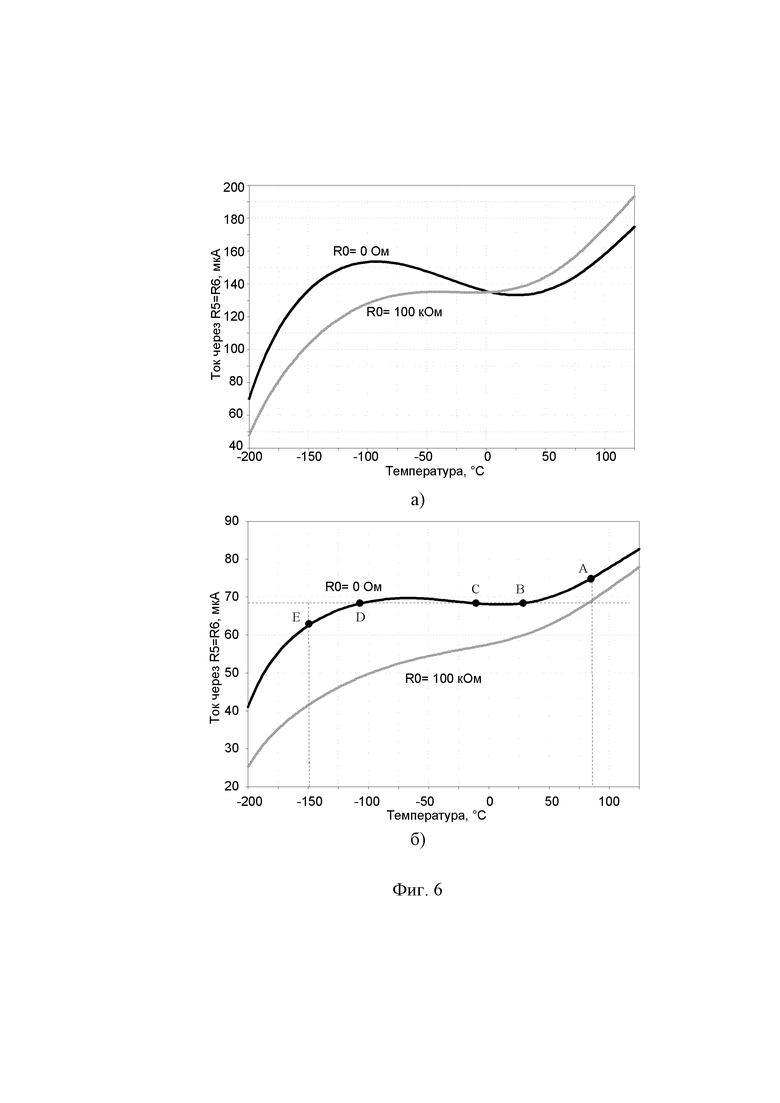

График фиг. 6 характеризует зависимость тока общей истоковой цепи ДУ фиг. 3 – фиг. 4 (тока в резисторах R15=R5, R16=R6) от температуры при ширине канала w=25u и разных значениях сопротивлений резисторов R15=R5 и R16=R6.

Дифференциальный усилитель на комплементарных полевых транзисторах с повышенной стабильностью статического режима фиг. 2 содержит первый 1 вход устройства, соединенный с затвором первого 2 входного полевого транзистора, второй 3 вход устройства, соединенный с затвором второго 4 входного полевого транзистора, первый 5 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком первого 2 входного полевого транзистора, второй 7 токовый выход, согласованный с первой 6 шиной источника питания и соединенный со стоком второго 4 входного полевого транзистора, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, третий 9 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком третьего 8 входного полевого транзистора, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 3 входом устройства, четвертый 12 токовый выход, согласованный со второй 10 шиной источника питания и соединенный со стоком четвертого 11 входного полевого транзистора, причем исток первого 2 входного полевого транзистора соединен с истоком второго 4 входного полевого транзистора, а исток третьего 8 входного полевого транзистора подключен к истоку четвертого 11 входного полевого транзистора. В качестве первого 2, второго 4, третьего 8 и четвертого 11 входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, кроме этого, в схему введены первый 13 и второй 14 дополнительные полевые транзисторы с управляющим p-n переходом, а также первый 15, второй 16 и третий 17 дополнительные резисторы, причем исток первого 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 2 и второго 4 входных полевых транзисторов с управляющим p-n переходом через первый 15 дополнительный резистор, его затвор подключен к стоку второго 14 дополнительного полевого транзистора с управляющим p-n переходом, его сток соединен с затвором второго 14 дополнительного полевого транзистора с управляющим p-n переходом, исток второго 14 дополнительного полевого транзистора с управляющим p-n переходом связан с объединёнными истоками третьего 8 и четвертого 11 входных полевых транзисторов с управляющим p-n переходом через второй 16 дополнительный резистор, а между стоками первого 13 и второго 14 дополнительных полевых транзисторов с управляющим p-n переходом включен третий 17 дополнительный резистор.

Кроме этого, на чертеже фиг. 2 в качестве элементов нагрузки ДУ используются вспомогательные резисторы 18, 19, 20, 21. В практических схемах в качестве этих элементов могут использоваться токовые зеркала и другие типы активных нагрузок [37].

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве первого 2, второго 4 входных полевых транзисторов и второго 14 дополнительного полевого транзистора с управляющим p-n переходом используются полевые транзисторы с n-каналом, а в качестве третьего 8, четвертого 11 входных полевых транзисторов и первого 13 дополнительного полевого транзистора с управляющим p-n переходом используются полевые транзисторы с p-каналом.

Рассмотрим работу ДУ фиг. 2.

Существенная особенность ДУ фиг. 2 состоит в том, что в нем идентичный статический режим по токам истока первого 2 и второго 4 входных полевых транзисторов, а также третьего 8 и четвертого 11 входных полевых транзисторов устанавливается не отдельными (как в схеме фиг.1) источниками опорного тока I1, I2, а интегрированной в единый функциональный узел цепью стабилизации статического режима ДУ, включающей как единое целое первый 2, второй 4, третий 8, четвертый 11 входные полевые транзисторы, а также первый 13 и второй 14 дополнительные полевые транзисторы с управляющим p-n переходом. Это позволяет обойтись без источников опорного тока I1, I2 и решить задачу установления статического режима ДУ нетрадиционным способом.

Следует заметить, что статический режим ДУ фиг. 2 практически не зависит от величины входного синфазного сигнала uc=uc1=uc2 и изменений напряжений на первой 6 и второй 10 шинах источников питания. Это позволяет исключить из схемы ДУ фиг. 2 традиционные источники опорного тока (I1, I2, фиг. 1), отрицательно влияющие на его многие параметры (особенно при их простейшем построении).

При этом независимо от численных значений напряжения отсечки применяемых полевых транзисторов c p и n-каналами ток общей истоковой цепи первого 2 и второго 4 входных полевых транзисторов (ток через первый 15 дополнительный резистор) всегда равен току общей истоковой цепи третьего 8 и четвертого 11 входных полевых транзисторов (току через второй 16 дополнительный резистор). Это важное свойство заявляемой схемы ДУ, способствующее ее симметрии.

Если на вход 1 подается положительное входное напряжение uвх относительно входа 3, то это вызывает увеличение тока первого 2 и четвертого 11 входных полевых транзисторов и уменьшение тока истока второго 4 и третьего 8 входных полевых транзисторов.

Графики, представленные на чертежах фиг. 5, фиг. 6, снятые при разных температурах и численных значениях сопротивлений R5 и R6 (в схемах фиг.3, фиг. 4), подтверждают сделанные выше качественные выводы относительно стабильности статического режима. Действительно, зависимость токов через R5 и R6 (фиг. 6б) имеет участок АЕ, в пределах которого статические токи IR5=IR6 изменяются незначительно. Это позволяет обеспечить за счет рационального выбора параметров элементов улучшенную стабильность статического режима заявляемого ДУ.

Предлагаемая схема ДУ имеет повышенные значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помехи по шинам питания. Этот эффект обусловлен тем, что для типовых ДУ данные параметры определяются двумя основными факторами [36, 37]:

1. Конечной величиной выходных сопротивлений источников опорного тока I1, I2 в схеме фиг. 1 (rвых.1, rвых.2).

2. Неидентичностью коэффициентов внутренней обратной связи применяемых полевых транзисторов.

Первый фактор в заявляемом ДУ фиг. 2 отсутствует, т.к. источники опорного тока I1, I2 здесь не нужны, а статический режим схемы устанавливается элементами, «изолированными» от шин источников питания. В конечном итоге предлагаемый ДУ (при таких же активных элементах, как и в схеме фиг. 1) имеет улучшенные значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания.

Результаты компьютерного моделирования в среде LTspice схемы ДУ фиг. 2 показывают, что на основе предлагаемого ДУ реализуется широкий спектр температурных зависимостей выходных токов ДУ. В итоге, это позволяет проектировать дифференциальные и мультидифференциальные операционные усилители с заданными параметрами статического режима в диапазоне температур.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известными схемотехническими решениями ДУ класса dual-input-stage [2-28], что позволяет рекомендовать его для практического использования в различных ОУ и при построении других низкотемпературных и радиационно-стойких аналоговых микросхем по техпроцессу CJFet ОАО «Интеграл» (г. Минск), а также комплементарному биполярно-полевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

Библиографический список

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

2. Патент US 5.291.149 fig. 4, 1994 г.

1. Патент US 4.377.789, fig. 1, 1983 г.

2. Патентная заявка US 2006/0125522, 2006 г.

3. Патент US 7.907.011, 2011

4. US 2008/0024217, fig. 1, 2008 г.

5. Патент EP 0318263,1989 г.

6. Патент US 5.907.259, fig. 1, 1999 г.

7. Патент US 7.408.410, 2008 г.

8. Патент US 6.628.168, fig.2, 2003 г.

9. Патентная заявка US 2009/0302895, 2009 г.

10. Патент US 5.714.906, fig. 4, 1998 г.

11. Патент US 2005/0285677, 2005 г.

12. Патент US 5.070.306, fig. 3, 1991 г.

13. Патент US 2010/001797, 2010 г.

14. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

15. Патент US 2008/0252374, 2008 г.

16. Патент US 7.586.373, 2009 г.

17. Патент US 2006/0215787, 2006 г.

18. Патент US 7.453.319, 2008 г.

19. Патент US 2004/0174216, fig. 2, 2004 г.

20. Патент US 7.215.200, fig. 6, 2007 г.

21. Патент US № 6.433.637, fig. 2, 2002 г.

22. Патент US № 6.392.485, 2002 г.

23. Патент US 5.963.085, fig. 3, 1999 г.

24. Патент US 6.788.143, 2004 г.

25. Патент US 4.390.850, 1983 г.

26. Патент US 6.696.894, fig. 1, 2004 г.

29. N. N. Prokopenko, N. V. Butyrlagin, A. V. Bugakova and A. A. Ignashin, "Method for speeding the micropower CMOS operational amplifiers with dual-input-stages," 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, 2017, pp. 78-81.

30. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

31. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

32. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

33. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, no. 2 (7), 2013, pp. 42-46.

34. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. – 2014. – №. 1. – С. 32-37.

35. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

36. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

37. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2021 |

|

RU2766861C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736549C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ КРУТИЗНОЙ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770915C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляемым напряжением ограничения проходной характеристики | 2018 |

|

RU2679970C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом | 2018 |

|

RU2688225C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

Изобретение относится к радиотехнике и связи. Технический результат заключается в создании условий, при которых в заявляемом дифференциальном усилителе (ДУ) обеспечивается более высокая стабильность статического режима при отрицательных температурах, а также повышение коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания. Усилитель содержит полевые транзисторы и резисторы, соединенные таким образом, чтобы статический режим схемы устанавливался элементами, изолированными от шин источников питания, что позволит улучшить значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания. 1 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель на комплементарных полевых транзисторах с повышенной стабильностью статического режима, содержащий первый (1) вход устройства, соединенный с затвором первого (2) входного полевого транзистора, второй (3) вход устройства, соединенный с затвором второго (4) входного полевого транзистора, первый (5) токовый выход, согласованный с первой (6) шиной источника питания и соединенный со стоком первого (2) входного полевого транзистора, второй (7) токовый выход, согласованный с первой (6) шиной источника питания и соединенный со стоком второго (4) входного полевого транзистора, третий (8) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, третий (9) токовый выход, согласованный со второй (10) шиной источника питания и соединенный со стоком третьего (8) входного полевого транзистора, четвертый (11) входной полевой транзистор, затвор которого соединен со вторым (3) входом устройства, четвертый (12) токовый выход, согласованный со второй (10) шиной источника питания и соединенный со стоком четвертого (11) входного полевого транзистора, причем исток первого (2) входного полевого транзистора соединен с истоком второго (4) входного полевого транзистора, а исток третьего (8) входного полевого транзистора подключен к истоку четвертого (11) входного полевого транзистора, отличающийся тем, что в качестве первого (2), второго (4), третьего (8) и четвертого (11) входных полевых транзисторов используются полевые транзисторы с управляющим р-n-переходом, кроме этого в схему введены первый (13) и второй (14) дополнительные полевые транзисторы с управляющим р-n-переходом, а также первый (15), второй (16) и третий (17) дополнительные резисторы, причем исток первого (13) дополнительного полевого транзистора с управляющим р-n-переходом соединен с объединенными истоками первого (2) и второго (4) входных полевых транзисторов с управляющим р-n-переходом через первый (15) дополнительный резистор, его затвор подключен к стоку второго (14) дополнительного полевого транзистора с управляющим р-n-переходом, его сток соединен с затвором второго (14) дополнительного полевого транзистора с управляющим р-n-переходом, исток второго (14) дополнительного полевого транзистора с управляющим р-n-переходом связан с объединенными истоками третьего (8) и четвертого (11) входных полевых транзисторов с управляющим р-n-переходом через второй (16) дополнительный резистор, а между стоками первого (13) и второго (14) дополнительных полевых транзисторов с управляющим р-n-переходом включен третий (17) дополнительный резистор.

2. Усилитель по п. 1, отличающийся тем, что в качестве первого (2), второго (4) входных полевых транзисторов и второго (14) дополнительного полевого транзистора с управляющим р-n-переходом используются полевые транзисторы с n-каналом, а в качестве третьего (8), четвертого (11) входных полевых транзисторов и первого (13) дополнительного полевого транзистора с управляющим р-n-переходом используются полевые транзисторы с р-каналом.

| US 5291149 A, 01.03.1994 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДРАЙВЕР КОММУТАТОРА РАЗРЯДНОГО ТОКА ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2014 |

|

RU2572389C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| US 5444413 A, 22.08.1995. | |||

Авторы

Даты

2020-01-14—Публикация

2019-07-15—Подача