Изобретение относится к области микроэлектроники, а именно к радиационно-стойким статическим оперативным запоминающим устройствам (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах, и может быть использовано при проектировании, по нанометровым технологиям объемного кремния, сверхбольших интегральных схем (СБИС), предназначенных для авионики, аэрокосмических и других применений.

Наиболее близким к заявленному изобретению является запоминающее устройство, описанное в патенте US 8,116,164 B2. Данное запоминающее устройство выбрано в качестве прототипа заявленного изобретения.

Недостатком запоминающего устройства прототипа является отсутствие в накопителях блоков обнаружения и исправления ошибок, что приводит к понижению сбоеустойчивости этих блоков.

Техническим результатом изобретения является создание радиационно-стойкого статического оперативного запоминающего устройства (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах с перестраиваемой организацией с повышенной устойчивостью к одиночным сбоям при воздействии отдельных ядерных частиц (ОЯЧ), при этом отсутствии многократных сбоев в разрядах шины данных, относящихся к одному информационному слову, за счет расположения блоков обнаружения и исправления ошибок вне накопителей, а также за счет разнесения разрядов одного слова на расстояние, достаточное для исключения многократных сбоев в разрядах шины данных, относящихся к одному информационному слову.

Поставленный технический результат достигнут путем создания радиационно-стойкого статического оперативного запоминающего устройства (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах, содержащего блоки адресных формирователей, блоки буферных формирователей данных, схему управления, схему разрешения выходов, отличающегося тем, что также содержит два накопителя, два блока обнаружения и исправления ошибок, блок формирователей адресных и управляющих сигналов, который соединен с накопителями, которые соединены с блоками обнаружения и исправления ошибок, которые соединены с блоками буферных формирователей данных, выходы которых являются выходами устройства, причем выходы блоков адресных формирователей и схемы управления соединены с входами блока формирователей адресных и управляющих сигналов, выход которого соединен со входом схемы разрешения выходов, выходы которой соединены с входами блоков буферных формирователей данных, при этом каждый накопитель выполнен в виде матрицы ячеек памяти и содержит блоки, состоящие из базовых субблоков, которые содержат разрядные секции основных разрядов и разрядные секции контрольных разрядов, которые относятся к разным словам и конструктивно расположены таким образом, что разряды одного слова разнесены на расстояние, достаточное для исключения многократных сбоев в разрядах шины данных, относящихся к одному информационному слову.

В предпочтительном варианте осуществления устройство содержит четыре блока адресных формирователей, при этом каждый адресный формирователь содержит детектор изменения адреса.

В предпочтительном варианте осуществления устройства первый накопитель соответствует младшему байту слова, а второй накопитель соответствует старшему байту слова, при этом каждый накопитель выполнен в виде матрицы ячеек памяти и содержит 8 блоков, состоящих из 16 базовых субблоков, которые содержат 12 разрядных секций, из которых 8 секций основных разрядов и 4 секции контрольных разрядов.

В предпочтительном варианте осуществления устройство содержит разрядные секции основных разрядов и разрядные секции контрольных разрядов, которые относятся к разным словам, при этом между смежными секциями расположена сплошная p+ область привязки подложки к земле шириной 2 мкм, а минимальное расстояние между одноадресными ячейками равно 64 мкм.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

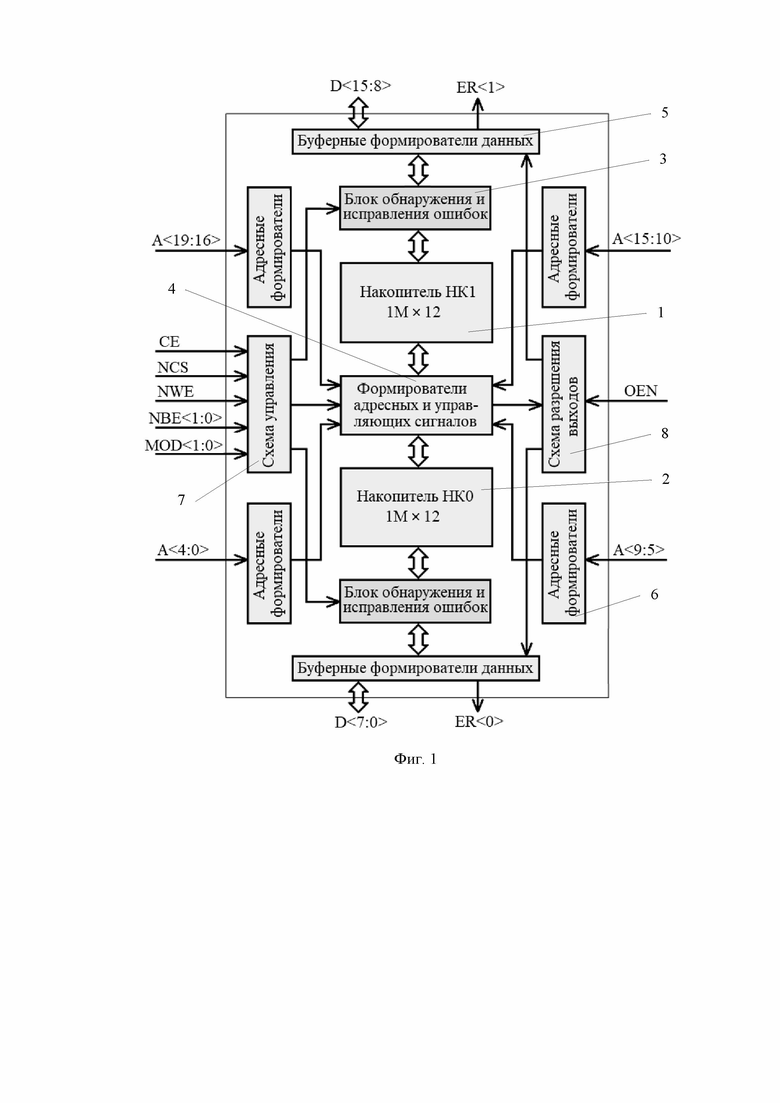

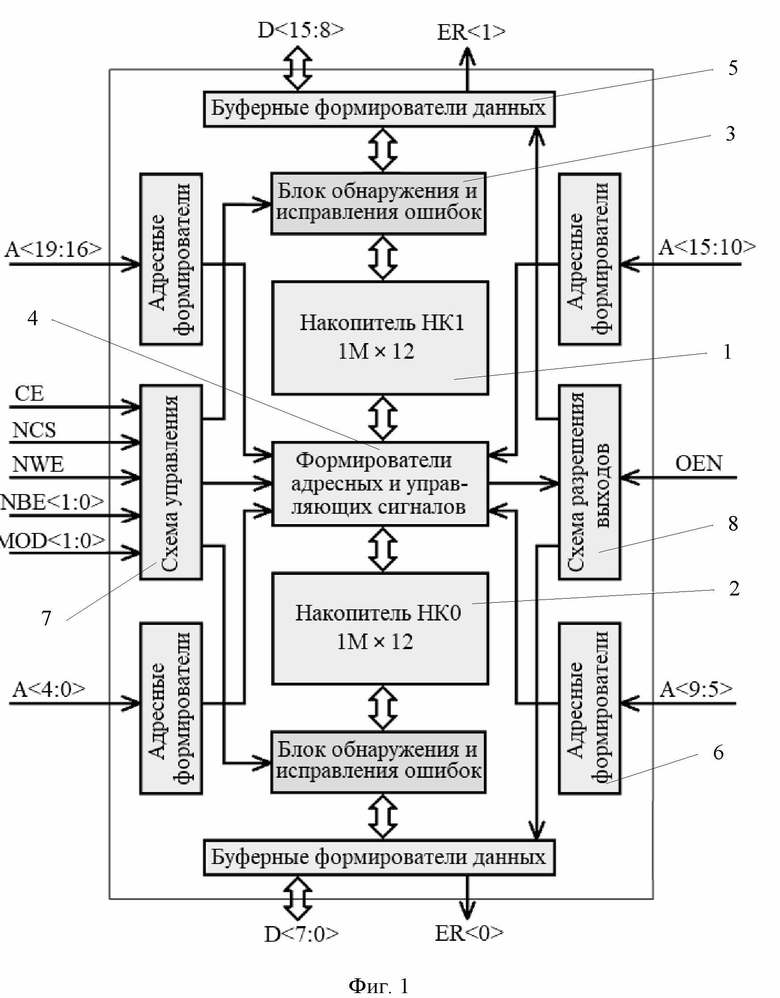

Фиг.1. Схема радиационно-стойкого статического оперативного запоминающего устройства (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах емкостью 16 Мбит с перестраиваемой организацией, выполненная согласно изобретению.

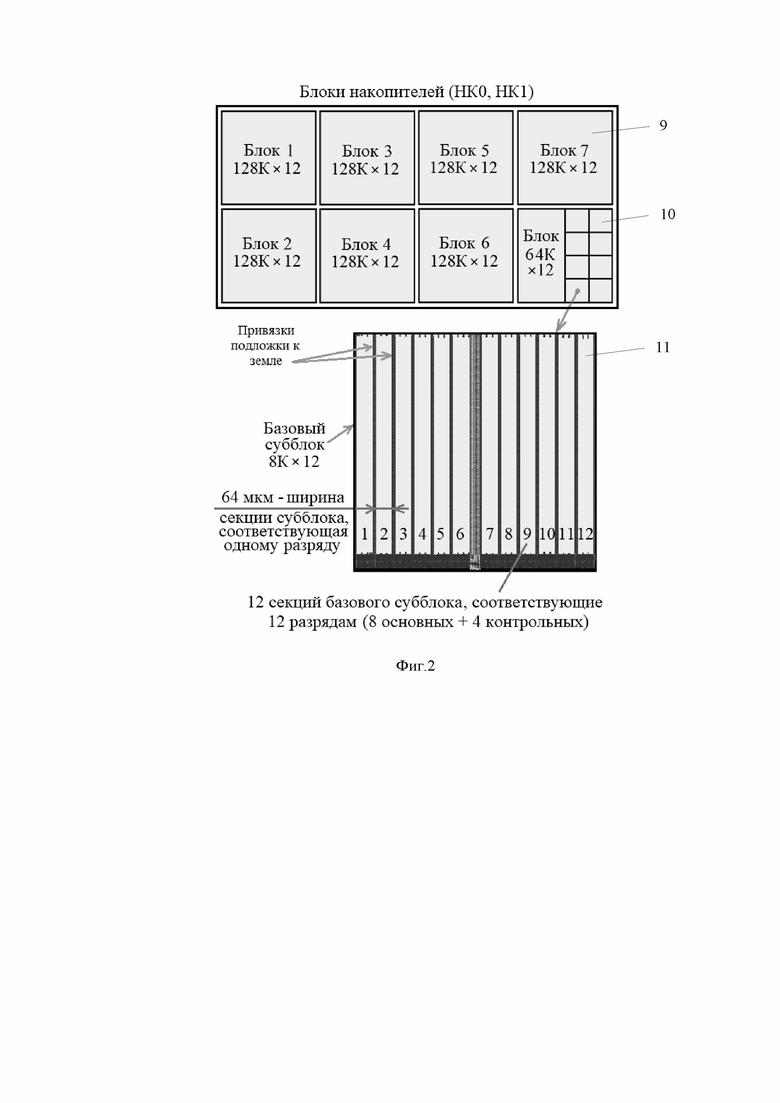

Фиг. 2. Схема накопителей радиационно-стойкого статического оперативного запоминающего устройства (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах, содержащая блоки, субблоки и секции ячеек памяти, выполненная согласно изобретению.

Элементы:

1 - первый накопитель;

2 - второй накопитель;

3 - блоки обнаружения и исправления ошибок;

4 - блок формирователей адресных и управляющих сигналов;

5 - блоки буферных формирователей данных;

6 - блоки адресных формирователей;

7 - схема управления;

8 - схема разрешения выходов;

9 - блоки накопителей;

1 - субблоки накопителей;

11 - секции накопителей.

Рассмотрим более подобно вариант выполнения заявленного изобретения, представленный на Фиг. 1 и Фиг. 2. Радиационно-стойкое статическое оперативное запоминающее устройство (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах содержит два накопителя 1, 2, два блока 3 обнаружения и исправления ошибок, блок 4 формирователей адресных и управляющих сигналов, блоки 5 буферных формирователей данных, блоки 6 адресных формирователей, схему 7 управления, схему 8 разрешения выходов, блоки 9 накопителя, субблоки 10 накопителя, секции 11 накопителя. Блок 4 формирователей адресных и управляющих сигналов соединен с накопителями 1, 2, которые соединены с блоками 3 обнаружения и исправления ошибок, которые соединены с блоками 5 буферных формирователей данных, выходы которых являются выходами заявленного устройства. Выходы блоков 6 адресных формирователей и схемы 7 управления соединены с входами блока 4 формирователей адресных и управляющих сигналов, выход которого соединен со входом схемы 8 разрешения выходов, выходы которой соединены с входами блоков 5 буферных формирователей данных. Каждый накопитель 1, 2 выполнен в виде матрицы ячеек памяти и содержит блоки 9, состоящие из базовых субблоков 10, которые содержат разрядные секции 11 основных разрядов и разрядные секции 11 контрольных разрядов, которые относятся к разным словам и конструктивно расположены таким образом, что разряды одного слова разнесены на расстояние, достаточное для исключения многократных сбоев в разрядах шины данных, относящихся к одному информационному слову.

Радиационно-стойкое статическое оперативное запоминающее устройство (Фиг. 1, 2) на комплементарных металл-окисел-полупроводник транзисторах (далее ОЗУ) содержит два независимых накопителя, первый НК0 накопитель 1 и второй НК1 накопитель 2, имеющие емкость 1МЧ12. Первый накопитель НК0 соответствует младшему байту слова, а второй накопитель НК1 – старшему байту слова. Каждый из двух накопителей 1, 2 содержит по 8 блоков 9 с организацией 128КЧ12, построенных на основе базовых субблоков 10 с организацией 8КЧ12, содержащих по 8 секций 11 основных разрядов, и 4 секции 11 контрольных разрядов. Все адресные формирователи блоков 6 содержат детекторы изменения адреса, благодаря чему реализуется режим асинхронного адресного чтения данных в ОЗУ, а также асинхронная запись по смене адреса, позволяющая быстро заполнять накопитель константой, например, логическим нулём для его «очистки».

Между смежными секциями 11 накопителя базового субблока 10 расположена сплошная p+ область привязки подложки к земле шириной 2 мкм, а минимальное расстояние между одноадресными ячейками секций 11 получается достаточно большим - 64 мкм, что обеспечивает отсутствие множественных сбоев в одном слове. Это позволяет в сочетании с дополнительной привязкой подложки к шине нулевого потенциала и n-кармана напряжению питания в каждой ячейке практически полностью подавить множественные сбои в одном байте при воздействии одиночных ядерных частиц (ОЯЧ) и обеспечить нечувствительность ОЗУ к эффекту «защелкивания».

Расположение блоков 3 обнаружения и исправления ошибок вне накопителей 1, 2 позволяет достигнуть более высокой сбоеустойчивости этих блоков по сравнению с их размещением непосредственно в накопителях 1, 2 в базовых субблоках 8KЧ12 с жесткими ограничениями на размеры транзисторов.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2674935C1 |

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2692307C1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении устойчивости к одиночным сбоям. Радиационно-стойкое статическое оперативное запоминающее устройство (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах содержит блоки адресных формирователей, блоки буферных формирователей данных, схему управления, схему разрешения выходов, два накопителя, два блока обнаружения и исправления ошибок, блок формирователей адресных и управляющих сигналов, при этом каждый накопитель выполнен в виде матрицы ячеек памяти и содержит блоки, состоящие из базовых субблоков, которые содержат разрядные секции основных разрядов и разрядные секции контрольных разрядов, которые относятся к разным словам и конструктивно расположены таким образом, что разряды одного слова разнесены на расстояние, достаточное для исключения многократных сбоев в разрядах шины данных, относящихся к одному информационному слову. 3 з.п. ф-лы, 2 ил.

1. Радиационно-стойкое статическое оперативное запоминающее устройство (ОЗУ) на комплементарных металл-окисел-полупроводник транзисторах, содержащее блоки адресных формирователей, блоки буферных формирователей данных, схему управления, схему разрешения выходов, отличающееся тем, что также содержит два накопителя, два блока обнаружения и исправления ошибок, блок формирователей адресных и управляющих сигналов, который соединен с накопителями, которые соединены с блоками обнаружения и исправления ошибок, которые соединены с блоками буферных формирователей данных, выходы которых являются выходами устройства, причем выходы блоков адресных формирователей и схемы управления соединены с входами блока формирователей адресных и управляющих сигналов, выход которого соединен со входом схемы разрешения выходов, выходы которой соединены с входами блоков буферных формирователей данных, при этом каждый накопитель выполнен в виде матрицы ячеек памяти и содержит блоки, состоящие из базовых субблоков, которые содержат разрядные секции основных разрядов и разрядные секции контрольных разрядов, которые относятся к разным словам и конструктивно расположены таким образом, что разряды одного слова разнесены на расстояние, достаточное для исключения многократных сбоев в разрядах шины данных, относящихся к одному информационному слову.

2. Устройство по п. 1, отличающееся тем, что содержит четыре блока адресных формирователей, при этом каждый адресный формирователь содержит детектор изменения адреса.

3. Устройство по п. 1, отличающееся тем, что первый накопитель соответствует младшему байту слова, а второй накопитель соответствует старшему байту слова, при этом каждый накопитель выполнен в виде матрицы ячеек памяти и содержит 8 блоков, состоящих из 16 базовых субблоков, которые содержат 12 разрядных секций, из которых 8 секций основных разрядов и 4 секции контрольных разрядов.

4. Устройство по п. 1, отличающееся тем, что содержит разрядные секции основных разрядов и разрядные секции контрольных разрядов, которые относятся к разным словам, при этом между смежными секциями расположена сплошная p+ область привязки подложки к земле шириной 2 мкм, а минимальное расстояние между одноадресными ячейками равно 64 мкм.

| US 8116164 B2, 14.02.2012 | |||

| EP 1844473 B1, 15.04.2009 | |||

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| CN 105336362 B, 23.01.2018 | |||

| CN 103956183 B, 04.01.2017. | |||

Авторы

Даты

2020-07-02—Публикация

2019-08-19—Подача