54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1976 |

|

SU648979A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1619252A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

1

Ьзобретение относится к области вычислительной техники.

Известны арифметико-логические устройства комбинационного типа, содержащие регистры первого и второго операндов,

блок распространения переносов и первый логический коммутатор, выходы которого соединены соответственно с выходами первого и второго регистров операндов, первы выход подключен к первому входу блока

распространения переносов.

Однако такое устройство не позволяет выполнять операции сдвигов и ряд операций, связанных с обработкой байтов (обмен байтов, расширение знака и т. п.)..

Кроме того, в устройстве для каждого разряда имеются два полусумматора, вногсяшие существенную дополнительную задержку в работу устройства при выполнений логических операций, когда сумматор не вы- полняет своих основных функций, а служит только для передачи информации.

Целью изобретения является увеличение быстродействия устройства при выполнении логических операций и операций сдвигов и

повышение коэффициента использования оборудования.

Поставленная цель достигается тем, что в устройство введен блок элементов импликации, блок ключей и второй логический коммутатор, причем второй выход первого логического коммутатора соединен с первым входом блока элементов импликации, вторым входом блока распространения переносов и через блок ключей с первым входом второго логического коммутатора, второй ВХОД- которого подключен к выходу блока ячементов импликаций, второй вход которого соединен с выходом блока распространения переносов.

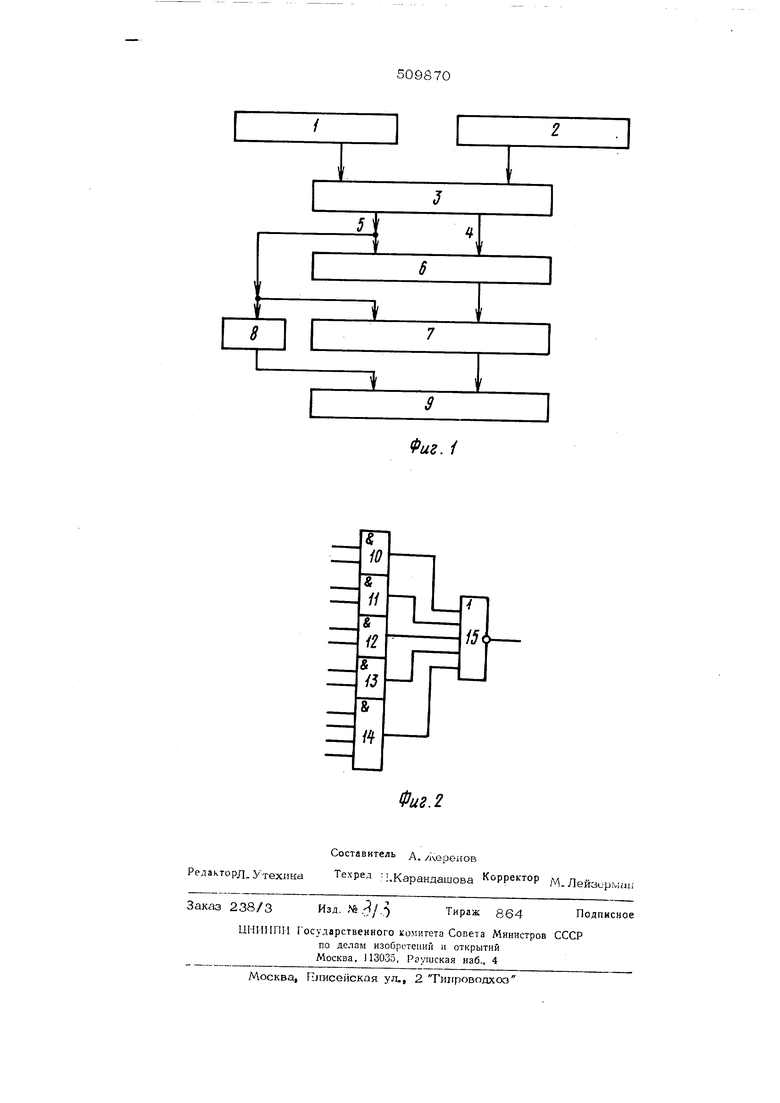

В арифметико-логическом устройстве каждый разряд второго логического коммутатора содержит черыте элел1ента И на два входа, элемент И на четыре входа, выходы которых подключены соответственно ко входам элемента КЛИ-НЕ.

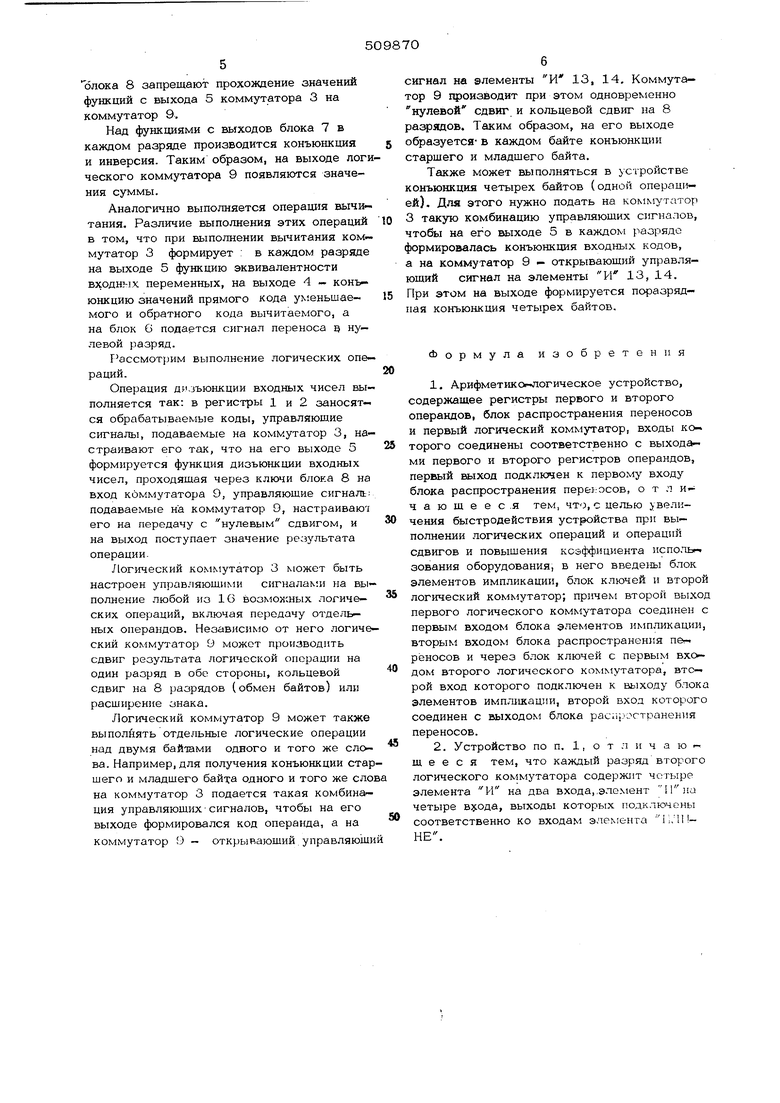

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - вариант выполнения одного разряда логического кбм- мутатора.

Устройство содержит элементы 1, 2 первого и второго операндов, логический коммутатор 3 с первым 4 и вторым 5 выходами, блок 6 распространения переног- сов, блок 7 элементов импликации, блок 8 ключей и логический коммутатор 9.

Один разряд логического коммутатора содержит элементы И 10-14, элемент ИЛИ-.НЕ 15.

Первые входы каждого элемента И соединены с первыми входами соответству«юших элементов И остальных разрядов.

Первые входы коммутатора 9 подключены ко вторым входам элементов И 14 ного разряда, элементов И 10 разрядов на единийу старше данного, элементов И 11 разрядов на единицу младше данног и элементов И 13 разрядов, отличающих ся от данного на 8 единиц. Первый вход седьмого разряда коммутатора 9 подключен кроме того, ко вторым входам элементов Г 12 разрядов с восьмого по пятнадцаты Вторые входы коммутатора 9 подключены к третьим и четвертым входам элементов И 14. Выходы всех элементов И в каждом разряде подключены ко входам эле мента ИЛИ-НЕ 15. Выход элемента 15 является выходом коммутатора 9.

Устройство работает следующим образом В регистры 1 и 2 помещаются операнды Ими могут быть щестнадцатиразр5щные слова, байты как в упакованном (два бай та Б одном слове), так и в распакованном виде (байт помещен в 8 младших разр5щах регистра, а 8 старших разрядов представляг ют собой расширенный знак). Прямой и инверсный коды каждого разряда операндов поступают на вход коммутатора 3- и преобразуются в зависимости от набора управлясющих сигналов так, что в каждом разряде выхода 5 получается одна из 16 возмож- ных логических функций двух переменных, а в каждом разряде выхода 4 конъюнК -ция либо прямых значений операндов, л№ бо прямого значения первого и инверсного значения второго операндов.

На входы блока 6 распространения переносов поступают значения логических функций с выходов 4 и 5 коммутатора 3,

На выходах блока 6 образуются значения переносов между разрядами. Значения переносов поступают на входы блока 7 элементов импликации, на другие входы

которого поступают значения функций каждого разряда выхода 5 коммутатора 3. Блок 7 выполняет для каждого разряда ик пликацию значения, функции с выхода блока 6 по значению функции с выхода 5

коммутатора 3 и импликацию значения функ- ции с выхода 5 по значению функции с выхода блока 6, Одновременно производится клапанирование значений выходных функций блока 7, прохождение которых разрешается при выполнении арифметических операций,. Ключи блока 8 разрешают прохождение значений функций с выхода 5 коммутатора 3 при выполнении логических операций и операций сдвигов и запрещают при выполнении арифметических операций.

В зависимости от набора управляющих сигналов логический коммутатор произво- дит следующие преобразования значений входных функций:

над значениями функций, поступающих с блока 7 f операции конъюнкции с инверси- ей в каждом разряде коммутатора 9;

над значениями функций, поступающих с выхода блока 8;

а)сдвиг влево на один разряд,

б)сдвиг вправо на один разр5Щ,

в) нулевой сдвиг,

г)кольцевой сдвиг на 8 разрядов,

д)расширение знака, т. е. передачу млащего байта с нулевым сдвигом и заполнение старшего байта значением разряда младшего байта.

Выполнение этих функций можно проиллюстрировать на примере варианта построе ния логического коммутатора 9, Для выполнения конъюнкции с инверсией над значениями функций, поступающих с выхода блока 7 необходимо, чтобы ключи блока 8 были закрыты, на элементы И 14 подавался открывающий сигнал, а на элементы И открывающий сигнал не подавался. Значения конъюнкций выходных функций блока 7 поступают на элементы 15 и затем на выход устройства.

Для выполнения операций над логическими функциями, поступающими с выхода блок 8, необходимо, чтобы выходные элементы блока 7 были закрыты, и на элементы И 10™14 подавались управляющие сигнат лы,

Рассмотрим выполнение операции сложения. В регистр 1 и 2 заносятся слагаемые Управляющие сигналы, подаваемые на ло гический коммутатор 3, настраивают его так, что на каждом разряде выхода 6 образуется сумма по модулю 2 входных onepai дов, и на выходе, 4 - их конъюнкции. Блок 6 формирует сигнал переносов, погступающих в блок 7, в. который на вторые входы поступают такде значения функций с выхода 5. На выходе блока 7 для каждого разряда образуются две функции импликации значений входных функций. Ключи блока 8 запрещают прохождение значений функций с выхода 5 коммутатора 3 на коммутатор 9. Над функциями с выходов блока 7 в каждом разряде производится конъюнкция и инверсия. Таким образом, на выходе лог ческого коммутатора 9 появляются значения суммы. Аналогично выполняется операция вычи тания. Различие выполнения этих операций в том, что при выполнении вычитания ком мутатор 3 формирует в каждом разряде на выходе 5 функцию эквивалентности входнмх переменных, на выходе 4 - конт юнкцию значений прямого кода уменьшаемого и обратного кода вычитаемого, а на блок G подается сигнал переноса Q нулевой разряд. FaccMOTjjHM выполнение логических опе раций. Операция дизъюнкции входных чисел въ1 полняется так: в регистры 1 и 2 заносятся обрабатываемые коды, управляющие сигналы, подаваемые на коммутатор 3, на страивают его так, что на его выходе 5 формируется функция дизъюнкции входных чисел, проходящая через ключи блока 8 на вход коммутатора О, управляющие сигнальподаваемые на коммутатор 9, настраивают его на передачу с нулевым сдвигом, и на выход поступает значение результата операции. Логический коммутатор 3 может быть настроен управляющими сигналак;и на вы полнение любой из 1G Бозмохшых логиче- ских операций, включая передачу отдельных операндов. Независимо от него логиче ский коммутатор 9 может производить сдвиг результата логической операции на один разряд в обе стороны, кольцевой Сдвиг на 8 разр$щов (обмен байтов) или расширение знака. Логический коммутатор 9 может также выполнять отдельные логические операции над двумя байтами одного и того же елова. Например, для получения конъюнкции стар шего и младшего байта одного и того же сло на коммутатор 3 подается такая комбинация управляющих-сигналов, чтобы на его выходе формировался код операнда, а на коммутатор 9 открывающий управляющ сигнал на элементы И 13, 14. Коммутатор 9 производит при этом одновременно нулевой сдвиг и кольцевой сдвиг на 8 разрядов. Таким образом, на его выходе образуется- в каждом байте конъюнкции старщего и младшего байта. Также может выполняться в устройстве конъюнкция четырех байтов (одной операцией). Для этого нужно подать на коммутатор 3 такую комбинацию управляющих сигналов, чтобы на его въ1ходе 5 в каждом разряде формировалась конъюнкция входных кодов, а на коммутатор 9 - открывающий управляющий сигнал на элементы И 13, 14. При этом на выходе формируется поразрядная конъюнкция четырех байтов. Формула изобретения 1.Арифметиког логическое устройство, содержащее регистры первого и второго операндов, блок распространения переносов и первый логический коммутатор, входы которого соединены соответственно с выходами первого и второго регистров операндов, первый выход подключен к первому входу блока распространения перек-осов, о т л и- чающеес.я тем, что, с целью увеличения быстродействия устройства при выполнении логических операций и операций сдвигов и повышения коэффициента исполь™ зования оборудования, в него введены блок элементов импликации, блок ключей и второй логический коммутатор; причем второй выход первого логического коммутатора соединен с первым входом блока элементов импликации, вторым входом блока распространения пе-. рёносов и через блок ключей с первым входом второго логического коммутатора, второй вход которого подключен к выходу блока элементов импликации, второй вход которого соединен с выходом блока рас 1р0страненпя переносов. 2.Устройство по п. 1, о т л и ч а ю fщ е е с я тем, что каждый разряд второго логического коммутатора содержит четыре элемента И на два входа,,элемент 11 ни четыре вуода, выходы которых подключены соответственно ко входам элемента ИЛПНЕ.

Фиг. i

Авторы

Даты

1976-04-05—Публикация

1974-05-22—Подача