Изобретение относится к вычислительной технике и может быть использовано при построении центральных процессоров ЦВМ.

Известно устройство для умножения чисел с фиксированной запятой, содержащее счетчик циклов, регистр микрокоманд, регистр множителя, регистр результата, сумматор, регистр множимого, три элемента ИЛИ, оход пуска устройства, группу информационных входов устройства, выход результата, информационный выход устройства.

Недостатком отого устройстпа является невозможность обработки чисел с переменной длиной формата, а также низкий коэффициент загрузки оборудования.

Наиболее близким из известных является устройство для умножения чисел с фиксированной запятой, содержащее операционный блок, регистр адреса, регистр микрокоманд, счетчик циклов, блок синхронизации, семь элементов И, четыре элемента НЕ, элемент ИЛИ-НЕ, пять элементов И-НЕ, два элемента 2И-ИЛИ, триггер коротких тактов, пять элементов ИЛИ, элемент 2И-ИЛИ-НЕ. триггер коррекций результата, триггер округления, триггер выдвигаемых разрядов множителя, триггер анализа значащего бита, триггер знака множимого, триггер блокировки.

Недостатком этого устройства является невозможность обработки чисел с переменной длиной формата, а также низкий коэффициент загрузки оборудования.

Так при умножении операндов, длина которых в два раза меньше основного формата, вторая (младшая) часть операционVI

сл со о

4 N

ного оборудования устройства умножения в операции умножения не участвует, что приводит к низким функциональным возможностям и к снижению коэффициента загрузки оборудования.

Целью изобретения является расширение функциональных возможностей за счет обработки чисел с переменной длиной формата с максимальным коэффициентом загрузки оборудования.

Поставленная цель достигается тем, что в устройство для умножения чисел с фиксированной запятой, содержащее счетчик циклов, регистр микрокоманд, регистр адреса, четыре элемента НЕ, пять элементов И-НЕ, элемент ИЛИ, блок синхронизации, первый и второй элементы 2И-ИЛИ, первый триггер выдвигаемых разрядов множителя, первый триггер анализа значащего бита, триггер знака и операционный блок, содержащий арифметические модули с первого по четвертый и первый блок ускоренного переноса, причем первые входы арифметических модулей с первого по четвертый объединены и соединены с первым входом считывания операционного блока, входы первой, второй и третьей групп арифметических модулей с первого по четвертый соединены соответственно с информационным входом, входом адреса и входом микроопераций операционного блока, вторые входы арифметических моделей с первого по четвертый соединены с первым входом синхронизации операционного блока, информационные выходы арифметических модулей с первого по четвертый соединены с первым информационным выходом операционного блока, выход переполнения которого соединен с выходом переполнения первого арифметического модуля, выход знака которого соединен с выходом знака операционного блока, первый и второй входы сдвига которого соединены соответственно с первым и вторым входами сдвига первого арифметического модуля, третьи входы первого, второго и третьего арифметических модулей соединены соответственно с первым, вторым и третьим выходами первого блока ускоренного переноса, входы с первого по шестой которого соединены соответственно с первым и вторым выходами второго, первым и вторым выходами третьего и первым и вторым выходами четвертого арифметических модулей, первый и второй входы сдвига 1-го арифметического модуля (i 2, 3, 4) соединен соответственно с первым и вторым выходами (И)-го арифметического модуля, седьмой вход первого блока ускоренного переноса соединен с первым входом переноса операционного блока и

третьим входом четвертого арифметического модуля, первый и второй выходы сдвига которого соединены соответственно с первым и вторым выходами сдвига операционного блока, выход устройства соединен с первым информационным выходом операционного блока, входы Пуск и Сброс устройства соединены с входами Пуск и Сброс блока синхронизации, входы мик0 рокоманд и адреса устройства соединены соответственно с информационными входами регистра микрокоманд и регистра адреса, информационный вход устройства соединен с информационным входом опе5 рационного блока, вход адреса которого соединен с выходом регистра адреса, выход знака операционного блока соединен с информационным входом триггера знака, син- хровход которого соединен с выходом

0 первого элемента И-НЕ, первый вход которого соединен с первым выходом регистра микрокоманд, второй выход которого соединен с входом микроопераций операционного блока, первый синхровход счетчика

5 циклов соединен с входами сброса первых триггеров выдвигаемых разрядов множителя и анализа значащего бита и выходом второго элемента И-НЕ, первый вход которого соединен с выходом микроопера0 ции записи выхода микроопераций регистра микрокоманд, синхровход которого соединен с первым выходом блока синхронизации и вторым входом второго элемента И-НЕ, прямой выход первого триггера вы5 двигаемых разрядов множителя соединен с синхровходом первого триггера анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, введены два буферных

0 регистра, третий и чегвертый элементы 2И- ИЛИ, три элемента ЗИ-ИЛИ, триггер переноса, второй триггер выдвигаемых разрядов множителя и второй триггер анализа значащего бита, а операционный блок дополни5 тельно содержит арифметические модули с пятого по восьмой и второй блок ускоренного переноса, причем первые входы арифметических модулей с пятого по восьмой объединены и соединены с вторым входом

0 считывания операционного блока, входы первой, второй и третьей групп арифметических модулей с пятого по восьмой соединены соответственно с информационным входом, входом адреса и входом микроопе5 раций операционного блока, вторые входы арифметических модулей с пятого по восьмой соединены с вторым входом синхронизации операционного блока, информационные выходы арифметических модулей с пятого по восьмой соединены с

вторым информационном т - одом опера- ционмого блока, третий и входы сдвига которого соединены соотгегстпенно с первым и вторым входами СДРПТЯ пятого арифметического модуля . пятого, шестого и сед:.мС|0 призматических модулей соединены сосгьегстг eci O с первым, ВТОРЫМ И ТретЧИП L J/0,.aMi1 ВТОРОГО

блока ускоренного переноса, о-оды с первого по шестой которого соединены соответственно с первым и вторым г-ыхсдами шестого, первым и вторым т-иод-.мм седьмого, ПерВЫМ И ОТОрЫМ DI 1X0,,Г1.И ЕОСЬМОГО

арифметических модулс-и, nei; tun и второй сходы сдвига j-ro apuq1 мыпче; сю мод/ля соединены соответственно с и пто- рым выходами сдвига (j-1) гч арн1мстиче- скою моду/1с 0 6, 7, Oj сед-пой вход второго блока ускорг-нногг (и ;;;чо а соединен с вторым входом переноса операционного блока и третьим -одо - t осьмого арифметичегного модуля, п-ргил и второй выходыc/ioiна которогоroe/vi/ сп соотсет- сгвонно с третьим и четре. тым гг лодгми сдвига операционного блсса t второй выходы переноса которою соединены соответственно с выходами р.-рспосо первого I пятого арифг/етичосчи ie.t, второй выход сдвша в.оро: 1 .риф; euj, еского модуля соединен с пять.м рьиодом сдвига операциониого бмокл nept i ir u г,ц. сон входы управления мн-/р опе, ;r.i которого соед11неиы соответстос1 НУ с - тисрп ми входамийритмегичоски- ,,-;n z мгргою по четвертый и ариммет .ь-есг л псдулей с пятого тю восьмой, имфорпг-и::: гходы старших разрядов устройсг. р гэ дгнемы соответственно с ин ормгщионпым гходом счетчика циклов, с ш. кодтг-и riepnoii i руппы первого буферного peinoi a ч а:. ходами сторо о буферного р лис i р { И f срмгцпон- ные вход i первсй грхппм i очч.ого ссецп- нены соответстьеипо с .яг/и второй

ГруППЫ ПСрВСГО Г.у||ЧрН ГП Р ПСГря, СИНХривход которого соо/дпнг i с Ji - O iOM третьего олеменм И-ИЕ пгосий ихс,; которого соединен с вторым opj - ro олемен- та И-МЕ и выходом г.еогоч) з /снта НЕ, вход соторсго соединен роиходом второго буферного репктрг; лтоным синх- ровходом счетчика цпг/с,: пс-| .г,, М вло/;ом ciiiixpOHHsai v H оперяциг |:,о;о , о-д, спнх- ровходами триггера пер пост . второго триггера пыд-игаемь -. ргз I/IPC мч ; гтетя и выходом четоерто; о э .т.- -нт ,, первый вход которого соединен с п р-зим сь хо- дом микрооперации с.ыхро-мзации регистра микрокоманд, с оро. п.%г Д микрооперации сннхро чиа /ы : второго соединен с пероым 1чодом пкт т-о элемента

И-НЕ, второй сход которого соединен с вторым входом четвертого элемента И-НЕ и выходом элемента ИЛИ. первый, второй и третий входы которого соединены соответственно с вторым, третьим и четвертым выходами блока синхронизации, пятый выход которого соединен с входом второго элемента НЕ, выход которого соединен с третьим входом второго элемента И-НЕ,

0 синхровход регистра адреса соединен с первым синхрОЕ)ходом счетчика циклов, вы- лод которого соединен с вторым выходом ветвления устройства, первый выход ветвления которого соединен с выходом пере5 полпенни операционного блока, второй выход сдвша котооого соединен с первым входом первого элемента 2И-ИЛИ, выход которого соединен с четвертым входом сдвига операционного блока, третий выход

0 сдвига которого соединен с четвертым входом первого элемента 2И-ИЛИ и первым влодом второго элемента 2И-ИЛИ, выход которого соединен с вторым входом сдвта операционного блока, первый выход сдвига

5 которого соединен с четвертым входом второго элемента 2И-ИЛИ и вторым входом третьего элемента 2И-ИЛИ, выход которого соединен с первым входом сдвига операционного блока, четвертый выход сдвига кото0 рсго соединен с третьим выходом ветвления устройства и информационным входом второго триггера выдвигаемых разрядов множителя, прямой выход которого соединен с синхровходом второго триггера анализа

5 значащего бита, информационный вход которого соединен с входом логической единицы устройства.а выход - с первыми входами третьего элемента 2И-ИЛИ и четвертого элемента 2И-ИЛИ, выход которого

0 соединен с третьим входом сдвига операционного блока, пятый выход сдвига которого соединен с четвертым выходом ветвления устройства и информационным входом первого триггера выдвигаемых разрядов мно5 житепя, синхровход которого соединен с выходом пятого элемента И-НЕ и вторым входом синхронизации операционного блока, первый выход переноса которого соединен с информационным входом триггера

0 переноса, выход которого соединен с первым входом первого элемента ЗИ-ИЛИ, второй вход которого соединен с третьим выходом регистра микрокоманд, четвертый выход которого соединен с третьим входом

5 первого элемента ЗИ-ИЛИ, вторыми входами первого и второго элементов 2И-ИЛИ, с шестым входом четвертого элемента 2И- ИЛИ, с пятым входом третьего элемента 2И- ИЛИ, с первыми входами второго и третьего элементов ЗИ-ИЛИ и входом третьего элемента НЕ, выход которого соединен с третьими входами первого, второго и третьего элементов 2И-ИЛИ и третьими входами четвертого элемента 2И-ИЛИ и второго и третьего элементов ЗИ-ИЛИ, второй выход переноса операционного блока соединен с четвертым входом первого элемента ЗИ- ИЛИ. выход которого соединен с первым входом переноса операционного блока, второй вход переноса соединен с пятым выходом регистра микрокоманд и шестым входом первого элемента ЗИ-ИЛИ, пятый вход которого соединен с вторыми входами второго, третьего элементов ЗИ-ИЛИ и вы- лодом четвертого элемента Н Е, вход которого соединен с шестым выходом регистра микрокоманд, четвертыми и пятыми входами второго и третьего элементов ЗИ-ИЛИ, выход триггера знака соединен с информационными входами первой группы первого буферного регистра, четвертым входом третьего элемента 2И-ИЛИ, вторым входом четвертого элемента 2И-ИЛИ и четвертым входом четвертого элемента 2И-ИЛ И, пятый вход которого соединен с выходом первого триггера анализа значащего бита, первый и второй выходы микрооперации чтения регистра микрокоманд соединены соответственно с входами считывания первого и второго буферных регистров, информационные входы второй группы которых соеди- нены с выходами младших разрядов операционного блока и информационными выходами младших разрядов устройства, седьмой выход регистра микрокоманд соединен с вторым входом третьего элемента И-НЕ, инверсный выход первого триггера выдвигаемых разрядов множителя соединен с шестым входом второго элемента ЗИ- ИЛИ и шестым входом третьего элемента ЗИ-ИЛИ, седьмые входы второго и третьего элементов ЗИ-ИЛИ соединены с третьим выходом микрооперации синхронизации регистра микрокоманд, восьмой вход второго элемента ЗИ-ИЛИ соединен с восьмым входом третьего элемента ЗИ-ИЛИ и инверсным выходом второго триггера выдвигаемых разрядов множителя, вход сброса которого соединен с входом сброса второго триггера анализа значащего бита соединен с выходом второго элемента И-НЕ, выходы второго и третьего элементов ЗИ-ИЛИ соединены соответственно с вторым и первым входами управления микрооперациями операционного блока, первый и второй входы считывания которого соединены соответственно с выходами микроопераций чтения старшей части и младшей части слова регистра микрокоманд.

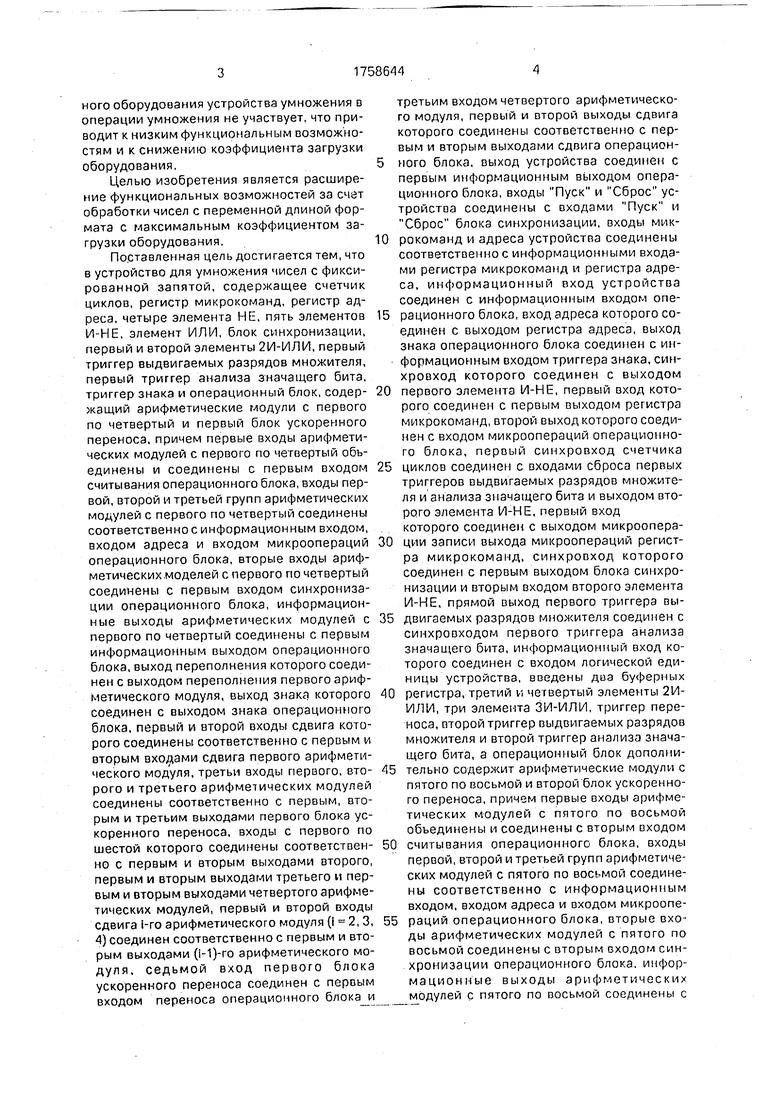

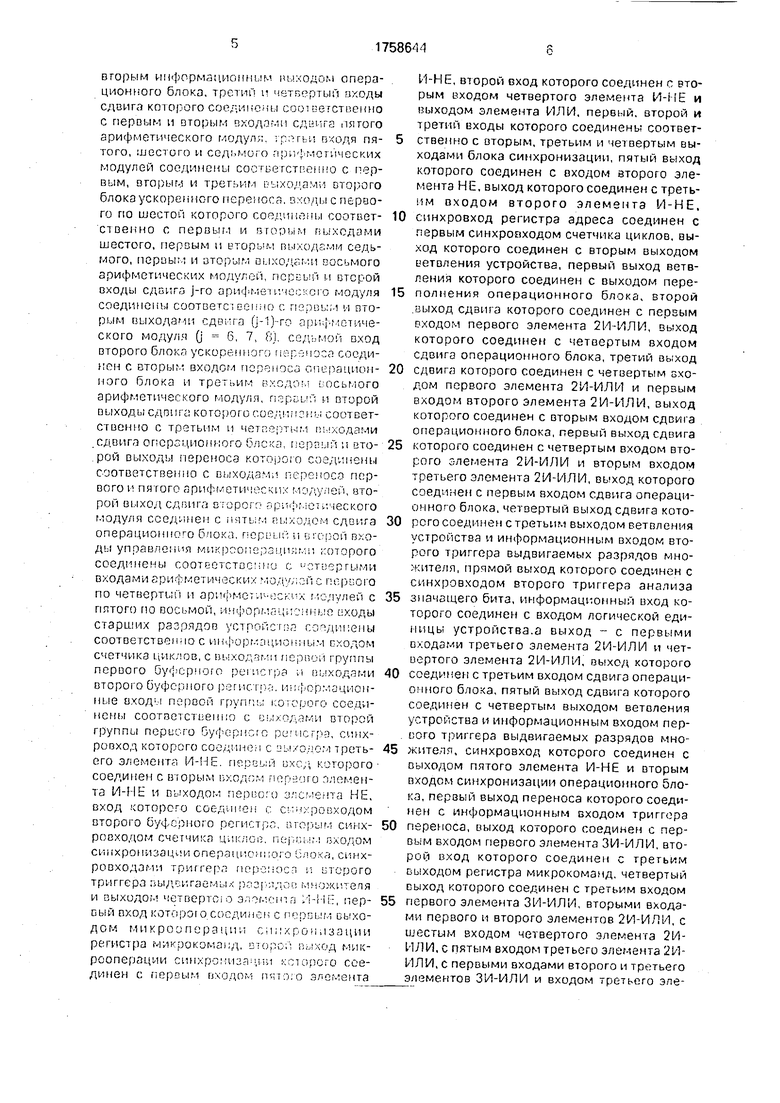

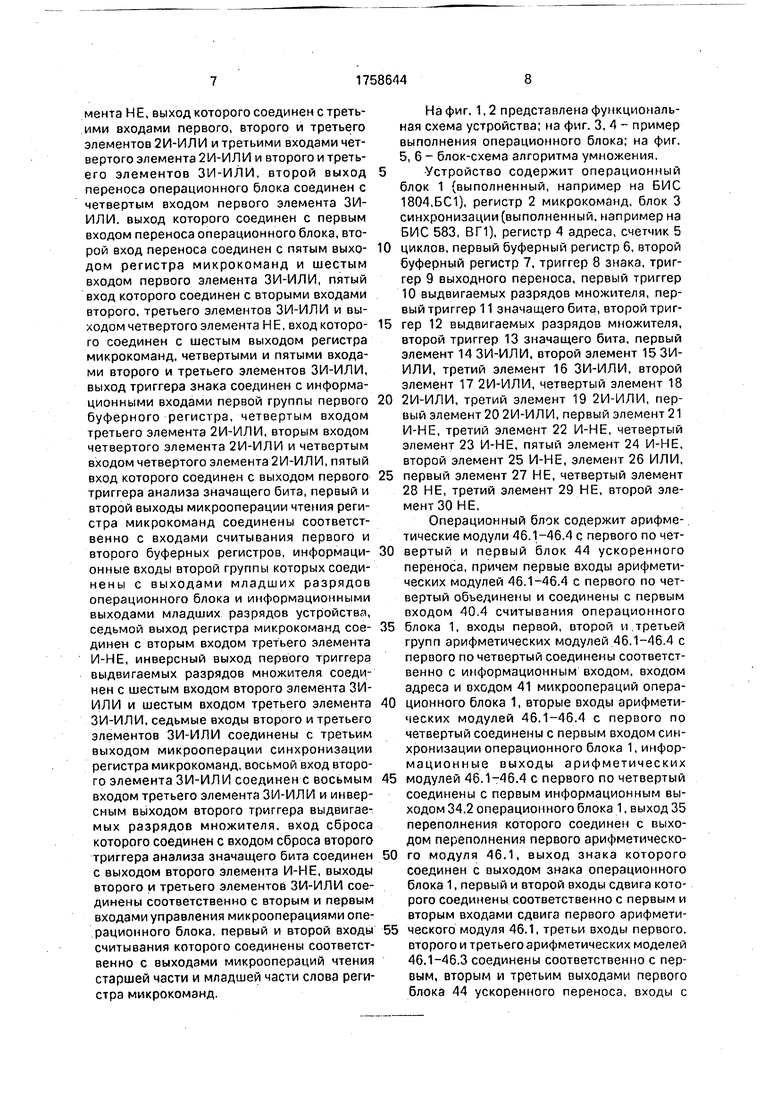

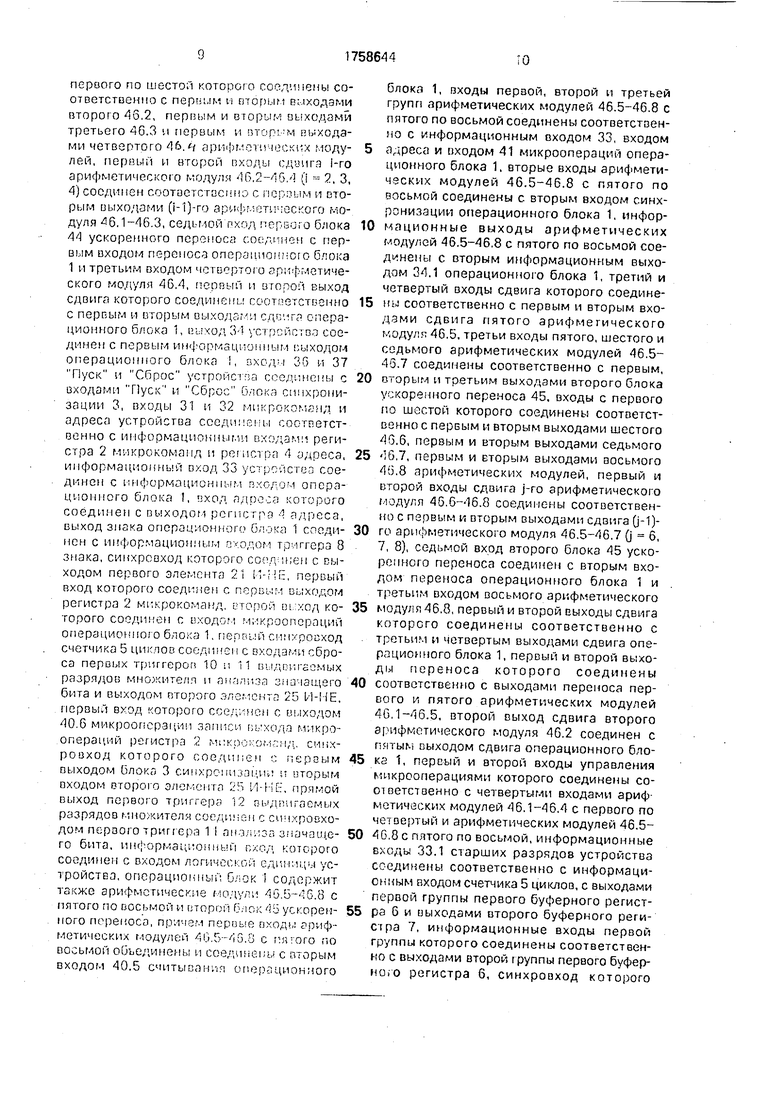

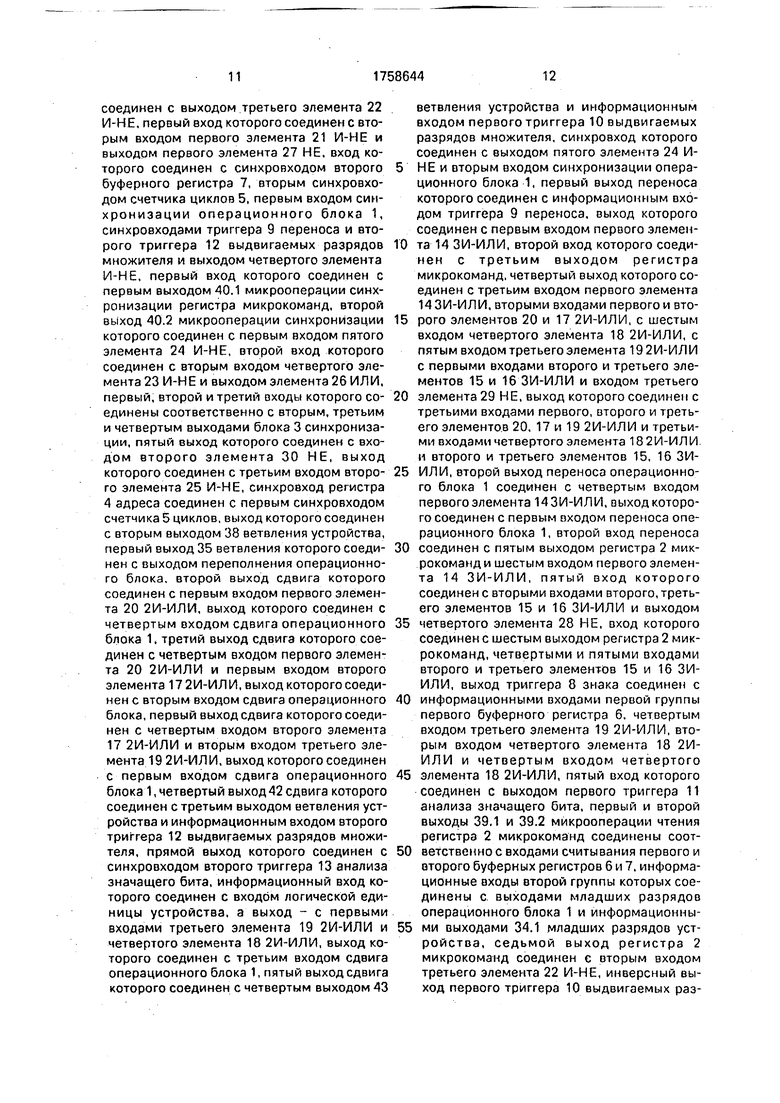

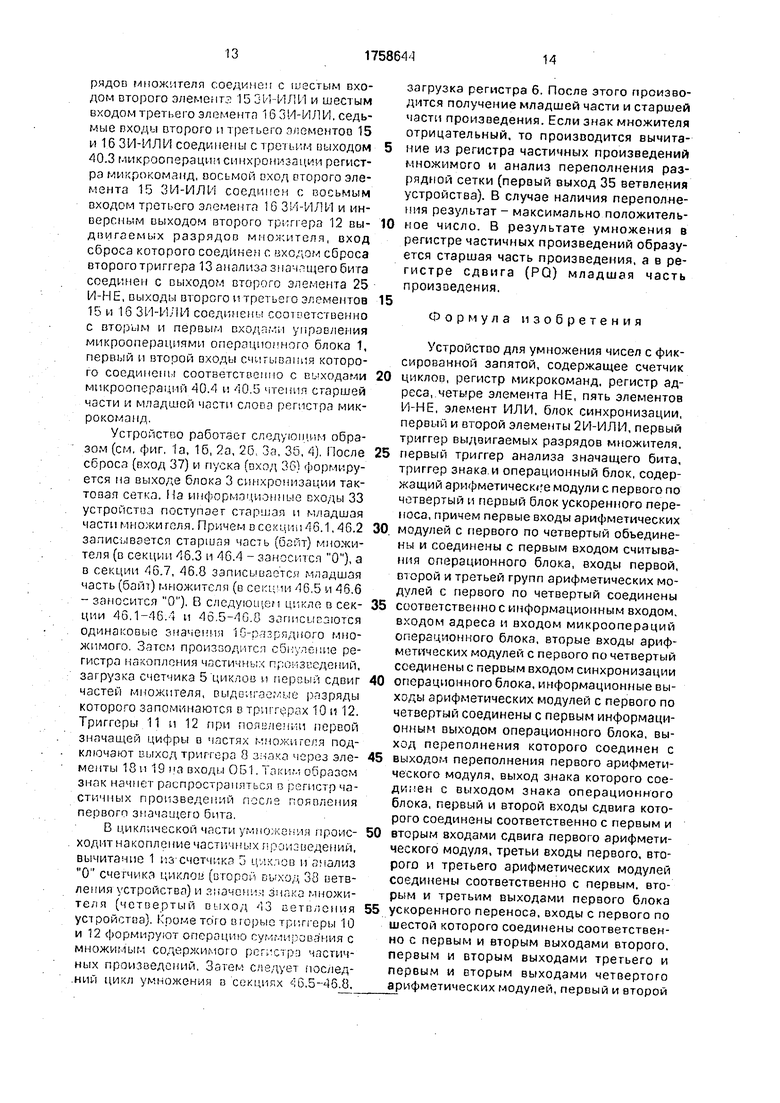

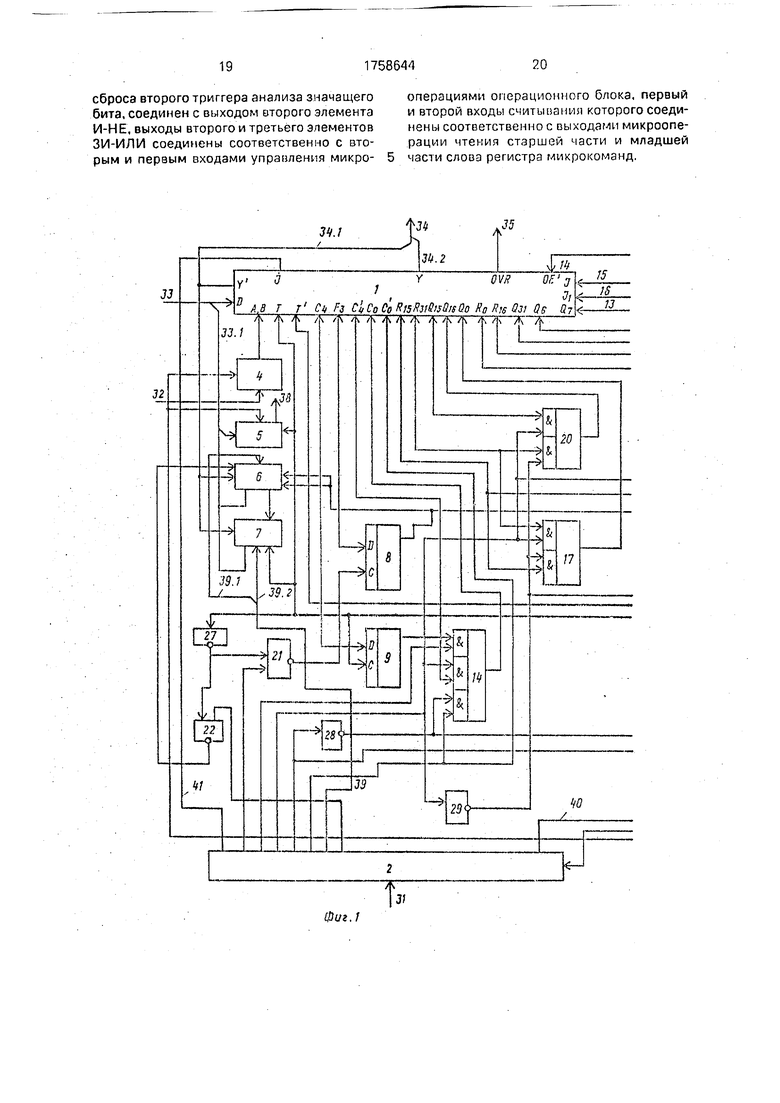

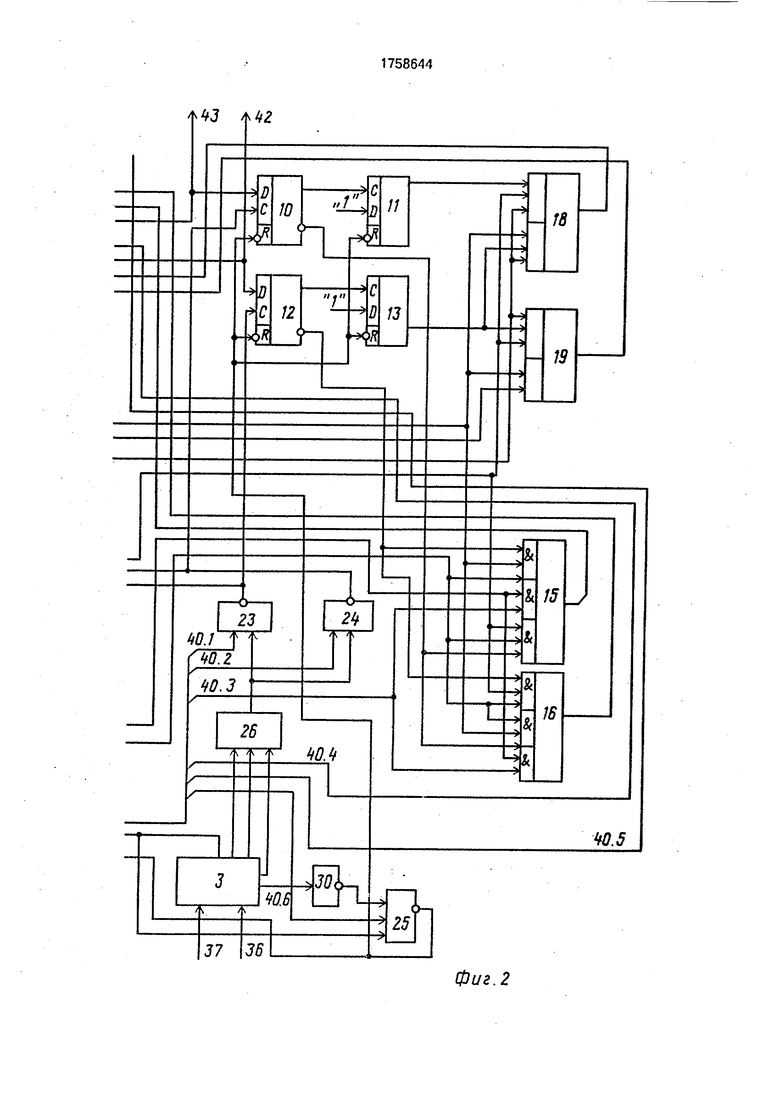

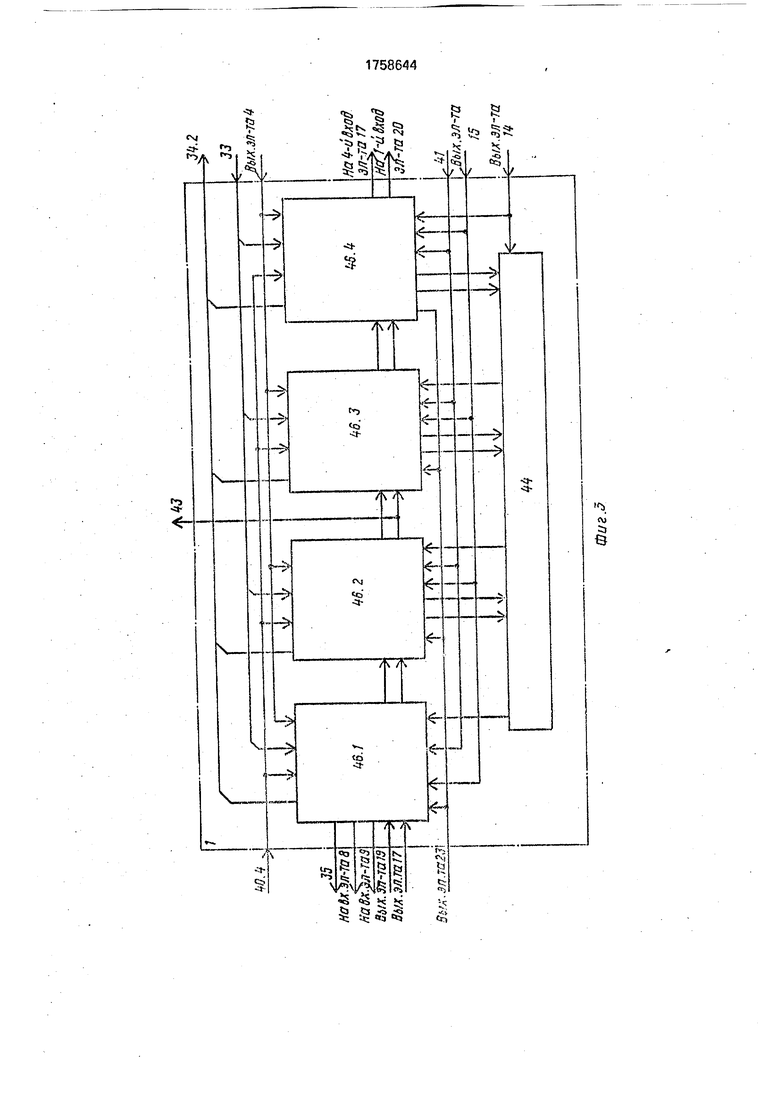

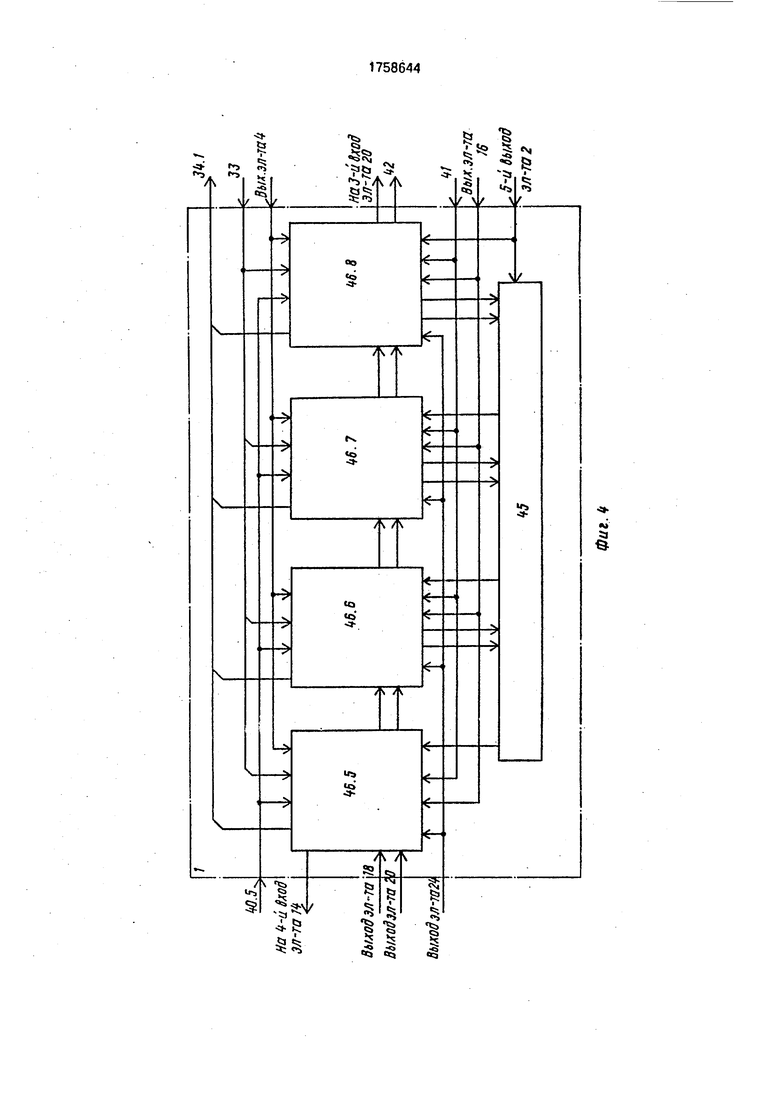

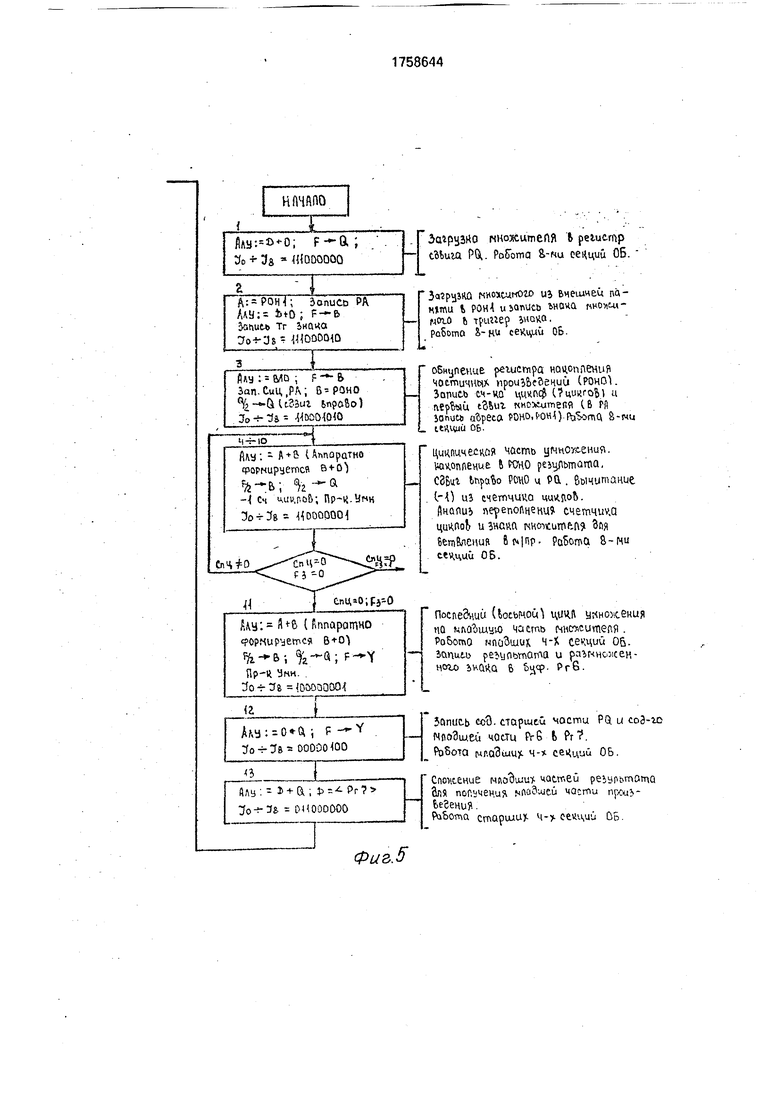

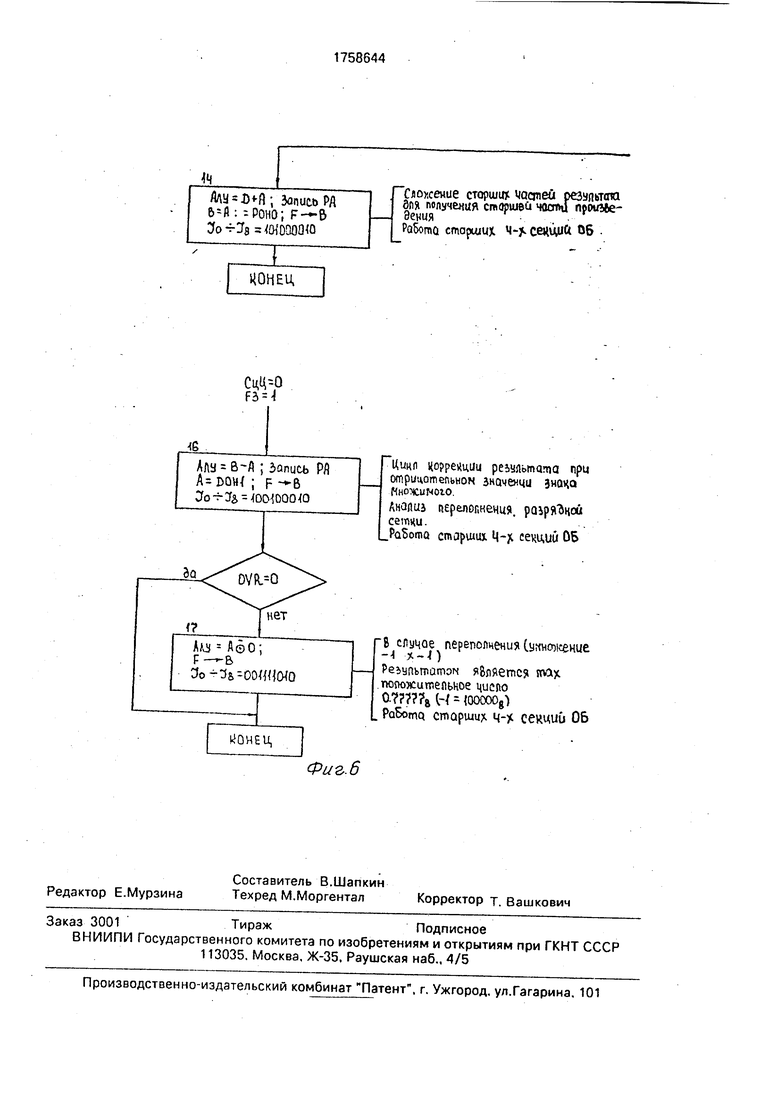

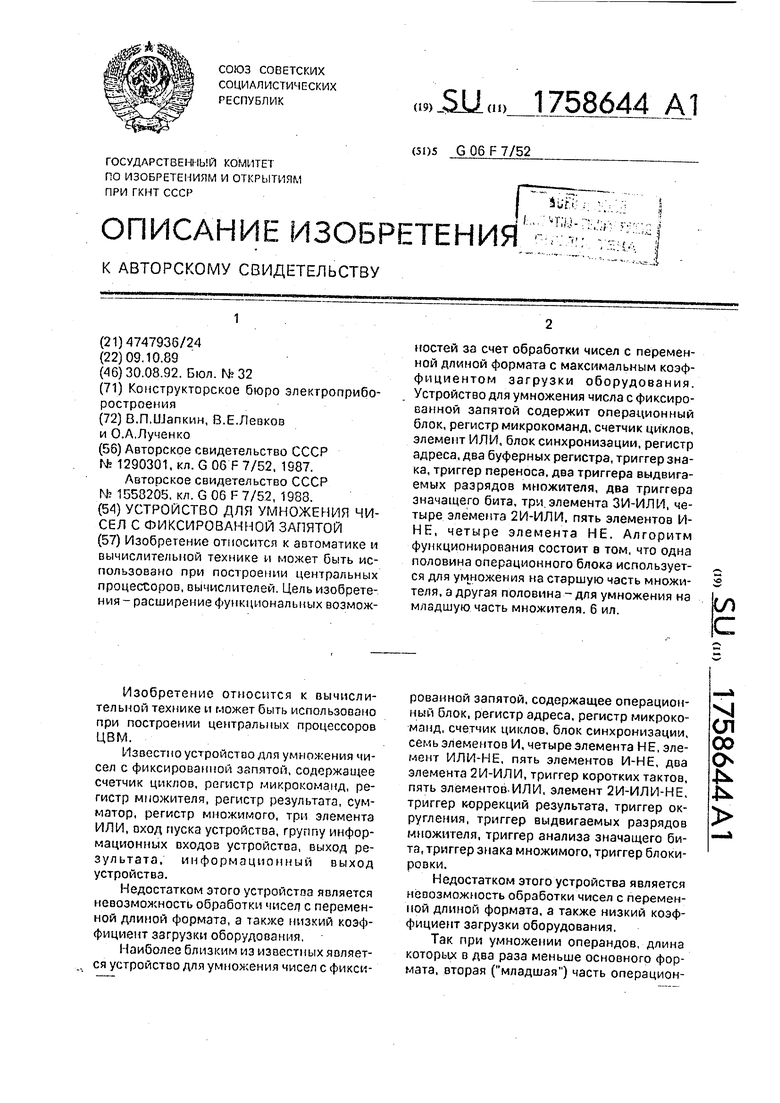

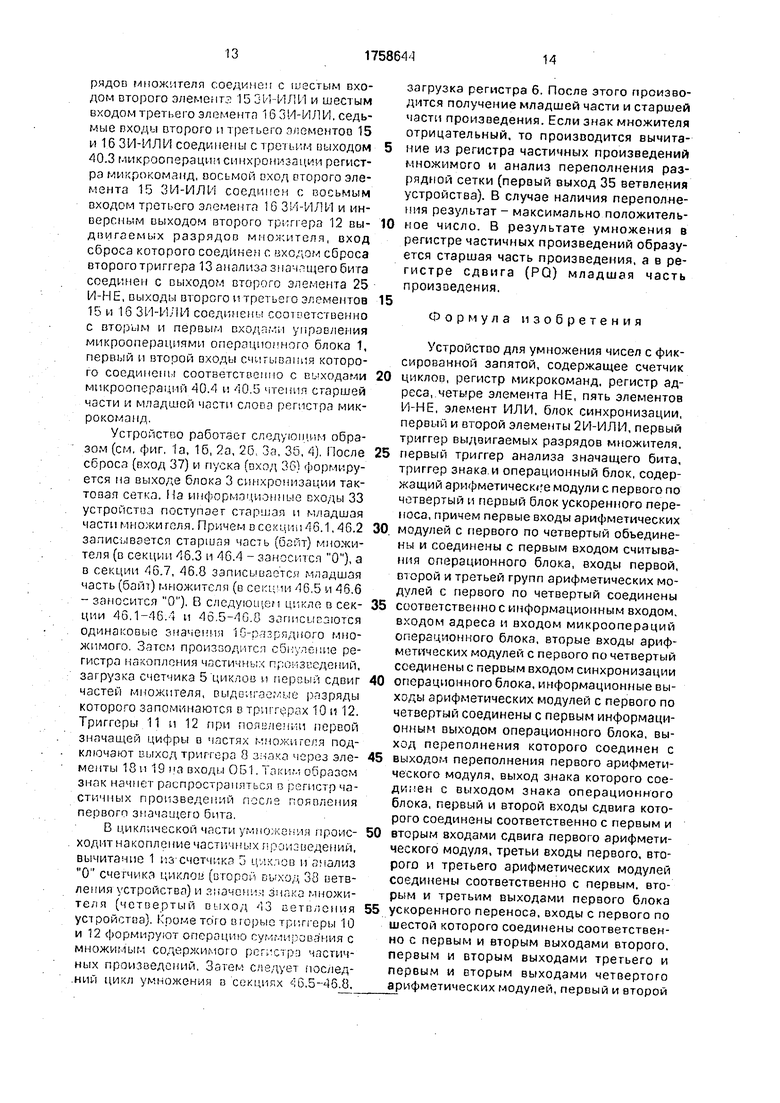

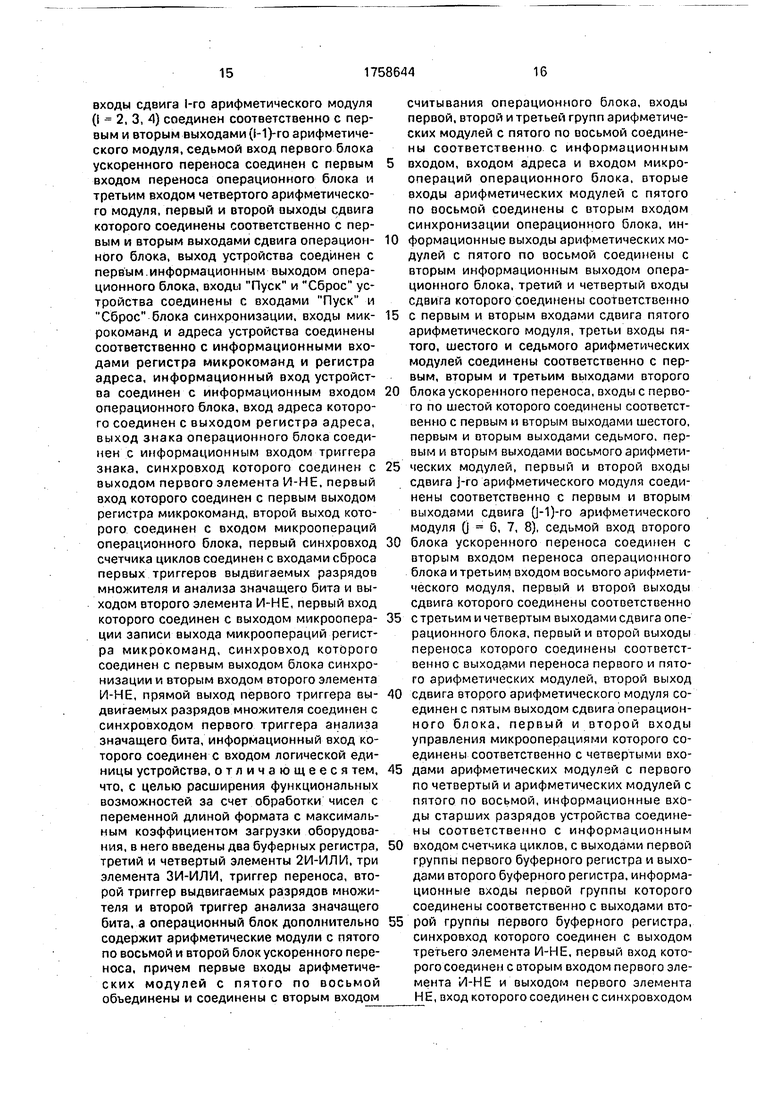

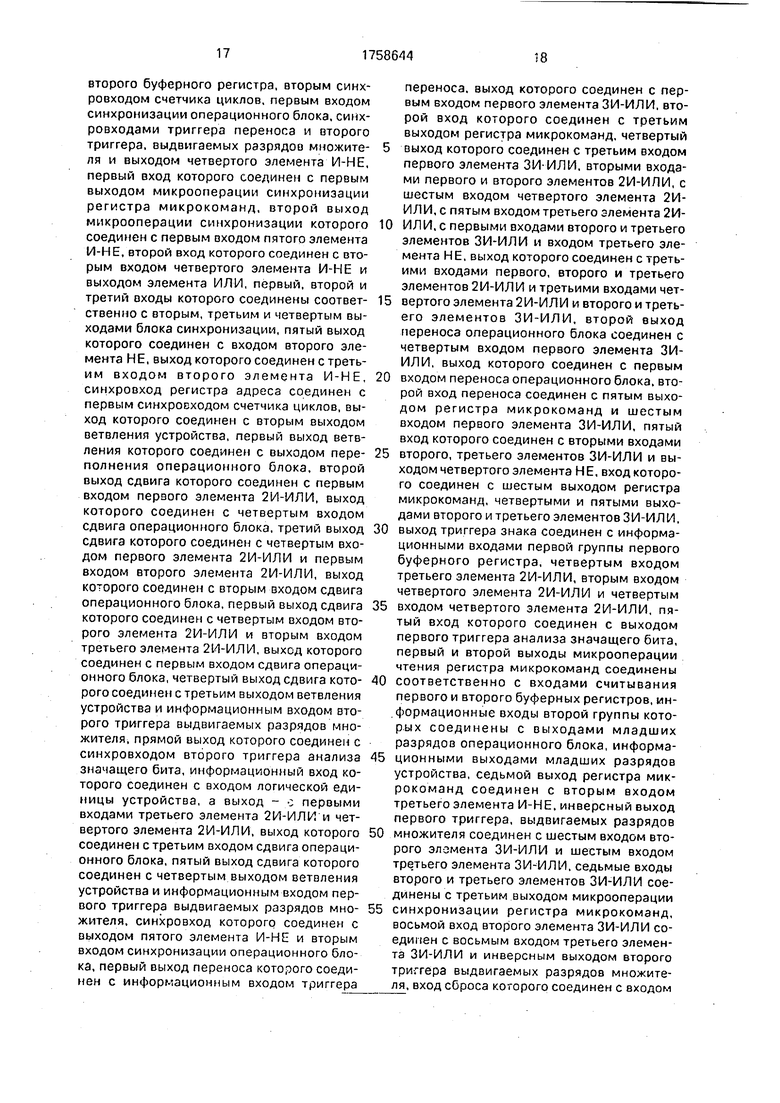

На фиг. 1,2 представлена функциональная схема устройства; на фиг. 3, 4 - пример выполнения операционного блока; на фиг. 5, 6 - блок-схема алгоритма умножения.

Устройство содержит операционный

блок 1 {выполненный, например на БИС 1804.БС1), регистр 2 микрокоманд, блок 3 синхронизации (выполненный, например на БИС 583, ВГ1), регистр 4 адреса, счетчик 5

циклов, первый буферный регистр 6, второй буферный регистр 7, триггер 8 знака, триггер 9 выходного переноса, первый триггер 10 выдвигаемых разрядов множителя, первый триггер 11 значащего бита, второй триггер 12 выдвигаемых разрядов множителя, второй триггер 13 значащего бита, первый элемент 14 ЗИ-ИЛИ. второй элемент 15 ЗИ- ИЛИ, третий элемент 16 ЗИ-ИЛИ, второй элемент 17 2И-ИЛИ, четвертый элемент 18

2И-ИЛИ, третий элемент 19 2И-ИЛИ, первый элемент 20 2И-ИЛИ, первый элемент 21 И-НЕ, третий элемент 22 И-НЕ, четвертый элемент 23 И-НЕ, пятый элемент 24 И-НЕ, второй элемент 25 И-НЕ, элемент 26 ИЛИ,

первый элемент 27 НЕ, четвертый элемент 28 НЕ, третий элемент 29 НЕ, второй элемент 30 НЕ.

Операционный блок содержит арифметические модули 46.1-46.4 с первого по четвертый и первый блок 44 ускоренного переноса, причем первые входы арифметических модулей 46.1-46.4 с первого по четвертый объединены и соединены с первым сходом 40.4 считывания операционного

блока 1, входы первой, второй и третьей групп арифметических модулей 46.1-46.4 с первого по четвертый соединены соответственно с информационным входом, входом адреса и входом 41 микроопераций операционного блока 1, вторые входы арифметических модулей 46.1-46.4 с первого по четвертый соединены с первым входом синхронизации операционного блока 1, инфор- мационные выходы арифметических

модулей 46.1-46.4 с первого по четвертый соединены с первым информационным выходом 34,2 операционного блока 1,выход 35 переполнения которого соединен с выходом переполнения первого арифметического модуля 46.1, выход знака которого соединен с выходом знака операционного блока 1, первый и второй входы сдвига которого соединены соответственно с первым и вторым входами сдвига первого арифметического модуля 46.1, третьи входы первого, второго и третьего арифметических моделей 46.1-46.3 соединены соответственно с первым, вторым и третьим выходами первого блока 44 ускоренного переноса, входы с

первого по шестой которого соединены соответственно с первым и вторым выходами второго 46.2, первым и вторим выходами третьего 46.3 и первым и втором выходами четвертого 46. / арпфмотп пзских модулей, мерный и второй входы сдоигз 1-го арифметического модуля 16.2-45, (I --- 2, 3, 4) соединен соответственно с парным и вторым выходами (i-l)-ro арифметического модуля 46.1-46.3, седьмой пхпд пг-р5о;о блока 44 ускоренного переноса соединен с первым входом переноса операционного блока 1 и третьим входом четвертого арифметического модуля 46.4, первый и агорой выход сдвига которого соединен:, соответственно с первым и вторым выходами сдвиг операционного блока 1, вькод 3-5 уел рейс; вл соединен с первым информационным выходом операционного блока , входы 36 и 37 Пуск и Сброс устройства соединены с входами Пуск и Сброс блока синхронизации 3, входы 31 и 32 микрокоманд и адреса устройства соединены соответственно с информационными входами регистра 2 микрокоманд и решет ра 4 адреса, информационный вход 33 уст рейсгеа соединен с информационным входом операционного блока , вход адреса которого соединен с выходом регистра адреса, выход знака операционного Опока 1 соединен с информационным ПУОДОМ триггера 8 знака, синхрсвход которого сосд ;неп с выходом первого элемента 21 П-Hi:, первый вход которого соединен с первым выходом регистра 2 микрокоманд, Е: торой BL ход которого соединен с входом микроопераций операционною блока 1, первыйсипхросход счетчика 5 цикчов соединен с входами сброса первых триггеров 10 п 11 выдвигаемых разрядов множителя п анализа значащего бита и выходом второго элемента 25 И-ПЕ, первый вход которого ссед-. нен с выходом 40.6 микрооперации записи выхода микроопераций регистра 2 MHKOOI ом :пд. смпх- рооход которого соединен с перзым выходом блока 3 синхронизации s; вторым входом второго элемента 25 И-НС:, прямой выход первого триггера 12 выдвигаемых разрядов мпохителя соединен с синхровхо- дом первого триггера 1 I анализа значащего бита, информационный сход которого соединен с входом логической единицы устройства, операционный блок i содержит также арифметические подули 40.5-45.8 с пятого по восьмой и второй блок 4й ускоренного переноса, причем первые ОУОД,: арифметических модулей 40.5-46.3 с пятого по восьмой объединены и соединены с пгорым входом 40.5 считывания операционного

блока 1, входы первой, второй п третьей групп арифметических модулей 46.5-46.8 с пятого по восьмой соединены соответственно с информационным входом 33, входом

адреса и входом 41 микроопераций операционного блока 1, вторые входы арифметических модулей 46.5-46.8 с пятого по восьмой соединены с вторым входом синхронизации операционного блока 1, информационные выходы арифметических модулей 46.5-46.8 с пятого по восьмой соединены с вторым информационным выходом 34.1 операционного блока 1, третий и четвертый входы сдвига которого соединены соответственно с первым и вторым входами сдвига пятого арифметического модуля 46.5. третьи входы пятого, шестого и седьмого арифметических модулей 46.546.7соединены соответственно с первым, вторым и третьим выходами второго блока

ускоренного переноса 45. входы с первого по шестой которого соединены соответственно с первым и вторым выходами шестого 46.6, первым и вторым выходами седьмого 46,7, первым и вторым выходами восьмого

45.8арифметических модулей, первый и второй входы сдвига j-ro арифметического модуля 46.6-46.8 соединены соответственно с первым и вторым выходами сдвига Q-1)го арифметического модуля 46,5-46.7 0 6, 7, 8), седьмой вход второго блока 45 ускоренного переноса соединен с вторым входом переноса операционного блока 1 и третьим входом восьмого арифметического

модуля 46.8, первый и второй выходы сдвига которого соединены соответственно с третьим и четвертым выходами сдвига операционного блока 1, первый и второй выходы переноса которого соединены

соответственно с выходами переноса первого и пятого арифметических модулей 4G.1-46.5, второй выход сдвига второго арифметического модуля 46.2 соединен с пятым выходом сдвига операционного блока 1, первый и второй входы управления микрооперациями которого соединены соответственно с четвертыми входами арифметических модулей 46.1-46.4 с первого по четвертый и арифметических модулей 46.546.8 с пятого по восьмой, информационные входы 33.1 старших разрядов устройства соединены соответственно с информационным входом счетчика 5 циклов, с выходами первой группы первого буферного регистра 6 и выходами второго буферного регистра 7, информационные входы первой группы которого соединены соответственно с выходами второй группы первого буфер- но;о регистра б, синхровход которого

соединен с выходом третьего элемента 22 И-НЕ, первый вход которого соединен с вторым входом первого элемента 21 И-НЕ и выходом первого элемента 27 НЕ, вход которого соединен с синхровходом второго буферного регистра 7, вторым синхровходом счетчика циклов 5, первым входом син- хронизации операционного блока 1, синхровходами триггера 9 переноса и второго триггера 12 выдвигаемых разрядов множителя и выходом четвертого элемента И-НЕ, первый вход которого соединен с первым выходом 40.1 микрооперации синхронизации регистра микрокоманд, второй выход 40.2 микрооперации синхронизации которого соединен с первым входом пятого элемента 24 И-НЕ, второй вход которого соединен с вторым входом четвертого элемента 23 И-НЕ и выходом элемента 26 ИЛИ, первый, второй и третий входы которого соединены соответственно с вторым, третьим и четвертым выходами блока 3 синхронизации, пятый выход которого соединен с входом второго элемента 30 НЕ, выход которого соединен с третьим входом второго элемента 25 И-НЕ, синхровход регистра 4 адреса соединен с первым синхровходом счетчика 5 циклов, выход которого соединен с вторым выходом 38 ветвления устройства, первый выход 35 ветвления которого соединен с выходом переполнения операционного блока, второй выход сдвига которого соединен с первым входом первого элемента 20 2И-ИЛИ, выход которого соединен с четвертым входом сдвига операционного блока 1. третий выход сдвига которого соединен с четвертым входом первого элемента 20 2И-ИЛИ и первым входом второго элемента 17 2И-ИЛ И, выход которого соединен с вторым входом сдвига операционного блока, первый выход сдвига которого соединен с четвертым входом второго элемента 17 2И-ИЛИ и вторым входом третьего элемента 19 2И-ИЛИ, выход которого соединен с первым входом сдвига операционного блока 1, четвертый выход 42 сдвига которого соединен с третьим выходом ветвления устройства и информационным входом второго триггера 12 выдвигаемых разрядов множителя, прямой выход которого соединен с синхровходом второго триггера 13 анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, а выход - с первыми входами третьего элемента 19 2И-ИЛИ и четвертого элемента 18 2И-ИЛИ, выход которого соединен с третьим входом сдвига операционного блока 1, пятый выход сдвига которого соединен с четвертым выходом 43

ветвления устройства и информационным входом первого триггера 10 выдвигаемых разрядов множителя, синхровход которого соединен с выходом пятого элемента 24 ИНЕ и вторым входом синхронизации операционного блока 1, первый выход переноса которого соединен с информационным входом триггера 9 переноса, выход которого соединен с первым входом первого элемента 14 ЗИ-ИЛИ, второй вход которого соединен с третьим выходом регистра микрокоманд, четвертый выход которого соединен с третьим входом первого элемента 14 ЗИ-ИЛИ. вторыми входами первого и второго элементов 20 и 17 2И-ИЛИ, с шестым входом четвертого элемента 18 2И-ИЛИ, с пятым входом третьего элемента 192И-ИЛИ с первыми входами второго и третьего элементов 15 и 16 ЗИ-ИЛИ и входом третьего

элемента 29 НЕ,выход которого соединен с третьими входами первого, второго и третьего элементов 20, 17 и 19 2И-ИЛИ и третьими входами четвертого элемента 182Й-ИЛИ и второго и третьего элементов 15, 16 ЗИИЛИ, второй выход переноса операционного блока 1 соединен с четвертым входом первого элемента 14 ЗИ-ИЛИ, выход которого соединен с первым входом переноса операционного блока 1, второй вход переноса

соединен с пятым выходом регистра 2 микрокоманд и шестым входом первого элемента 14 ЗИ-ИЛИ, пятый вход которого соединен с вторыми входами второго, третьего элементов 15 и 16 ЗИ-ИЛИ и выходом

четвертого элемента 28 НЕ, вход которого соединен с шестым выходом регистра 2 микрокоманд, четвертыми и пятыми входами второго и третьего элементов 15 и 16 ЗИ- ИЛИ, выход триггера 8 знака соединен с

информационными входами первой группы первого буферного регистра 6. четвертым входом третьего элемента 19 2И-ИЛИ, вторым входом четвертого элемента 18 2И- ИЛИ и четвертым входом четвертого

элемента 18 2И-ИЛИ, пятый вход которого соединен с выходом первого триггера 11 анализа значащего бита, первый и второй выходы 39.1 и 39.2 микрооперации чтения регистра 2 микрокоманд соединены соот0 ветственно с входами считывания первого и второго буферных регистров 6 и 7, информационные входы второй группы которых соединены с выходами младших разрядов операционного блока 1 и информационны5 ми выходами 34.1 младших разрядов устройства, седьмой выход регистра 2 микрокоманд соединен с вторым входом третьего элемента 22 И-НЕ, инверсный выход первого триггера 10 выдвигаемых разрядов множителя соединен с шестым входом второго элемента 15 ЗИ-ИЛ И и шестым входом третьего элемента 16 ЗИ-ИЛ И. седьмые входы второго и третьего элементов 15 и 16 ЗИ-ИЛ И соединены с треп-им шходом 40.3 микрооперации синхронизации регистра микрокоманд, восьмой вход второго элемента 15 ЗИ-ИЛИ соединен с восьмым входом третьего элемент 16 ЗИ-ИЛИ и инверсным выходом второго триггера 12 выдвигаемых разрядов множителя, вход сброса которого соединен с входом сброса второго триггера 13 анализа зна -пщего бита соединен с выходом второго элемента 25 И-НЕ, выходы второго и третьего элементов 15 и 16 ЗИ-ИЛИ соединены соответственно с вторим и первым входами управления микрооперациями операционного блока 1, первый и второй входы считывания которого соединены соответственно с выходами микроопераций 40.4 и 40.5 чтения старшей части и младшей части слова регистра микрокоманд.

Устройство работает следующим образом (см, фиг, 1а, 16, 2а, 26, За, 35, 4). После сброса (вход 37) и пуска (вход 36} формируется на выходе блока 3 синхронизации тактовая сетка. На информационные входы 33 устройства поступает старшая и младшая части множителя. Причем в секции 46.1,40.2 записывается старшая часть (байт) множителя (в секции 46.3 и 46.4 - заносится О), а в секции 46.7, 46.8 записывается младшая часть (байт) множителя (в секции 46.5 и 46.6 - заносится О). В следующем цикле в секции 46.1-46.4 и 46.5-4G.8 записываются одинаковые значенич Ш-р-прядного множимого. Затем производится c5i:yneni:e регистра накопления частичньк произведений, загрузка счетчика 5 циклов и первый сдвиг частей множителя, выдвигаемые разряды которого запоминаются в триггерах 10 и 12. Триггеры 11 и 12 при появлении первой значащей цифры в частях множителя подключают выход триггера 8 знача через элементы 18 и 19 на входы ОБ1. Таким образом знак начнет распространяться о регистр частичных произведений после появления первого значащего бита.

В циклической части умно/коння происходит накопление частичных произведений, вычитание 1 из счетчики 5 циклов и анализ О счегчика циклон (второй выход 38 гзетв- ления устройства) и значение знака множителя (четвертый оиход 43 ветвления устройства). Кроме того вторые триггеры 10 и 12 формируют операцию суммирования с множимым содержимою per/стр:) частичных произведений. Затем следует последний цикл умножения в секциях -16,5-45.8,

загрузка регистра 6. После этого производится получение младшей части и старшей части произведения. Если знак множителя отрицательный, то производится вычитание из регистра частичных произведений множимого и анализ переполнения разрядной сетки (первый выход 35 ветвления устройства). В случае наличия переполнения результат - максимально положительное число. В результате умножения в регистре частичных произведений образуется старшая часть произведения, а в регистре сдвига (PQ) младшая часть произведения.

Формула изобретения

Устройство для умножения чисел с фиксированной запятой, содержащее счетчик

циклов, регистр микрокоманд, регистр адреса, четыре элемента НЕ, пять элементов И-НЕ, элемент ИЛИ, блок синхронизации, первый и второй элементы 2И-ИЛИ, первый триггер выдвигаемых разрядов множителя,

первый триггер анализа значащего бита, триггер знака и операционный блок, содержащий арифметические модули с первого по четвертый и первый блок ускоренного переноса, причем первые входы арифметических

модулей с первого по четвертый объединены и соединены с первым входом считывания операционного блока, входы первой, второй и третьей групп арифметических модулей с первого по четвертый соединены

соответственно с информационным входом, входом адреса и входом микроопераций операционного блока, вторые входы арифметических модулей с первого по четвертый соединены с первым входом синхронизации

операционного блока, информационные выходы арифметических модулей с первого по четвертый соединены с первым информационным выходом операционного блока, выход переполнения которого соединен с

выходом переполнения первого арифметического модуля, выход знака которого соединен с выходом знака операционного блока, первый и второй входы сдвига которого соединены соответственно с первым и

вторым входами сдвига первого арифметического модуля, третьи входы первого, второго и третьего арифметических модулей соединены соответственно с первым, вторым и третьим выходами первого блока

ускоренного переноса, входы с первого по шестой которого соединены соответственно с первым и вторым выходами второго, первым и вторым выходами третьего и первым и вторым выходами четвертого арифметических модулей, первый и второй

входы сдвига 1-го арифметического модуля О 2, 3, 4) соединен соответственно с первым и вторым выходами (М)-го арифметического модуля, седьмой вход первого блока ускоренного переноса соединен с первым входом переноса операционного блока и третьим входом четвертого арифметического модуля, первый и второй оыходы сдвига которого соединены соответственно с первым и вторым выходами сдвига операционного блока, выход устройства соединен с первым информационным выходом операционного блока, входи Пуск и Сброс устройства соединены с входами Пуск и Сброс блока синхронизации, входы микрокоманд и адреса устройства соединены соответственно с информационными входами регистра микрокоманд и регистра адреса, информационный вход устройства соединен с информационным входом операционного блока, вход адреса которого соединен с выходом регистра адреса, выход знака операционного блока соединен с информационным входом триггера знака, синхровход которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с первым выходом регистра микрокоманд, второй выход которого соединен с входом микроопераций операционного блока, первый синхровход счетчика циклов соединен с входами сброса первых триггеров выдвигаемых разрядов множителя и анализа значащего бита и выходом второго элемента И-НЕ, первый вход которого соединен с выходом микрооперации записи выхода микроопераций регистра микрокоманд, синхровход которого соединен с первым выходом блока синхронизации и вторым входом второго элемента И-НЕ, прямой выход первого триггера выдвигаемых разрядов множителя соединен с синхровходом первого триггера анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обработки чисел с переменной длиной формата с максимальным коэффициентом загрузки оборудования, в него введены два буферных регистра, третий и четвертый элементы 2И-ИЛИ, три элемента ЗИ-ИЛИ, триггер переноса, второй триггер выдвигаемых разрядов множителя и второй триггер анализа значащего бита, а операционный блок дополнительно содержит арифметические модули с пятого по восьмой и второй блок ускоренного переноса, причем первые входы арифметических модулей с пятого по восьмой объединены и соединены с вторым входом

считывания операционного блока, входы первой, второй и третьей групп арифметических модулей с пятого по восьмой соединены соответственно с информационным

входом, входом адреса и входом микроопераций операционного блока, вторые входы арифметических модулей с пятого по восьмой соединены с вторым входом синхронизации операционного блока, ин0 формационные выходы арифметических модулей с пятого по восьмой соединены с вторым информационным выходом операционного блока, третий и четвертый входы сдвига которого соединены соответственно

5 с первым и вторым входами сдвига пятого арифметического модуля, третьи входы пятого, шестого и седьмого арифметических модулей соединены соответственно с первым, вторым и третьим выходами второго

0 блока ускоренного переноса, входы с первого по шестой которого соединены соответственно с первым и вторым выходами шестого, первым и вторым выходами седьмого, первым и вторым выходами восьмого арифмети5 ческих модулей, первый и второй входы сдвига j-ro арифметического модуля соединены соответственно с первым и вторым выходами сдвига Q-1)-ro арифметического модуля (j G, 7, 8), седьмой вход второго

0 блока ускоренного переноса соединен с вторым входом переноса операционного блока и третьим входом восьмого арифметического модуля, первый и второй выходы сдвига которого соединены соответственно

5 с третьим и четвертым выходами сдвига операционного блока, первый и второй выходы переноса которого соединены соответственно с выходами переноса первого и пятого арифметических модулей, второй выход

0 сдвига второго арифметического модуля соединен с пятым выходом сдвига операционного блока, первый и второй входы управления микрооперациями которого соединены соответственно с четвертыми вхо5 дами арифметических модулей с первого по четвертый и арифметических модулей с пятого по восьмой, информационные входы старших разрядов устройства соединены соответственно с информационным

0 входом счетчика циклов, с выходами первой группы первого буферного регистра и выходами второго буферного регистра, информа- ционные входы первой группы которого соединены соответственно с выходами вто5 рой группы первого буферного регистра, синхровход которого соединен с выходом третьего элемента И-НЕ, первый вход которого соединен с вторым входом первого элемента И-НЕ и выходом первого элемента НЕ, вход которого соединен с синхровходом

второго буферного регистра, вторым синх- ровходом счетчика циклов, первым входом синхронизации операционного блока, синх- ровходами триггера переноса и второго триггера, выдвигаемых разрядов множителя и выходом четвертого элемента И-НЕ, первый вход которого соединен с первым выходом микрооперации синхронизации регистра микрокоманд, второй выход микрооперации синхронизации которого соединен с первым входом пятого элемента И-НЕ, второй вход которого соединен с вторым входом четвертого элемента И-НЕ и выходом элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с вторым, третьим и четвертым выходами блока синхронизации, пятый выход которого соединен с входом второго элемента НЕ, выход которого соединен с третьим входом второго элемента И-НЕ, синхровход регистра адреса соединен с первым синхровходом счетчика циклов, выход которого соединен с вторым выходом ветвления устройства, первый выход ветвления которого соединен с выходом переполнения операционного блока, второй выход сдвига которого соединен с первым входом первого элемента 2И-ИЛИ, выход которого соединен с четвертым входом сдвига операционного блока, третий выход сдвига которого соединен с четвертым входом первого элемента 2И-ИЛИ и первым входом второго элемента 2И-ИЛИ, выход которого соединен с вторым входом сдвига операционного блока, первый выход сдвига которого соединен с четвертым входом второго элемента 2И-ИЛИ и вторым входом третьего элемента 2И-ИЛИ, выход которого соединен с первым входом сдвига операционного блока, четвертый выход сдвига которого соединен с третьим выходом ветвления устройства и информационным входом второго триггера выдвигаемых разрядов множителя, прямой выход которого соединен с синхровходом второго триггера анализа значащего бита, информационный вход которого соединен с входом логической единицы устройства, а выход - с первыми входами третьего элемента 2И-ИЛИ и четвертого элемента 2И-ИЛИ, выход которого соединен с третьим входом сдвига операционного блока, пятый выход сдвига которого соединен с четвертым выходом ветвления устройства и информационным входом первого триггера выдвигаемых разрядов множителя, синхровход которого соединен с выходом пятого элемента И-НЕ и вторым входом синхронизации операционного блока, первый выход переноса которого соединен с информационным входом триггера

переноса, выход которого соединен с первым входом первого элемента ЗИ-ИЛИ, второй вход которого соединен с третьим выходом регистра микрокоманд, четвертый выход которого соединен с третьим входом первого элемента ЗИ-ИЛИ. вторыми входами первого и второго элементов 2И-ИЛИ, с шестым входом четвертого элемента 2И- ИЛИ, с пятым входом третьего элемента 2И0 ИЛИ. с первыми входами второго и третьего элементов ЗИ-ИЛИ и входом третьего элемента НЕ, выход которого соединен с третьими входами первого, второго и третьего элементов 2И-ИЛИ и третьими входами чет5 вертого элемента 2И-ИЛИ и второго и третьего элементов ЗИ-ИЛИ, второй выход переноса операционного блока соединен с четвертым входом первого элемента ЗИ- ИЛИ, выход которого соединен с первым

0 входом переноса операционного блока, второй вход переноса соединен с пятым выходом регистра микрокоманд и шестым входом первого элемента ЗИ-ИЛИ, пятый вход которого соединен с вторыми входами

5 второго, третьего элементов ЗИ-ИЛИ и выходом четвертого элемента НЕ, вход которого соединен с шестым выходом регистра микрокоманд, четвертыми и пятыми выходами второго и третьего элементов ЗИ-ИЛИ,

0 выход триггера знака соединен с информационными входами первой группы первого буферного регистра, четвертым входом третьего элемента 2И-ИЛИ, вторым входом четвертого элемента 2И-ИЛИ и четвертым

5 входом четвертого элемента 2И-ИЛИ, пятый вход которого соединен с выходом первого триггера анализа значащего бита, первый и второй выходы микрооперации чтения регистра микрокоманд соединены

0 соответственно с входами считывания первого и второго буферных регистров, информационные входы второй группы которых соединены с выходами младших разрядов операционного блока, информа5 ционными выходами младших разрядов устройства, седьмой выход регистра микрокоманд соединен с вторым входом третьего элемента И-НЕ. инверсный выход первого триггера, выдвигаемых разрядов

0 множителя соединен с шестым входом второго элемента ЗИ-ИЛИ и шестым входом третьего элемента ЗИ-ИЛИ, седьмые входы второго и третьего элементов ЗИ-ИЛИ соединены с третьим выходом микрооперации

5 синхронизации регистра микрокоманд, восьмой вход второго элемента ЗИ-ИЛИ соединен с восьмым входом третьего элемента ЗИ-ИЛИ и инверсным выходом второго триггера выдвигаемых разрядов множителя, вход сброса которого соединен с входом

сброса второго триггера анализа значащего бита, соединен с выходом второго элемента И-НЕ, выходы второго и третьего элементов ЗИ-ИЛИ соединены соответственно с втооперзциями операционного блока, и второй входы считывания которого нены соответственно с выходами мик рации чтения старшей части и мл

рым и первым входами управления микро- 5 части слова регистра микрокоманд.

оперзциями операционного блока, первый и второй входы считывания которого соединены соответственно с выходами микрооперации чтения старшей части и младшей

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1990 |

|

SU1741129A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Операционный модуль | 1982 |

|

SU1083198A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении центральных процессоров, вычислителей. Цель изобретения - расширение функциональных возможностей за счет обработки чисел с переменной длиной формата с максимальным коэф- фициентом загрузки оборудования. Устройство для умножения числа с фиксированной запятой содержит операционный блок, регистр микрокоманд, счетчик циклов, элемент ИЛИ, блок синхронизации, регистр адреса, два буферных регистра, триггер знака, триггер переноса, два триггера выдвигаемых разрядов множителя, два триггера значащего бита, три элемента ЗИ-ИЛИ, четыре элемента 2И-ИЛИ, пять элементов И- НЕ, четыре элемента НЕ. Алгоритм функционирования состоит в том, что одна половина операционного блока используется для умножения на старшую часть множителя, а другая половина - для умножения на младшую часть множителя. 6 ил. СО С

ЗД./

У

У

OVX

OF.1 у

о,

А.В Т т Сii Co Co RisRuBifQtsQo Ко RX Qu Qs Я

35

OVX

„Фл

OF.1 у

о,

sQo Ко RX Qu Qs Я

15

1-.М-. Т 7J

Фиг. 2

и .tj -S .-о О; «з

л

3

Q

%

Н «sT

: 5

«S

Ǥ

НАЧАЛО

i

1

Дмг. Зо За «{оооооо

U JPOHT;запись РА ААМ: Р -ь Затль Тг 5нача ШОООСЦО

Ала : Мо ; Зап. СиЦ, 8-РОно %- -йигвиг ьпраЫ Зо 3& .MuOOWO

-ю

илу: - А + & (Аппоратно формирнеглсй в+б

%-гь;

-{ Сч чицпоб; Пр-ц. 000000

cnu,so;Fa-0

Aw. (fcnnapairiHO нормируете В+о

, %-а;

Пр-Ч Чмн

о-т-tJa шьоаооо

г

Ака: i Р

rfo-r-tfft а 00000100

3

ЯЛУ -ь-fa. DH оооооо

Загрызло множители Ь регистр сйЬига Рй,. Робота &-NU секций Об.

rsHoswMOto uj вчешиеи па- кцти I РОнА иьапись гнаиа «копии- мого ь триггер IHQKO. Робота &-ни секции ОБ.

оБиупениЕ регистра наяоппенив чоатичнад npou bfSeHuu tPOHDl. Запись ач-на ццчпс (ци«гоЬ1 и пеоЫц «нохитепя С 6 pfl ion-act Лреса TOHO,) PaSsmQ &-NU ttnvwu ОБ.

Цичпцческоя Чисть умнокения. tovmnewe 6 fOHO pesyAbmaroa. С3Јиг btvpauo РСНО и Рй . Вычитание ((} и счетчииа . Дналиь ле епоинеки счетчича циЯПоЬ и wsfta tsucntuifl ft.fi Зпя бстбленив Йм|пр. paSoma S-NU ««.ций ОБ.

ПоспеЗцци UocbMoCt1 и,ичл умнокения nQ ила Ьидц Л цасгпь (чнс ситепя . РаБото 4-Х секций 05. ianutb результата и рагкножец- ною анаца 6 Ргб.

5апис.ь ссЗ. старшей части PQ и соЭ-го мпоЗилей части Ргб Ь Рг. PoWa rur. ч- сецций ОБ.

Спокение миоЗши частей реььр&тогпа

ЙЛЯ пог. 4(o3wtu ча;гпи npouiЬейени.

Paboma cmapuaajt ч секций ОБ

Фиг.5

К

Ma .D«-fl; Запись PA 6-fl: POHO; Зо-Ма ШООШО

HOHEU

СцЦ--0

F3 -f

-16

Ала ; Запись Р/) ; р

СГо-г г.

Aw -А©о;

F--В (МО

с

40НЈЦ

Фиг. 6

Сложение старшие vacjneu резапькпа бпя попечения старшей частой приябе- Эения . , л

Работа старших. Ч-f сенчий 06

Цицп ко реииии peiyflbmama при отрицотепьном значекци знача

|Чно:чсиГ огО.

Анализ перелог.кечия. сетци. PaSoma старших Ц- сеииий ОБ

В случае переполнения (у одгение - х-О

Реьупыпйто яВлйбтс STVi)c попо)сип5епькое циспо О. t- iooooog) . PaSomq старшие ц-f. секции ОБ

| Устройство для умножения | 1985 |

|

SU1290301A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1558205 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-30—Публикация

1989-10-09—Подача