Изобретение относится к вычислительной технике и может быть использовано при создании микроЭВМ.

Известно устройство для сопряжения процессора с памятью, содержащее блок управления, регистр адреса, первый и второй приемопередатчики, причем входы-выходы первого и второго приемопередатчиков соединены с входами-выходами устройства для подключения соответственно входов-выходов старшего и младшего байтов данных - адреса процессора, первый, второй входы задания направления передачи информации первого, второго приемопередатчиков подключены к входам устройства для подключения выходов чтения и записи процессора, входы выборки первого, второго приемопередатчиков соединены соответственно с первым, вторым выходами блока управления, третий выход которого соединен с выходом устройства для подключения к входу синхронизации процессора, с первого по пятый входы блока управления соединены с входами устройства для подключения выходов записи, чтения, записи режима работы с данными, синхронизации и нулевого разряда данных - адреса процессора, вход регистра адреса соединен с входом устройства для подключения выхода данных - адреса процессора, вторые входы-выходы первого и второго приемопередатчиков соединены с входами-выходами устройства для подключения соответственно входов-выходов данных младших и старших разрядов памяти, выход регистра адреса соединен с выходом устройства для подключения к адресному входу памяти, а также дешифратор на n выходов (n - число модулей памяти) и n групп по два элемента ИЛИ в каждой группе, причем первые входы первого, второго элементов ИЛИ i-группы (i = (i =  ) ) соединены с i-м выходом дешифратора, вторые входы первого, второго элементов ИЛИ всех групп соединены соответственно с первым, вторым выходами блока управления, вход дешифратора соединен с выходами регистра адреса, выходы первого, второго элементов ИЛИ всех групп соединены с группой выходов устройства для подключения входов выборки модулей памяти.

) ) соединены с i-м выходом дешифратора, вторые входы первого, второго элементов ИЛИ всех групп соединены соответственно с первым, вторым выходами блока управления, вход дешифратора соединен с выходами регистра адреса, выходы первого, второго элементов ИЛИ всех групп соединены с группой выходов устройства для подключения входов выборки модулей памяти.

Данное устройство не позволяет сопрягать с процессором память емкостью более 2m-1 m-разрядных слов (m - количество линий данных - адреса в магистрали "Общая шина").

Целью изобретения является повышение емкости, подключаемой к процессору памяти, при фиксированном количестве линий данных - адреса магистрали "Общая шина" за счет увеличения числа регистров адреса и сообщения ему способности их последовательно заполнять через магистраль перед обращением к запоминающему устройству.

Цель достигается тем, что устройство для сопряжения процессора с памятью снабжено k (k = 1, 2, 3, ...) m-разрядными регистрами адреса, информационные входы которых соединены с одноименными входами устройства, служащими для подключения шин адреса - данных магистрали "Общая шина", управляющие входы 2 (k + 1)-го регистров адреса подсоединены к входам устройства для подключения одноименных шин синхронизации записи адреса магистрали, (l + 1) - (m(k + 1) -1) (l = 1, 2, ..., m (k + 1) - 2) выходы регистра адреса подключены соответственно к 1-(m(k+1)-l-1) входам дешифратора, остальные 1-l выходы регистров адреса служат выходами устройства для подключения адресных входов памяти.

Сущность изобретения заключается в следующем. Наличие в предложенном устройстве k + 1 m-разрядных регистров адреса вместо одного позволяет увеличить область адресуемой памяти дот 2m(k+1)-1 m-разрядных слов. При этом организация последовательного заполнения данных регистров обеспечивает такое же количество используемых линий данных - адреса, как и в известном устройстве. В результате при фиксированном количестве линий данных - адреса магистрали "Общая шина" увеличивается емкость подключаемой к процессору памяти.

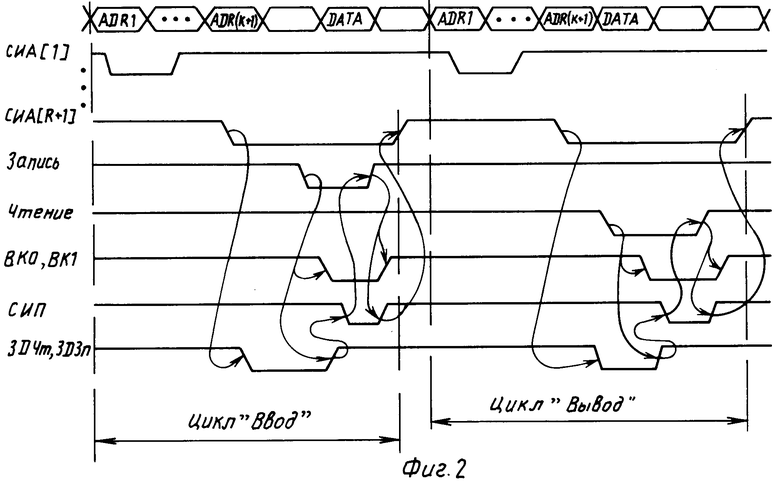

На фиг. 1 приведена структурная схема устройства; на фиг.2 - временная диаграмма его работы; на фиг.3 - зависимость емкости, подключенной к процессору памяти, от количества регистров адреса в устройстве.

Устройство для сопряжения процессора с памятью содержит (фиг.1) блок 1 управления, дешифратор 2 на n выходов, два магистральных приемопередатчика 3-1 и 3-2, k+1 m-разрядных регистров 4 адреса, 2 . n элементов ИЛИ 5. Кроме того, на фиг.1 показаны n модулей 6 оперативной памяти, в состав каждого из которых входят блоки хранения старших байтов (полуслов) 7 и младших байтов 8.

Блок 1 управления предназначен для управления работой устройства посредством формирования сигналов выборки блока хранения младших или старших байтов (полуслов) в модуле памяти, соответственно ВК0 и ВК1, а также сигнала синхронизации пассивного устройства СИП на основе управляющей информации, поступающей из магистрали. Данный блок реализуется идентично блоку управления прототипа.

Дешифратор 2 служит для определения модуля памяти, к которому производится обращение, и управления передачей в него сигналов выборки ВК0 и ВК1 от блока 1 управления. Данный блок представляет собой дешифратор с инверсными выходами по количеству подключаемых модулей памяти.

Двунаправленные приемопередатчики 3 предназначены для передачи информации посредством шины данных (ШД) либо из магистрали в память, либо в обратном направлении. Данные блоки могут быть выполнены стандартным образом, например, на основе микросхем КР588ВА1.

Регистры 4 адреса предназначены для запоминания кода адреса, по которому производится обращение к памяти и установка его посредством шины адреса (ША) на адресных входах модулей памяти.

Элементы ИЛИ 5 служат для передачи сигналов ВК0 и ВК1 блока 1 управления только в тот модуль памяти, к которому производится обращение, что инициируется сигналами от дешифратора 2.

Модули 6 памяти предназначены для хранения кодов. Блоки хранения старших и младших байтов 7 и 8 служат для хранения соответственно 8-15 и 0-7 разрядов, записанных в модуль 6 памяти 16-разрядных слов.

На схеме не показана связь блоков устройства с шиной питания.

Работа устройства рассматривается на примере сопряжения процессора с памятью емкостью 231 16-разрядных слов. В этом случае устройство содержит два регистра адреса (4-1 и 4-2), синхронизация записи информации в которые производится соответственно по сигналам СИА1 и СИА2(синхронизация активного устройства магистрали "Общая шина"), т.е. k = 1, m = 16.

При обращении к памяти процессор устанавливает на шинах данных - адреса (ДА [0 - 15] ) магистрали "Общая шина" первое слово адреса считываемого слова данных (см. фиг.2). Затем подается первый сигнал синхронизации активного устройства (СИА1=0) на управляющий вход регистра 4-1 адреса, по которому слово адреса записывается в данный регистр. После этого процессор снимает сигнал СИА1=0 и на шинах данных - адреса магистрали устанавливает второе слово адреса считываемого слова данных, в котором значение ДА [0] определяет, к старшему или младшему байту (полуслову) адресуемого слова данных производится обращение. Затем процессор выставляет второй сигнал синхронизации активного устройства (СИА2 = 0), по которому слово адреса переписывается в регистр 4-2 адреса. Кроме того, данный сигнал поступает в блок 1 управления и инициирует запоминание в блоке 1 сигналов с шин ДА [0] и "Байт", последний из которых определяет разрядность адресуемых слов (если "Байт" = 1, то устройство работает с 16-разрядными словами, если "Байт" = 0, то устройство работает с байтами).

Записанный в регистры адреса (4-1 и 4-2) адрес делится на две части. Первая часть (разряды 1-l) поступает по шине адреса ША [1-l]) на адресные входы памяти, вторая часть (разряды (l+1)-[m(k+1)-1]) служит кодом номера модуля памяти и поступает по шине адреса (ША[(l+1-(m(k+1)-1)]) на входы дешифратора 2, устанавливая нулевой сигнал на выходе дешифратора, соответствующем адресуемому модулю памяти. После этого процессор снимает старое слово адреса с магистрали "Общая шина".

При считывании данных из модуля памяти (см. цикл "Ввод" на фиг.2) процессор устанавливает нулевой сигнал на шине "Запись" магистрали "Общая шина" (3п = 0). Данный сигнал, поступая в блок 1 управления, вызывает формирование на его выходах сигналов ВК0 и ВК1 в зависимости от сигналов "Байт" и ДА [0] , например, при реализации блока 1 на основе микросхемы КР 588 ВГ2 в соответствии с таблицей.

Сформированные на выходах блока 1 нулевые сигналы ВК0 и ВК1 посредством элементов ИЛИ 5, управляемых дешифратором 2, передаются в адресуемый модуль 6 памяти на входы разрешения обращения к микросхемам памяти (входы выборки кристалла). При этом на вход режима работы микросхем с шины "Запись" магистрали "Общая шина" поступает нулевой сигнал, что соответствует режиму чтения, а на их адресные входы - код адреса по шине адреса ША [1-l] с регистров адреса (4-1, 4-2). В результате производится считывание информации из памяти, которая устанавливается на шинах данных памяти (ШД [8-15] и ШД [0-7] ) в зависимости от разрядности считываемого слова (определяемого нулевыми сигналами ВК0 и ВК1). Считанные данные поступают в каналы магистральных приемопередатчиков 3-1 и 3-2, на входы разрешения передачи которых поступают нулевые сигналы ВК. В результате обеспечивается передача данных из канала в магистраль "Общая шина" на шины ДА [0-15], поскольку сигнал 3п=0, также поступающий на управляющие входы магистральных приемопередатчиков, настраивает их на передачу информации в магистраль "Общая шина".

Затем блок 1 управления формирует сигнал синхронизации пассивного устройства (СИП= 0),, который поступает в магистраль "Общая шина" и служит для процессора сигналом квитирования, сообщающим о передаче данных из памяти в магистраль. Задержка формирования сигнала СИП=0 относительно сигналов ВК задается длительностью нулевого сигнала "Задержка чтения" ЗД Чт, который вырабатывается в блоке 1 управления на основе разряда емкости RC-цепочки. По сигналу СИП=0 процессор считывает данные из магистрали и снимает сигнал "Запись" (Зп=1). После этого блок управления перестает формировать сигналы (нулевые) ВК и СИП (ВК0=ВК1=СИП=1), последний из которых инициирует установку процессором СИА2=1, что в свою очередь приводит к установке блока управления в исходное состояние. На этом цикл обращения к памяти завершен.

Запись данных в модуль памяти (см. цикл "Вывод" на фиг.2) производится аналогично циклу считывания. Отличие заключается в следующем.

После снятия последнего слова адреса процессор устанавливает на шинах данных - адреса магистрали данные и вместо сигнала "Запись" формирует сигнал "Чтение" (Чт=0). Блок 1 срабатывает в соответствии с приведенной таблицей. В результате микросхемы адресуемого модуля 6 работают в режиме записи (на вход "Запись-чтение" поступает единица с шины "Запись"), магистральные приемопередатчики передают данные из магистрали "Общая шина" в память, а сигнал СИП=0 сообщает процессору о записи данных в память и вызывает снятие последним данных с магистрали, установку сигналов Чт=ВК0=ВК1=1 и, затем СИП= 1, СИА[k+1] = 1. Вместо сигнала ЗДЧт = 0 блоком 1 формируется нулевой сигнал "Задержка записи" ЗДЗп.

При сопряжении с постоянной памятью устройство работает только в режиме считывания данных из памяти, реализуя цикл "Ввод".

При работе с фиксированным модулем памяти устройство может функционировать в режиме с сокращенным временем доступа. В этом случае код модуля памяти записывается в соответствующие регистры при первом обращении. В дальнейшем производится запись информации лишь в те регистры, где хранится адрес слова данных в модуле памяти. Это достигается установкой сокращенного числа сигналов синхронизации СИА и позволяет уменьшить длительность последовательной записи адреса данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1345203A1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Вычислительная система | 1989 |

|

SU1734101A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании микроЭВМ. Целью изобретения является повышение емкости, подключаемой к процессору памяти, при фиксированном количестве линий данных - адреса магистрали "Общая шина". Это достигается тем, что в устройство введены k(k= 1, 2, 3, ...) m-разрядных регистров адреса, запись в которые производится последовательно, и соответствующие функциональные связи. В результате достигается увеличение емкости, подключаемой к процессору памяти, в 2mk раз. Устройство содержит блок управления, регистр адреса, приемопередатчик, дешифратор и группы элементов ИЛИ. 1 табл., 3 ил.

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ, содержащее блок управления, регистр адреса, первый и второй приемопередатчики, причем входы-выходы первого и второго приемопередатчиков соединены с входами старшего и младшего байтов адреса устройства, первый и второй входы задания направления передачи первого и второго приемопередатчиков подключены к входам чтения и записи устройства, входы выборки первого и второго приемопередатчиков соединены соответственно с первым и вторым выходами блока управления, третий выход которого соединен с выходом синхронизации устройства, с первого по пятый входы блока управления соединены с входами записи, чтения, режима, синхронизации и нулевого разряда шины данных адреса устройства, вход данных регистра адреса соединен с шиной данных-адреса устройства, вторые входы-выходы первого и второго приемопередатчиков соединены с младшими и старшими разрядами шины данных памяти устройства, выход регистра адреса соединен с шиной адреса памяти устройства, дешифратор и n групп по два элемента ИЛИ, причем первые входы первого и второго элементов ИЛИ i-й групп (i=  )соединены с i-м выходом дешифратора, вторые входы первого и второго элементов ИЛИ всех групп соединены соответственно с первым и вторым выходами блока управления, вход дешифратора соединен с выходами регистра адреса, выходы первого и второго элементов ИЛИ всех групп соединены с группой выходов выборки модулей памяти устройства, отличающееся тем, что оно дополнительно снабжено k (k = 1, 2, ...) m-разрядными регистрами адреса, информационные входы которых соединены с одноименными входами устройства, служащими для подключения шин адреса-данных магистрали "Общая шина", управляющие входы 2 ÷ (k + 1)-х регистров адреса подсоединены к входам устройства для подключения одноименных шин синхронизации записи адреса магистрали, (l + 1) ÷ [m(k+1)-1] , (где l = 1, 2, ..., m(k + 1) - 2) выходы регистров адреса подключены соответственно к 1 ÷ [m(k+1)-(l-1)] входам дешифратора, остальные 1 ÷ l выходы регистров адреса служат выходами устройства для подключения адресных входов памяти.

)соединены с i-м выходом дешифратора, вторые входы первого и второго элементов ИЛИ всех групп соединены соответственно с первым и вторым выходами блока управления, вход дешифратора соединен с выходами регистра адреса, выходы первого и второго элементов ИЛИ всех групп соединены с группой выходов выборки модулей памяти устройства, отличающееся тем, что оно дополнительно снабжено k (k = 1, 2, ...) m-разрядными регистрами адреса, информационные входы которых соединены с одноименными входами устройства, служащими для подключения шин адреса-данных магистрали "Общая шина", управляющие входы 2 ÷ (k + 1)-х регистров адреса подсоединены к входам устройства для подключения одноименных шин синхронизации записи адреса магистрали, (l + 1) ÷ [m(k+1)-1] , (где l = 1, 2, ..., m(k + 1) - 2) выходы регистров адреса подключены соответственно к 1 ÷ [m(k+1)-(l-1)] входам дешифратора, остальные 1 ÷ l выходы регистров адреса служат выходами устройства для подключения адресных входов памяти.

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1345203A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1991-07-09—Подача