версным входом первого элемента И, первым входом переключателя и выходо второго элемента И, первый вход которого соединен с выходом элемента задержки, вход которого соединен со счетным входом второго триггера и первым входом уп равления группы управляющих входов/выходом блрка, первый выход управления которой соединен с выходом переключателя, второй вход которого соединей с выходом первого триггера, вход элемента НЕ соединен с управляющим входом.блока,информационШ)1м входом второго триггера и инверснь входом сброса второго триггера, выход которого соединен с инверсным входом второго элемента И и вторым управляющим выходом блока, выход элемента НЕ соединен с вторым инверсным входом первого элемента И и вторым входом/выходом управления

группы управляющих входов/выходов блока.

3. Устройство по п. 1, отличающееся тем, что блок связи с магистралью общего памяти содержит m каналов, каждый из которых содержи элемент И-НЕ и Элемент НЕ, вход которого соединен с выходом элемента И-НЕ и с соответствующим входом/выходом второй группы адресных, информационных и управляющих входов/выходов блока, вынод элемента НЕ соединен с соответствующим выходом перво группы адресных, управляющих и информационных входов/выходов блока, первый вход элемента И-НЕ соединен с соответствующим входом первой группы адресных, управляющих и информационных входов/выходов блока, вторые входы элементов И-НЕ каждого канала объединены и подключены к управляющему входу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОДКЛЮЧЕНИЕМ .К МАГИСТРАЛИ ОБЩЕГО БЛОКА ПАМЯТИ, содержащее N каналов, причем каждый канал содержит коммутатор адреса, дешифратор адреса, блок связи с каналом ввода/вывода, блок управления направлением передачи, первый управляющий выход которого соединен с управляющим входом блока связи с каналом ввода/вывода, первые группы информационных, адресных и управляющих входов/выходов которого являются соответственно первой группой информационных, адресных и управляющих входов/выходов устройства, вторая группа управляющих и информационных входов/выходов блока связи с каналом ввода/вывода соеДинена с входом блока управления направлением передачи, выход коммутатора адреса соединен с управляющим входом дешифратора адреса, информационный вход которого соединен с адресным выходом блока связи с каналом ввода/вывбда отличающ ее с я тем, что, с целью повышения производительности, в каждый канал введены блок задания адреса. блок арбитража, блок связи с магистралью общего блока памяти, а также общая для всех каналов магистраль, общего блока памяти, причем адресный выход блока связи с каналом ввода/вывода соединен с входом блока задания адреса, выход которого соединен с адресным входом блока связи с магистралью общего блока памяти, первые управляющие и информационные входы/ вькоды которого соединены с вторыми управляющими и информационными входами/выходами блока связи с каналом ввода/вывода, выход дещифратора соединен с управлякицим входом блока арбитража, выход которого соединен с вторым управляющим входом блока управления направлением передачи, второй управляющий выход котрро.гр соединен с управляющим входом блока связи, с магистралью общего блока памяти, вторые информационные, управляющие и адресные входы/выходы блоков :о связи с магистралью общего блока пасо мяти всех каналов соединены соответ4 ственно и подключены к магистрали 00 СО 4 общего блока памяти, которая является второй группой информационных, управляющих и адресных выходов устройства, группы управляющих входов/вы;ходов блоков арбитража каждого канала соединены между собойо - , 2, Устройство по п. 1, отли.чающееся тем, что блок арбитража содержит элемент НЕ, элемент задержки, переключатель, два триггера, два элемента И, причем выход первого элемента И соединен со счетным входом первого триггера, вход сброса которого соединен с первым ни

Изобретение относится к области вычислительной техники, в частности к вопросу управления доступом к обще му блоку памяти. Известна вычислительная система l Содержащая две независимо работающих ЭВМ, включающих центральный процессор, оперативное запомингиощее устройство, набор периферийных устройст объединенных с помощью указанного выше устройства, содержащего блоки связи с каналш-ш ввода/вывода (типа общей шины) каждой ЭВМ, дешифраторы адреса, ког«с утаторы адреса, блоки захвата шин и прерывания, блоки адресуемых регистров, блок управления направлением передачи данных. Однако известная система обладает следующими недостатками. Пропускная способность канала общего поля памяти резко ограничивается пропускной способностью системных магистралей каждой взаимодействующей ЭВМ. При этом существуют жесткие ограничения на использование каналов прямого доступа в каждой ЭВМ, так как время работы канала прямого доступа исключается возможность обращения к общему полю памяти со стороны другой ЭВМ. Кроме того, при объединении более двух-трех-ЭВМ в систему с общим полэм памяти возникают трудности принципиального характера, связанные с дисциплиной обслуживания запросов к общему полю памяти от различных ЭВМ. Чтобы обеспечить работоспособность такой системы, необходимо жестко ограничить интенсивность об- . ращений к общему полю памяти от каждой ЭВМ, кроме того, одна из ЭВМ в таких системах выделяется для обслуживания запросов других ЭВМ. Это приводит к существенному удорсшанию таких систем и снижению их эффективности. Ближайшим к изобретению является вычислительная система 2 . Эта система содержит две назависимо работающих ЭВМ, каждая из которых содержит процессор, оперативное запоминающее устройство, периферийные устройства, взаимодействующие по общему каналу, а также блоки связи с каждым каналом, дешифраторы адреса, коммутаторы адреса, блок управления направлением передачи, блоки адресуемых регист3ров, блоки захвата каналов каждой ЭВМ,линии передачи данных между каналами. При обращении по адресам общего поля памяти от одной ЭВМ выполняется операция захвата канала , другой ЭВМ и после зтого проводится передача слова данных между общей памятью и запрашивающей ЭВМ. Указанная система обладает всеми перечисленными вьщ1е недостатками. Цель изобретения - повышение про изводительности. Цель достигается тем, что в устройство для управления подключением к магистрали общего блока памяти, со держащее N каналов, причем каждый канал содержит коммутатор адреса, дешифраторадреса, блок связи с каналом ввода/вывода, блок управления направлением передачи, первый управляющий вькод которого соединен с управляющим входом блока- связи с каналом ввода/вывода, первые группы информационных, адресных и управляющих входов/выходов которого являются соответственно первой группой информационных, адресных и управляющих входов/выходов устройства, вторая группа управляющих и информационных входов/выходов блока связи с каналом ввода/вывода соединена с входом блока управления направлением передачи вькод коммутатора адреса соединен с управляющим входом дешифратора адрес информационный вход которого соединен с адресным выходом блока связи с каналом ввода/вывода, в каждый канал введены блок задания адреса, блок арбитража, блок связи с магистралью общего блока памяти, а также общая дпя всех каналов магистраль общего блока памяти, причем адресный выход блока связи с каналом ввода/вывода соединен с входом блока задания адреса, выход которого.соединен с адресным входом блока связи с магистралью общего блока памяти, первые управляющие и информационные входы/выходы которого соединены со вторь 1и управляющими и информационны

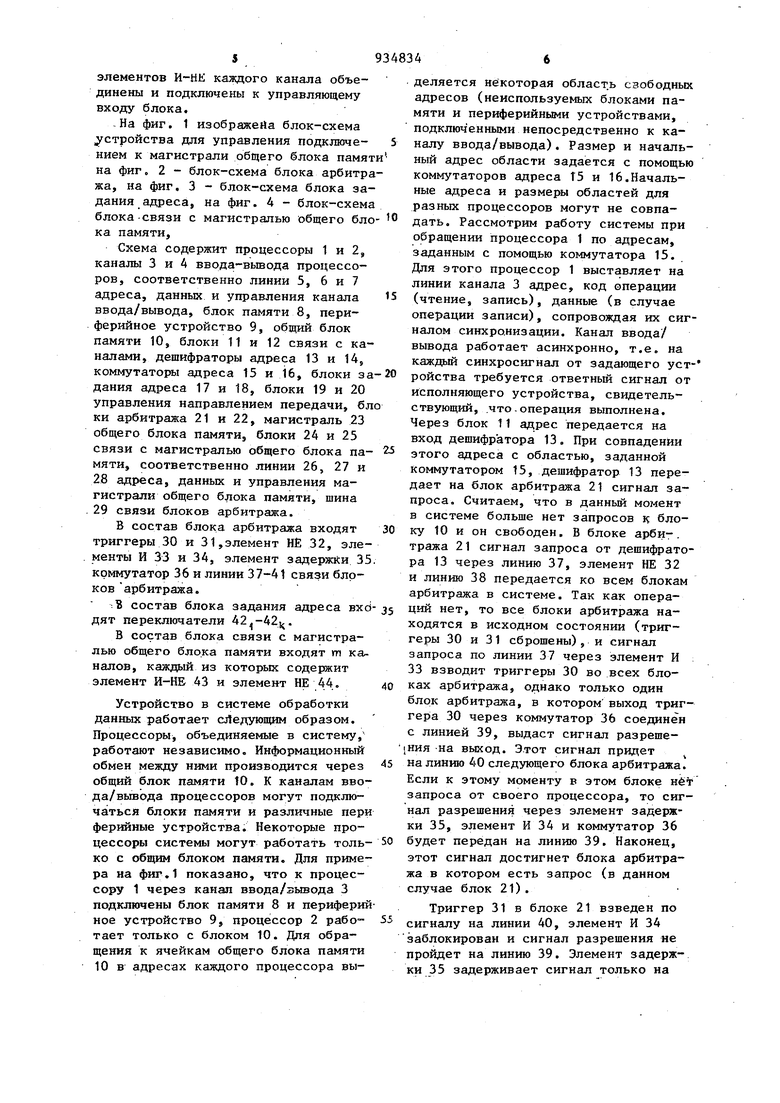

ми входами/выходами блока связи с каналом ввода/вывода j выход дешифратора соединен с управляющим входом блока арбитража, выход которого соединен со вторым управляющим входом блока 55 управления направлением передачи, второй управляющий выход которого соединен с управлякицим входом блока свявьосод элемента НЕ соединен с соответствующим выходом первой группы адресных, управляющих и информационньк входов/выходов блока, первый вход элемента И-НЕ соединен с соответствующим входом первой группы адресных, управляющих и информационньк входов/выходов блока, вторые входы 4 с магистралью общего блока памя, вторые информационные, управляющие и адресные входы/выходы блоков связи с магистралью общего блока памяти всех каналов соединены соответственно и подключены к магистрали общего блока памяти, которая является второй группой информационных, управляющих и адресных выходов устроисТВа, группы управляющих входов/выходов блоков арбитража каждого канала соединены между собой. Цель достигается также тем, что блок арбитража содержит элемент НЕ, элемент задержки, переключатель, два триггера, два элемента И, выход первого элемента И соединен со счетным входом первого триггера, вход сброса которого соединен с первым инверсным входом первого элемента И,первым входом переключателя и выходом второго элемента И,первый вход которого соединен с выходом элемента задержки, вход которого соединен со счетным входом второго триггера и первым входом управления группы управляющих входов/выходов блока, первый выход управления которой соединен с выходом переключателя, второй вход которого соединен с выходом первого триггера, вход элемента НЕ соединен с управляющим входом блока, информационным входом второго триггера и инверсным входом сброса второго триггера, выход которого соединен с инверсным входом второго элемента И и вторым управляющим выходом блока, выход элемента НЕ соединен с вторым инверсным входом первого элемента И и вторым входом/ выходом управления группы управляющих входов/выходов блока. Цель достигается также тем, что блок связи с магистралью общего блока памяти содержит rti каналов, каждый из которых содержит элемент И-НЕ и элемент НЕ, вход которого соединен с выходом элемента И-НЕ и с соответствующим входом/выходом второй группы адресных, информационньк и управляющих входов/выходов блока. элементов И-НЕ каждого канала объединены и подключены к управляющему входу блока. -На фиг. 1 изображала блок-схема устройства для управления подключением к магистрали общего блока памят на фиг. 2 - блок-схема блока арбитра жа, на фиг. 3 - блок-схема блока задания адреса, на фиг. 4 - блок-схема блока-связи с магистралью общего бло ка памяти. Схема содержит процессоры 1 и 2, каналы 3 и 4 ввода-вьшода процессоров, соответственно линии 5, 6 и 7 адреса, данных и управления канала ввода/вывода, блок памяти 8, периферийное устройство 9, общий блок памяти 10, блоки 11 и 12 связи с каналами, дешифраторы адреса 13 и 14, коммутаторы адреса 15 и 16, блоки за Дания адреса 17 и 18, блоки 19 и 20 управления направлением передачи, бл ки арбитража 21 и 22, магистраль 23 общего блока памяти, блоки 24 и 25 связи с магистралью общего блока памяти, соответственно линии 26, 27 и 28 адреса, данных и управления магистрали общего блока памяти, шина . 29 связи блоков арбитража. В состав блока арбитража входят триггеры 30 и 31,элемент НЕ 32, эле. менты И 33 и 34, элемент задержйи 35 коммутатор 36 и линии 37-41 связи блоков арбитража. ;В состав блока задания адреса Bxd дят переключатели . В состав блока связи с магистралью общего блока памяти входят т каналов, каждый из которых содержит элемент И-НЕ 43 и элемент НЕ 44. Устройство в системе обработки данных работает следующим образом. Процессоры, объединяемые в систему, работают независимо. Информационный обмен между ними производится через общий блок памяти 10. К каналам ввода/вывода процессоров могут подключаться блоки памяти и различные пери ферийные устройства. Некоторые процессоры системы могут работать только с общим блоком памяти. Для примера на фиг.1 показано, что к процессору 1 через канал ввода/вывода 3 подключены блок памяти 8 и периферий ное устройство 9, процессор 2 работает только с блоком 10. Для обращения к ячейкам общего блока памяти 10 в адресах каждого процессора вызаблокирован и сигнал разрешения не пройдет на линию 39. Элемент задержки 35 задерживает сигнал только на деляется некоторая област.ь свободных адресов (неиспользуемых блоками памяти и периферийными устройствами, подключенными непосредственно к каналу ввода/вывода). Размер и начальный адрес области задается с помощью коммутаторов адреса Т5 и 16.Начальные адреса и размеры областей для разных процессоров могут не совпадать. Рассмотрим работу системы при обращении процессора 1 по адресам, заданным с помощью коммутатора 15. Для этого процессор 1 выставляет на линии канала 3 адрес, код операции (чтение, запись), данные (в случае операции записи), сопровождая их сигналом синхронизации. Канал ввода/ вывода работает асинхронно, т.е. на каждый синхросигнал от задающего уст- ройства требуется ответный сигнал от исполняющего устройства, свидетельствующий, .что-операция выполнена. Через блок 11 адрес передается на вход дешифратора 13. При совпадении этого адреса с областью, заданной коммутатором 15, дешифратор 13 передает на блок арбитража 21 сигнал запроса. Считаем, что в данный момент в системе больше нет запросов к блоку 10 и он свободен. В блоке арби-. тража 21 сигнал запроса от дешифратора 13 через линию 37, элемент НЕ 32 и линию 38 передается ко всем блокам арбитража в системе. Так как операций нет, то все блоки арбитража находятся в исходном состоянии (триггеры 30 и 31 сброшены), и сигнал запроса по линии 37 через элемент И 33 взводит триггеры 30 во всех блоках арбитража, однако только один блок арбитража, в котором выход триггера 30 через коммутатор 36 соединен с линией 39, выдаст сигнал разрешения-на выход. Этот сигнал придет на линию 40 следующего блока арбитража. Если к этому моменту в этом блоке нет запроса от своего процессора, то сигнал разрешения через элемент задержки 35, элемент И 34 и коммутатор 36 будет передан на линию 39. Наконец, этот сигнал достигнет блока арбитража в котором есть запрос (в данном случае блок 21). Триггер 31 в блоке 21 взведен по сигналу на линии 40, элемент И 34

время срабатывания триггера 31. Сигнал по линии 41 от триггера 31 запустит блок управления направлением -передачи 19. Этот блок открывает в блоке 24 передатчики адреса, кода операции, сигнала синхронизации, в блоке 11 - передатчик ответного сигнала синхронизации. Если выполняется операция записи, передатчики по линиям данных открьюаются в блоке 24, если чтения - в блоке 11. Таким образом, команда из канала 3 передается в магистраль 2.3 и поступает на блок 10. Адрес из блока 11 в магистраль 23 передается через блок 17 задания адреса, который осуществляет смещение адресов на фиксированное число. В частном случае адрес может передаваться без изменения. Выполнив операцию, блок 10 вырабатывает ответный сигнал синхронизации, который через блоки 24 и 11 передается в канал 3. Приняв его, процессор заканчивает операцию, снимая сигналы с линий. Дешифратор 13, снимает сигнал запроса с линии 37. При этом сбрасывается триггер 31, открываете элемент И 34, и сигнал разрешения передается на выход 39. В nepSoM блоке арбитра сигнал с элемента И 34 сбросит триггер 30, сигнал разрешения снимается. Снятие этого сигнала рас

пространяется по всему кольцу, в результате схемы всех блоков арбитров переходят в исходное состояние. Если в момент снятия сигнала с элементом И 34 в первом блоке арбитража на линии 38 будет сигнал запроса, то триггер 30 в нем снова взведен и на линию 39 выдан новый Сигнал разрешения. Описанным способом организуется кольцевой приоритет между процессорами при доступе к общему блоку памяти 10. Этим ограничивается максимальное время задержки во всех процессорах при любых интенсивностях запросов от них. Максимальное число процессоров, которое может быть объединено в системе, ограничено лишь допустимым временем задержки.

Организация в системе отдельной магистрали общего поля памяти позволяет максимально снизить взаимные задержки каждой ЭВМ при обращении к oCjщему полю памяти. Предлагаемое устройство не накладывает ограничений на монопольные передачи блоков данных по каналам ввода/вывода ЭВМ,

так как они не блокируют обращений

к общему полю памяти других процессоров.

23

Фиг.1

J7

J2

N

-

e

.

7:гч

D C R

Т Д

36

33

«/

Фаг.2

tt2.J

ФигЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3940743, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1985-02-07—Публикация

1980-03-31—Подача