Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей и выходных каскадов в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.).

В современной аналоговой микросхемотехнике находят широкое применение буферные усилители класса АВ на комплементарных n-p-n и p-n-p выходных транзисторах, в которых для улучшения линейности амплитудной характеристики вводится общая отрицательная обратная связь (ООС) [1-10]. В практических схемах ООС реализуется на двух входных комплементарных дифференциальных каскадах класса dual-input-stage [1-10].

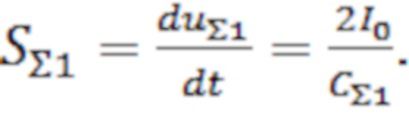

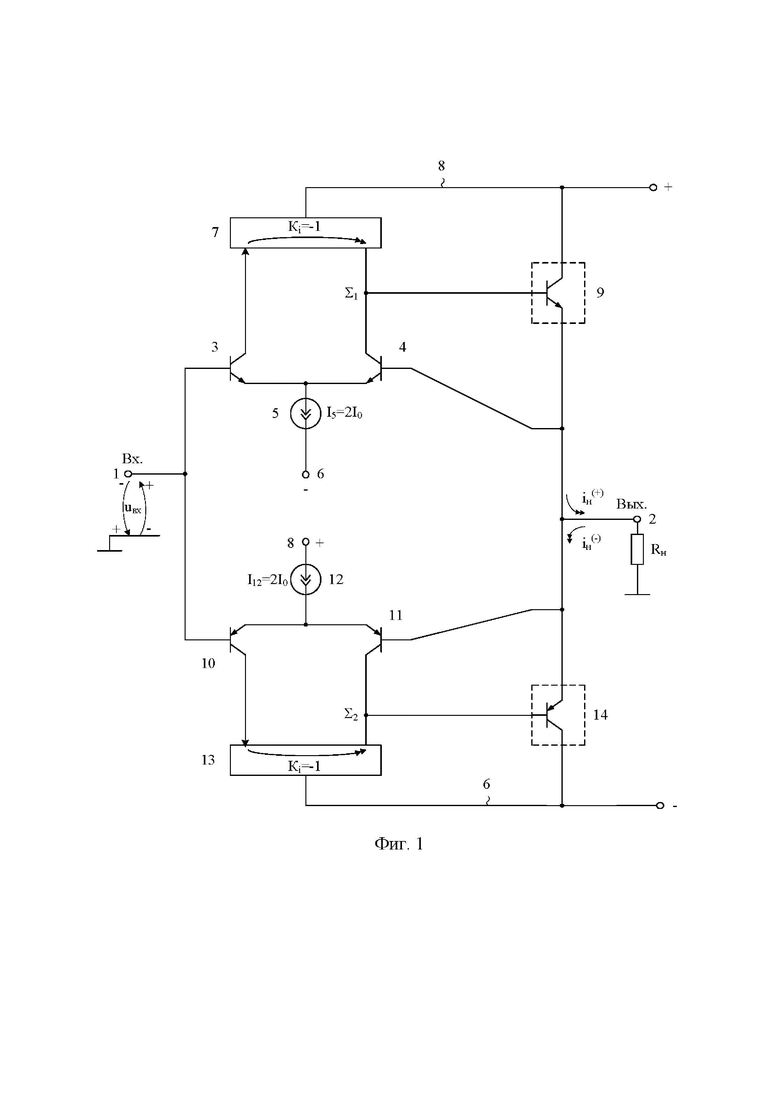

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1), представленный в патенте US 6724260, fig. 12, 2004 г. Схема БУ-прототипа фиг. 1 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания.

Существенный недостаток БУ-прототипа состоит в том, что он имеет сравнительно небольшие значения максимальной скорости нарастания выходного напряжения при больших импульсных изменениях входного сигнала. Это ограничивает области его применения, не позволяет применять данное схемотехническое решение в качестве выходных каскадов быстродействующих ОУ, драйверов линий связи и т.п.

Основная задача предполагаемого изобретения состоит в создании буферного усилителя с повышенными (на 1-2 порядка) значениями максимальной скорости нарастания выходного напряжения при малом статическом токопотреблении, не превышающем статическое токопотребление БУ-прототипа.

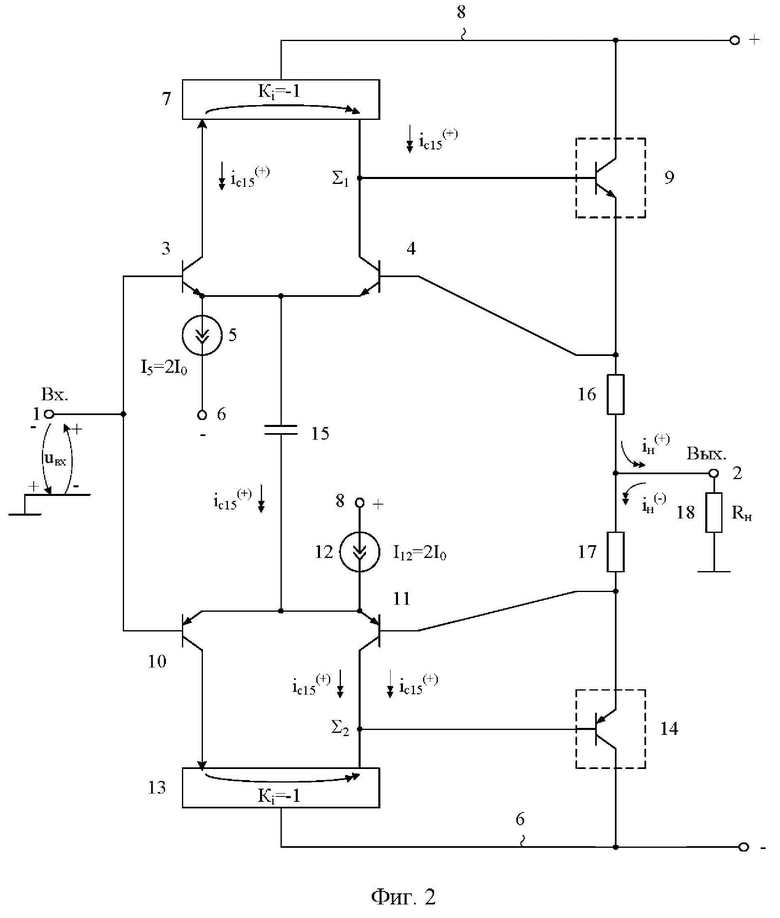

Поставленная задача решается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания, предусмотрены новые элементы и связи – объединенные эмиттеры первого 3 и второго 4 входных транзисторов связаны с объединенными эмиттерами третьего 10 и четвертого 11 входных транзисторов через дополнительный корректирующий конденсатор 15, эмиттер первого 9 выходного транзистора связан с выходом устройства 2 через первый 16 дополнительный резистор, а эмиттер второго 14 выходного транзистора связан с выходом устройства 2 через второй 17 дополнительный резистор.

На чертеже фиг. 1 представлена схема буферного усилителя-прототипа по патенту US 6724260, fig. 12, 2004 г.

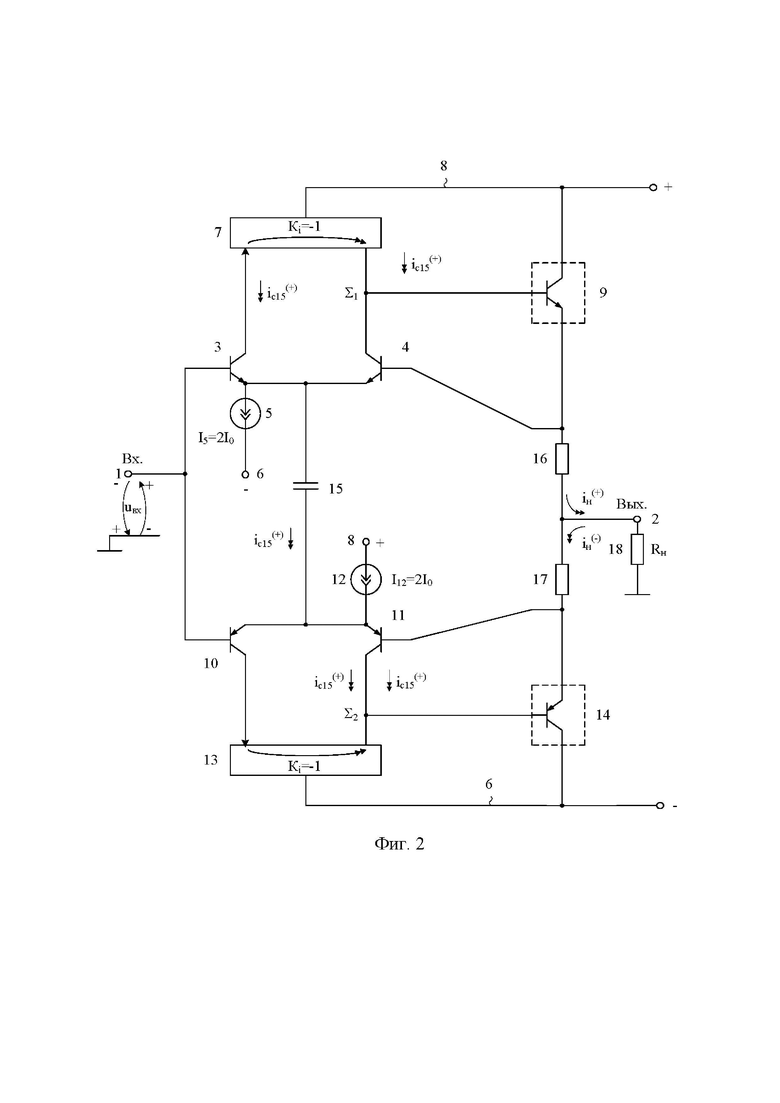

На чертеже фиг. 2 приведена схема заявляемого буферного усилителя в соответствии с формулой изобретения.

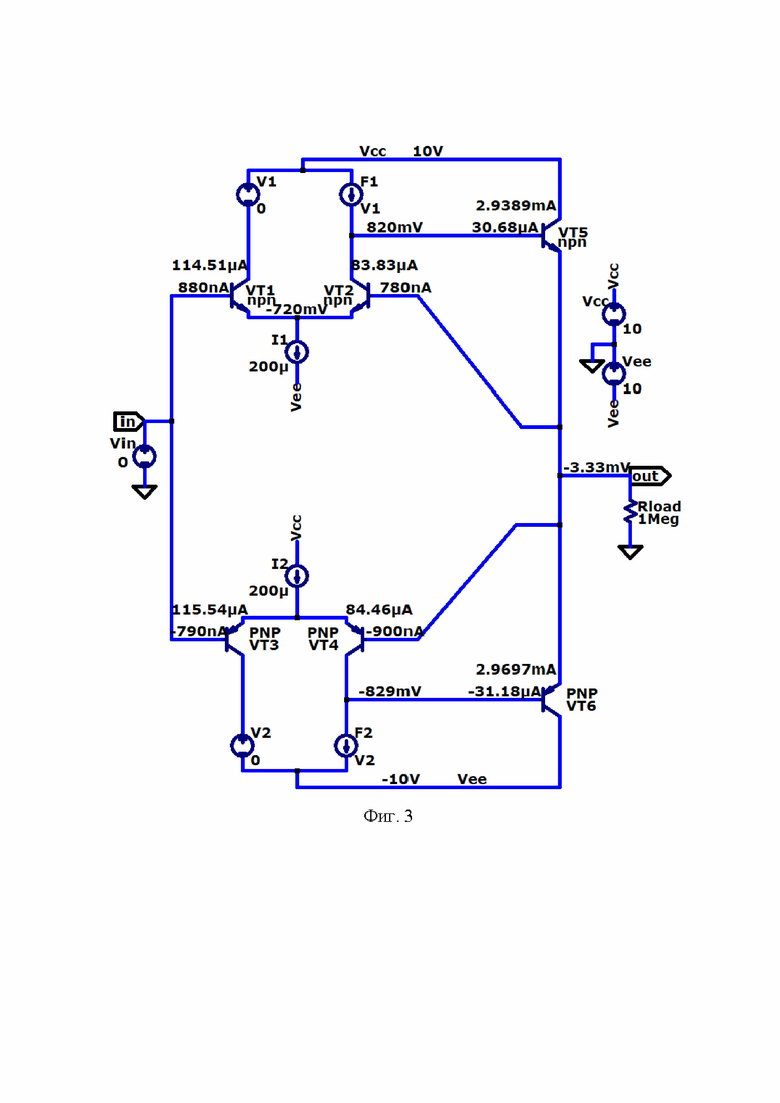

На чертеже фиг. 3 показана схема для моделирования БУ-прототипа фиг. 1 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА. При этом здесь и далее использовались компьютерные модели биполярных транзисторов базовых матричных кристаллов АО «Интеграл» (г. Минск).

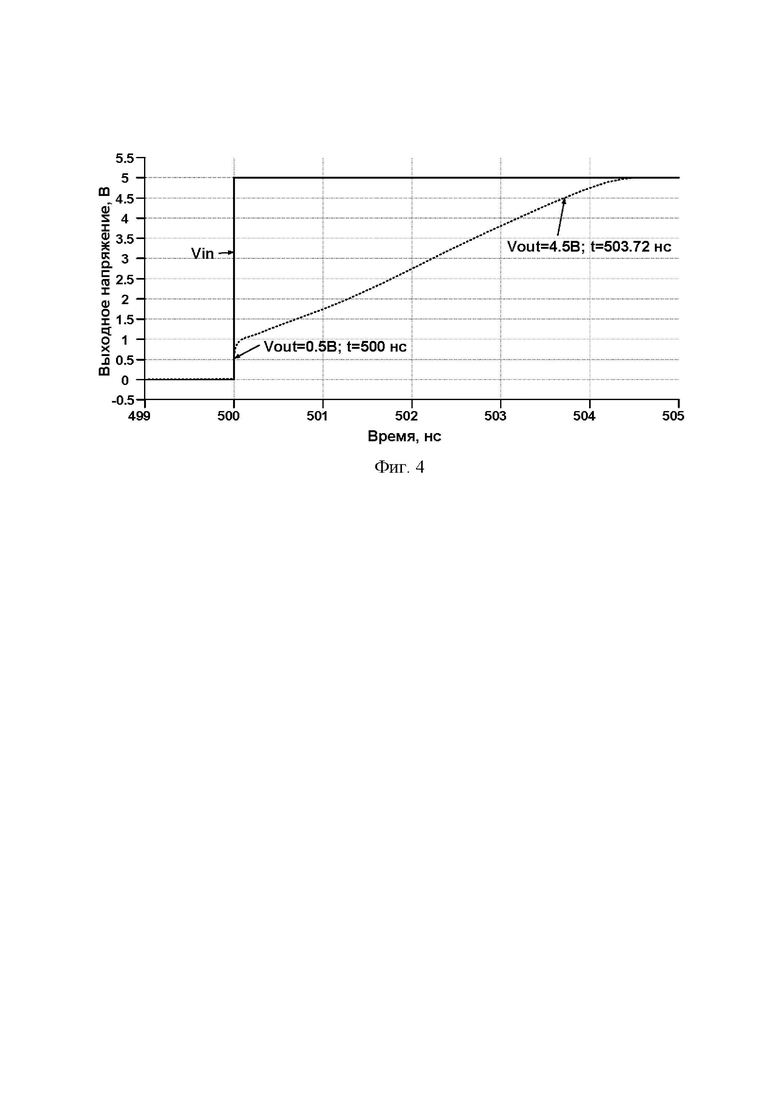

На чертеже фиг. 4 представлена переходная характеристика переднего фронта БУ-прототипа фиг. 3 в среде LTspice.

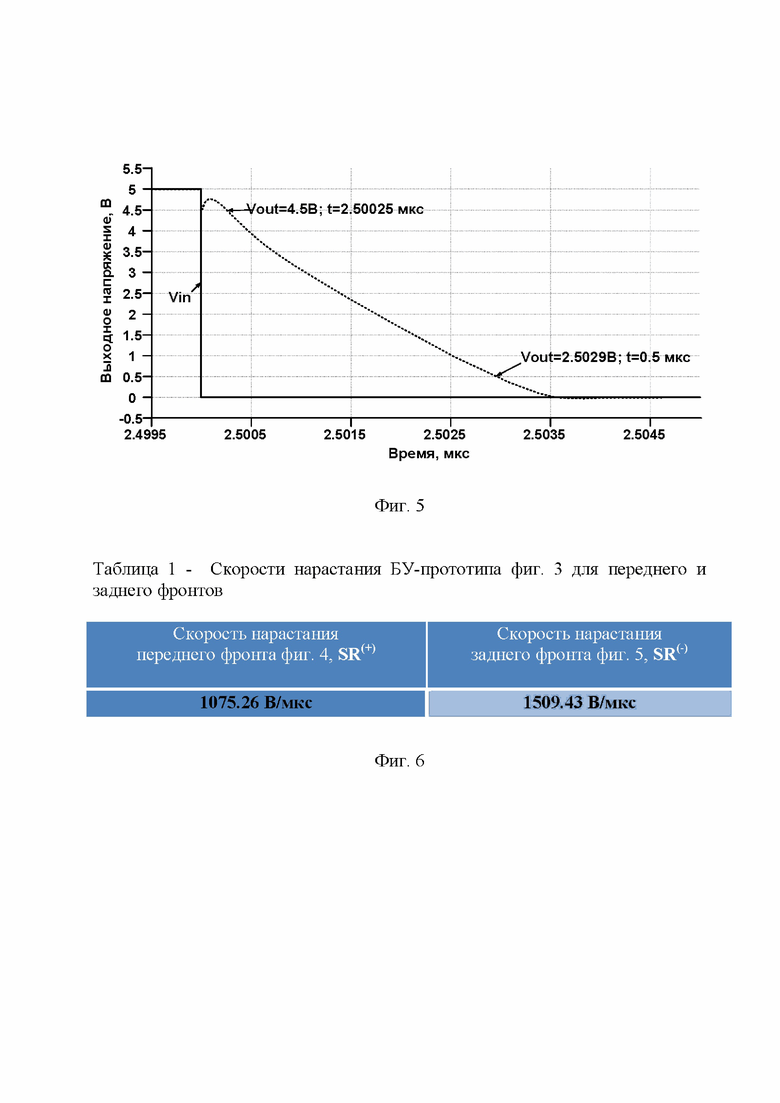

На чертеже фиг. 5 приведена переходная характеристика заднего фронта БУ-прототипа фиг. 3 в среде LTspice.

На чертеже фиг. 6 в таблице 1 показаны скорости нарастания выходного напряжения БУ-прототипа фиг. 3 для переднего и заднего фронтов.

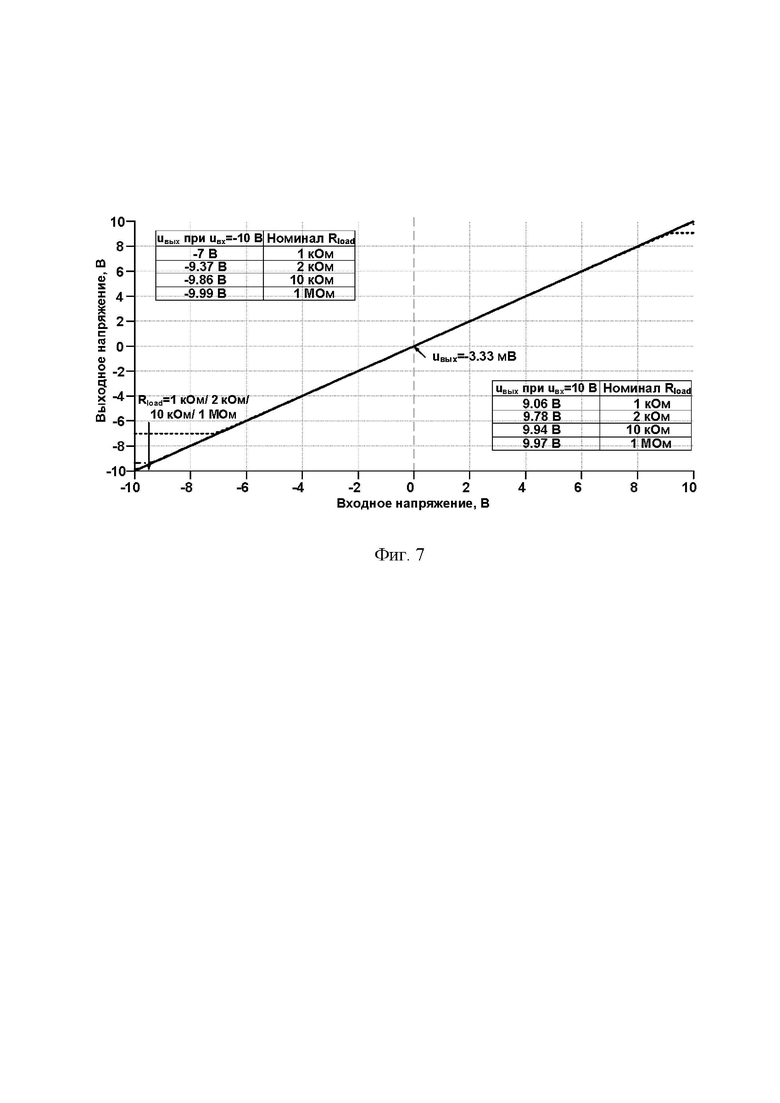

На чертеже фиг. 7 представлена амплитудная характеристика БУ-прототипа фиг. 3 в среде LTspice.

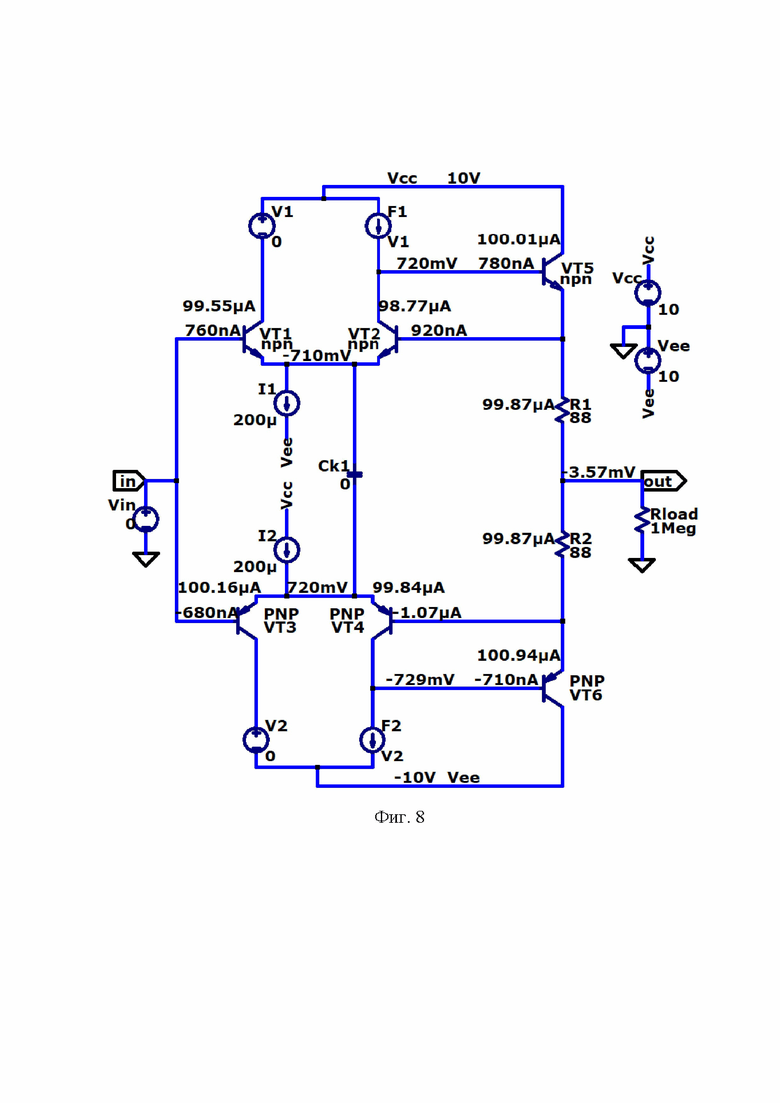

На чертеже фиг. 8 приведена схема для моделирования предлагаемого БУ фиг. 2 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, Rload=1 МОм, I1= I2=200 мкА, R1=R2=88 Ом, Ск1=0.

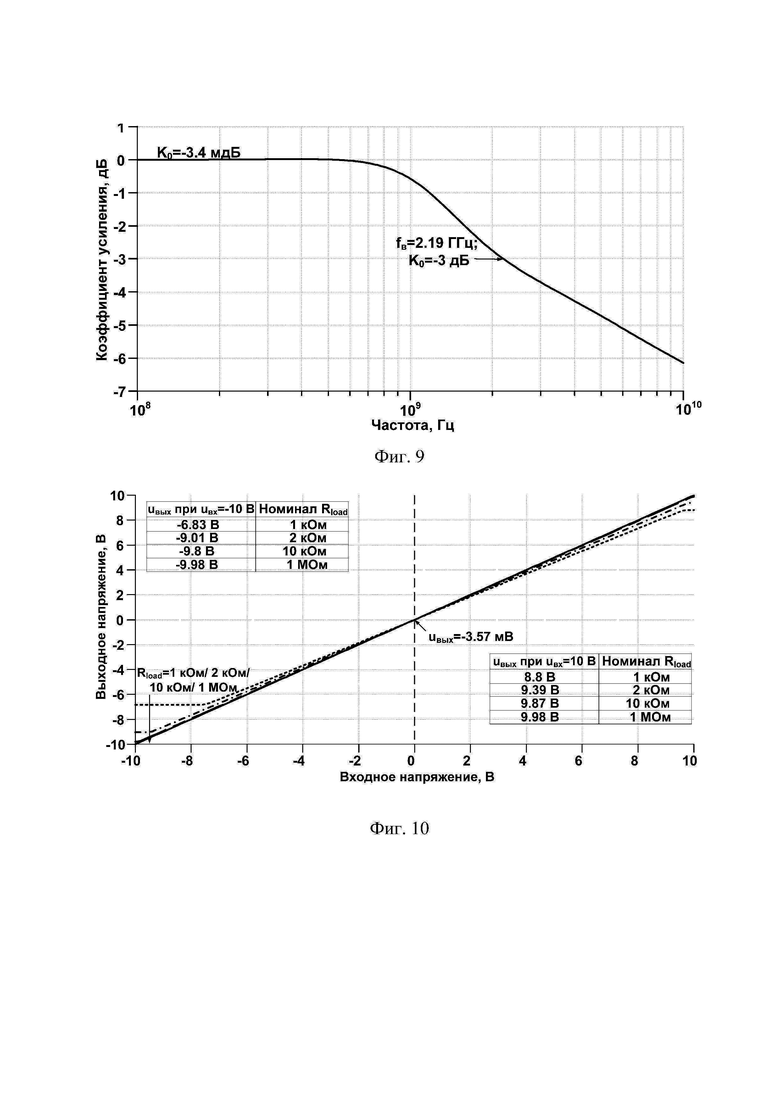

На чертеже фиг. 9 показана логарифмическая амплитудно-частотная характеристика (ЛАЧХ) коэффициента передачи по напряжению предлагаемого быстродействующего БУ фиг. 8 в среде LTspice.

На чертеже фиг. 10 представлена амплитудная характеристика предлагаемого быстродействующего БУ фиг. 8 в среде LTspice при Rload=1 кОм/ 2 кОм/ 10 кОм/1 МОм.

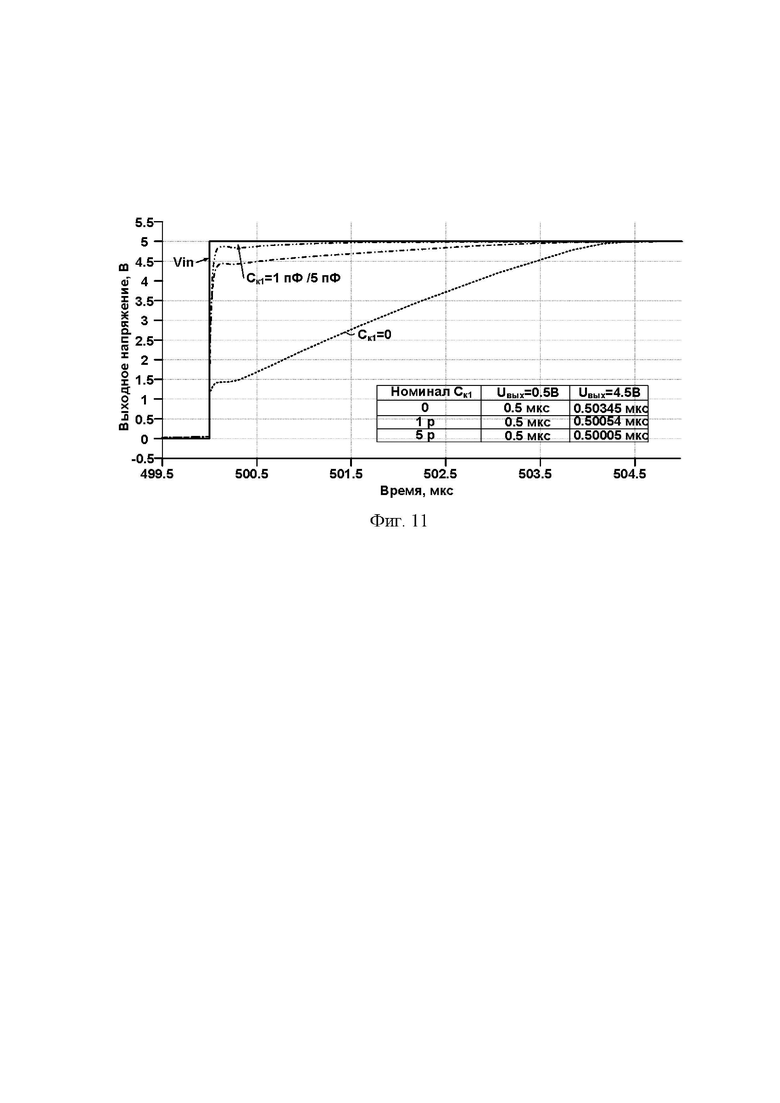

На чертеже фиг. 11 приведена переходная характеристика переднего фронта предлагаемого быстродействующего БУ фиг. 8 в среде LTspice при Ск1=0÷5 пФ.

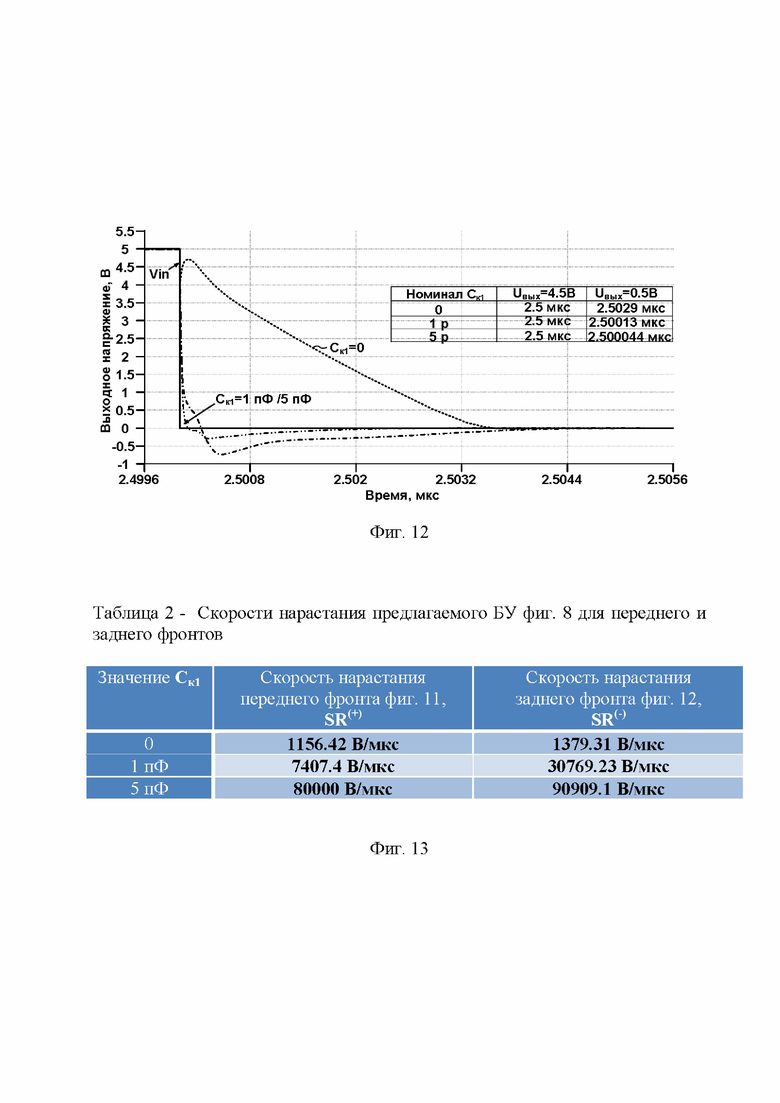

На чертеже фиг. 12 показана переходная характеристика заднего фронта предлагаемого быстродействующего БУ фиг.8 в среде LTspice при Ск1=0÷5 пФ.

На чертеже фиг. 13 в таблице 2 представлены скорости нарастания выходного напряжения предлагаемого БУ фиг. 8 для переднего и заднего фронтов.

Быстродействующий буферный усилитель класса АВ фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, общая эмиттерная цепь которых связана через первый 5 источник опорного тока с первой 6 шиной источника питания, первое 7 токовое зеркало, согласованное со второй 8 шиной источника питания, вход которого соединен с коллектором первого 3 входного транзистора, а выход связан с коллектором второго 4 входного транзистора и базой первого 9 выходного транзистора, база первого 3 входного транзистора соединена со входом 1 устройства, а база второго 4 входного транзистора соединена с эмиттером первого 9 выходного транзистора и связана с выходом устройства 2, третий 10 и четвертый 11 входные транзисторы, общая эмиттерная цепь которых соединена через второй 12 источник опорного тока со второй 8 шиной источника питания, второе 13 токовое зеркало, согласованное с первой 6 шиной источника питания, вход которого соединен с коллектором третьего 10 входного транзистора, а выход связан с коллектором четвертого 11 входного транзистора и базой второго 14 выходного транзистора, база третьего 10 входного транзистора подключена ко входу 1 устройства, а база четвертого 11 входного транзистора соединена с эмиттером второго 14 выходного транзистора и связана с выходом устройства 2, причем коллектор первого 9 выходного транзистора соединен со второй 8 шиной источника питания, а коллектор второго 14 выходного транзистора связан с первой 6 шиной источника питания. Объединенные эмиттеры первого 3 и второго 4 входных транзисторов связаны с объединенными эмиттерами третьего 10 и четвертого 11 входных транзисторов через дополнительный корректирующий конденсатор 15, эмиттер первого 9 выходного транзистора связан с выходом устройства 2 через первый 16 дополнительный резистор, а эмиттер второго 14 выходного транзистора связан с выходом устройства 2 через второй 17 дополнительный резистор. В схеме фиг. 2 резистор 18 моделирует свойства нагрузки.

Рассмотрим вначале работу БУ-прототипа фиг. 1.

При импульсном изменении входного напряжения положительной полярности первый 3 входной транзистор ОУ в схеме со 100% отрицательной обратной связью (ООС) практически мгновенно переключается и его эмиттерный и коллекторный токи становятся равным току первого 5 источника опорного тока I5=2I0, а второй 4 входной транзистор запирается по цепи эмиттера. Как следствие, суммарная емкость СΣ1 в высокоимпедансном узле Σ1 перезаряжается сравнительно малым током I5=2I0, а напряжение  имеет «пилообразную» форму с крутизной

имеет «пилообразную» форму с крутизной

(1)

(1)

Как следствие, напряжение в высокоимпедансном узле Σ1 ( ) передается (практически с единичным коэффициентом) через эмиттерный повторитель на первом 9 выходном транзисторе на выход 2 устройства. Поэтому максимальная скорость нарастания выходного напряжения БУ-прототипа также определяется формулой (1), из которой следует, что при фиксированных значениях

) передается (практически с единичным коэффициентом) через эмиттерный повторитель на первом 9 выходном транзисторе на выход 2 устройства. Поэтому максимальная скорость нарастания выходного напряжения БУ-прототипа также определяется формулой (1), из которой следует, что при фиксированных значениях  , которое определяется емкостью база-коллектор первого 9 выходного и первого 4 входного транзисторов, в схеме известного БУ для увеличения SR приходится существенно увеличивать ток I5=2I0. Это отрицательно сказывается на энергопотреблении БУ в статическом режиме. Об этом свидетельствуют графики переходных характеристик на чертежах фиг. 4 и фиг. 5, а также данные таблицы фиг. 6.

, которое определяется емкостью база-коллектор первого 9 выходного и первого 4 входного транзисторов, в схеме известного БУ для увеличения SR приходится существенно увеличивать ток I5=2I0. Это отрицательно сказывается на энергопотреблении БУ в статическом режиме. Об этом свидетельствуют графики переходных характеристик на чертежах фиг. 4 и фиг. 5, а также данные таблицы фиг. 6.

Введение первого 16 и второго 17 дополнительных резисторов позволяет, в случае необходимости, стабилизировать статические коллекторные токи первого 9 и второго 14 выходных транзисторов и уменьшить их значения с 2,9 мА до уровня менее 100 мкА. Об этом свидетельствует сравнение статических режимов схем БУ на чертежах фиг.3 и фиг.8.

Введение новых элементов и связей между ними в соответствии с формулой изобретения позволяет повысить максимальную скорость нарастания выходного напряжения БУ на 1-2 порядка без увеличения его статического токопотребления.

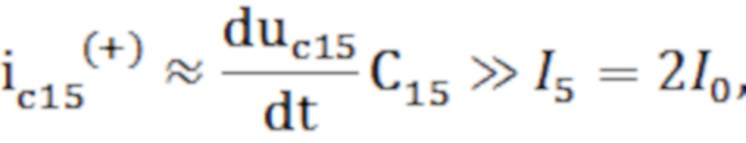

Действительно, при импульсном изменении входного напряжения положительной полярности uвх(+) импульсный коллекторный ток первого 3 входного транзистора не ограничивается уровнем I5=2I0 и определяется током iс15(+) через дополнительный корректирующий конденсатор 15:

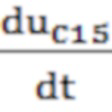

где  – производная напряжения на дополнительном корректирующем конденсаторе 15 на начальном этапе переходного процесса,

– производная напряжения на дополнительном корректирующем конденсаторе 15 на начальном этапе переходного процесса,

С15 – емкость дополнительного корректирующего конденсатора 15.

Как следствие, паразитная емкость СΣ1 в высокоимпедансном узле Σ1 перезаряжается сравнительно большим током iс15(+), что значительно повышает максимальную скорость нарастания напряжения на выходе 2 устройства. Об этом свидетельствуют графики переходного процесса на чертежах фиг. 11, а также данные таблицы 2 на чертеже фиг. 13, из которых следует, что SR увеличивается в 69 раз.

При больших отрицательных импульсных сигналах на входе 1 получаются аналогичные результаты, что отражено на графиках фиг. 12 и в таблице 2 на чертеже фиг. 13 – максимальная скорость нарастания улучшается более чем в 65 раз.

Амплитудная характеристика фиг. 10 предлагаемого БУ фиг.8 показывает, что рассматриваемая схема обеспечивает удовлетворительную работу при сравнительно низкоомных сопротивлениях нагрузки (Rload=1 кОм).

Таким образом, предлагаемый буферный усилитель имеет существенные преимущества в сравнении с БУ-прототипом по быстродействию.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.724.260, fig. 12, 2004 г.

2. Патент US 6.724.260 B2, fig. 12, 2004 г.

3. Патент US 5.291.149, fig. 3, 1994 г.

4. Патент US 6.268.769, fig. 3, 2001 г.

5. Патент US 4.636.743, fig. 1, 1987 г.

6. Патент US 4.783.637, fig. 1, 1988 г.

7. Патент US 5.225.791, fig. 2, 1993 г.

8. Патент US 5.512.859, fig. 1, 1996 г.

9. Патент US 3.968.451, fig. 7, 1976 г.

10. Патент SU 1220105, fig. 1, 1982 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ КЛАССА АВ | 2022 |

|

RU2790615C1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786191C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2023 |

|

RU2802051C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА n-p-n БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786630C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей. Технический результат: создание буферного усилителя с повышенными (на 1-2 порядка) значениями максимальной скорости нарастания выходного напряжения при малом статическом токопотреблении, не превышающем статическое токопотребление буферного усилителя-прототипа. Такой результат достигается тем, что в буферном усилителе объединенные эмиттеры первого (3) и второго (4) входных транзисторов связаны с объединенными эмиттерами третьего (10) и четвертого (11) входных транзисторов через дополнительный корректирующий конденсатор (15), эмиттер первого (9) выходного транзистора связан с выходом устройства (2) через первый (16) дополнительный резистор, а эмиттер второго (14) выходного транзистора связан с выходом устройства (2) через второй (17) дополнительный резистор. 13 ил.

Быстродействующий буферный усилитель класса АВ, содержащий вход (1) и выход (2) устройства, первый (3) и второй (4) входные транзисторы, общая эмиттерная цепь которых связана через первый (5) источник опорного тока с первой (6) шиной источника питания, первое (7) токовое зеркало, согласованное со второй (8) шиной источника питания, вход которого соединен с коллектором первого (3) входного транзистора, а выход связан с коллектором второго (4) входного транзистора и базой первого (9) выходного транзистора, база первого (3) входного транзистора соединена со входом (1) устройства, а база второго (4) входного транзистора соединена с эмиттером первого (9) выходного транзистора и связана с выходом устройства (2), третий (10) и четвертый (11) входные транзисторы, общая эмиттерная цепь которых соединена через второй (12) источник опорного тока со второй (8) шиной источника питания, второе (13) токовое зеркало, согласованное с первой (6) шиной источника питания, вход которого соединен с коллектором третьего (10) входного транзистора, а выход связан с коллектором четвертого (11) входного транзистора и базой второго (14) выходного транзистора, база третьего (10) входного транзистора подключена ко входу (1) устройства, а база четвертого (11) входного транзистора соединена с эмиттером второго (14) выходного транзистора и связана с выходом устройства (2), причем коллектор первого (9) выходного транзистора соединен со второй (8) шиной источника питания, а коллектор второго (14) выходного транзистора связан с первой (6) шиной источника питания, отличающийся тем, что объединенные эмиттеры первого (3) и второго (4) входных транзисторов связаны с объединенными эмиттерами третьего (10) и четвертого (11) входных транзисторов через дополнительный корректирующий конденсатор (15), эмиттер первого (9) выходного транзистора связан с выходом устройства (2) через первый (16) дополнительный резистор, а эмиттер второго (14) выходного транзистора связан с выходом устройства (2) через второй (17) дополнительный резистор.

| US 6724260 B2, 20.04.2004 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2674885C1 |

| ЛИНЕЙНЫЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2387074C1 |

| КАСКАД УСИЛИТЕЛЯ С РЕГУЛИРУЕМЫМ УСИЛЕНИЕМ, УСИЛИТЕЛЬ С РЕГУЛИРУЕМЫМ УСИЛЕНИЕМ, ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 1993 |

|

RU2140705C1 |

| US 10461706 B1, 29.10.2019 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2676014C1 |

| WO 2019213084 A1, 07.11.2019. | |||

Авторы

Даты

2023-02-28—Публикация

2022-12-09—Подача