Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение операционные усилители на биполярных [3-20] и полевых [21-24] транзисторах, выполненные на основе архитектуры двухтактного комплементарного «перегнутого» каскода. Их основные достоинства – расширенный частотный диапазон, а также эффективное использование напряжения питания. Однако, в данном классе известных ОУ [3-24] не решаются проблемы существенного повышения максимальной скорости нарастания выходного напряжения (SR).

Как показано в работах [25-27], быстродействие классических операционных усилителей с однополюсной частотной коррекцией с помощью одного интегрирующего конденсатора (Ск) определяется диапазоном активной работы входного каскада. Для увеличения максимальной скорости выходного напряжения (SR) ОУ с классической архитектурой, как правило, предусматриваются специальные цепи динамической коррекции переходного процесса, обеспечивающие в режиме перегрузки входного каскада ОУ большие уровни токов, перезаряжающих Ск. Это способствует существенному повышению SR [25-27]. Однако для рассматриваемого класса ОУ на основе двухтактных комплементарных «перегнутых» каскодов [3-24] такие цепи не разработаны. Данная задача решается в предлагаемом ниже схемотехническом решении.

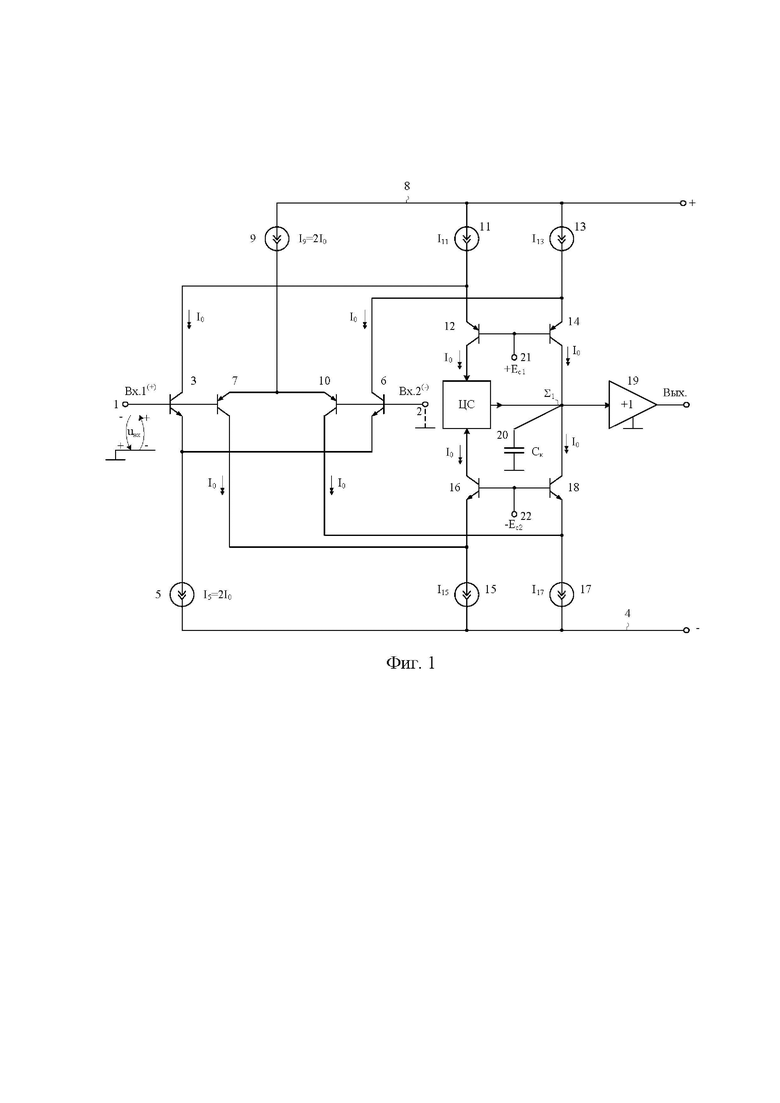

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, описанный в монографии «Прокопенко Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – С. 63, рис. 2.18». ОУ-прототип содержит (фиг.1) первый 1 и второй 2 входы устройства, первый 3 входной транзистор, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и соединен с эмиттером второго 6 входного транзистора, третий 7 входной транзистор, эмиттер которого связан со второй 8 шиной источника питания через второй 9 токостабилизирующий двухполюсник и соединен с эмиттером четвертого10 входного транзистора, базы первого 3 и третьего 7 входных транзисторов соединены с первым 1 входом устройства, базы второго 6 и четвертого 10 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 3 входного транзистора подключен ко второй 8 шине источника питания через третий 11 токостабилизирующий двухполюсник и связан с эмиттером первого 12 выходного транзистора, коллектор второго 6 входного транзистора связан со второй 8 шиной источника питания через четвертый 13 токостабилизирующий двухполюсник и подключен к эмиттеру второго 14 выходного транзистора, коллектор третьего 7 входного транзистора связан с первой 4 шиной источника питания через пятый 15 токостабилизирующий двухполюсник и соединен с эмиттером третьего 16 выходного транзистора, коллектор четвертого 10 входного транзистора связан с первой 4 шиной источника питания через шестой 17 токостабилизирующий двухполюсник и соединен с эмиттером четвертого 18 выходного транзистора, коллекторы второго 14 и четвертого 18 выходных транзисторов соединены со входом буферного усилителя 19 и корректирующим конденсатором 20, базы первого 12 и второго 14 выходных транзисторов соединены с первым 21 источником напряжения смещения, а базы третьего 16 и четвертого 18 выходных транзисторов связаны со вторым 22 источником напряжения смещения.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что в режиме динамической перегрузки входного каскада на первом 3 и втором 6 входных транзисторах или третьем 7 и четвертом 10 входных транзисторах максимальный выходной ток «перегнутого» каскода жестко связан с токами четвертого 13 и шестого 17 токостабилизирующих двухполюсников. Это не позволяет при ограничениях на статическое токопотребление ОУ осуществить быстрый перезаряд интегрирующего корректирующего конденсатора 20 (Ск=С20), обеспечивающего устойчивость схемы, что ограничивает максимальную скорость нарастания выходного напряжения в ОУ данного класса [25-27].

Основная задача предполагаемого изобретения состоит в обеспечении во время фронта переходного процесса более высоких уровней выходного тока двухтактного комплементарного «перегнутого» каскода (Iвых.max), перезаряжающего интегрирующий корректирующий конденсатор ОУ 20 (Ск=С20). В конечном итоге это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса [25-27].

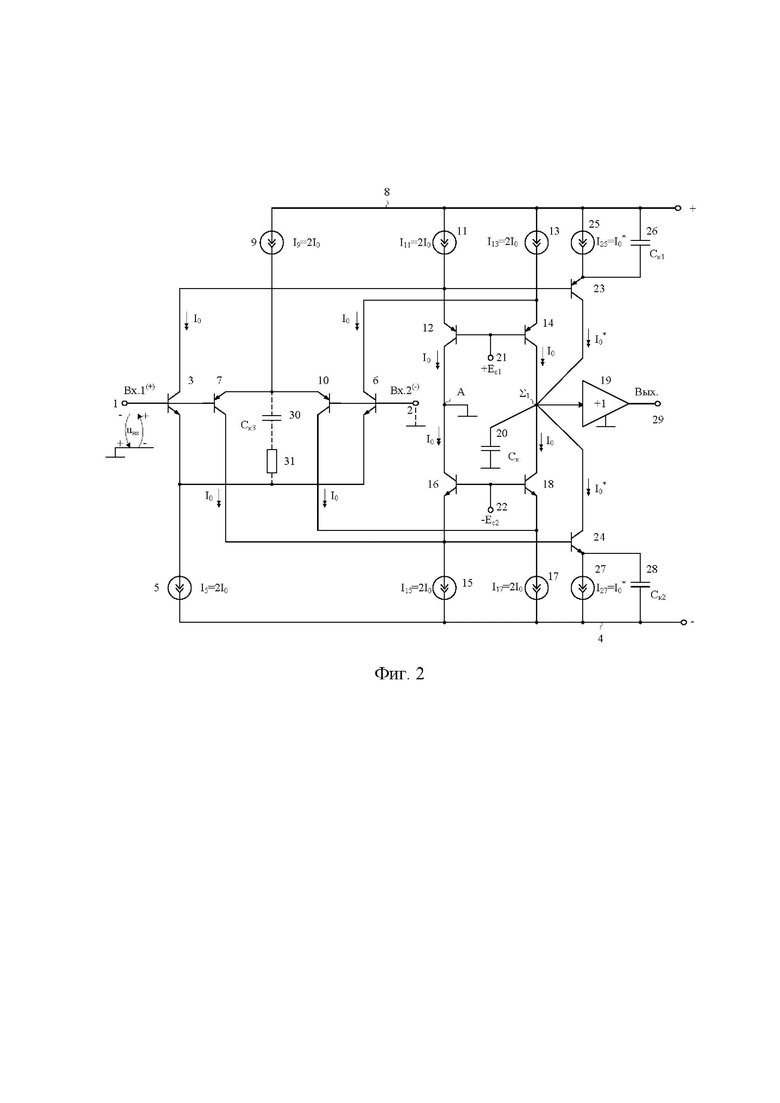

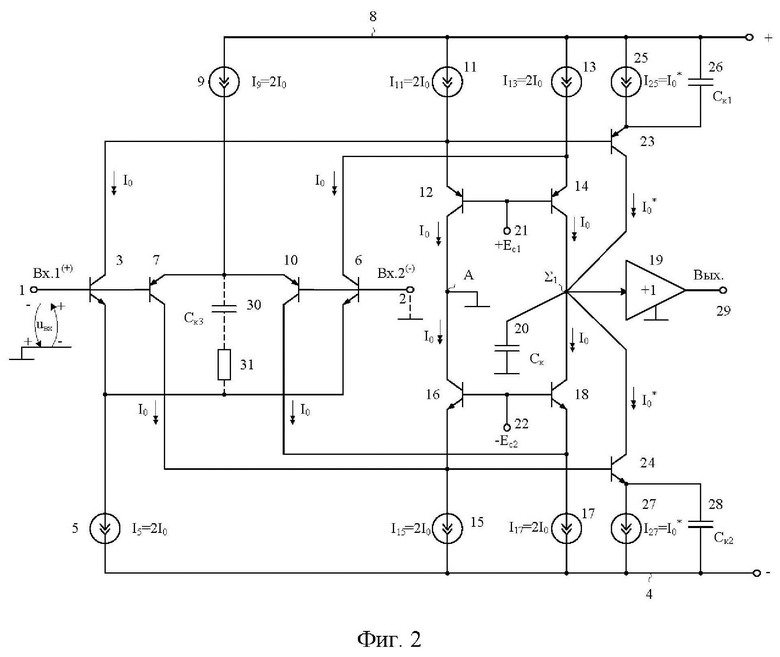

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной транзистор, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и соединен с эмиттером второго 6 входного транзистора, третий 7 входной транзистор, эмиттер которого связан со второй 8 шиной источника питания через второй 9 токостабилизирующий двухполюсник и соединен с эмиттером четвертого10 входного транзистора, базы первого 3 и третьего 7 входных транзисторов соединены с первым 1 входом устройства, базы второго 6 и четвертого 10 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 3 входного транзистора подключен ко второй 8 шине источника питания через третий 11 токостабилизирующий двухполюсник и связан с эмиттером первого 12 выходного транзистора, коллектор второго 6 входного транзистора связан со второй 8 шиной источника питания через четвертый 13 токостабилизирующий двухполюсник и подключен к эмиттеру второго 14 выходного транзистора, коллектор третьего 7 входного транзистора связан с первой 4 шиной источника питания через пятый 15 токостабилизирующий двухполюсник и соединен с эмиттером третьего 16 выходного транзистора, коллектор четвертого 10 входного транзистора связан с первой 4 шиной источника питания через шестой 17 токостабилизирующий двухполюсник и соединен с эмиттером четвертого 18 выходного транзистора, коллекторы второго 14 и четвертого 18 выходных транзисторов соединены со входом буферного усилителя 19 и корректирующим конденсатором 20, базы первого 12 и второго 14 выходных транзисторов соединены с первым 21 источником напряжения смещения, а базы третьего 16 и четвертого 18 выходных транзисторов связаны со вторым 22 источником напряжения смещения, предусмотрены новые элементы и связи – в схему введены первый 23 и второй 24 дополнительные транзисторы, эмиттер первого 23 дополнительного транзистора соединен со второй 8 шиной источника питания через параллельно-включенные первый 25 дополнительный токостабилизирующий двухполюсник и первый 26 дополнительный корректирующий конденсатор, база первого 23 дополнительного транзистора соединена с эмиттером первого 12 выходного транзистора, эмиттер второго 24 дополнительного транзистора связан с первой 4 шиной источника питания через параллельно-включенные второй 27 дополнительный токостабилизирующий двухполюсник и второй 28 дополнительный корректирующий конденсатор, причем база второго 24 дополнительного транзистора соединена с эмиттером третьего 16 выходного транзистора, коллекторы первого 23 и второго 24 дополнительных транзисторов связаны со входом буферного усилителя 19, а коллекторы первого 12 и третьего 16 выходных транзисторов соединены с общей шиной первого 4 и второго 8 источников питания.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа. В данной схеме цепь согласования (ЦС) обеспечивает передачу приращений коллекторных токов первого 12 и третьего 16 выходных транзисторов в высокоимпедансный узел Σ1.

На чертеже фиг. 2 показана схема заявляемого ОУ в соответствии с п.1 и п.2 формулы изобретения.

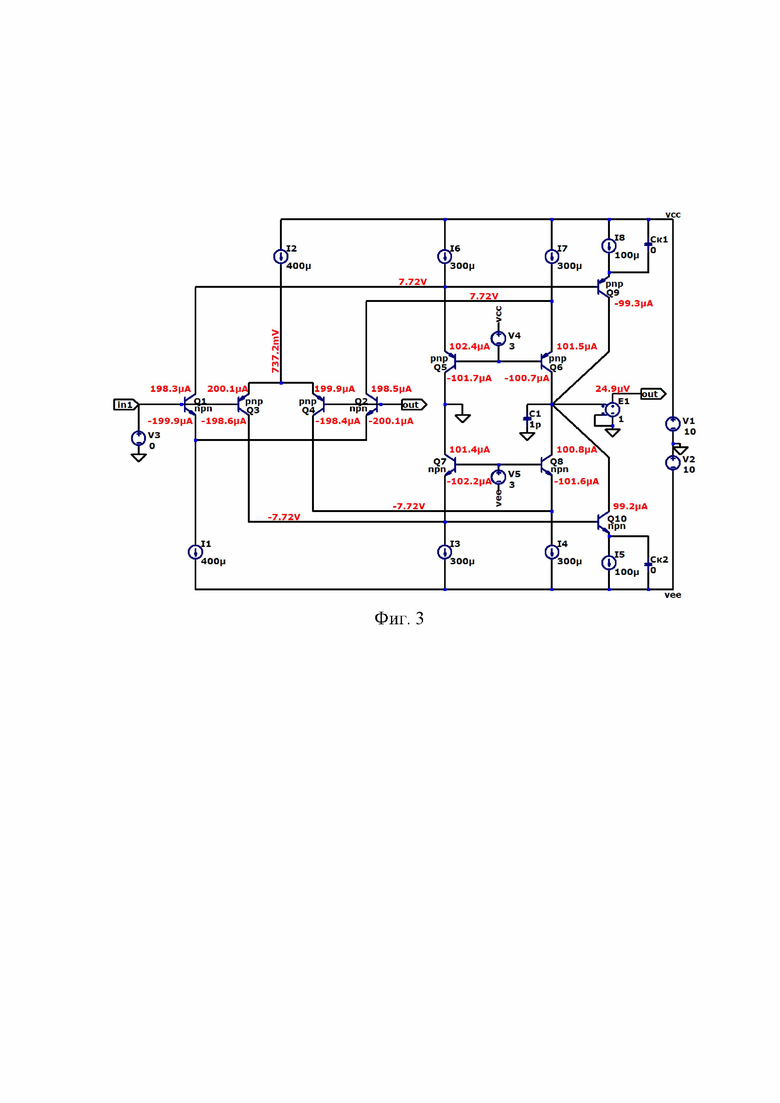

На чертеже фиг. 3 представлен статический режим заявляемого ОУ фиг. 2 в среде LTSpice на моделях транзисторов базового матричного кристалла MH2XA031_25.01.21 при 27°С, источниках опорного тока I1=I2=400мкА, I3=I4=I6=I7=300мкА, I5=I8=100мкА, корректирующем конденсаторе 20 (С1=Ск=С20=1пФ), дополнительных корректирующих конденсаторах 26 и 28 (Cк1=С26=Ск2=С28=0пФ), шинах питания V1=V2=±10В.

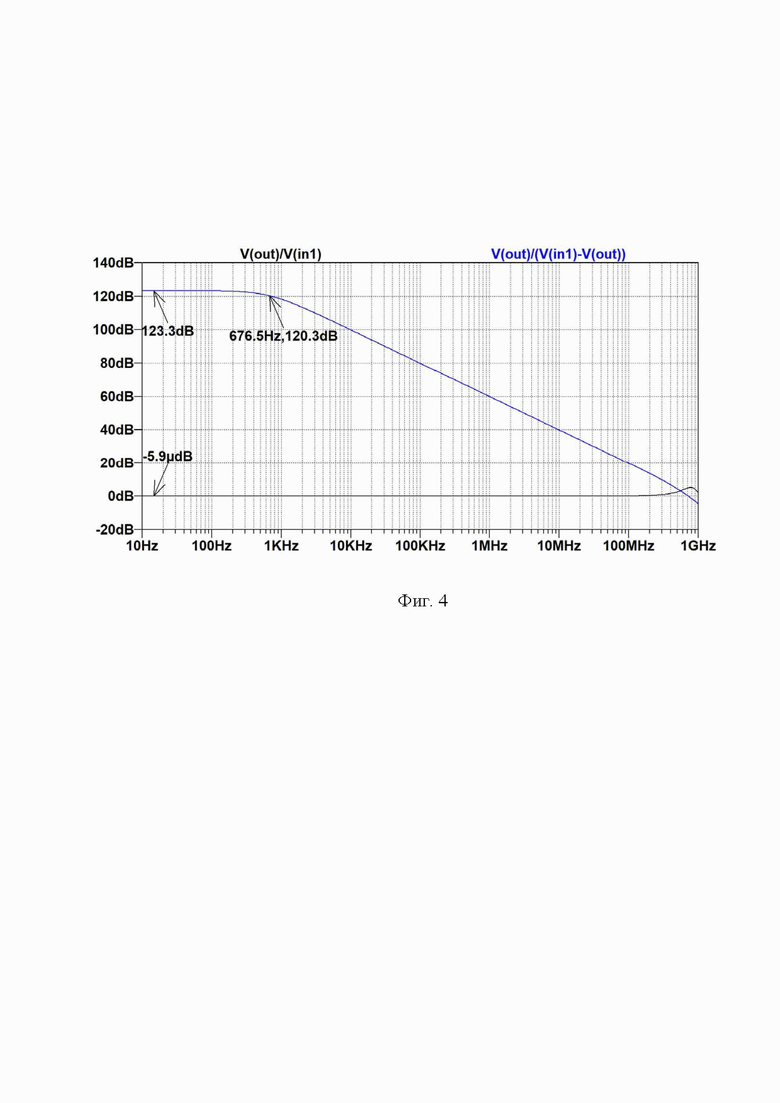

На чертеже фиг. 4 приведены логарифмические амплитудно-частотные характеристики (ЛАЧХ) ОУ на чертеже фиг. 3.

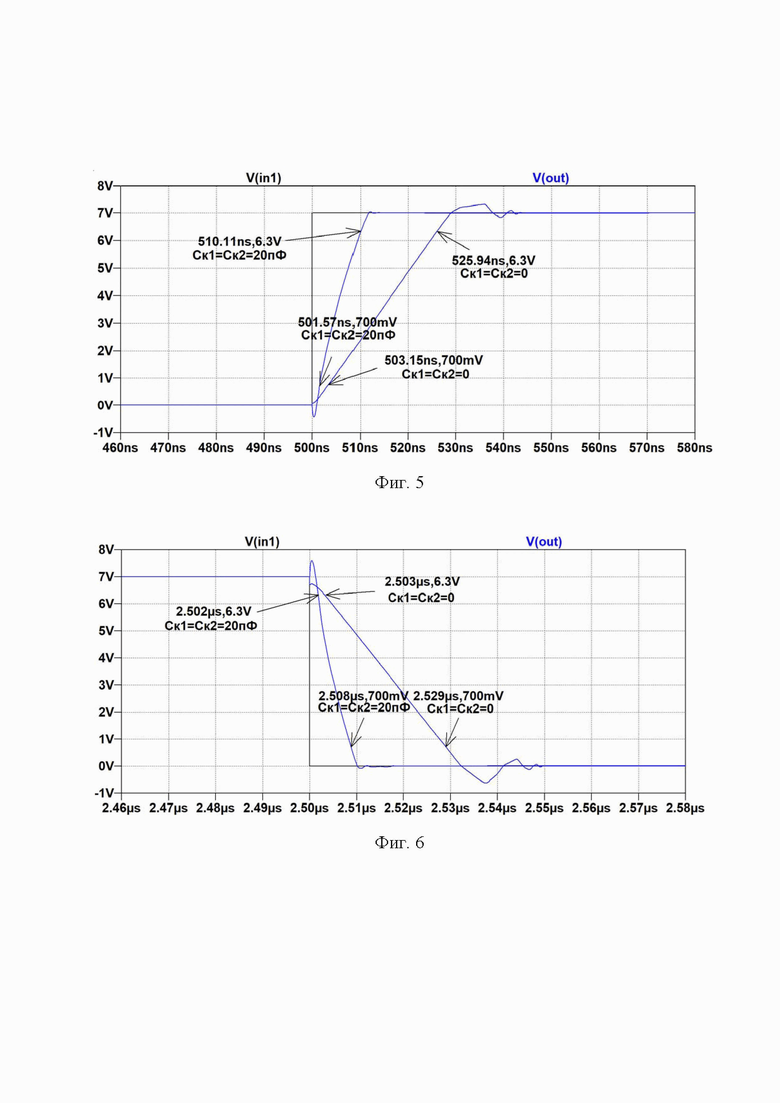

На чертеже фиг. 5 показан передний фронт переходного процесса в ОУ фиг. 3 по п. 1 формулы изобретения.

На чертеже фиг. 6 представлен задний фронт переходного процесса в ОУ фиг. 3 по п. 1 формулы изобретения.

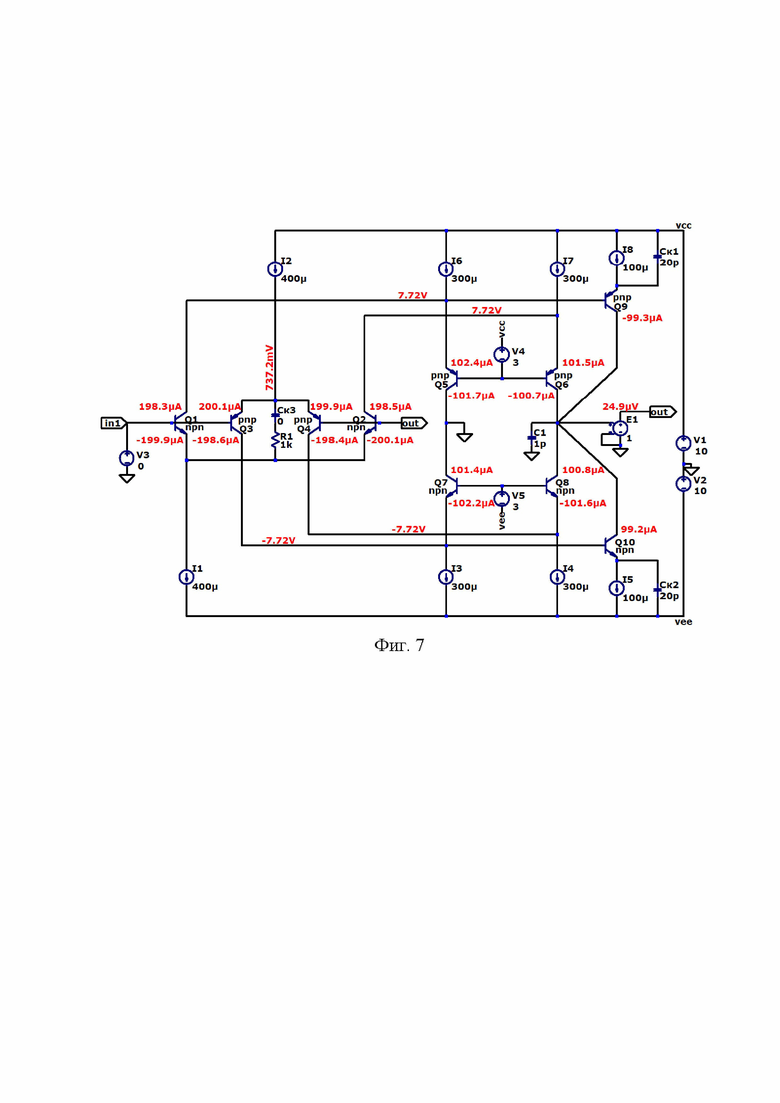

На чертеже фиг. 7 приведен статический режим ОУ фиг. 2 по п. 2 формулы изобретения в среде LTSpice на моделях транзисторов базового матричного кристалла MH2XA031_25.01.21 при 27°С, источниках опорного тока I1=I2=400мкА, I3=I4=I6=I7=300мкА, I5=I8=100мкА, корректирующем конденсаторе 20 (С1=Ск=С20=1пФ), дополнительных корректирующих конденсаторах 26, 28 и 30 (Cк1=С26=Ск2=С28=Ск3=С30=0пФ), шинах питания V1=V2=±10В.

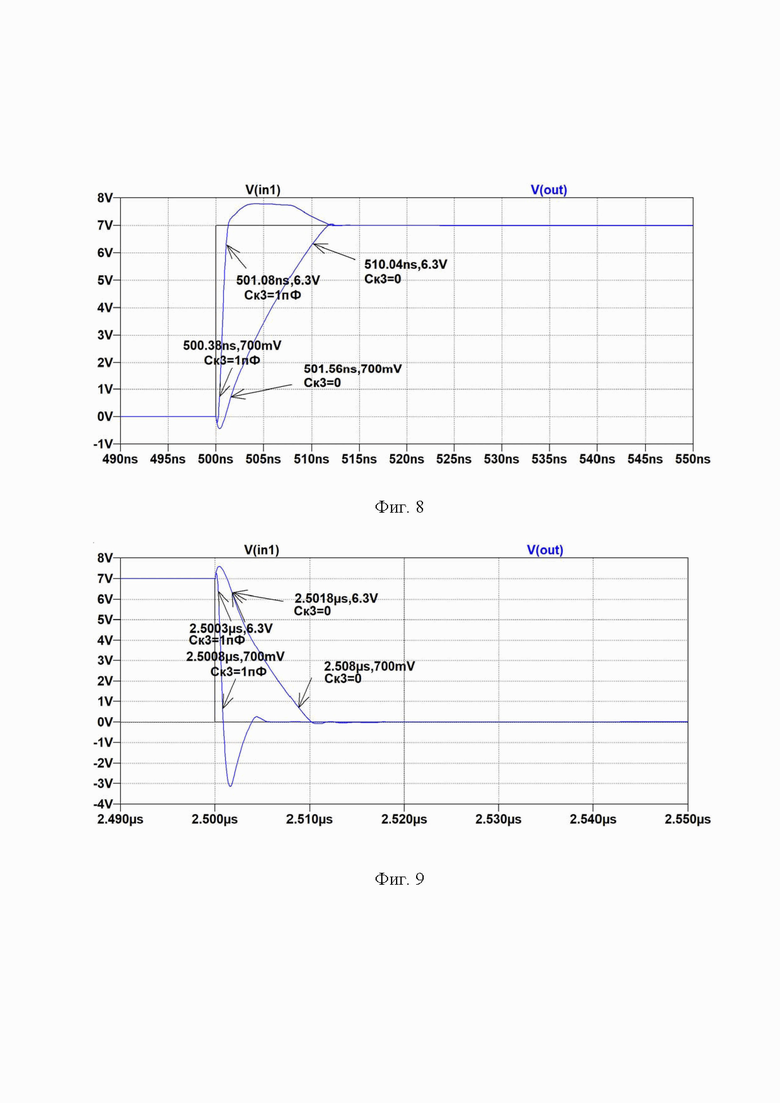

На чертеже фиг. 8 представлен передний фронт переходного процесса в ОУ фиг. 7 по п. 2 формулы изобретения.

На чертеже фиг. 9 приведен задний фронт переходного процесса в ОУ фиг. 7 по п. 2 формулы изобретения.

Быстродействующий операционный усилитель на основе комплементарного «перегнутого» каскода фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 входной транзистор, эмиттер которого связан с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и соединен с эмиттером второго 6 входного транзистора, третий 7 входной транзистор, эмиттер которого связан со второй 8 шиной источника питания через второй 9 токостабилизирующий двухполюсник и соединен с эмиттером четвертого10 входного транзистора, базы первого 3 и третьего 7 входных транзисторов соединены с первым 1 входом устройства, базы второго 6 и четвертого 10 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 3 входного транзистора подключен ко второй 8 шине источника питания через третий 11 токостабилизирующий двухполюсник и связан с эмиттером первого 12 выходного транзистора, коллектор второго 6 входного транзистора связан со второй 8 шиной источника питания через четвертый 13 токостабилизирующий двухполюсник и подключен к эмиттеру второго 14 выходного транзистора, коллектор третьего 7 входного транзистора связан с первой 4 шиной источника питания через пятый 15 токостабилизирующий двухполюсник и соединен с эмиттером третьего 16 выходного транзистора, коллектор четвертого 10 входного транзистора связан с первой 4 шиной источника питания через шестой 17 токостабилизирующий двухполюсник и соединен с эмиттером четвертого 18 выходного транзистора, коллекторы второго 14 и четвертого 18 выходных транзисторов соединены со входом буферного усилителя 19 и корректирующим конденсатором 20, базы первого 12 и второго 14 выходных транзисторов соединены с первым 21 источником напряжения смещения, а базы третьего 16 и четвертого 18 выходных транзисторов связаны со вторым 22 источником напряжения смещения. В схему введены первый 23 и второй 24 дополнительные транзисторы, эмиттер первого 23 дополнительного транзистора соединен со второй 8 шиной источника питания через параллельно-включенные первый 25 дополнительный токостабилизирующий двухполюсник и первый 26 дополнительный корректирующий конденсатор, база первого 23 дополнительного транзистора соединена с эмиттером первого 12 выходного транзистора, эмиттер второго 24 дополнительного транзистора связан с первой 4 шиной источника питания через параллельно-включенные второй 27 дополнительный токостабилизирующий двухполюсник и второй 28 дополнительный корректирующий конденсатор, причем база второго 24 дополнительного транзистора соединена с эмиттером третьего 16 выходного транзистора, коллекторы первого 23 и второго 24 дополнительных транзисторов связаны со входом буферного усилителя 19, а коллекторы первого 12 и третьего 16 выходных транзисторов соединены с общей шиной первого 4 и второго 8 источников питания.

На чертеже фиг.2, в соответствии с п. 2 формулы изобретения, объединенные эмиттеры третьего 7 и четвертого 10 входных транзисторов связаны с объединенными эмиттерами первого 3 и второго 6 входных транзисторов через третий 30 дополнительный корректирующий конденсатор и дополнительный токоограничивающий резистор 31.

Рассмотрим работу ОУ фиг.2.

Статический режим транзисторов схемы ОУ фиг. 2 обеспечивается первым 5, вторым 9, третьим 11, четвертым 13, пятым 15, шестым 17 токостабилизирующими двухполюсниками, первым 25 и вторым 27 дополнительными токостабилизирующими двухполюсниками, а также первым 21 и вторым 22 источниками напряжения смещения.

Токи третьего 11, четвертого 13, а также пятого 15 и шестого 17 токостабилизирующих двухполюсников выбираются на 50-100 мкА меньше, чем токи второго 9 и первого 5 токостабилизирующих двухполюсников. При большом импульсном изменении входного напряжения на первом 1 входе ОУ фиг. 2 второй 6 входной транзистор практически мгновенно запирается, а напряжение на базе первого 23 дополнительного транзистора увеличивается, что формирует дополнительный импульсный ток через первый 26 дополнительный корректирующий конденсатор и соответствующий ему ток заряда корректирующего конденсатора 20.

При отрицательном импульсном изменении напряжения на входе 1 увеличивается напряжение на базе второго 24 дополнительного транзистора, что формирует импульсный ток через второй 28 дополнительный корректирующий конденсатор и дополнительный коллекторный ток второго 24 дополнительного транзистора, форсирующий процесс разряда корректирующего конденсатора 20. Вследствие указанных выше переходных процессов повышается максимальная скорость нарастания выходного напряжения (таблица 1).

Таблица 1 - Зависимости максимальной скорости нарастания выходного напряжения ОУ фиг. 3 от емкостей дополнительных корректирующих конденсаторов 26 (Ск1=С26) и 28 (Ск2=С28)

Ск1=С26, Ск2=С28 в схеме фиг. 3

Дальнейшее повышение SR и ее предельных значений до 8000-11000 В/мкс (см. фиг. 8, фиг. 9, таблица 2) обеспечивается в соответствии с п.2 формулы изобретения – введением третьего 30 дополнительного корректирующего конденсатора 30 и дополнительного токоограничивающего резистора 31. Для уменьшения перерегулирования во время фронта переходного процесса можно изменять сопротивление этого токоограничивающего резистора 31 (R31=R1).

Таблица 2 - Зависимости SR ОУ на чертеже фиг. 7 от емкостей первого 26 (Ск1=С26), второго 28 (Ск2=С28), а также третьего 30 (Ск3=С30) дополнительных корректирующих конденсаторов

Из таблицы 2 следует, что введение третьего 30 дополнительного корректирующего конденсатора обеспечивает дальнейшее повышение SR (более чем на порядок) как переднего, так и заднего фронтов переходного процесса.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483

Схемы ОУ на основе двухтактных «перегнутых» каскодов, выполненных на биполярных транзисторах

3. Патент US 5.153.529, fig. 1, 1992 г.

4. Патент US 5.140.280, fig. 1, 1992 г.

5. Патент US 5.455.535, fig. 5, 1995 г.

6. Патент US 5.610.557, fig. 1, 1997 г.

7. Патент US 5.770.972, fig. 37, 1998 г.

8. Патент US 5.420.540, fig. 2, 1994 г.

9. Патент US 5.729.177, fig. 1,fig. 2, 1998 г.

10. Патент US 5.523.718, fig. 2, 1995 г.

11. Патент US 4.649.352, fig. 1, fig. 2, 1987 г.

12. Патент US 4.837.523, fig. 1, 1989 г.

13. Патент RU 2319286, fig. 2, 2008 г.

14. Патент US 6.249.153, fig. 9, 2001 г.

15. Патент US 4.766.394, fig. 3, 1988 г.

16. Патент US 5.294.893, fig. 2, 1994 г.

17. Патент US 6.963.244, fig. 8, 2005 г.

18. Патент US 5.963.085, fig. 3, 1999 г.

19. Патент RU 2193273, fig. 2, 2002 г.

20. Патент US 5.291.149, fig. 1, 1994 г.

Схемы ОУ на основе двухтактных «перегнутых» каскодов, выполненных на полевых транзисторах

21. Патент US 5.894.245, fig. 2, 1999 г.

22. Патентная заявка US 2005/0275459, fig. 1, 2005 г.

23. Патент US 5.805.021, fig. 1, 1998 г.

24. Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика /Под редакцией канд. техн. наук В.И. Эннса. – М.: Горячая линия-Телеком. – 2005. – С. 206, рис. 3.81

Монографии по теории ОУ

25. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

26. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н.Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. – 222 с.

27. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – 231 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

Изобретение относится к радиоэлектронике. Технический результат: обеспечение во время фронта переходного процесса более высоких уровней выходного тока двухтактного комплементарного «перегнутого» каскода, перезаряжающего интегрирующий корректирующий конденсатор ОУ. Для этого предложен операционный усилитель, в схему которого введены первый (23) и второй (24) дополнительные транзисторы, первый (25) дополнительный токостабилизирующий двухполюсник, первый (26) дополнительный корректирующий конденсатор, второй (27) дополнительный токостабилизирующий двухполюсник, второй (28) дополнительный корректирующий конденсатор, причем база второго (24) дополнительного транзистора соединена с эмиттером третьего (16) выходного транзистора, коллекторы первого (23) и второго (24) дополнительных транзисторов связаны с входом буферного усилителя (19), а коллекторы первого (12) и третьего (16) выходных транзисторов соединены с общей шиной первого (4) и второго (8) источников питания. 9 ил., 2 табл.

1. Быстродействующий операционный усилитель на основе комплементарного «перегнутого» каскода, содержащий первый (1) и второй (2) входы устройства, первый (3) входной транзистор, эмиттер которого связан с первой (4) шиной источника питания через первый (5) токостабилизирующий двухполюсник и соединен с эмиттером второго (6) входного транзистора, третий (7) входной транзистор, эмиттер которого связан со второй (8) шиной источника питания через второй (9) токостабилизирующий двухполюсник и соединен с эмиттером четвертого (10) входного транзистора, базы первого (3) и третьего (7) входных транзисторов соединены с первым (1) входом устройства, базы второго (6) и четвертого (10) входных транзисторов соединены со вторым (2) входом устройства, коллектор первого (3) входного транзистора подключен ко второй (8) шине источника питания через третий (11) токостабилизирующий двухполюсник и связан с эмиттером первого (12) выходного транзистора, коллектор второго (6) входного транзистора связан со второй (8) шиной источника питания через четвертый (13) токостабилизирующий двухполюсник и подключен к эмиттеру второго (14) выходного транзистора, коллектор третьего (7) входного транзистора связан с первой (4) шиной источника питания через пятый (15) токостабилизирующий двухполюсник и соединен с эмиттером третьего (16) выходного транзистора, коллектор четвертого (10) входного транзистора связан с первой (4) шиной источника питания через шестой (17) токостабилизирующий двухполюсник и соединен с эмиттером четвертого (18) выходного транзистора, коллекторы второго (14) и четвертого (18) выходных транзисторов соединены с входом буферного усилителя (19) и корректирующим конденсатором (20), базы первого (12) и второго (14) выходных транзисторов соединены с первым (21) источником напряжения смещения, а базы третьего (16) и четвертого (18) выходных транзисторов связаны со вторым (22) источником напряжения смещения, отличающийся тем, что в схему введены первый (23) и второй (24) дополнительные транзисторы, эмиттер первого (23) дополнительного транзистора соединен со второй (8) шиной источника питания через параллельно-включенные первый (25) дополнительный токостабилизирующий двухполюсник и первый (26) дополнительный корректирующий конденсатор, база первого (23) дополнительного транзистора соединена с эмиттером первого (12) выходного транзистора, эмиттер второго (24) дополнительного транзистора связан с первой (4) шиной источника питания через параллельно-включенные второй (27) дополнительный токостабилизирующий двухполюсник и второй (28) дополнительный корректирующий конденсатор, причем база второго (24) дополнительного транзистора соединена с эмиттером третьего (16) выходного транзистора, коллекторы первого (23) и второго (24) дополнительных транзисторов связаны с входом буферного усилителя (19), а коллекторы первого (12) и третьего (16) выходных транзисторов соединены с общей шиной первого (4) и второго (8) источников питания.

2. Быстродействующий операционный усилитель на основе комплементарного «перегнутого» каскода по п.1, отличающийся тем, что объединенные эмиттеры третьего (7) и четвертого (10) входных транзисторов связаны с объединенными эмиттерами первого (3) и второго (6) входных транзисторов через третий (30) дополнительный корректирующий конденсатор и дополнительный токоограничивающий резистор (31).

| ПРОКОПЕНКО Н.Н | |||

| и др., "Архитектура и схемотехника быстродействующих операционных усилителей: монография", Шахты: Изд-во ЮРГУЭС, 2006, стр | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| US 6501333 B1, 31.12.2002. | |||

Авторы

Даты

2024-02-09—Публикация

2023-10-11—Подача