Изобретение относится к области радиотехники и может быть использовано в структуре различных аналоговых интерфейсов на базе операционных усилителей (ОУ).

Известны схемы классических входных каскадов современных операционных усилителей [1-38], содержащих так называемый «перегнутый» каскод, который реализуется как на КМОП полевых транзисторах с индуцированным каналом, так и на биполярных транзисторах (BJT). Это одна из наиболее популярных схем в аналоговой микроэлектронике. При этом входные каскады (преобразователи напряжение-ток) рассматриваемых ОУ [1-38] выполняются в рамках десятков различных схемотехнических решений, в том числе каскодных включений.

Все существующие сегодня входные каскады ОУ на основе «перегнутых» каскодов (ПК) [1-38] можно разделить на два больших подкласса:

- схемы с двумя токостабилизирующими резисторами, определяющими статический режим выходных транзисторов ПК. Данное схемотехническое решение относится к числу наиболее популярных [1-36] и используется, например, как в зарубежных (OP-90, OP-42, AD8631), так и в российских (140УД30) серийных микросхемах;

- схемы с двумя транзисторными источниками опорного тока в ПК, которые часто используются для введения отрицательной обратной связи по синфазному сигналу в ОУ с парафазным выходом. Данные схемотехнические решения реализуются как на биполярных (патенты US 6.529.076, 2003 г.; US 7.714.656, фиг.3, 2010 г.; US 6.018.268, фиг. 1, 2000 г.), так и на КМОП транзисторах (патенты US 6.717.466, фиг. 1, 2004 г.; US 5.424.681, фиг. 1, 1995 г.; US 2008/0129383, фиг. 1, 2008г.). Каждый из вышеназванных подклассов ОУ характеризуется собственными недостатками и преимуществами в сравнении друг с другом.

Заявляемый ОУ относится к первому подклассу рассматриваемых устройств.

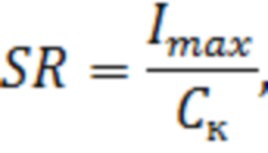

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в патенте US 4.600.893, 1986 г. Он содержит входной дифференциальный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, согласованными с первой 6 шиной источника питания, вторую 7 шину источника питания, связанную с входным дифференциальным усилителем 1, первый 8 и второй 9 транзисторные трехполюсники, каждый из которых имеет управляющий вывод, инжектирующий вывод и токовый выход, причем токовый выход первого 8 транзисторного трехполюсника связан с первым 10 токовым выходом устройства, согласованным со второй 7 шиной источника питания, а токовый выход второго 9 транзисторного трехполюсника связан со вторым 11 токовым выходом устройства, согласованным со второй 7 шиной источника питания, первый 4 токовый выход входного дифференциального усилителя 1 связан с первым выводом первого 12 токостабилизирующего двухполюсника, второй 5 токовый выход входного дифференциального усилителя 1 связан с первым выводом второго 13 токостабилизирующего двухполюсника, а вторые выводы первого 12 и второго 13 токостабилизирующих двухполюсников подключены к первой 6 шине источника питания.

Существенный недостаток ОУ с классическим «перегнутым» каскодом [1-36] состоит в том, что данная схема имеет небольшие значения максимальной скорости нарастания выходного напряжения (SR). Это связано с тем, что здесь «перегнутый» каскод работает в режиме класса «А», и как показано в [37,38], его

где Imax - максимальный выходной ток ПК, перезаряжающий емкость интегрирующего корректирующего конденсатора Ск.

Основная задача предполагаемого изобретения состоит в создании входного дифференциального каскада для работы в структуре различных быстродействующих операционных усилителей с промежуточным «перегнутым» каскодом, функционирующим в режиме класса «АВ». Это позволит существенно повысить SR ОУ и драйверов АЦП на их основе.

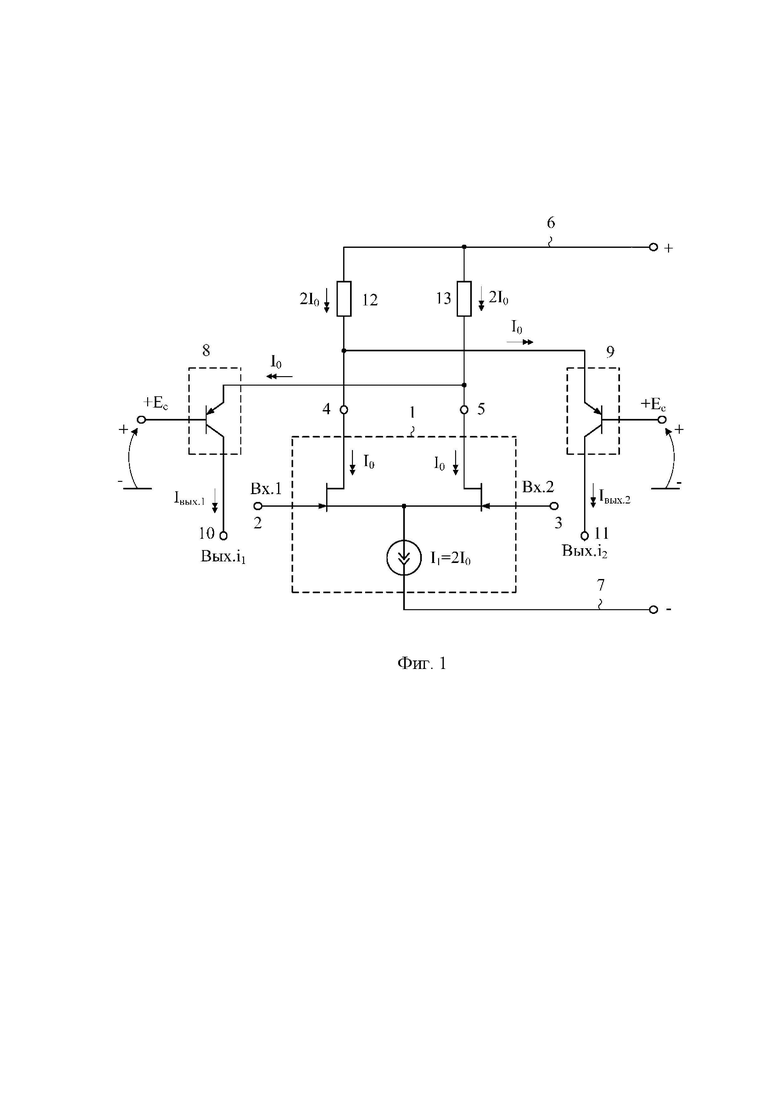

Поставленная задача решается тем, что во входном каскаде операционного усилителя фиг. 1, содержащем входной дифференциальный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, согласованными с первой 6 шиной источника питания, вторую 7 шину источника питания, связанную с входным дифференциальным усилителем 1, первый 8 и второй 9 транзисторные трехполюсники, каждый из которых имеет управляющий вывод, инжектирующий вывод и токовый выход, причем токовый выход первого 8 транзисторного трехполюсника связан с первым 10 токовым выходом устройства, согласованным со второй 7 шиной источника питания, а токовый выход второго 9 транзисторного трехполюсника связан со вторым 11 токовым выходом устройства, согласованным со второй 7 шиной источника питания, первый 4 токовый выход входного дифференциального усилителя 1 связан с первым выводом первого 12 токостабилизирующего двухполюсника, второй 5 токовый выход входного дифференциального усилителя 1 связан с первым выводом второго 13 токостабилизирующего двухполюсника, а вторые выводы первого 12 и второго 13 токостабилизирующих двухполюсников подключены к первой 6 шине источника питания, предусмотрены новые элементы и связи - в схему введены первый 14 и второй 15 дополнительные транзисторные трехполюсники, управляющий вывод первого 14 дополнительного транзисторного трехполюсника связан с первым выводом второго 13 токостабилизирующего двухполюсника, токовый выход первого 14 дополнительного транзисторного трехполюсника соединен с первым 16 дополнительным токовым выходом устройства, инжектирующий вывод первого 14 дополнительного транзисторного трехполюсника связан с инжектирующим выводом первого 8 транзисторного трехполюсника, управляющий вывод второго 15 дополнительного транзисторного трехполюсника подключен к первому выводу первого 12 токостабилизирующего двухполюсника, токовый выход второго 15 дополнительного транзисторного трехполюсника соединен со вторым 17 дополнительным токовым выходом устройства, инжектирующий вывод второго 15 дополнительного транзисторного трехполюсника связан с инжектирующим выводом второго 9 транзисторного трехполюсника, причем управляющий вывод первого 8 транзисторного трехполюсника соединен с первым 4 токовым выходом входного дифференциального усилителя 1, а управляющий вывод второго 9 транзисторного трехполюсника соединен со вторым 5 токовым выходом входного дифференциального усилителя 1.

На чертеже фиг. 1 представлена схема входного каскада операционного усилителя на основе «перегнутого» каскода - прототипа.

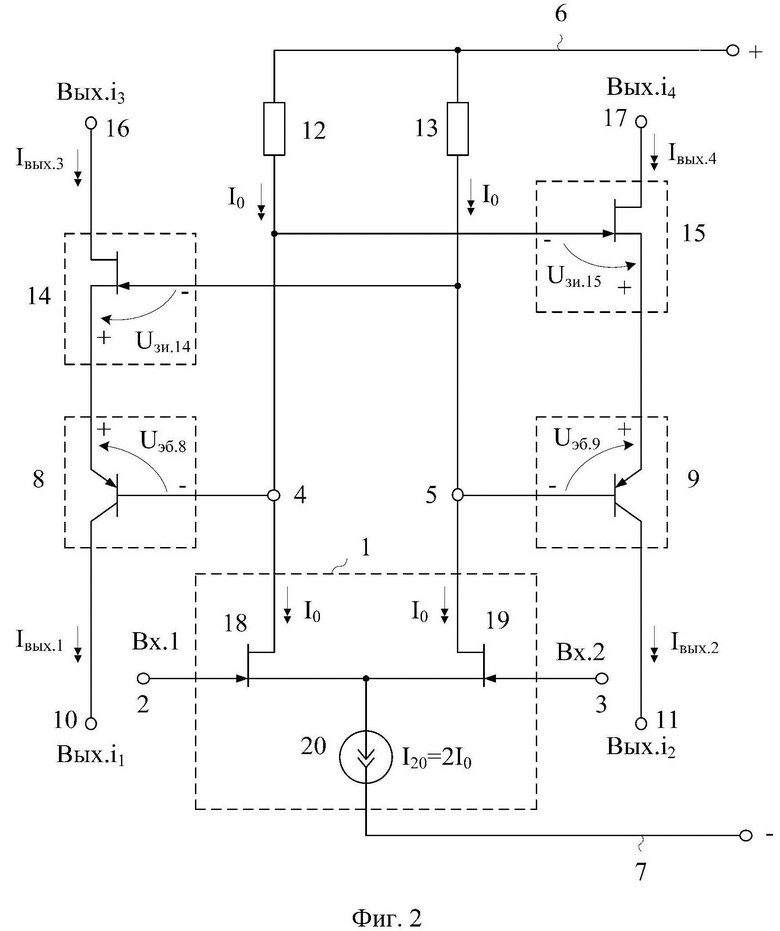

На чертеже фиг. 2 показана схема входного каскада заявляемого быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п. 1 и п. 2 формулы изобретения для случая, когда первый 8 и второй 9 транзисторные трехполюсники выполнены на биполярных транзисторах, а первый 14 и второй 15 дополнительные транзисторные трехполюсники - на полевых транзисторах с управляющим p-n переходом.

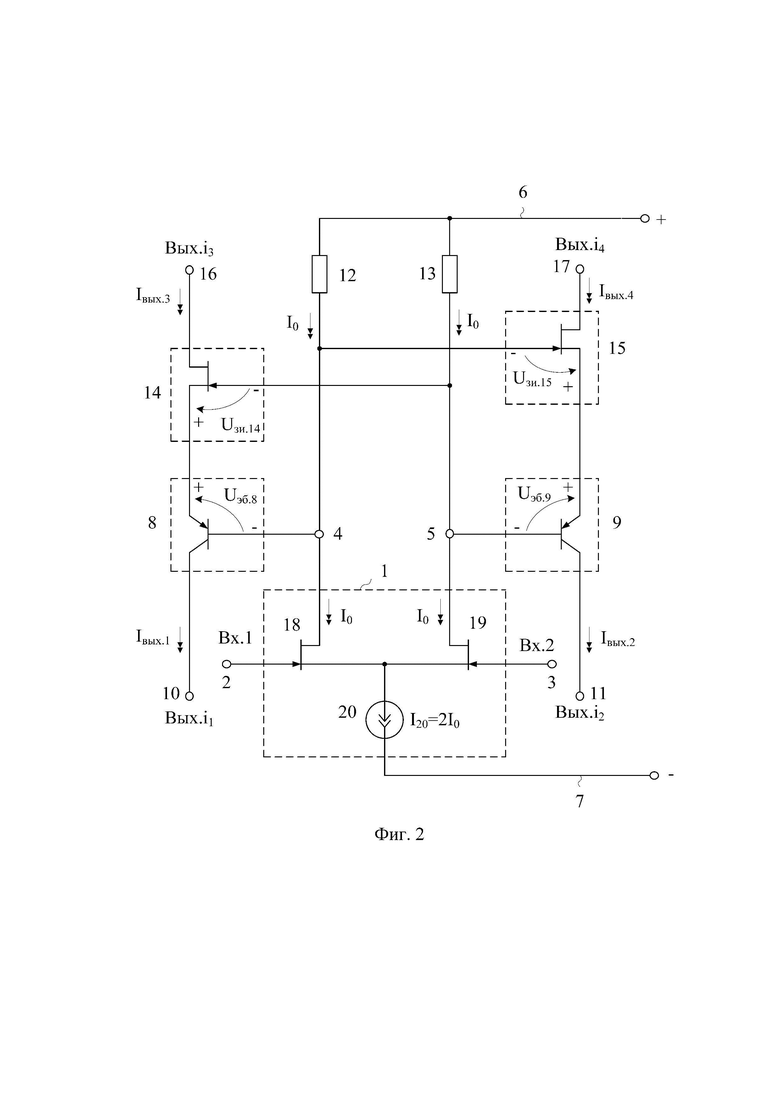

На чертеже фиг. 3 приведена схема входного каскада заявляемого быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п. 3 формулы изобретения для случая, когда первый 8 и второй 9 транзисторные трехполюсники выполнены на биполярных транзисторах, а первый 14 и второй 15 дополнительные транзисторные трехполюсники - на полевых транзисторах с управляющим p-n переходом при реализации первой 21 и второй 22 цепей согласования потенциалов в виде резисторов.

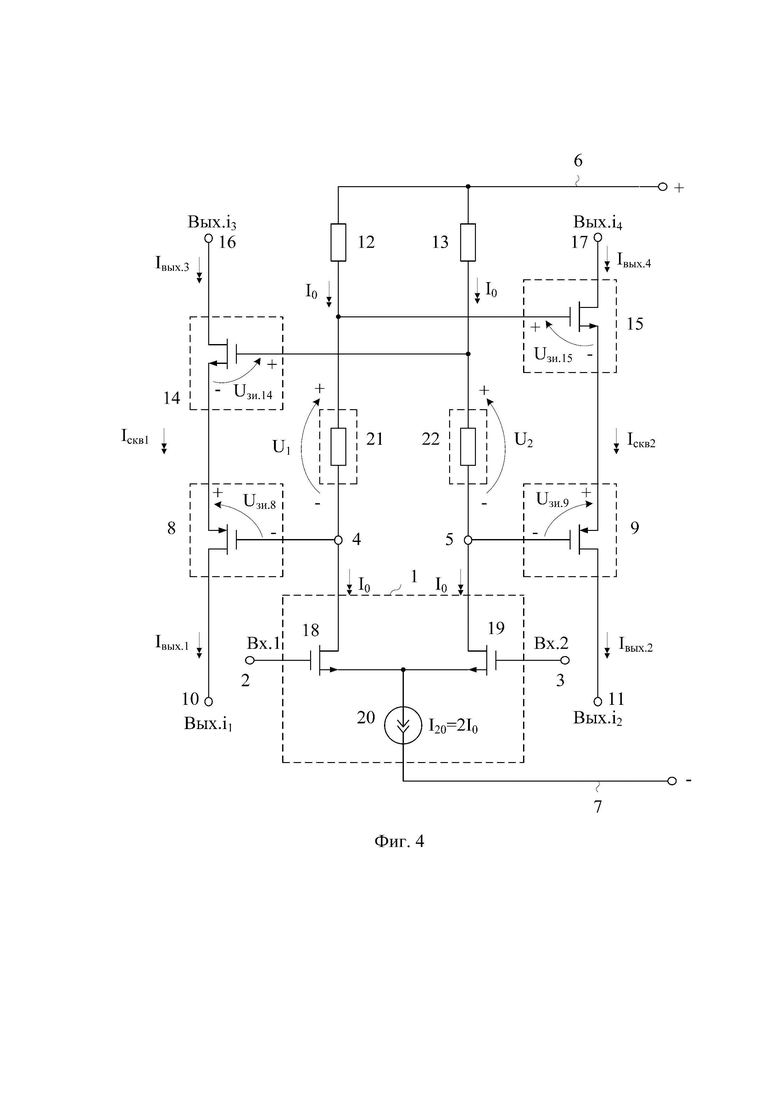

На чертеже фиг. 4 представлена схема входного каскада заявляемого быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п. 4 формулы изобретения для случая, когда первый 8 и второй 9 транзисторные трехполюсники, первый 14 и второй 15 дополнительные транзисторные трехполюсники выполнены на КМОП транзисторах, а первая 21 и вторая 22 цепи согласования потенциалов выполнены в виде резисторов.

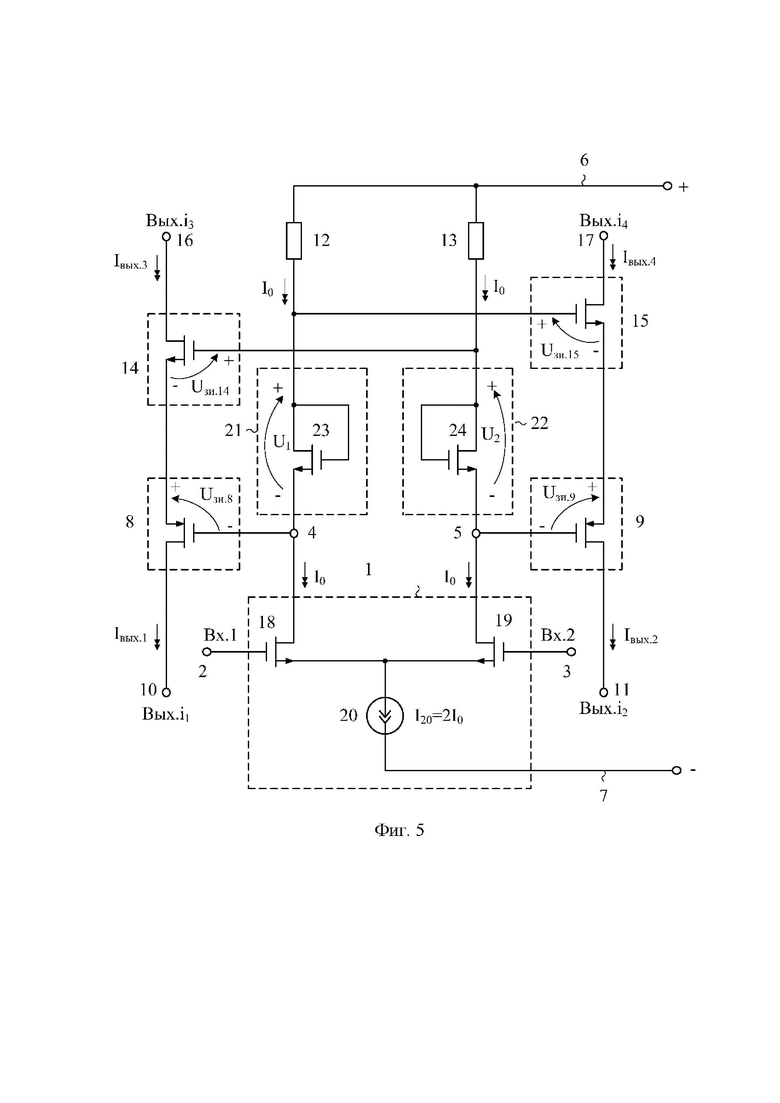

На чертеже фиг. 5 показана схема входного каскада заявляемого быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п. 5 формулы изобретения для случая, когда первый 8 и второй 9 транзисторные трехполюсники, первый 14 и второй 15 дополнительные транзисторные трехполюсники выполнены на КМОП транзисторах, а первая 21 и вторая 22 цепи согласования потенциалов реализованы на первом 23 и втором 24 вспомогательных КМОП транзисторах.

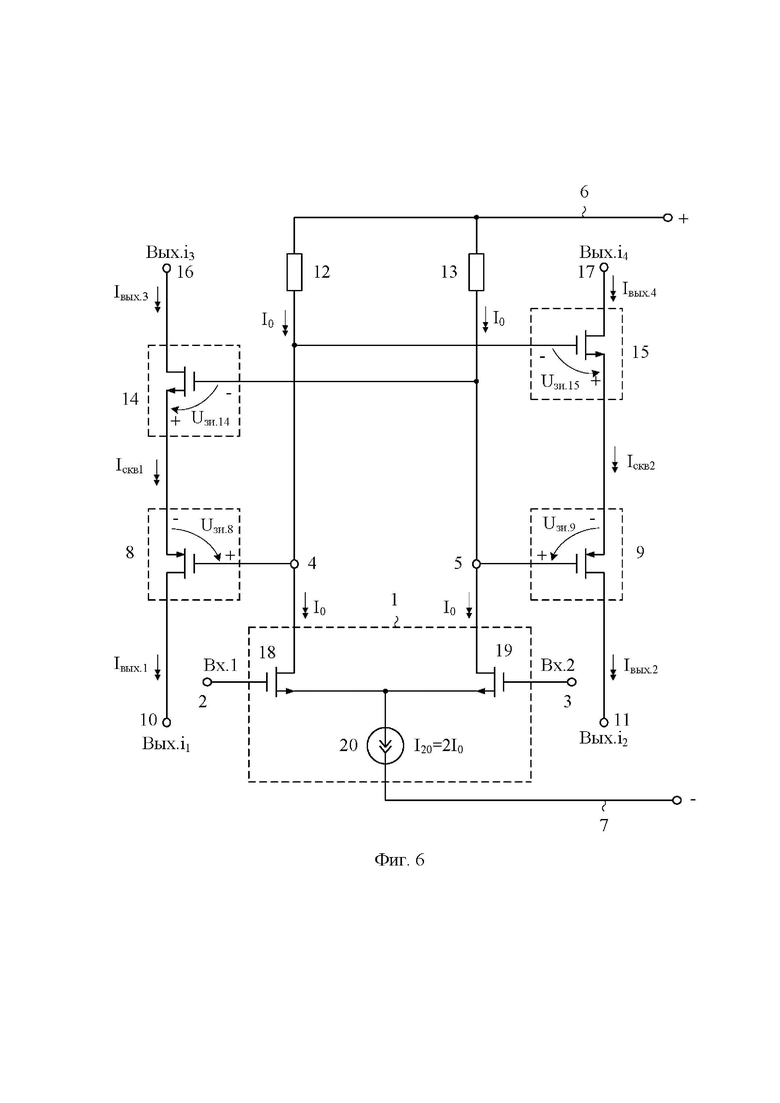

На чертеже фиг. 6 приведена схема входного каскада заявляемого быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п. 6 формулы изобретения для случая, когда первый 8 и второй 9 транзисторные трехполюсники, первый 14 и второй 15 дополнительные транзисторные трехполюсники выполнены на КМОП транзисторах со встроенным каналом.

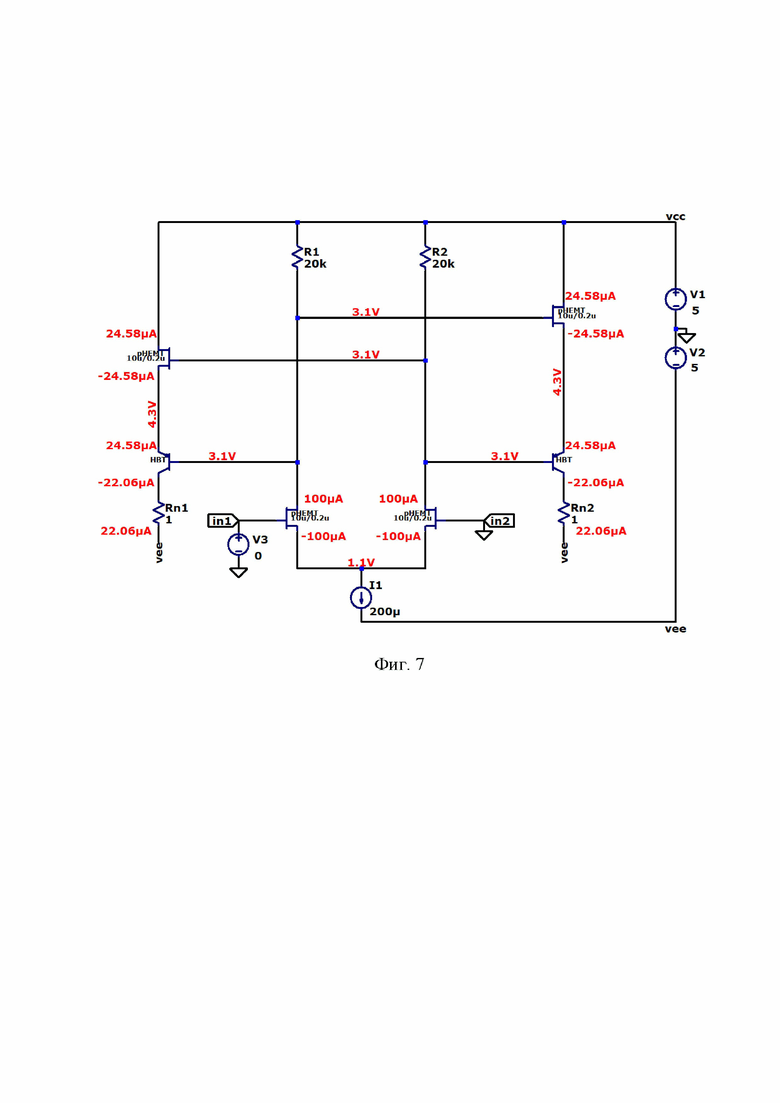

На чертеже фиг. 7 представлен статический режим заявляемого входного каскада быстродействующего ОУ фиг. 2 в среде LTSpice на моделях GaAs транзисторов при 27°С, источнике опорного тока I1=200мкА, резисторах R1=R2=20кОм, напряжениях на шинах питания V1=V2=±5В.

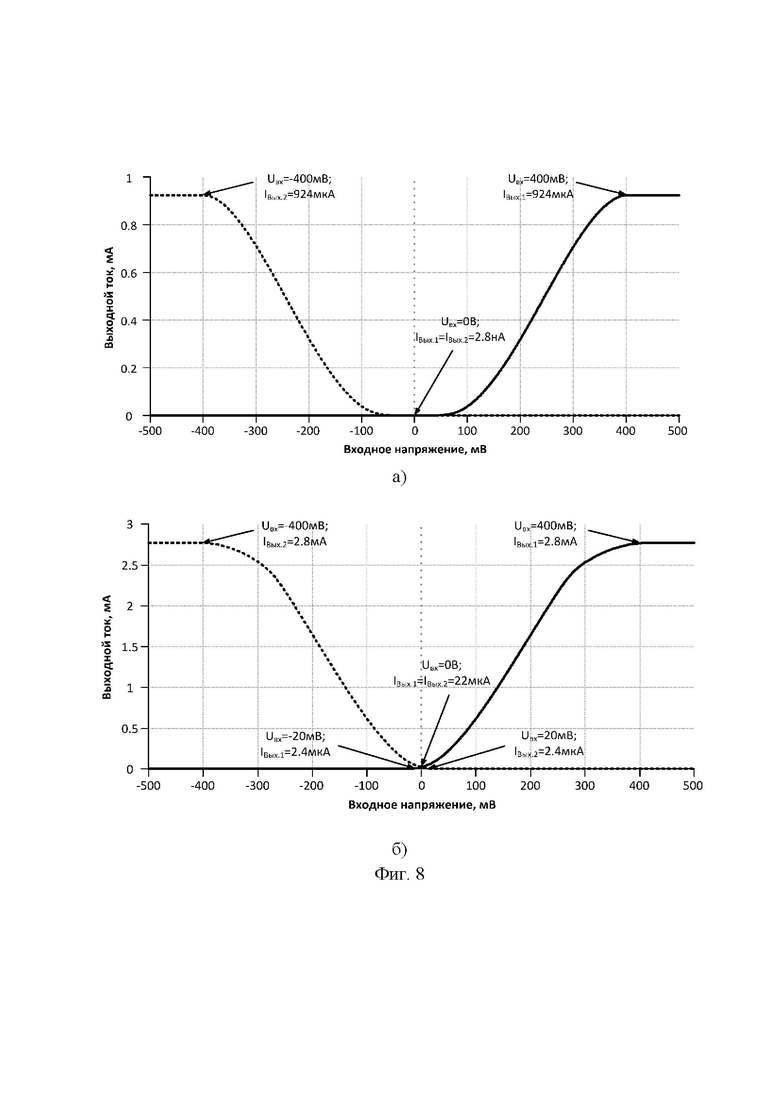

На чертеже фиг. 8 показана зависимость выходных токов входного каскада фиг. 7 от входного напряжения при разных значениях сопротивлений резисторов R1 и R2: R1=R2=10 кОм (а), R1=R2=20 кОм (б).

Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ фиг. 2 входной дифференциальный усилитель 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, согласованными с первой 6 шиной источника питания, вторую 7 шину источника питания, связанную с входным дифференциальным усилителем 1, первый 8 и второй 9 транзисторные трехполюсники, каждый из которых имеет управляющий вывод, инжектирующий вывод и токовый выход, причем токовый выход первого 8 транзисторного трехполюсника связан с первым 10 токовым выходом устройства, согласованным со второй 7 шиной источника питания, а токовый выход второго 9 транзисторного трехполюсника связан со вторым 11 токовым выходом устройства, согласованным со второй 7 шиной источника питания, первый 4 токовый выход входного дифференциального усилителя 1 связан с первым выводом первого 12 токостабилизирующего двухполюсника, второй 5 токовый выход входного дифференциального усилителя 1 связан с первым выводом второго 13 токостабилизирующего двухполюсника, а вторые выводы первого 12 и второго 13 токостабилизирующих двухполюсников подключены к первой 6 шине источника питания. В схему введены первый 14 и второй 15 дополнительные транзисторные трехполюсники, управляющий вывод первого 14 дополнительного транзисторного трехполюсника связан с первым выводом второго 13 токостабилизирующего двухполюсника, токовый выход первого 14 дополнительного транзисторного трехполюсника соединен с первым 16 дополнительным токовым выходом устройства, инжектирующий вывод первого 14 дополнительного транзисторного трехполюсника связан с инжектирующим выводом первого 8 транзисторного трехполюсника, управляющий вывод второго 15 дополнительного транзисторного трехполюсника подключен к первому выводу первого 12 токостабилизирующего двухполюсника, токовый выход второго 15 дополнительного транзисторного трехполюсника соединен со вторым 17 дополнительным токовым выходом устройства, инжектирующий вывод второго 15 дополнительного транзисторного трехполюсника связан с инжектирующим выводом второго 9 транзисторного трехполюсника, причем управляющий вывод первого 8 транзисторного трехполюсника соединен с первым 4 токовым выходом входного дифференциального усилителя 1, а управляющий вывод второго 9 транзисторного трехполюсника соединен со вторым 5 токовым выходом входного дифференциального усилителя 1.

На чертеже фиг.2, в соответствии с п. 2 формулы изобретения, в качестве первого 8 и второго 9 транзисторных трехполюсников используются биполярные транзисторы, а в качестве первого 14 и второго 15 дополнительных транзисторных трехполюсников используются полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 4 токовый выход входного дифференциального усилителя 1 связан с первым выводом первого 12 токостабилизирующего двухполюсника через первую 21 цепь согласования потенциалов, а второй 5 токовый выход входного дифференциального усилителя 1 связан с первым выводом второго 13 токостабилизирующего двухполюсника через вторую 22 цепь согласования потенциалов.

На чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, в качестве первого 8 и второго 9 транзисторных трехполюсников, а также первого 14 и второго 15 дополнительных транзисторных трехполюсников используются КМОП полевые транзисторы с индуцированным каналом.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, первая 21 и вторая 22 цепи согласования потенциалов выполнены на первом 23 и втором 24 вспомогательных КМОП транзисторах с индуцированным каналом, у каждого из которых затвор соединен со стоком.

На чертеже фиг. 6, в соответствии с п. 6 формулы изобретения, в качестве первого 8 и второго 9 транзисторных трехполюсников, а также в качестве первого 14 и второго 15 дополнительных транзисторных трехполюсников используются КМОП транзисторы со встроенным каналом

Компьютерное моделирование входного каскада - прототипа фиг. 1 показывает, что в данной схеме при R12=R13=3,5 КОм, Ес=3 В, I1=200 мкА, выходной статический ток равен 100 мкА, а максимальный выходной ток ДК Iвых.max =182 мкА. Таким образом, ДК-прототип работает в режиме класса «А», что является его недостатком.

Рассмотрим работу схемы на чертеже фиг. 2 для случая, когда второй вход 3 связан с общей шиной источника питания, а на первый 2 вход подается напряжение источника сигнала. При этом ток цепи первого 4 токового выхода увеличивается, а цепи второго 5 токового выхода уменьшается. Как следствие, увеличивается падение напряжения на первом 12 токостабилизирующем двухполюснике, уменьшается напряжение на втором 13 токостабилизирующем двухполюснике и увеличивается напряжение между затвором и базой первого 14 дополнительного и первого 8 транзисторных трехполюсников. Это приводит к увеличению тока в цепях первого 10 токового выхода и первого 16 дополнительного токового выхода устройства (фиг. 8).

Особенность предлагаемой схемы фиг. 2 состоит в том, что она имеет два основных токовых выхода (первый 10 и второй 11), согласованных со второй 7 шиной источника питания, а также два дополнительных токовых выхода (первый 16 и второй 17), согласованных с первой 6 шиной источника питания. В качестве нагрузки для выходов 16-17 и 10-11 могут использоваться различные токовые зеркала, входящие в традиционную архитектуру операционного усилителя (см., например, патент US 4.757.273, фиг. 22, фиг. 23, 1988 г.; патент US 5.714.906, фиг. 9а, 1998 г., патент US 4.377.789, 1983 г., патент US 6.433.637, 2002 г. и др., а также монографию [37]).

Библиографический список

1. Патентная заявка US № 2002/0196079, fig. 1, 2002 г.

2. Патент US № 4.600.893, fig. 5, fig. 6, fig. 7, 1986 г.

3. Патент US № 4.406.990, fig. 4, 1983 г.

4. Патент US № 4.004.245, 1977 г.

5. Патент US № 7.411.451, fig. 5, 2008 г.

6. Патент US № 6.788.143, 2004 г.

7. Патент США № 5.422.600, фиг. 2, 1995 г.

8. Патент США № 5.952.882, 1999 г.

9. Патент США № 4.723.111, 1988 г.

10. Патент США № 4.293.824, 1981 г.

11. Патент США № 5.323.121, 1994 г.

12. Патент США № 5.420.540, fig. 1, 1995 г.

13. Патент RU № 2.354.041 C1, 2009 г.

14. Патентная заявка США № 2003/0201828, fig. 1, fig. 2, 2003 г.

15. Патент США № 6.825.721, fig. 1, fig. 2, 2004 г.

16. Патент США № 6.542.030, fig. 1, 2003 г.

17. Патент US 6.456.162, fig. 2, 2002 г.

18. Патент US 6.501.333, 2002 г.

19. Патент US 6.717.466, 2004 г.

20. Патент US 4.387.309, 1983 г.

21. Патент US 4.390.850, 1983 г.

22. Патент US 5.963.085, 1999 г.

23. Патент US 4.783.637, 1988 г.

24. Патент US 5.610.577, fig 2, 1997 г.

25. Патент US 5.734.296, fig. 5, 1998 г.

26. Патент US 4.463.319, 1984 г.

27. Патент US 6.304.143, fig. 3, 2001 г.

28. Патент US 4.644.295, fig. 4, 1987 г.

29. Патент US 7.215.200, fig. 6, 2007 г.

30. Патент RU 2684500, фиг.2, 2018 г.

31. Патент RU 2592455, фиг.1, 2016 г.

32. Патент RU 2595923, фиг.1, 2016 г.

33. Патент RU 2592429, фиг.1, 2016 г.

34. Патент RU 2604684, фиг.1, 2016 г.

35. Патент RU 2321158, фиг.2, 2006 г.

36. Патент RU 2331865, фиг.2, 2008 г.

37. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

38. Zhengrong He, Yuanjie Zhou, Jiali Xu, Yang Yang, Chenghe Wang, Guoliang Fan, “A High Speed JFET Operational Amplifier Based on Complementary Bipolar Process”, EITCE 2021: Proceedings of the 2021 5th International Conference on Electronic Information Technology and Computer Engineering, October 2021, Pages 44-49, https://doi.org/10.1145/3501409.3501418

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

Изобретение относится к области радиотехники и может быть использовано в структуре различных аналоговых интерфейсов на базе операционных усилителей (ОУ). Техническим результатом изобретения является повышение максимальной скорости нарастания выходного напряжения (SR) ОУ и драйверов АЦП на их основе. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ дополнительно содержит первый (14) и второй (15) дополнительные транзисторные трехполюсники. Управляющий вывод первого (14) дополнительного транзисторного трехполюсника связан с первым выводом второго (13) токостабилизирующего двухполюсника. Токовый выход первого (14) дополнительного транзисторного трехполюсника соединен с первым (16) дополнительным токовым выходом устройства. Инжектирующий вывод первого (14) дополнительного транзисторного трехполюсника связан с инжектирующим выводом первого (8) транзисторного трехполюсника. Управляющий вывод второго (15) дополнительного транзисторного трехполюсника подключен к первому выводу первого (12) токостабилизирующего двухполюсника. Токовый выход второго (15) дополнительного транзисторного трехполюсника соединен со вторым (17) дополнительным токовым выходом устройства. Инжектирующий вывод второго (15) дополнительного транзисторного трехполюсника связан с инжектирующим выводом второго (9) транзисторного трехполюсника. Управляющий вывод первого (8) транзисторного трехполюсника соединен с первым (4) токовым выходом входного дифференциального усилителя (1). Управляющий вывод второго (9) транзисторного трехполюсника соединен со вторым (5) токовым выходом входного дифференциального усилителя (1). 5 з.п. ф-лы, 8 ил.

1. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ, содержащий входной дифференциальный усилитель (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, согласованными с первой (6) шиной источника питания, вторую (7) шину источника питания, связанную с входным дифференциальным усилителем (1), первый (8) и второй (9) транзисторные трехполюсники, каждый из которых имеет управляющий вывод, инжектирующий вывод и токовый выход, причем токовый выход первого (8) транзисторного трехполюсника связан с первым (10) токовым выходом устройства, согласованным со второй (7) шиной источника питания, а токовый выход второго (9) транзисторного трехполюсника связан со вторым (11) токовым выходом устройства, согласованным со второй (7) шиной источника питания, первый (4) токовый выход входного дифференциального усилителя (1) связан с первым выводом первого (12) токостабилизирующего двухполюсника, второй (5) токовый выход входного дифференциального усилителя (1) связан с первым выводом второго (13) токостабилизирующего двухполюсника, а вторые выводы первого (12) и второго (13) токостабилизирующих двухполюсников подключены к первой (6) шине источника питания, отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные транзисторные трехполюсники, управляющий вывод первого (14) дополнительного транзисторного трехполюсника связан с первым выводом второго (13) токостабилизирующего двухполюсника, токовый выход первого (14) дополнительного транзисторного трехполюсника соединен с первым (16) дополнительным токовым выходом устройства, инжектирующий вывод первого (14) дополнительного транзисторного трехполюсника связан с инжектирующим выводом первого (8) транзисторного трехполюсника, управляющий вывод второго (15) дополнительного транзисторного трехполюсника подключен к первому выводу первого (12) токостабилизирующего двухполюсника, токовый выход второго (15) дополнительного транзисторного трехполюсника соединен со вторым (17) дополнительным токовым выходом устройства, инжектирующий вывод второго (15) дополнительного транзисторного трехполюсника связан с инжектирующим выводом второго (9) транзисторного трехполюсника, причем управляющий вывод первого (8) транзисторного трехполюсника соединен с первым (4) токовым выходом входного дифференциального усилителя (1), а управляющий вывод второго (9) транзисторного трехполюсника соединен со вторым (5) токовым выходом входного дифференциального усилителя (1).

2. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п.1, отличающийся тем, что в качестве первого (8) и второго (9) транзисторных трехполюсников используются биполярные транзисторы, а в качестве первого (14) и второго (15) дополнительных транзисторных трехполюсников используются полевые транзисторы с управляющим p-n переходом.

3. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п.1, отличающийся тем, что первый (4) токовый выход входного дифференциального усилителя (1) связан с первым выводом первого (12) токостабилизирующего двухполюсника через первую (21) цепь согласования потенциалов, а второй (5) токовый выход входного дифференциального усилителя (1) связан с первым выводом второго (13) токостабилизирующего двухполюсника через вторую (22) цепь согласования потенциалов.

4. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п.3, отличающийся тем, что в качестве первого (8) и второго (9) транзисторных трехполюсников, а также первого (14) и второго (15) дополнительных транзисторных трехполюсников используются КМОП полевые транзисторы с индуцированным каналом.

5. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п.4, отличающийся тем, что первая (21) и вторая (22) цепи согласования потенциалов выполнены на первом (23) и втором (24) вспомогательных КМОП транзисторах с индуцированным каналом, у каждого из которых затвор соединен со стоком.

6. Входной каскад быстродействующего операционного усилителя с «перегнутым» каскодом класса АВ по п.1, отличающийся тем, что в качестве первого (8) и второго (9) транзисторных трехполюсников, а также в качестве первого (14) и второго (15) дополнительных транзисторных трехполюсников используются КМОП транзисторы со встроенным каналом.

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

| СХЕМА УСИЛИТЕЛЯ СИГНАЛА, ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ И СИСТЕМА | 2018 |

|

RU2736323C1 |

| US 4600893 A, 15.07.1986 | |||

| US 5422600 A, 06.06.1995 | |||

| WO 2016031120 A1, 03.03.2016 | |||

| WO 9730512 A1, 21.08.1997 | |||

| МАНЖУЛА В.Г., ПУГАЧЕВ И.Б., ПРОКОПЕНКО Н.Н | |||

| Вариативный синтез схемы операционного усилителя с пониженным напряжением смещения нуля | |||

Авторы

Даты

2022-12-21—Публикация

2022-05-06—Подача