ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

[0001] Настоящая заявка ссылается на заявку на патент Китая № 202010505672.3, поданную 5 июня 2020 г. и озаглавленную «Read-Write Conversion Circuit and Memory», и заявку на патент Китая № 202021024456.9, поданную 5 июня 2020 г. и озаглавленную «Read-Write Conversion Circuit and Memory», раскрытия которых полностью включены в настоящий документ путем ссылки.

ОБЛАСТЬ ТЕХНИКИ

[0002] Варианты реализации настоящего изобретения относятся к технической области полупроводников и, в частности, к схеме преобразования чтения-записи и памяти.

УРОВЕНЬ ТЕХНИКИ

[0003] Динамическое оперативное запоминающее устройство (Dynamic Random Access Memory, DRAM) - это полупроводниковое запоминающее устройство, которое широко распространено в компьютерах и состоит из множества повторяющихся ячеек памяти. Каждая ячейка памяти обычно содержит конденсатор и транзистор. Транзистор содержит затвор, соединенный с числовой линией, сток, соединенный с разрядной линией, и исток, соединенный с конденсатором. Сигнал напряжения в числовой линии может включать или выключать транзистор для считывания информации данных, хранящихся в конденсаторе, через разрядную линию или записи информации данных в конденсатор для хранения через разрядную линию.

[0004] DRAM может быть классифицировано как DRAM с удвоенной скоростью передачи данных (Double Data Rate (DDR) DRAM), DRAM с удвоенной скоростью передачи графических данных (Graphics Double Data Rate (GDDR) DRAM) или DRAM с низким энергопотреблением и удвоенной скоростью передачи данных (Low Power Double Data Rate (LPDDR) DRAM). С увеличением числа областей применения DRAM, например, с применением DRAM в области мобильной связи, требования пользователей к показателю скорости DRAM возросли.

[0005] Однако потребность в улучшении рабочих характеристик DRAM известного уровня техники по-прежнему сохраняется.

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0006] Согласно вариантам реализации настоящего изобретения предложена схема преобразования чтения-записи и памяти в качестве решения технической проблемы. Скорость операции чтения-записи схемы преобразования чтения-записи является переменной, так что рабочие характеристики памяти улучшаются.

[0007] Для решения вышеуказанной проблемы в вариантах реализации настоящего изобретения предложена схема преобразования чтения-записи, которая отличается тем, что указанная схема содержит: модуль преобразования чтения-записи, выполняющий операцию чтения-записи в ответ на сигнал управления чтением-записью; и модуль управления, выводящий переменный сигнал управления чтением-записью в ответ на сигнал конфигурирования скорости чтения-записи для управления скоростью операции чтения-записи модуля преобразования чтения-записи таким образом, чтобы она была переменной.

[0008] Кроме того, также может быть включен модуль конфигурирования скорости, который может быть соединен с модулем управления и выполнен с возможностью вывода сигнала конфигурирования скорости чтения-записи в модуль управления.

[0009] Кроме того, сигнал управления чтением-записью может содержать сигнал управления чтением и сигнал управления записью. Модуль преобразования чтения-записи может выполнять операцию чтения в ответ на сигнал управления чтением и выполнять операцию записи в ответ на сигнал управления записью. Модуль конфигурирования скорости может содержать блок конфигурирования скорости чтения, выполненный с возможностью вывода сигнала конфигурирования скорости чтения в сигнале конфигурирования скорости чтения-записи в модуль управления, что вызывает вывод модулем управления чтением, в ответ на сигнал конфигурирования скорости чтения, переменного сигнала управления, управляющего скоростью операции чтения таким образом, чтобы она была переменной. Модуль конфигурирования скорости может также содержать блок конфигурирования скорости записи, выполненный с возможностью вывода сигнала конфигурирования скорости записи в сигнале конфигурирования скорости чтения-записи в модуль управления, чтобы вызвать вывод модулем управления, в ответ на сигнал конфигурирования скорости чтения, переменного сигнала управления записью для управления скоростью операции записи таким образом, чтобы она была переменной.

[0010] Кроме того, также могут быть включены локальная линия данных, локальная комплементарная линия данных и глобальная линия данных. Во время операции чтения-записи может выполняться передача данных между каждой из локальной линии данных, локальной комплементарной линии данных и глобальной линией данных, во время которой сигналы данных локальной линии данных и локальной комплементарной линии данных могут быть в противофазе.

[0011] Кроме того, модуль преобразования чтения-записи может содержать локальный блок чтения-записи, выполняющий локальную операцию чтения-записи в ответ на локальный сигнал управления чтением-записью в сигнале управления чтением-записью. Модуль управления может содержать локальный блок управления, выводящий, в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменного локального сигнала управления чтением-записью для управления скоростью локальной операции чтения-записи локального блока чтения-записи таким образом, чтобы она была переменной.

[0012] Кроме того, схема преобразования чтения-записи может также содержать локальный модуль конфигурирования скорости, соединенный с локальным блоком управления и выполненный с возможностью вывода локального сигнала конфигурирования скорости чтения-записи в локальный блок управления.

[0013] Кроме того, схема преобразования чтения-записи может также содержать усилитель считывания, соединенный с локальным блоком чтения-записи посредством локальной линии данных и локальной комплементарной линии данных и выполненный с возможностью считывания напряжения разрядной линии.

[0014] Кроме того, один и тот же локальный блок чтения-записи может быть соединен с множеством усилителей считывания посредством локальной линии данных и локальной комплементарной линии данных.

[0015] Кроме того, тракт данных чтения может быть следующим: от локального блока чтения-записи к усилителю считывания через локальную линию данных и локальную комплементарную линию данных, а затем к разрядной линии через усилитель считывания. Тракт данных чтения может быть следующим: от разрядной линии к локальной линии данных и локальной комплементарной линии данных через усилитель считывания, а затем к локальному блоку чтения-записи через локальную линию данных и локальную комплементарную линию данных.

[0016] Кроме того, модуль преобразования чтения-записи может содержать глобальный блок чтения-записи, выполняющий глобальную операцию чтения-записи в ответ на глобальный сигнал управления чтением-записью в сигнале управления чтением-записью. Модуль управления может содержать глобальный модуль управления, выводящий, в ответ на глобальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменный глобальный сигнал управления чтением-записью для управления скоростью глобальной операции чтения-записи глобального блока чтения-записи таким образом, чтобы она была переменной.

[0017] Кроме того, схема преобразования чтения-записи может также содержать глобальный модуль конфигурирования скорости, соединенный с глобальным блоком управления и выполненный с возможностью вывода глобального сигнала конфигурирования скорости чтения-записи в глобальный блок управления.

[0018] Кроме того, локальный блок чтения-записи может содержать локальный усилитель, подсоединенный между локальной линией данных и локальной комплементарной линией данных и выполненный с возможностью усиления данных локальной линии данных и данных локальной комплементарной линии данных.

[0019] Кроме того, локальный усилитель может содержать первый фазоинвертор, в котором первый вход первого фазоинвертора электрически соединен с локальной линией данных, а первый выход первого фазоинвертора, электрически соединен с локальной комплементарной линией данных; и второй фазоинвертор, в котором второй вход второго фазоинвертора электрически соединен с первым выходом первого фазоинвертора и локальной комплементарной линией данных, а второй выход второго фазоинвертора электрически соединен с первым входом первого фазоинвертора и локальной линией данных.

[0020] Кроме того, первый фазоинвертор может содержать первый транзистор на структуре металл-оксид-полупроводник с каналом p-типа (pМОП) и первый транзистор на структуре металл-оксид-полупроводник с каналом n-типа (nМОП). Затвор первого pМОП-транзистора может быть соединен с затвором первого nМОП-транзистора, чтобы служить первым входом первого фазоинвертора, исток первого pМОП-транзистора может быть соединен с рабочим питанием, а сток первого pМОП-транзистора может быть соединен со стоком первого nМОП-транзистора, чтобы служить первым выходом первого фазоинвертора. Второй фазоинвертор может содержать нулевой pМОП-транзистор и нулевой nМОП-транзистор. Затвор нулевого pМОП-транзистора может быть соединен с затвором нулевого nМОП-транзистора, чтобы служить вторым входом второго фазоинвертора. Исток нулевого pМОП-транзистора может быть соединен с рабочим питанием, а сток нулевого pМОП-транзистора может быть соединен со стоком нулевого nМОП-транзистора, чтобы служить вторым выходом второго фазоинвертора.

[0021] Кроме того, локальный блок чтения-записи может содержать локальную схему преобразования чтения, выполненную с возможностью передачи данных локальной линии данных и локальной комплементарной линии данных в глобальную линию данных в ответ на локальный сигнал управления чтением в локальном сигнале управления чтением-записью. Локальная схема преобразования чтения может содержать третий nМОП-транзистор и четвертый nМОП-транзистор. Сток третьего nМОП-транзистора может быть соединен с глобальной линией данных, затвор третьего nМОП-транзистора может быть соединен с локальной комплементарной линией данных, а исток третьего nМОП-транзистора может быть соединен со стоком четвертого nМОП-транзистора. Затвор четвертого nМОП-транзистора может принимать локальный сигнал чтения в локальном сигнале управления чтением, тогда как исток может быть заземлен.

[0022] Кроме того, схема преобразования чтения-записи может также содержать глобальную комплементарную линию данных, причем во время операции чтения сигналы данных глобальной комплементарной линии данных и глобальной линии данных могут быть в противофазе. Локальная схема преобразования чтения может также содержать восьмой nМОП-транзистор и девятый nМОП-транзистор. Сток восьмого nМОП-транзистора может быть соединен с глобальной комплементарной линией данных, затвор восьмого nМОП-транзистора может быть соединен с локальной линией данных, а исток восьмого nМОП-транзистора может быть соединен со стоком девятого nМОП-транзистора. Затвор девятого nМОП-транзистора может принимать локальный сигнал чтения, тогда как исток может быть заземлен.

[0023] Кроме того, локальный блок чтения-записи может содержать локальную схему преобразования записи, выполненную с возможностью передачи данных глобальной линии данных в локальную линию данных и локальную комплементарную линию данных в ответ на локальный сигнал управления записью в локальном сигнале управления чтением-записью. Локальная схема преобразования записи может содержать пятый nМОП-транзистор, шестой nМОП-транзистор и седьмой nМОП-транзистор. Сток пятого nМОП-транзистора может быть соединен с локальной комплементарной линией данных, затвор пятого nМОП-транзистора может быть соединен с истоком седьмого nМОП-транзистора, а исток пятого nМОП-транзистора может быть соединен со стоком шестого nМОП-транзистора. Затвор шестого nМОП-транзистора может принимать локальный сигнал записи в локальном сигнале управления записью, тогда как исток может быть заземлен. Сток седьмого nМОП-транзистора может быть соединен с локальной линией данных, тогда как затвор может принимать локальный сигнал записи.

[0024] Кроме того, схема преобразования чтения-записи может также содержать глобальную комплементарную линию данных, причем во время операции чтения-записи сигналы данных глобальной комплементарной линии данных и глобальной линии данных могут быть в противофазе. Локальная схема преобразования записи может также содержать десятый nМОП-транзистор, одиннадцатый nМОП-транзистор и двенадцатый nМОП-транзистор. Сток десятого nМОП-транзистора может быть соединен с локальной линией данных, затвор десятого nМОП-транзистора может быть соединен с истоком двенадцатого nМОП-транзистора и глобальной комплементарной линией, а исток десятого nМОП-транзистора может быть соединен со стоком одиннадцатого nМОП-транзистора. Затвор одиннадцатого nМОП-транзистора может принимать локальный сигнал записи, тогда как исток может быть заземлен. Сток двенадцатого nМОП-транзистора может быть соединен с локальной комплементарной линией данных, тогда как затвор может принимать локальный сигнал записи.

[0025] Кроме того, локальный блок чтения-записи может также содержать схему предварительной зарядки, подсоединенную между локальной линией данных и локальной комплементарной линией данных и выполненную с возможностью предварительной зарядки локальной линии данных и локальной комплементарной линии данных в ответ на сигнал управления предварительной зарядкой.

[0026] Кроме того, схема предварительной зарядки может содержать третий pМОП-транзистор, четвертый pМОП-транзистор и пятый pМОП-транзистор. Затвор третьего pМОП-транзистора, затвор четвертого pМОП-транзистора и затвор пятого pМОП-транзистора могут принимать сигнал управления предварительной зарядкой. Исток третьего pМОП-транзистора и исток четвертого pМОП-транзистора могут быть соединены с рабочим питанием. Сток третьего pМОП-транзистора может быть электрически соединен с локальной линией данных. Сток четвертого pМОП-транзистора может быть электрически соединен с локальной комплементарной линией данных. Пятый pМОП-транзистор может быть электрически соединен с локальной линией данных и локальной комплементарной линией данных в ответ на сигнал управления предварительной зарядкой.

[0027] Соответственно, согласно вариантам реализации настоящего изобретения также предложена память, которая может содержать вышеупомянутую схему преобразования чтения-записи.

[0028] По сравнению с известным уровнем техники технические решения, предложенные в этих вариантах реализации настоящего изобретения, имеют следующие преимущества.

[0029] Согласно вариантам реализации настоящего изобретения предложена схема преобразования чтения-записи с высокими структурными характеристиками, которая включает в себя модуль преобразования чтения-записи, который выполняет операцию чтения-записи в ответ на сигнал управления чтением-записью, и модуль управления, который выводит переменный сигнал управления чтением-записью в ответ на сигнал конфигурирования скорости чтения-записи, так что скорость операции чтения-записи модуля преобразования чтения-записи остается переменной. Поскольку сигнал управления чтением-записью, выводимый модулем управления, является переменным, скорость операции чтения-записи, выполняемой модулем преобразования чтения-записи после приема переменного сигнала управления чтением-записью, тоже переменная, и поэтому скорость операции чтения-записи схемы преобразования чтения-записи может быть сконфигурирована. По сравнению с известным уровнем техники, в котором скорость операции чтения-записи схемы преобразования чтения-записи фиксирована, схема преобразования чтения-записи, предложенная согласно вариантам реализации настоящего изобретения, позволяет корректировать скорость операции чтения-записи в соответствии с практическими потребностями, так что эта схема преобразования чтения-записи может применяться более широко, например, не только к низкоскоростной операции чтения-записи, но и также к высокоскоростной операции чтения-записи. Кроме того, с принятием схемы преобразования чтения-записи, предложенной согласно вариантам реализации настоящего изобретения, высокоскоростная операция чтения-записи, когда она не требуется, может быть скорректирована до низкоскоростной операции чтения-записи, тем самым решается проблема высокого потребления энергии, вызываемого высокоскоростной операцией. Следовательно, рабочие характеристики схемы чтения-записи, предложенной согласно вариантам реализации настоящего изобретения, могут быть улучшены.

[0030] Кроме того, модуль преобразования чтения-записи содержит локальный блок чтения-записи, а модуль управления содержит локальный модуль управления, выводящий переменный локальный сигнал управления чтением-записью в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, так что скорость локальной операции чтения-записи локального блока чтения-записи остается переменной. Следовательно, скорость локальной операции чтения-записи схемы преобразования чтения-записи, предложенной согласно вариантам реализации настоящего изобретения, может быть сконфигурирована.

[0031] Кроме того, модуль преобразования чтения-записи содержит глобальный блок чтения-записи, а модуль управления содержит глобальный блок управления, выводящий переменный глобальный сигнал управления чтением-записью в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, так что скорость глобальной операции чтения-записи глобального блока чтения-записи остается переменной. Следовательно, скорость глобальной операции считывания-записи схемы преобразования чтения-записи, предложенной согласно вариантам реализации настоящего изобретения, может быть сконфигурирована.

[0032] Кроме того, локальный блок чтения-записи содержит локальный усилитель, подсоединенный между локальной линией данных и локальной комплементарной линией данных и выполненный с возможностью усиления данных локальной линии данных и данных локальной комплементарной линии данных. Локальный усилитель способствует ускорению установления различия между локальной линией данных и локальной комплементарной линией данных и способствует не только увеличению скорости локальной операции чтения-записи, но и снижению требований по возбуждению, предъявляемых локальной линией данных и локальной комплементарной линией данных к усилителю считывания, что упрощает проектирование усилителей считывания.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

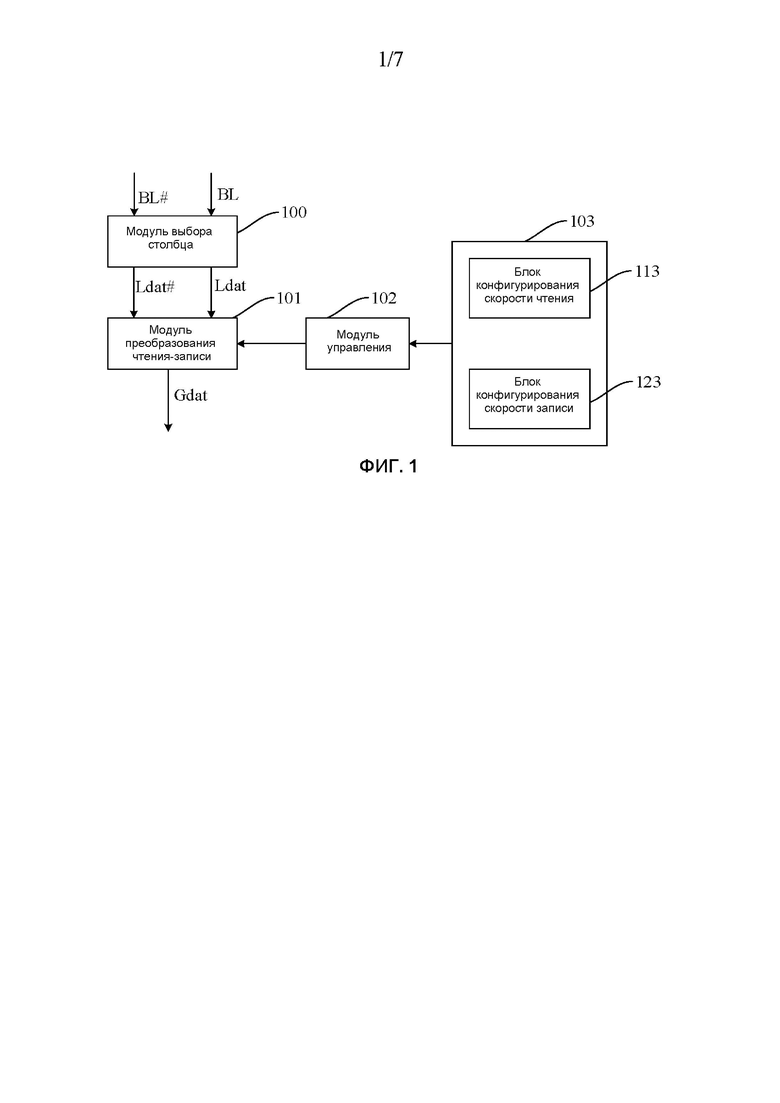

[0033] На ФИГ. 1 приведена принципиальная схема для схемы преобразования чтения-записи в соответствии с вариантом реализации настоящего изобретения.

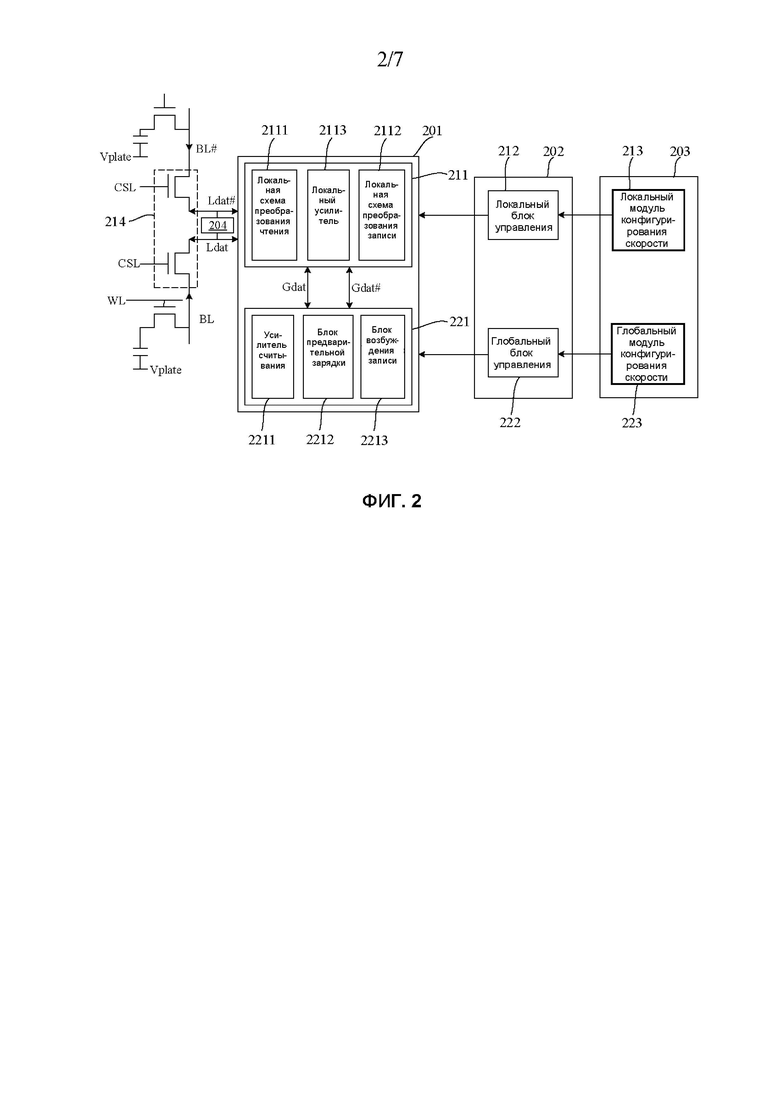

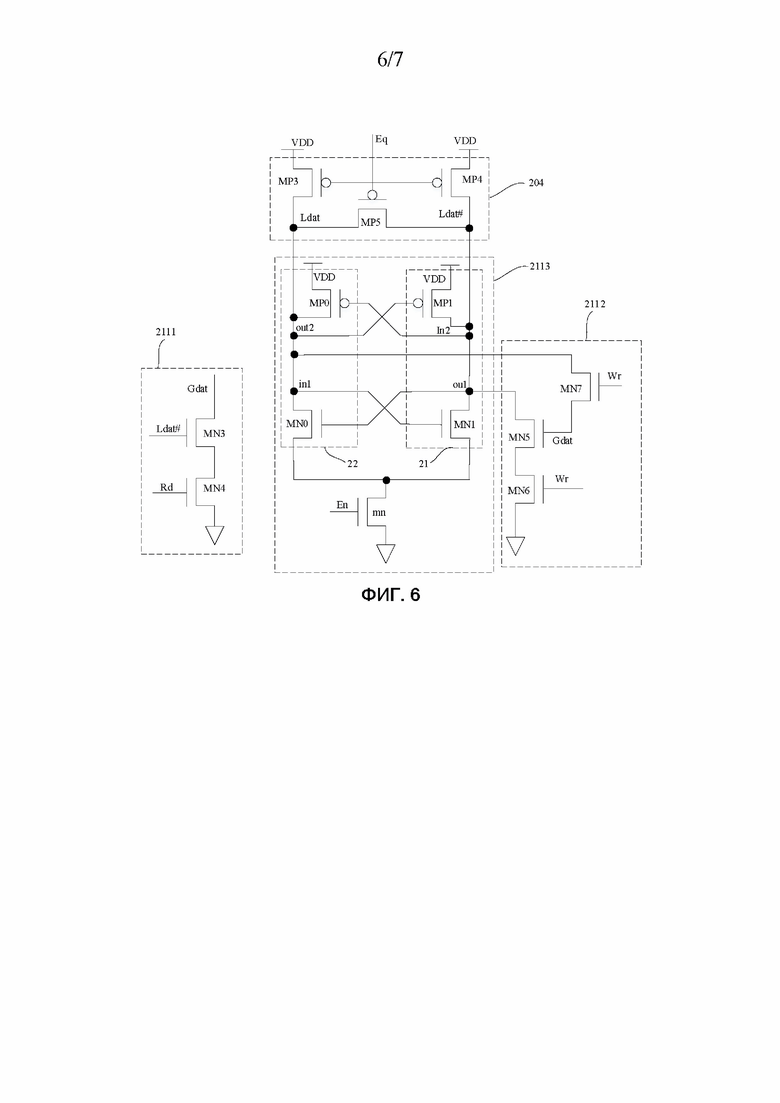

[0034] На ФИГ. 2 приведена принципиальная схема для схемы преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

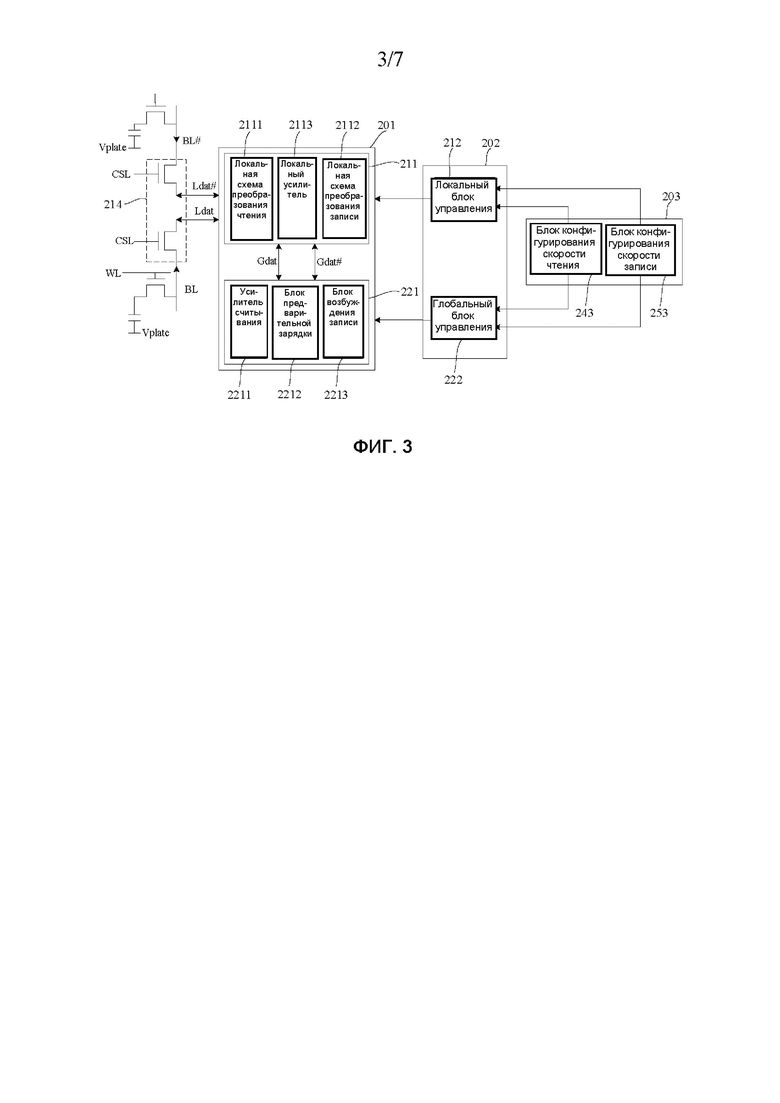

[0035] На ФИГ. 3 приведена еще одна принципиальная схема для схемы преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

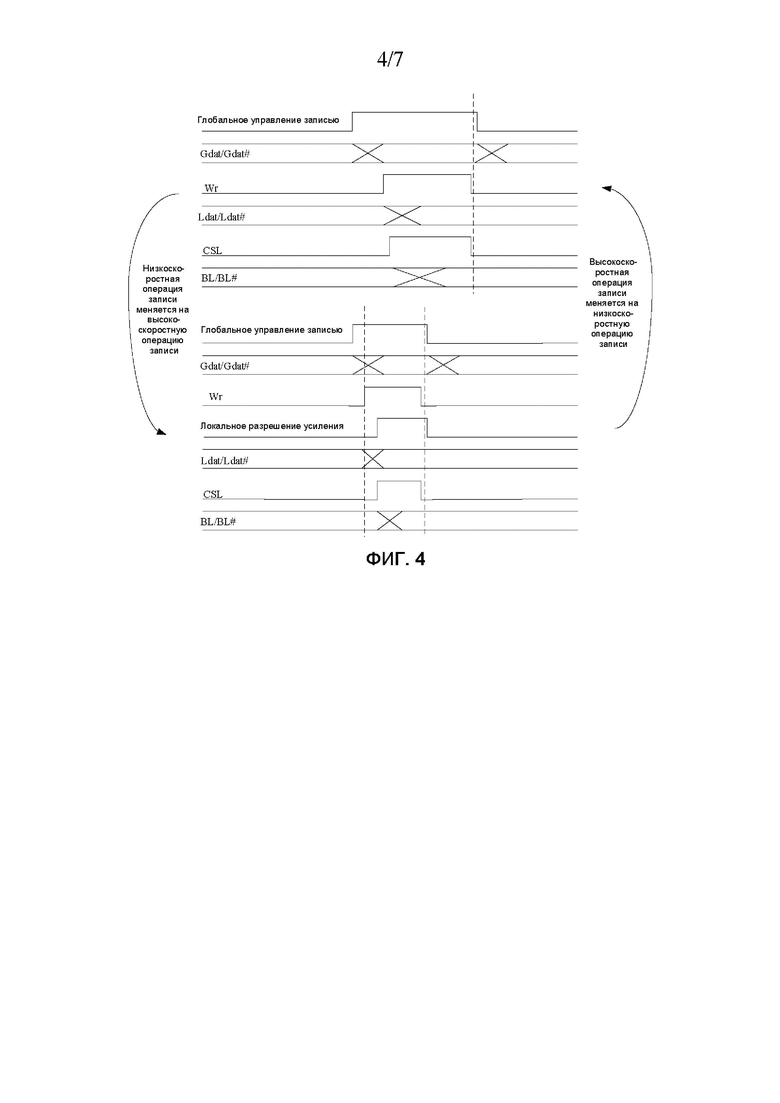

[0036] На ФИГ. 4 приведена диаграмма последовательности сигнала управления чтения-записи, соответствующего высокоскоростной операции записи и низкоскоростной операции записи в операции записи схемы преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

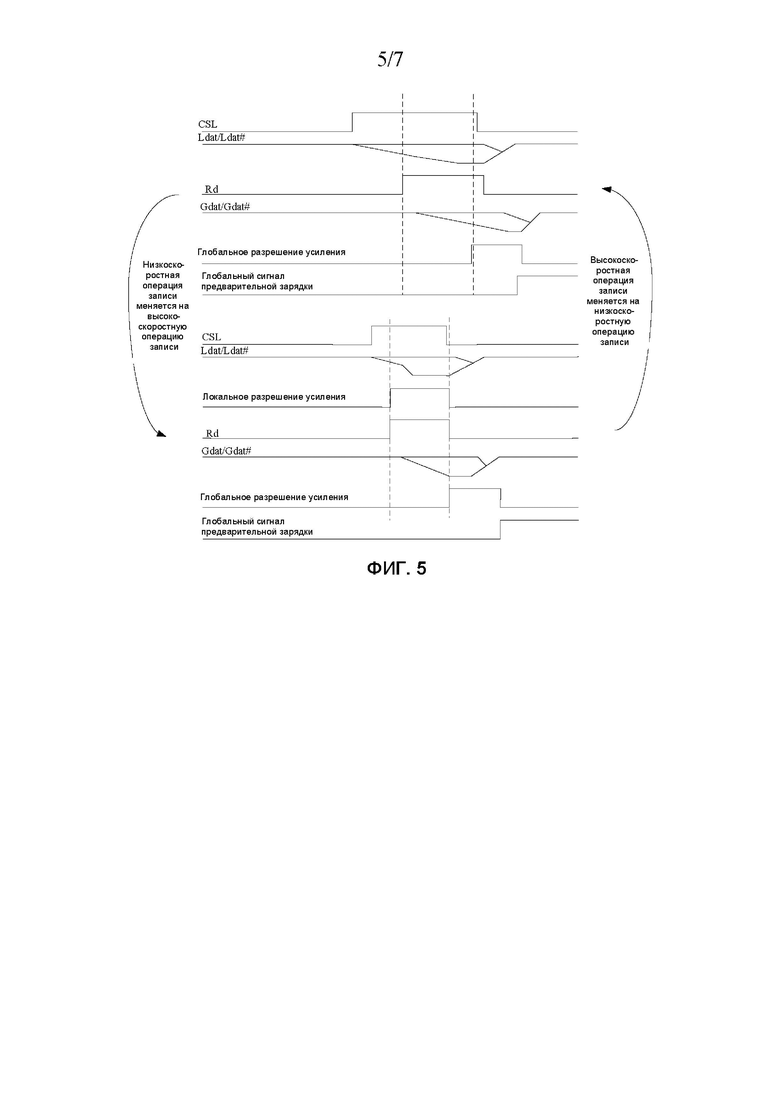

[0037] На ФИГ. 5 приведена диаграмма последовательности сигнала управления чтением-записью, соответствующего высокоскоростной операции чтения и низкоскоростной операции чтения в операции чтения схемы преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

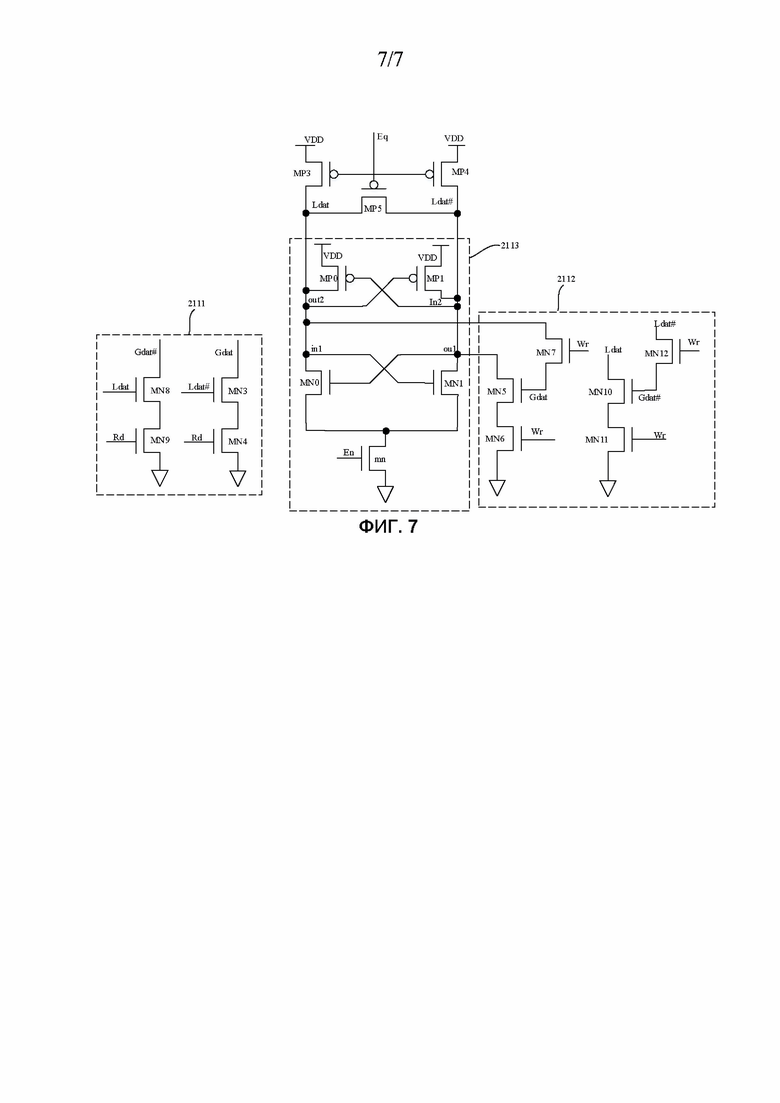

[0038] На ФИГ. 6 приведена принципиальная схема структуры схемы локального блока чтения-записи в схеме преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

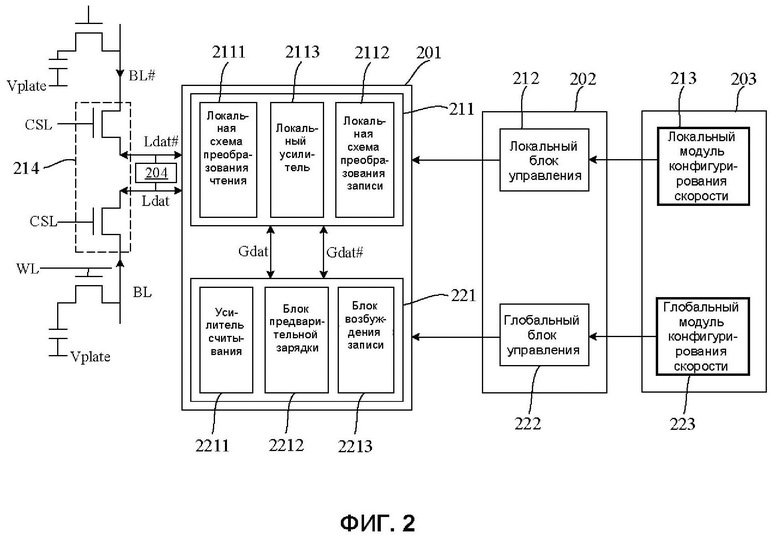

[0039] На ФИГ. 7 приведена принципиальная схема еще одной структуры схемы локального блока чтения-записи в схеме преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0040] В возможном варианте реализации для одного и того же DRAM скорость (включая скорость чтения и скорость записи) операции чтения-записи фиксирована. Поскольку скорость операции чтения-записи DRAM фиксирована, то если DRAM спроектирована для низкой скорости операции чтения-записи, трудно требовать от DRAM высокой скорости операции чтения-записи в некоторые периоды времени. С другой стороны, если DRAM спроектировано для фиксированной высокой скорости операций чтения-записи, то в периоды времени, когда DRAM имеет низкие скорости операций чтения-записи, фиксированная высокая скорость чтения-записи DRAM приведет к проблеме энергопотребления. Т.е. в настоящее время память сталкивается с проблемой фиксированной скорости операции чтения-записи и высокого потребления энергии.

[0041] Для решения вышеуказанной проблемы согласно вариантам реализации настоящего изобретения предложена схема преобразования чтения-записи, которая содержит модуль преобразования чтения-записи и модуль управления. Модуль управления выводит, в ответ на сигнал конфигурирования скорости чтения-записи, переменный сигнал управления чтением-записью для управления скоростью операции чтения-записи модуля преобразования чтения-записи таким образом, чтобы она была переменной. Таким образом, в соответствии с вариантами реализации настоящего изобретения скорость операции чтения-записи может быть сконфигурирована так, чтобы скорректировать скорость операции чтения-записи схемы преобразования чтения-записи до ожидаемой скорости, избегая ненужного потребления энергии схемы преобразования чтения-записи и улучшая рабочие характеристики схемы преобразования чтения-записи.

[0042] Чтобы сделать более понятными цели, технические решения и преимущества вариантов реализации настоящего изобретения, ниже будет подробно описан каждый вариант реализации изобретения в сочетании с чертежами. Однако специалисты в данной области могут отметить, что в каждом варианте реализации настоящего изобретения предложены множество технических подробностей, чтобы читатели лучше поняли изобретение. Тем не менее технические детали, заявленные в изобретении, могут быть также реализованы даже без этих технических подробностей, вариантов и модификаций, как объяснено в каждом из следующих вариантов реализации.

[0043] На ФИГ. 1 приведена принципиальная схема для схемы преобразования чтения-записи в соответствии с вариантом реализации настоящего изобретения.

[0044] Со ссылкой на ФИГ. 1, в этом варианте реализации схема преобразования чтения-записи одержит: модуль 101 преобразования чтения-записи, выполняющий операцию чтения-записи в ответ на сигнал управления чтением-записью; и модуль 102 управления, выводящий, в ответ на сигнал конфигурирования скорости чтения-записи, переменный сигнал управления чтением-записью для управления скоростью операции чтения-записи модуля 101 преобразования чтения-записи таким образом, чтобы она была переменной.

[0045] Схема преобразования чтения-записи, предложенная согласно этому варианту реализации, будет подробно описана ниже в сочетании с чертежами.

[0046] В этом варианте реализации схема преобразования чтения-записи может также содержать локальную линию Ldat данных, локальную комплементарную линию Ldat# данных и глобальную линию Gdat данных. Во время операции чтения-записи выполняется передача данных между каждой из локальной линии Ldat данных, локальной комплементарной линии Ldat# данных и глобальной линией Gdat данных, причем сигнал данных локальной линии Ldat данных и сигнал данных локальной комплементарной линии Ldat# данных противоположны по фазе.

[0047] В этом варианте реализации сигналы данных, считываемые или записываемые схемой преобразования чтения-записи, объединены в пару. Каждая пара сигналов данных содержит два фрагмента данных. В процессе операции чтения-записи один из двух фрагментов данных является сигналом высокого уровня, тогда как другой фрагмент данных является сигналом низкого уровня. Таким образом, схема преобразования чтения-записи содержит по меньшей мере одну пару из локальной линии Ldat данных и локальной комплементарной линии Ldat#, а двумя фрагментами данных являются соответственно данные локальной линии Ldat данных и данные локальной комплементарной линии Ldat# данных. В частности, во время операции чтения схемы преобразования чтения-записи данные передаются из локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в глобальную линию Gdat данных; а во время операции записи схемы преобразования чтения-записи данные передаются из глобальной линии Gdat данных в локальную линию данных Ldat и локальную комплементарную линию Ldat# данных.

[0048] Локальную линию Ldat данных также называют локальной линией данных, локальную комплементарную линию Ldat# данных также называют локальной комплементарной линией данных, а глобальную линию Gdat данных также называют глобальной линией данных.

[0049] В этом варианте реализации для глобальной линии Gdat данных схемы преобразования чтения-записи используют односторонний способ передачи, а именно: в схеме преобразования чтения-записи нет глобальной дополнительной линии, комплементарной глобальной линии Gdat данных по фазе сигнала данных.

[0050] Следует отметить, что еще в одном варианте реализации для глобальной линии данных схемы преобразования чтения-записи также может быть использован двусторонний способ передачи, а именно: схема преобразования записи может также содержать глобальную комплементарную линию записи, и во время операции чтения-записи сигнал данных глобальной комплементарной линии данных и сигнал данных глобальной линии данных противоположны по фазе.

[0051] В конкретном варианте реализации схему преобразования чтения-записи применяют к памяти. Память содержит модуль 100 выбора столбца и множество ячеек памяти. Локальная линия Ldat данных соединена с разрядной линией BL посредством модуля 100 выбора столбца, а локальная комплементарная линия Ldat# данных соединена с комплементарной разрядной линией BL# посредством модуля 100 выбора столбца. Ячейку памяти для операции чтения или операции записи выбирают посредством модуля 100 выбора столбца. Соответственно, сигналы передаются между разрядной линией BL, соединенной с выбранной ячейкой памяти, и локальной линией Ldat данных, и сигналы передаются между комплементарной разрядной линией BL#, соединенной с выбранной ячейкой памяти, и локальной комплементарной линией Ldat# данных.

[0052] Во время операции чтения модуль 101 преобразования чтения-записи передает данные локальной линии Ldat данных и данные локальной комплементарной линии Ldat# данных в глобальную линию Gdat данных; а во время операции записи модуль 101 преобразования чтения-записи передает данные из глобальной линии Gdat данных в локальную линию Ldat данных и локальную комплементарную линию Ldat# данных.

[0053] Сигнал управления чтением-записью содержит сигнал выбора столбца, локальный сигнал управления чтением-записью и глобальный сигнал управления чтением-записью. Локальный сигнал управления чтением-записью сконфигурирован для управления модулем 101 преобразования чтения-записи для выполнения локальной операции чтения-записи. Глобальный сигнал управления чтением-записью сконфигурирован для управления модулем 101 преобразования чтения-записи для выполнения глобальной операции чтения-записи.

[0054] Скорость сигнала управления чтением-записью влияет на скорость операции чтения-записи схемы преобразования чтения-записи. Например, если скорость сигнала управления чтением записью выше, то скорость операции чтения записи соответственно выше, а если скорость сигнала управления чтением-записью ниже, то скорость операции чтения-записи соответственно ниже.

[0055] Сигнал управления чтением-записью предоставляется модулем 102 управления, причем сигнал управления чтением-записью, выводимый модулем 102 управления, является переменным, в частности, скорость сигнала управления чтением-записью переменная. Сигнал конфигурирования скорости чтения-записи связан с ожидаемой скоростью операции чтения-записи. Когда скорость операции чтения-записи не соответствует ожидаемой, сигнал управления чтением-записью, выводимый модулем 102 управления, изменяется. Т.е. скорость сигнала управления чтением-записью изменяется, в результате чего изменяется скорость операции чтения-записи, выполняемой модулем 101 преобразования чтения-записи в ответ на измененный сигнал управления чтением-записью, что обеспечивает соответствие скорости чтения-записи операции чтения-записи ожидаемой скорости.

[0056] В конкретном варианте реализации, когда скорость операции чтения-записи, выполняемой модулем 101 преобразования чтения-записи в ответ на первый сигнал управления чтением-записью, ниже ожидаемой скорости, модуль 102 управления выводит второй сигнал управления чтением-записью в ответ на сигнал конфигурирования чтения-записи, чтобы увеличить скорость операции чтения-записи модуля 101 преобразования чтения-записи до ожидаемой скорости. Когда скорость операции чтения-записи, выполняемой модулем 101 преобразования чтения-записи в ответ на третий сигнал управления чтением-записью, выше ожидаемой скорости, модуль 102 управления выводит четвертый сигнал управления чтением-записью в ответ на сигнал конфигурирования чтения-записи, чтобы уменьшить скорость операции чтения-записи модуля 101 преобразования чтения-записи до ожидаемой скорости.

[0057] Поскольку скорость операции чтения-записи модуля 101 преобразования чтения-записи переменная, скорость операции чтения-записи модуля 101 преобразования чтения-записи может быть скорректирована в соответствии с практическими требованиями к рабочим характеристикам. Например, увеличение или уменьшение скорости передачи данных в операции чтения-записи может быть использовано для удовлетворения требований к рабочим характеристикам чтения-записи, а также снижения ненужного потребления энергии.

[0058] В этом варианте реализации схема преобразования чтения-записи может также содержать модуль 103 конфигурирования скорости, соединенный с модулем 102 управления и выполненный с возможностью вывода сигнала конфигурирования скорости чтения-записи в модуль 102 управления. Таким образом, модуль 103 конфигурирования скорости записи встроен в схему преобразования чтения-записи, чтобы способствовать уменьшению длины тракта передачи для передачи сигнала конфигурирования скорости чтения-записи модулю 102 управления и ускорения скорости отклика модуля 102 управления для более своевременного вывода скорректированного сигнала управления чтением-записью, чтобы быстрее достичь изменения скорости операции чтения-записи модуля 101 преобразования чтения-записи.

[0059] Сигнал управления чтением-записью содержать сигнал управления чтением и сигнал управления записью. Модуль 101 преобразования чтения-записи выполняет операцию чтения в ответ на сигнал управления чтением и выполняет операцию записи в ответ на сигнал управления записью. В этом варианте реализации модуль 102 управления выводит, в ответ на сигнал конфигурирования скорости чтения-записи, переменный сигнал управления чтением для управления скоростью операции чтения модуля 101 преобразования записи таким образом, чтобы она была переменной. Модуль 102 управления выводит, в ответ на сигнал конфигурирования скорости чтения-записи, переменный сигнал управления записью для управления скоростью операции записи модуля 101 преобразования чтения-записи таким образом, чтобы она была переменной.

[0060] Соответственно, сигнал конфигурирования скорости чтениям-записи содержит сигнал конфигурирования скорости чтения и сигнал конфигурирования скорости записи. Модуль 103 конфигурирования скорости содержит: блок 113 конфигурирования скорости чтения, выполненный с возможностью вывода сигнала конфигурирования скорости чтения в сигнале конфигурирования скорости чтения-записи в модуль 102 управления, который затем в ответ на сигнал конфигурирования скорости чтения выводит переменный сигнал управления чтением для управления скоростью операции чтения таким образом, чтобы она была переменной; блок 123 конфигурирования скорости записи, выполненный с возможностью вывода сигнала конфигурирования скорости записи в сигнале конфигурирования скорости чтения-записи в модуль 102 управления, который затем в ответ на сигнал конфигурирования скорости записи выводит переменный сигнал управления записью для управления скоростью операции записи таким образом, чтобы она была переменной

[0061] Следует отметить, что модуль конфигурирования скорости может также содержать локальный модуль конфигурирования скорости и глобальный модуль конфигурирования скорости. Локальный модуль конфигурирования скорости выполнен с возможностью вывода локального сигнала конфигурирования скорости чтения в модуль управления для управления скоростью локальной операции чтения-записи модуля преобразования чтения-записи таким образом, чтобы она была переменной. Глобальный модуль конфигурирования скорости выполнен с возможностью вывода глобального сигнала конфигурирования скорости чтения-записи в модуль управления для управления скоростью глобальной операции чтения-записи модуля преобразования чтения-записи таким образом, чтобы она была переменной.

[0062] Также следует отметить, что другом варианте реализации модуль конфигурирования скорости может быть также снабжен другой схемой помимо схемы преобразования чтения-записи.

[0063] Согласно схеме преобразования чтения-записи, приведенной в этом варианте реализации, модуль 102 управления выводит переменный сигнал управления чтением-записью, чтобы сделать переменной скорость операции чтения-записи модуля 101 преобразования чтения-записи. Это позволяет применять схему преобразования чтения-записи к большему количеству сценариев, например, применять не только к высокоскоростной операции чтения-записи, но и к низкоскоростной операции чтения-записи. Кроме того, это решает проблему высокого потребления энергии, вызываемого длительным пребыванием в состоянии высокоскоростной операции чтения-записи.

[0064] В еще одном варианте реализации настоящего изобретения также предложена схема преобразования чтения-записи. Эта схема преобразования чтения-записи по существа такая же, как и схема преобразования чтения-записи, предложенная в предыдущем варианте реализации. Разница в том, что в этом варианте реализации модуль преобразования чтения-записи и модуль управления описаны более подробно. Схема преобразования чтения-записи, предложенная согласно этому варианту реализации, будет подробно описана ниже в сочетании с чертежами. Описание деталей, которые совпадают с деталями предыдущего варианта реализации или соответствуют им, см. в подробных описаниях в предыдущем варианте реализации.

[0065] На ФИГ. 2 показана схема преобразования чтения-записи в соответствии еще с одним вариантом реализации настоящего изобретения.

[0066] Со ссылкой на ФИГ. 2, схема преобразования чтения-записи содержит локальную линию Ldat данных, локальную комплементарную линию Ldat# данных, глобальную линию Gdat данных, глобальную комплементарную линию Gdat# данных, модуль 201 преобразования чтения-записи и модуль 202 управления. Модуль 201 преобразования чтения-записи выполняет операцию чтения-записи в ответ на сигнал управления чтением-записью, чтобы реализовать передачу данных между каждой из локальной линии Ldat данных и локальной комплементарной линии Ldat# данных и каждой из глобальной линии Gdat и глобальной комплементарной линии Gdat# данных. Во время операции чтения-записи сигналы данных локальной линии Ldat данных и локальной комплементарной линии Ldat# данных противоположны по фазе, и сигналы данных глобальной линией Gdat данных и глобальной комплементарной линии Gdat# данных противоположны по фазе.

[0067] Следует отметить, что еще в одном варианте реализации в схеме преобразования чтения-записи может быть не предусмотрена глобальная комплементарная линия данных или предусмотрена только глобальная линия данных. Подробнее см. в предыдущем варианте реализации.

[0068] В этом варианте реализации модуль 201 преобразования чтения-записи содержит локальный блок 211 чтения-записи, выполняющий локальную операцию чтения-записи в ответ на локальный сигнал управления чтением-записью в сигнале управления чтением-записью. Локальный сигнал управления чтением-записью содержит локальный сигнал Rd чтения и локальный сигнал разрешения усиления.

[0069] Соответственно, модуль 202 управления содержит локальный блок 212 управления, выводящий, в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменный локальный сигнал управления чтением-записью для управления скоростью локальной операции чтения-записи в локальном блоке 211 чтения-записи таким образом, чтобы она была переменной.

[0070] Таким образом, скорость локальной операции чтения-записи в схеме преобразования чтения-записи является переменной. В частности, скорость локальной операции чтения в локальной операции чтения-записи является переменной, и скорость локальной операции записи в локальной операции чтения-записи также является переменной. Например, локальная операция чтения может быть изменена с высокоскоростного чтения на низкоскоростное чтение или изменена с низкоскоростного чтения на высокоскоростное чтение. Локальная операция записи может быть изменена с высокоскоростной записи на низкоскоростную запись или изменена с низкоскоростной записи на высокоскоростную запись. Поскольку скорость локальной операции чтения-записи является переменной, скорость локальной операции чтения-записи может быть скорректирована по мере практической необходимости для удовлетворения требования к скорости передачи данных и, одновременно, для обеспечения преимущества низкого потребления энергии схемы преобразования чтения-записи.

[0071] В этом варианте реализации схема преобразования чтения-записи может также содержать локальный модуль 213 конфигурирования скорости, соединенный с локальным модулем 212 управления и выполненный с возможностью вывода локального сигнала конфигурирования скорости чтения-записи в локальный модуль 212 управления, чтобы сделать регулируемым локальный сигнал управления чтением-записью, выводимый локальным блоком 212 управления.

[0072] Следует отметить, что еще в одном варианте реализации локальный сигнал конфигурирования скорости чтения-записи может также предоставляться локальному блоку управления внешней схемой, т. е. схема преобразования чтения-записи не нуждается в локальном модуле конфигурирования скорости.

[0073] Схема преобразования чтения-записи может также содержать усилитель 214 считывания. Усилитель 214 считывания соединен с локальным блоком 211 чтения-записи посредством локальной линии Ldat данных и локальной комплементарной линии Ldat# данных и выполнен с возможностью считывания напряжений разрядной линии BL и комплементарной разрядной линии BL#.

[0074] Разрядная линия BL соединена с локальной линией Ldat данных посредством усилителя 214 считывания, и комплементарная разрядная линия BL# соединена с локальной комплементарной линией Ldat# данных посредством того же усилителя 214 считывания.

[0075] В этом варианте реализации усилитель 214 считывания принимает сигнал CSL выбора столбца. Усилитель 214 считывания содержит два nМОП-транзистора (не отмечены), и затворы nМОП-транзисторов принимают сигнал CSL выбора столбца. Один nМОП-транзистор соединяется с разрядной линией BL и локальной линией Ldat данных в ответ на сигнал CSL выбора столбца, тогда как другой nМОП-транзистор соединяется с комплементарной разрядной линией BL# и локальной комплементарной линией Ldat# данных в ответ на сигнал CSL выбора столбца. В частности, когда nМОП-транзистор принимает сигнал CSL выбора столбца и включается, разрядная линия BL соединяется с локальной линией Ldat данных, а комплементарная разрядная линия BL# соединяется с локальной комплементарной линией Ldat# данных. Когда nМОП-транзистор прекращает прием сигнала CSL выбора столбца, разрядная линия BL отсоединяется от локальной линии Ldat данных, а комплементарная разрядная линия BL# отсоединяется от локальной комплементарной линии Ldat# данных.

[0076] Понятно, что в другом варианте реализации усилитель считывания может содержать любое количество транзисторов, например, множество nМОП-транзисторов и/или множество pМОП-транзисторов. В качестве усилителя считывания может быть использовано любое устройство, выполненное с возможностью реализации функции усилителя считывания.

[0077] Разрядная линия BL соединена с запоминающим транзистором (не отмечен). Затвор запоминающего транзистора соединен с числовой линией WL. Один вывод запоминающего транзистора соединен с разрядной линией BL, тогда как другой вывод соединен с напряжением Vplate через конденсатор (не отмечен). Комплементарная разрядная линия BL# соединена с управляющим транзистором (не отмечен). Один вывод управляющего транзистора соединен с комплементарной разрядной линией BL#, тогда как другой вывод соединен с напряжением Vplate.

[0078] Кроме того, один и тот же локальный блок 211 чтения-записи может быть соединен с множеством усилителей 214 считывания посредством локальной линии Ldat данных и локальной комплементарной линией данных Ldat#. Для удобства иллюстрации и описания на ФИГ. 2 показан только один усилитель 214 считывания.

[0079] В этом варианте реализации схему преобразования чтения-записи применяют к памяти. Тракт данных записи проходит от локального блока 211 чтения-записи к усилителю считывания через локальную линию Ldat данных и через локальную комплементарную линию Ldat# данных, а затем к разрядной линии BL и комплементарной разрядной линии BL# через усилитель 214 считывания. Тракт данных чтения проходит от разрядной линии к локальной линии Ldat данных и локальной комплементарной линии Ldat# данных через усилитель 214 считывания, а затем к локальному блоку 211 чтения-записи через локальную линию Ldat данных и локальную комплементарную линию Ldat# данных.

[0080] В этом варианте реализации модуль 201 преобразования чтения-записи также содержит глобальный блок 221 чтения-записи, выполняющий глобальную операцию чтения-записи в ответ на глобальный сигнал управления чтением-записью в сигнале управления чтением-записью.

[0081] Модуль 202 управления содержит глобальный блок 222 управления, выводящий, в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменный глобальный сигнал управления чтением-записью, чтобы поддерживать переменной скорость глобальной операции чтения-записи в глобальном блоке 221 чтения-записи. Таким образом, скорость глобальной операции чтения-записи в схеме преобразования чтения-записи является переменной. В частности, скорость глобальной операции чтения в глобальной операции чтения-записи является переменной, и скорость глобальной операции записи в глобальной операции чтения-записи является переменной.

[0082] Т.е. в этом варианте реализации переменной является не только скорость локальной операции чтения-записи, но и скорость глобальной операции чтения-записи.

[0083] Следует отметить, что еще в одном варианте реализации модуль управления может содержать только один из локального блока управления или глобального блока управления, и, соответственно, переменной является только скорость локальной операции чтения-записи или переменной является только скорость глобальной операции чтения-записи.

[0084] Соответственно, схема преобразования чтения-записи может также содержать глобальный модуль 223 конфигурирования скорости, соединенный с глобальным блоком 222 управления и выполненный с возможностью вывода глобального сигнала конфигурирования скорости чтения-записи в глобальный блок 222 управления.

[0085] Локальный модуль 213 конфигурирования скорости и глобальный модуль 223 конфигурирования скорости могут быть встроены в один модуль 203 конфигурирования скорости. Модуль 203 конфигурирования скорости выполнен с возможностью вывода локального сигнала конфигурирования скорости чтения-записи в локальный блок 212 управления и также выполнен с возможностью вывода глобального сигнала конфигурирования скорости чтения-записи в глобальный блок 222 управления.

[0086] Понятно, что в другом варианте реализации глобальный сигнал конфигурирования скорости чтения-записи может также предоставляться глобальному блоку управления внешней схемой, т.е. схема преобразования чтения-записи не нуждается в глобальном модуле конфигурирования скорости.

[0087] На ФИГ. 3 показана еще одна схема преобразования чтения-записи в соответствии еще с одним вариантом реализации. Со ссылкой на ФИГ. 3, еще в одном примере схема преобразования чтения-записи может также содержать блок 243 конфигурирования скорости чтения, выполненный с возможностью вывода сигнала конфигурирования скорости чтения в сигнале конфигурирования скорости чтения-записи в локальный блок 212 управления и глобальный блок 222 управления. Это вызывает вывод локальным блоком 212 управления, в ответ на сигнал конфигурирования скорости чтения, переменного локального сигнала управления чтением для управления скоростью локальной операции чтения таким образом, чтобы она была переменной. Кроме того, это вызывает вывод глобальным блоком 222 управления, в ответ на сигнал конфигурирования скорости чтения, переменного глобального сигнала управления чтением для управления скоростью глобальной операции чтения таким образом, чтобы она была переменной. Схема преобразования чтения-записи может также содержать блок 253 конфигурирования скорости записи, выполненный с возможностью вывода сигнала конфигурирования скорости записи в сигнале конфигурирования скорости чтения-записи в локальный блок 212 управления и глобальный блок 222 управления, вызывающего вывод локальным блоком 212 управления переменного сигнала управления записью в ответ на сигнал конфигурирования скорости записи для управления скоростью локальной операции записи таким образом, чтобы она была переменной. Это вызывает вывод глобальным блоком 222 управления, в ответ на сигнал конфигурирования скорости записи, переменного глобального сигнала управления записью для управления скоростью глобальной операции записи таким образом, чтобы она была переменной. Блок 243 конфигурирования скорости считывания и блок 253 конфигурирования скорости записи могут быть встроены в один модуль 203 конфигурирования скорости. Описания модуля 203 конфигурирования скорости приведено в вышеупомянутом варианте реализации.

[0088] В случае схемы преобразования чтения-записи с глобальным блоком 221 чтения-записи тракт данных записи проходит к глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных через глобальный блок 221 чтения-записи, затем к глобальному блоку 211 чтения-записи через глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных, от локального блока 211 чтения-записи к усилителю 214 считывания через локальную линию Ldat данных и локальную комплементарную линию Ldat# данных, а затем к разрядной линии BL и комплементарной разрядной линии BL# через усилитель 214 считывания.

[0089] В случае схемы преобразования чтения-записи с глобальным блоком 221 чтения-записи тракт данных чтения проходит от разрядной линии BL и комплементарной разрядной линии BL# к локальной линии Ldat данных и локальной комплементарной линии Ldat# данных через усилитель 214 считывания, затем к локальному блоку 211 чтения-записи через локальную линию Ldat данных и локальную комплементарную линию Ldat# данных, затем к глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных через локальный блок 211 чтения-записи и, наконец, к глобальному блоку 221 чтения-записи через глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных.

[0090] Со ссылкой на Фиг. 2 и ФИГ. 3, в этом варианте реализации локальный блок 211 чтения-записи содержит локальную схему 2111 преобразования чтения, которая выполнена с возможностью передачи данных локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных в ответ на локальный сигнал чтения в локальном сигнале чтения-записи.

[0091] Модуль 202 управления выводит локальный сигнал управления чтением и переменный локальный сигнал управления чтением в ответ на сигнал конфигурирования скорости чтения-записи для коррекции скорости чтения локальной схемы 2111 преобразования чтения, делая скорость локальной операции чтения модуля 201 преобразования чтения-записи переменной.

[0092] Локальный блок 211 чтения-записи также содержит локальную схему 2112 преобразования записи, выполненную с возможностью передачи данных глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных в локальную линию Ldat данных и локальную комплементарную линию Ldat# данных в ответ на локальный сигнал записи в локальном сигнале чтения-записи.

[0093] Модуль 202 управления выводит локальный сигнал управления записью и модуль 202 управления выводит переменный локальный сигнал управления записью в ответ на сигнал конфигурирования скорости чтения-записи для коррекции скорости записи локальной схемы 2112 преобразования записи, чтобы также сделать переменной скорость локальной операции записи модуля 201 преобразования чтения-записи.

[0094] Блок 211 чтения-записи также содержит локальный усилитель 2113, соединенный между локальной линией Ldat данных и локальной комплементарной линией Ldat# данных и выполненный с возможностью усиления данных локальной линии Ldat данных и данных локальной комплементарной линии Ldat# данных.

[0095] Модуль 202 управления выводит переменный локальный сигнал управления чтением или локальный сигнал управления записью, чтобы сделать переменной скорость усиления локального усилителя 2113, так что скорости локальной операции чтения и локальной операции записи модуля 201 преобразования считывания-записи могут быть изменены до определенной степени.

[0096] Локальный усилитель 2113 образует схему для усиления сигнала локальной линии Ldat данных и сигнала локальной комплементарной линии Ldat# данных и помогает ускорить различение между уровнем локальной линии Ldat данных и уровнем локальной комплементарной линии Ldat# данных, тем самым увеличивая скорость передачи сигнала данных и улучшая скорость чтения-записи. Кроме того, поскольку сигналы данных локальной линии Ldat данных и локальной комплементарной линии Ldat# данных усилены, локальная линия Ldat данных и локальная комплементарная линия Ldat# данных имеют пониженные требования к возбуждающей способности усилителя считывания в памяти. Таким образом, даже если площадь усилителя считывания постепенно уменьшается, усилитель считывания имеет достаточную возбуждающую способность, чтобы локальная линия Ldat данных и локальная комплементарная линия Ldat# данных удовлетворяли тенденции к миниатюризации устройства при одновременном обеспечении высоких электрических характеристик схемы преобразования чтения-записи, тем самым улучшая эффективность хранения памяти, содержащей схему преобразования чтения-записи.

[0097] Глобальный блок 221 чтения-записи содержит усилитель 2211 считывания, блок 2212 предварительной зарядки и блок 2213 возбуждения записи. Усилитель 2211 считывания может усиливать сигнал данных глобальной линии Gdat данных и сигнал данных глобальной комплементарной линии Gdat# данных. Блок 2212 предварительной зарядки может предварительно заряжать глобальную линию данных Gdat и глобальную комплементарную линию Gdat# данных.

[0098] Модуль 202 управления выводит переменный глобальный сигнал управления чтением для коррекции скорости глобальной операции чтения или глобальной операции записи глобального блока 221 чтения-записи так, чтобы коррекция скорости усиления усилителя 2211 считывания, скорости предварительной зарядки блока 2212 предварительной зарядки и скорости возбуждения блока 2213 возбуждения записи достигала цели изменения глобальной операции чтения-записи модуля 201 преобразования чтения-записи.

[0099] Со ссылкой на ФИГ. 2, в этом варианте реализации схема преобразования чтения-записи может также содержать схему 204 предварительной зарядки. Схема 204 предварительной зарядки подсоединена между локальной линией Ldat данных и локальной комплементарной линией Ldat# данных и выполнена с возможностью предварительной зарядки локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в ответ на сигнал управления предварительной зарядкой.

[00100] На ФИГ. 4 приведена схема последовательности сигнала управления чтения-записи, соответствующего высокоскоростной операции записи и низкоскоростной операции записи в операции записи схемы преобразования чтения-записи в соответствии с этим вариантом реализации. На ФИГ. 5 приведена схема последовательности сигнала управления чтения-записи, соответствующего высокоскоростной операции чтения и низкоскоростной операции чтения в операции чтения схемы преобразования чтения-записи в соответствии с этим вариантом реализации. На ФИГ. 4 и ФИГ. 5 также показаны сигнал разрядной линии/комплементарной разрядной линии (BL/BL#), сигнал глобальной линии данных/глобальной комплементарной линии данных (Gdat/Gdat#) и сигнал локальной линии данных/локальной комплементарной линии данных (Ldat/Ldat#). Понятно, что высокая скорость и низкая скорость являются относительными.

[00101] Со ссылкой на ФИГ. 4, при выполнении операции записи сигнал управления чтением-записью содержит глобальный сигнал управления записью, сигнал CSL выбора столбца, локальный сигнал Wr записи и локальный сигнал разрешения усиления. Понятно, что при выполнении низкоскоростной операции записи уровень локального разрешения усиления может быть равен 0, и, таким образом, низкоскоростная операция записи соответствует схеме последовательности, на которой не показано локальное разрешение усиления.

[00102] Из ФИГ. 4 легко увидеть, что когда высокоскоростная операция записи меняется на низкоскоростную операцию записи, скорость сигнала управления чтением-записью уменьшается, скорости передачи данных глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных уменьшаются, и скорости передачи данных локальной линии Ldat данных и локальной комплементарной линии Ldat# данных уменьшаются, а когда низкоскоростная операция записи меняется на высокоскоростную операцию записи, скорость сигнала управления чтением-записью увеличивается, скорости передачи данных глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных увеличиваются, и скорости передачи данных локальной линии Ldat данных и локальной комплементарной Ldat# линии данных увеличиваются.

[00103] Кроме того, на ФИГ. 4 показана только схема последовательности каждого сигнала управления чтением-записью в течение одного тактового периода. Если исходить из всего тактового периода, то когда низкоскоростная операция записи меняется на высокоскоростную операцию записи, скорость сигнала управления записью в соответствующем сигнале управления чтением-записью увеличивается, а когда высокоскоростная операция записи меняется на низкоскоростную операцию записи, скорость сигнала управления записью в соответствующем сигнале управления чтением-записью уменьшается.

[00104] Со ссылкой на ФИГ. 5, когда выполняется операция чтения, сигнал управления чтением-записью содержит сигнал CSL выбора столбца, локальный сигнал Rd чтения, глобальное разрешение усиления, глобальный сигнал предварительной зарядки и локальное разрешение усиления. Понятно, что при выполнении низкоскоростной операции чтения уровень локального разрешения усиления может быть равен 0, и, таким образом, низкоскоростная операция чтения соответствует схеме последовательности, на которой не показано локальное разрешение усиления. Из ФИГ. 5 легко увидеть, что: когда высокоскоростная операция чтения меняется на низкоскоростную операцию чтения, скорость сигнала управления чтением-записью уменьшается, скорости передачи данных локальной Ldat данных и локальной комплементарной линии Ldat# данных уменьшаются, и скорости передачи данных глобальной линии Gdat данных и локальной комплементарной линии Gdat# данных уменьшаются; а когда низкоскоростная операция чтения меняется на высокоскоростную операцию чтения, скорость сигнала управления чтением-записью увеличивается, скорости передачи данных локальной линии Ldat данных и глобальной комплементарной линии Ldat# данных увеличиваются, и скорости передачи данных глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных увеличиваются.

[00105] На ФИГ. 5 показана только схема последовательности каждого сигнала управления чтением-записью в течение одного тактового периода. Если исходить из всего тактового периода, то когда низкоскоростная операция чтения меняется на высокоскоростную операцию чтения, скорость сигнала управления чтением в соответствующем сигнале управления чтением-записью увеличивается, а когда высокоскоростная операция чтения меняется на низкоскоростную операцию чтения, скорость сигнала управления чтением в соответствующем сигнале управления чтением-записью уменьшается.

[00106] Следует отметить, что на ФИГ. 4 и ФИГ. 5 показаны только некоторые общие сигналы управления, влияющие на скорость операции чтения-записи, а в практических схемах в соответствии с другими схемными решениями могут быть другие сигналы управления чтением-записью, влияющие на скорость операции чтения-записи.

[00107] В частности, ниже в сочетании с чертежами будет описана структура схемы локального блока чтения-записи в схеме преобразования чтения-записи, предложенной в данном варианте реализации.

[00108] На ФИГ. 6 приведена принципиальная схема структуры схемы локального блока чтения-записи в схеме преобразования чтения-записи в соответствии с этим вариантом реализации. На ФИГ. 7 приведена принципиальная схема еще одной структуры схемы локального блока чтения-записи в схеме преобразования чтения-записи в соответствии с этим вариантом реализации.

[00109] Со ссылкой на ФИГ. 6, для глобальной линии Gdat данных используется односторонний способ передачи, т.е. схема преобразования чтения-записи не содержит глобальной комплементарной линии данных. Локальный блок 211 чтения-записи содержит локальную схему 2111 преобразования чтения, выполненную с возможностью передачи данных локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в глобальную линию Gdat в ответ на локальный сигнал управления чтением в локальном сигнале управления чтением-записью.

[00110] В этом варианте реализации локальная схема 2111 преобразования чтения содержит третий nМОП-транзистор MN3 и четвертый nМОП-транзистор MN4. Сток третьего nМОП-транзистора MN3 соединен с глобальной линией Gdat данных, затвор третьего nМОП-транзистора MN3 соединен с локальной комплементарной линией Ldat# данных, а исток третьего nМОП-транзистора MN3 соединен со стоком четвертого nМОП-транзистора MN4. Затвор четвертого nМОП-транзистора MN4 принимает локальный сигнал Rd чтения в локальном сигнале управления чтением, тогда как исток заземлен.

[00111] Понятно, что локальная схема 2111 может быть также другой подходящей преобразованной схемой. Например, затвор четвертого nМОП-транзистора соединен с локальной комплементарной линией данных, а затвор третьего nМОП-транзистора принимает локальный сигнал чтения.

[00112] Еще в одном примере, со ссылкой на ФИГ. 7, для глобальной линии Gdat данных также может быть использован двусторонний способ передачи, а именно: схема преобразования чтения-записи содержит глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных. Во время операции чтения сигналы данных глобальной комплементарной линии Gdat# данных и глобальной линии Gdat данных противоположны по фазе. Соответственно, помимо вышеупомянутого третьего nМОП-транзистора MN3 и четвертого nМОП-транзистора MN4 локальная схема 2111 преобразования чтения также содержит восьмой nМОП-транзистор MN8 и девятый nМОП-транзистор MN9. Сток восьмого nМОП-транзистора MN8 соединен с глобальной комплементарной линией Gdat# данных, затвор девятого nМОП-транзистора MN8 соединен с локальной линией Ldat данных, а исток восьмого nМОП-транзистора MN8 соединен со стоком девятого nМОП-транзистора MN9. Затвор девятого nМОП-транзистора MN9 принимает локальный сигнал Rd чтения, тогда как исток заземлен.

[00113] Локальный блок 211 чтения-записи содержит локальную схему 2112 преобразования записи, выполненную с возможностью передачи данных глобальной линии Gdat данных в локальную линию Ldat данных и локальную комплементарную линию Ldat# данных в ответ на локальный сигнал записи в локальном сигнале чтения-записи.

[00114] В этом варианте реализации локальная схема 2112 преобразования записи содержит пятый nМОП-транзистор MN5, шестой nМОП-транзистор MN6 и седьмой nМОП-транзистор MN7. Сток пятого nМОП-транзистора MN5 соединен с локальной комплементарной линией Ldat# данных, затвор пятого nМОП-транзистора MN5 соединен с истоком седьмого nМОП-транзистора MN7, а исток пятого nМОП-транзистора MN5 соединен со стоком шестого nМОП-транзистора MN6. Затвор шестого nМОП-транзистора MN6 принимает локальный сигнал Wr записи в локальном сигнале управления чтением, тогда как исток заземлен. Сток седьмого nМОП-транзистора MN7 соединен с локальной линией Ldat данных, тогда как затвор принимать локальный сигнал Wr записи.

[00115] Еще в одном примере, со ссылкой на ФИГ. 7, схема 211 преобразования чтения-записи также содержит глобальную комплементарную линию Gdat# данных. Во время операции чтения сигналы данных глобальной комплементарной линии Gdat# данных и глобальной линии Gdat данных противоположны по фазе. Помимо вышеупомянутых пятого nМОП-транзистора MN5, шестого nМОП-транзистора MN6 и седьмого nМОП-транзистора MN7 локальная схема 2112 преобразования записи содержит десятый nМОП-транзистор MN10, одиннадцатый nМОП-транзистор MN11 и двенадцатый nМОП-транзистор MN12. Сток десятого nМОП-транзистора MN10 соединен с локальной линией Ldat данных, затвор десятого nМОП-транзистора MN10 соединен с истоком двенадцатого nМОП-транзистора MN12 и глобальной комплементарной линией Gdat# данных, а исток десятого nМОП-транзистора MN10 соединен со стоком одиннадцатого nМОП-транзистора MN11. Затвор одиннадцатого nМОП-транзистора MN11 принимает локальный сигнал Wr записи, тогда как исток заземлен. Сток двенадцатого nМОП-транзистора MN12 соединен с локальной комплементарной линией Ldat# данных, тогда как затвор принимает локальный сигнал Wr записи.

[00116] Локальный усилитель 2113 содержит: первый фазоинвертор 21, причем первый вход первого фазоинвертора электрически соединен с локальной линией Ldat данных, а первый выход out1 первого фазоинвертора электрически соединен с локальной комплементарной линией Ldat# данных; и второй фазоинвертор 22, причем второй вход in2 второго фазоинвертора 22 электрически соединен со вторым выходом out2 первого фазоинвертора 21 и локальной комплементарной линией Ldat# данных, а второй выход out2 второго фазоинвертора 22 электрически соединен с первым входом in1 первого фазоинвертора 21 и локальной линией Ldat данных.

[00117] В частности, первый фазоинвертор 21 содержит первый pМОП-транзистор MP1 и первый nМОП-транзистор MN1. Затвор первого pМОП-транзистора MP1 электрически соединен с затвором первого nМОП-транзистора MN1, чтобы служить первым входом in1 первого фазоинвертора, исток первого pМОП-транзистора MP1 соединен с рабочим питанием VDD, а сток первого pМОП-транзистора MP1 соединен со стоком первого nМОП-транзистора MN1, чтобы служить первым выходом out1 первого фазоинвертора 21.

[00118] Второй фазоинвертор 22 содержит нулевой pМОП-транзистор MP0 и нулевой nМОП-транзистор MN0. Затвор нулевого pМОП-транзистора MP0 электрически соединен с затвором нулевого nМОП-транзистора MN0, чтобы служить вторым входом in2 второго фазоинвертора 22, исток нулевого pМОП-транзистора MP0 соединен с рабочим питанием VDD, а сток нулевого pМОП-транзистора MP0 соединен со стоком нулевого nМОП-транзистора MN0, чтобы служить вторым выходом out2 второго фазоинвертора 22.

[00119] Первый pМОП-транзистор MP1, первый nМОП-транзистор MN1, нулевой pМОП-транзистор MP0 и нулевой nМОП-транзистор MN0 образуют локальный усилитель 2113.

[00120] Кроме того, локальный усилитель 2113 также содержит разрешающий nМОП-транзистор mn. Первый фазоинвертор 21 и второй фазоинвертор 22 также соединены со стоком разрешающего nМОП-транзистора mn. Сток разрешающего nМОП-транзистора mn заземлен, тогда как затвор принимает локальный разрешающий сигнал En. В частности, исток первого nМОП-транзистора MN1 соединен с истоком нулевого nМОП-транзистора MN0 и стоком шестого nМОП-транзистора MN6. В некоторых других вариантах реализации исток первого nМОП-транзистора MN1 заземлен, и исток нулевого nМОП-транзистора MN0 заземлен.

[00121] За счет структуры локального усилителя 2113 скорость передачи данных из разрядной линии BL в локальную линию Ldat данных увеличивается, скорость передачи данных из комплементарной разрядной линии BL# в локальную комплементарную линию Ldat# данных увеличивается, и требования по возбуждению памяти, предъявляемые к усилителю считывания, снижаются. В частности, предположим в качестве примера, что данные разрядной линии BL находятся на высоком уровне, а данные комплементарной разрядной линии BL# данных находятся на низком уровне. Поскольку первый вход in1 первого фазоинвертора 21 соединен со вторым выходом out2 второго фазоинвертора 22, а первый выход out1 первого фазоинвертора 21 соединен со вторым входом in2 второго фазоинвертора 22, во время передачи из разрядной линии BL и комплементарной разрядной линии BL# в локальную линию Ldat данных и локальную комплементарную линию Ldat# данных, структура схемы усилителя 2113 можете быстрее понизить напряжение локальной комплементарной линии Ldat# данных с более низким напряжением до «0» или может быстрее повысить напряжение локальной линии Ldat данных с более высоким напряжением до «1». Следовательно, скорость повышения напряжения локальной линии Ldat# данных увеличивается, и скорость понижения напряжения локальной комплементарной линии Ldat# данных тоже увеличивается. Более того, локальная линия Ldat данных и локальная комплементарная линия Ldat# данных предъявляют пониженные требования к возбуждению усилителя считывания.

[00122] Кроме того, поскольку локальная линия Ldat данных и локальная комплементарная линия Ldat# могут быстрее достичь высоких уровней или низких уровней, передача из локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных может быть реализована раньше. Таким образом, при чтении данных скорость передачи из локальной линии Ldat данных и локальной комплементарной линии Ldat# данных в глобальную линию Gdat данных и глобальную комплементарную линию Gdat# данных увеличивается.

[00123] Соответственно, во время операции записи локальный усилитель 2113 может также усилить локальную линию Ldat данных и локальную комплементарную линию Ldat# данных для увеличения скорости передачи данных из глобальной линии Gdat данных и глобальной комплементарной линии Gdat# данных в локальную линию Ldat данных и комплементарную линию Ldat# данных.

[00124] В этом варианте реализации схема 204 предварительной зарядки содержит третий pМОП-транзистор MP3, четвертый pМОП-транзистор MP4 и пятый pМОП-транзистор MP5. Затвор третьего pМОП-транзистора MP3, затвор четвертого pМОП-транзистора MP4 и затвор пятого pМОП-транзистора MP5 принимают сигнал Eq управления предварительной зарядкой. Исток третьего pМОП-транзистора MP3 и исток четвертого pМОП-транзистора MP4 соединены с рабочим питанием VDD, сток третьего pМОП-транзистора MP3 электрически соединен с локальной линией Ldat данных, а сток четвертого pМОП-транзистора MP4 электрически соединен с локальной комплементарной линией Ldat# данных. Пятый pМОП-транзистор MP5 электрически соединяется с локальной линией Ldat данных и локальной комплементарной линией Ldat# данных в ответ на сигнал Eq управления предварительной зарядкой. Модуль 202 управления в ответ на сигнал конфигурирования скорости чтения-записи выводит сигнал управления чтением-записью для изменения скорости чтения данных локальной схемы 2111 преобразования чтения или локальной схемы 2112 преобразования записи и т. д., тем самым корректирую скорость операции чтения-записи схемы преобразования чтения-записи.

[00125] Схема преобразования чтения-записи, предложенная в этом варианте реализации, может корректировать скорость локальной операции чтения записи, но также скорость глобальной операции чтения-записи, так что удобство коррекции скорости операции чтения-записи схемы преобразования чтения-записи дополнительно улучшается.

[00126] Соответственно, согласно варианту реализации настоящего изобретения предложена память, которая содержит вышеупомянутую схему преобразования чтения-записи.

[00127] Память может представлять собой динамическое оперативное запоминающее устройство (DRAM), статическое оперативное запоминающее устройство (Static Random-Access Memory, SRAM), магниторезистивное оперативное запоминающее устройство (Magneto resistive Random-Access Memory, MRAM), ферроэлектрическое оперативное запоминающее устройство (Ferroelectric Random-Access Memory, FeRAM), оперативное запоминающее устройство с изменением фазового состояния (Phase Change RAM, PCRAM), флэш-память NAND, флэш-память NOR или другую память. Из приведенного выше анализа можно увидеть, что память, предложенная в этом варианте реализации, имеет преимущество переменной скорости передачи данных, предъявляет низкие требования к возбуждающей способности усилителя считывания и способствует удовлетворению тенденции к миниатюризации устройства.

[00128] Специалистам в данной области могут понять, что каждый из вышеупомянутых режимов реализации представляет собой конкретный вариант реализации настоящей заявки, и что в практических применениях в них могут быть изменены формы и детали, не выходящие за пределы сущности и объема настоящего изобретения. Специалисты в данной области могут реализовать соответствующие варианты или модификации в рамках сущности и объема настоящего изобретения, и поэтому объем защиты изобретения должен быть ограничен объемом, определенным формулой изобретения.

Изобретение относится к области полупроводников, используемых в качестве схемы преобразования чтения-записи и памяти. Технический результат заключается в том, что скорость операции чтения-записи схемы преобразования чтения-записи является переменной, так что рабочие характеристики памяти улучшаются. Технический результат достигается за счет того, что схема преобразования чтения-записи также содержит усилитель считывания, локальную линию данных, локальную комплементарную линию данных, глобальную линию данных и глобальную дополнительную линию данных, а модуль преобразования чтения-записи содержит локальный блок чтения-записи и глобальный блок чтения-записи, при этом тракт данных чтения схемы преобразования чтения-записи проходит от разрядной линии и комплементарной разрядной линии к локальной линии данных и локальной комплементарной линии данных через усилитель считывания, затем к локальному блоку чтения-записи через локальную линию данных и локальную комплементарную линию данных, затем к глобальной линии данных и глобальной комплементарной линии данных через локальный блок чтения-записи и, наконец, к глобальному блоку чтения-записи через глобальную линию данных и глобальную комплементарную линию данных. 2 н. и 8 з.п. ф-лы, 7 ил.

1. Схема преобразования чтения-записи в динамическом оперативном запоминающем устройстве, содержащая:

модуль преобразования чтения-записи, выполненный с возможностью осуществления операции чтения-записи в ответ на сигнал управления чтением-записью; и

модуль управления, выполненный с возможностью вывода, в ответ на сигнал конфигурирования скорости чтения-записи, переменного сигнала управления чтением-записью для управления скоростью операции чтения-записи модуля преобразования чтения-записи в динамическом оперативном запоминающем устройстве таким образом, чтобы она была переменной,

при этом схема преобразования чтения-записи также содержит усилитель считывания, локальную линию данных, локальную комплементарную линию данных, глобальную линию данных и глобальную дополнительную линию данных, а модуль преобразования чтения-записи содержит локальный блок чтения-записи и глобальный блок чтения-записи,

при этом тракт данных чтения схемы преобразования чтения-записи проходит от разрядной линии и комплементарной разрядной линии к локальной линии данных и локальной комплементарной линии данных через усилитель считывания, затем к локальному блоку чтения-записи через локальную линию данных и локальную комплементарную линию данных, затем к глобальной линии данных и глобальной комплементарной линии данных через локальный блок чтения-записи и, наконец, к глобальному блоку чтения-записи через глобальную линию данных и глобальную комплементарную линию данных.

2. Схема преобразования чтения-записи по п. 1, также содержащая модуль конфигурирования скорости, соединенный с модулем управления и выполненный с возможностью вывода сигнала конфигурирования скорости чтения-записи в модуль управления.

3. Схема преобразования чтения-записи по п. 2, в которой сигнал управления чтением-записью содержит сигнал управления чтением и сигнал управления записью, а модуль преобразования чтения-записи выполняет операцию чтения в ответ на сигнал управления чтением и выполняет операцию записи в ответ на сигнал управления записью,

при этом модуль конфигурирования скорости содержит: блок конфигурирования скорости чтения, выполненный с возможностью вывода сигнала конфигурирования скорости чтения в сигнале конфигурирования скорости чтения-записи в модуль управления, чтобы вызвать вывод модулем управления, в ответ на сигнал конфигурирования скорости чтения, переменного сигнала управления чтением для управления скоростью операции чтения таким образом, чтобы она была переменной, и

блок конфигурирования скорости записи, выполненный с возможностью вывода сигнала конфигурирования скорости записи в сигнале конфигурирования скорости чтения-записи в модуль управления, чтобы вызвать вывод модулем управления, в ответ на сигнал конфигурирования скорости чтения, переменного сигнала управления записью для управления скоростью операции записи таким образом, чтобы она была переменной.

4. Схема преобразования чтения-записи по п. 1, в которой во время операции чтения-записи выполняется передача данных между каждой из локальной линии данных и локальной комплементарной линии данных и глобальной линией данных, а сигналы данных локальной линии данных и локальной комплементарной линии данных противоположны по фазе.

5. Схема преобразования чтения-записи по п. 4, в которой локальный блок чтения-записи выполнен с возможностью

осуществления локальной операции чтения-записи в ответ на локальный сигнал управления чтением-записью в сигнале управления чтением-записью; а

модуль управления содержит локальный блок управления, выполненный с возможностью вывода, в ответ на локальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменного локального сигнала управления чтением-записью для управления скоростью локальной операции чтения-записи локального блока управления чтением-записью таким образом, чтобы она была переменной,

причем схема преобразования чтения-записи также содержит локальный модуль конфигурирования скорости, соединенный с локальным блоком управления и выполненный с возможностью вывода локального сигнала конфигурирования скорости чтения-записи в локальный блок управления, или

в котором усилитель считывания соединен с локальным блоком чтения-записи посредством локальной линии данных и локальной комплементарной линии данных и выполненный с возможностью считывания напряжения разрядной линии.

6. Схема преобразования чтения-записи по п. 5, в которой один и тот же локальный блок чтения-записи соединен с множеством усилителей считывания посредством локальной линии данных и локальной комплементарной линии данных.

7. Схема преобразования чтения-записи по п. 5, в которой тракт данных записи проходит от локального блока чтения-записи к усилителю считывания через локальную линию данных и локальную комплементарную линию данных, а затем к разрядной линии через усилитель считывания.

8. Схема преобразования чтения-записи по п. 4, в которой глобальный блок чтения-записи выполнен с возможностью

осуществления глобальной операции чтения-записи в ответ на глобальный сигнал управления чтением-записью; а

модуль управления содержит глобальный блок управления, выполненный с возможностью вывода, в ответ на глобальный сигнал конфигурирования скорости чтения-записи в сигнале конфигурирования скорости чтения-записи, переменного глобального сигнала управления чтением-записью в сигнале управления чтением-записью для управления скоростью глобальной операции чтения-записи глобального блока управления чтением-записью таким образом, чтобы она была переменной,

причем схема преобразования чтения-записи также содержит глобальный модуль конфигурирования скорости, соединенный с глобальным блоком управления и выполненный с возможностью вывода глобального сигнала конфигурирования скорости чтения-записи в глобальный блок управления.

9. Схема преобразования чтения-записи по п. 5, в которой локальный блок чтения-записи содержит локальный усилитель, подсоединенный между локальной линией данных и локальной комплементарной линией данных и выполненный с возможностью усиления данных локальной линии данных и данных локальной комплементарной линии данных,

причем локальный усилитель содержит: первый фазоинвертор, в котором первый вход первого фазоинвертора электрически соединен с локальной линией данных, а первый выход первого фазоинвертора электрически соединен с локальной комплементарной линией данных; и

второй фазоинвертор, в котором второй вход второго фазоинвертора электрически соединен с первым выходом первого фазоинвертора и локальной комплементарной линией данных, а второй выход второго фазоинвертора электрически соединен с первым входом первого фазоинвертора и локальной линией данных, при этом первый фазоинвертор содержит первый транзистор на структуре металл-оксид-полупроводник с каналом p-типа (рМОП) и первый транзистор на структуре металл-оксид-полупроводник с каналом n-типа (nМОП),

причем затвор первого pМОП-транзистора соединен с затвором первого nМОП-транзистора, чтобы служить в качестве первого входа первого фазоинвертора, исток первого pМОП-транзистора соединен с рабочим питанием, а сток первого pМОП-транзистора соединен со стоком первого nМОП-транзистора, чтобы служить в качестве первого выхода первого фазоинвертора;

при этом второй фазоинвертор содержит нулевой рМОП-транзистор и нулевой nМОП-транзистор,

причем затвор нулевого pМОП-транзистора соединен с затвором нулевого nМОП-транзистора, чтобы служить в качестве второго входа второго фазоинвертора, исток нулевого pМОП-транзистора соединен с рабочим питанием, а сток нулевого pМОП-транзистора соединен со стоком нулевого nМОП-транзистора, чтобы служить в качестве второго выхода второго фазоинвертора.

10. Память, содержащая схему преобразования чтения-записи по любому из пп. 1-9.

| US 6212109 B1, 03.04.2001 | |||

| US 7379347 B1, 27.05.2008 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| US 9548105 B1, 17.01.2017 | |||