Изобретение относится к области радиоавтоматики и может быть использовано в радиотехнических устройствах и системах связи различного назначения для повышения стабильности частот и синхронизации приемной и передающей аппаратуры.

Системы фазовой автоподстройки частоты (ФАПЧ) имеют широкую область применения в технике связи. Их проектирование часто сводится к выбору структуры системы и ее параметров при заданных исходных данных и условиях применения так, чтобы она наилучшим образом удовлетворяла требуемым критериям. Широкое распространение получили отличающиеся хорошими фильтрующими свойствами системы ФАПЧ, которые описываются нелинейными дифференциальными уравнениями второго и более высоких порядков. При их построении основное внимание уделяют решению проблемы определения условий устойчивости требуемого режима, а также качественных характеристик процесса его установления. В технических приложениях функционирование систем управления связано с разрешением структурной неопределенности, которая проявляется в результате пересечений областей фазового пространства с нечеткими границами. Эффективным математическим аппаратом синтеза систем управления с ограниченной степенью неполноты информации о характеристиках объекта управления является нечеткая логика. В отличие от известных решений в работе предлагается в заключении продукционных правил использовать управления, синтезированные на основе условия максимума функции обобщенной мощности.

Известно устройство фазовой автоподстройки частоты (ФАПЧ) (см. патент RU № 2547635, МПК H03L 7/06, опубл. 10.04.2015), где ЭГ - эталонный генератор, УЭ - управляющий элемент, ПГ - подстраиваемый генератор, ФД - фазовый детектор, ФНЧ - фильтр нижних частот.

Наиболее близким техническим решением является многорежимное устройство синхронизации с адаптацией (ФАПЧ) (см. патент RU № 2713726, МПК H03L 7/06, опубл. 07.02.2020), содержащее блок формирования суммы (9), со вторым входом которого соединен вход устройства, который соединен с входом блока формирования модуля (2), вторым входом блока формирования произведения (7) и входом блока формирования линии задержки (1), выход которого соединен с четвертым входом блока формирования произведения (8) и входом блока формирования модуля (3), выход которого соединен с третьим входом блока (8), выход которого соединен с первым входом блока формирования отношения (12) и первым входом блока формирования отношения (11), выход которого соединен со вторым входом блока формирования суммы (15), выход которого соединен с входом блока формирования функции sign (22), выход которого соединен с четвертым входом блока формирования произведения (21), выход которого соединен с первым входом блока формирования суммы (25), выход которого является выходом устройства, первый выход блока хранения констант (6) соединен со вторым входом блока формирования суммы (5), выход которого соединен со вторым входом блока (12), выход которого соединен со вторым входом блока формирования суммы (18), выход которого соединен с третьим входом блока формирования произведения (24), выход которого соединен со вторым входом блока (25), второй выход блока хранения констант (6) соединен со вторым входом блока формирования произведения (17) и с первым входом блока формирования произведения (4), выход которого соединен со вторым входом блока (11), третий выход блока хранения констант (6) соединен с первым входом блока (8) и входом блока формирования возведения в «-1» степень (10), выход которого соединен с третьим входом блока (21) и вторым входом блока (24), четвертый выход блока хранения констант (6) соединен с первым входом блока (9), выход которого соединен со вторым входом блока формирования произведения (13), выход которого соединен с входом блока формирования экспоненты (14), выход которого соединен со вторым входом блока формирования суммы (16), выход которого соединен со вторым входом блока формирования отношения (19), выход которого соединен с первым входом блока формирования произведения (20) и вторым входом блока (21), пятый выход блока хранения констант (6) соединен с первым входом блока (13), вторым входом блока (20), вторым входом блока (18) и первым входом блока формирования произведения (7), выход которого соединен с пятым входом блока (8), с первым входом блока (15) и первым входом блока формирования произведения (17), выход которого соединен с первым входом блока (18), шестой выход блока хранения констант (6) соединен с первым входом блока (16), первым входом блока (19) и первым входом блока формирования суммы (23), выход которого соединен с первым входом блока (24), выход семь блока (6) соединен с первым входом блока (21), выход блока (2) соединен со вторым входом блока (4) и первым входом блока (5), выход блока (20) соединен со вторым входом блока (23).

Однако у данного устройства низкое быстродействие в условиях априорно неизвестных внешних воздействий.

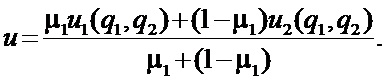

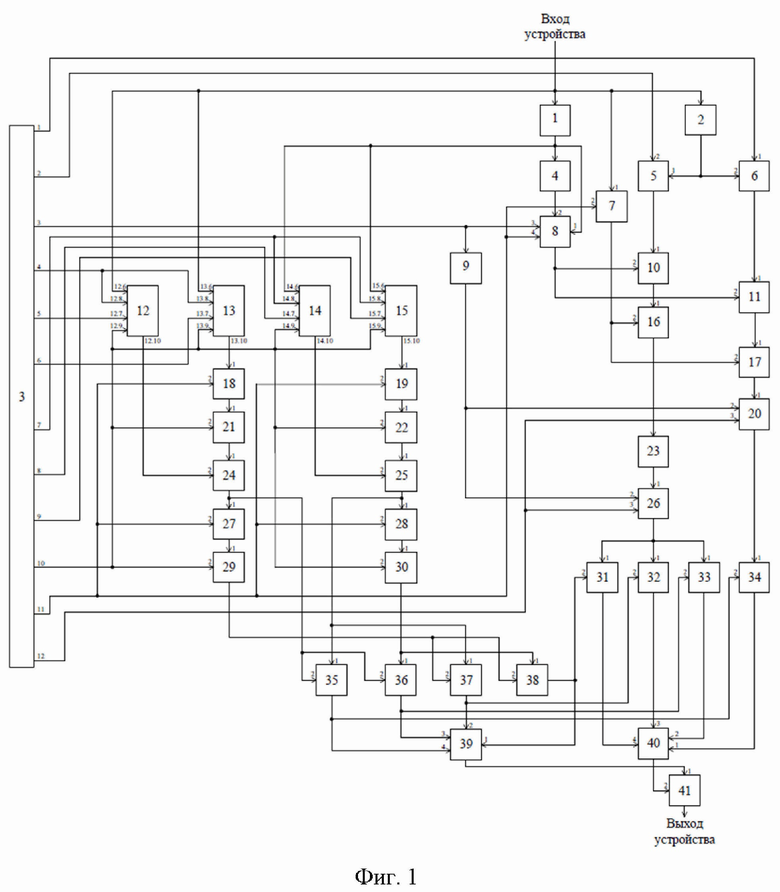

Сущность изобретения заключается в том, что устройство синхронизации с нечетким контроллером, содержащее вход устройства соединенный со входом (12.6) блока (12) расчета функции принадлежности, входом (13.6) блока (13) расчета функции принадлежности, входом блока (1) формирования задержки, первым входом блока (7) формирования произведения и входом блока (2) формирования модуля, выход которого соединен с первым входом блока (5) формирования суммы и вторым входом блока (6) формирования суммы, выход которого соединен с первым входом блока (11) формирования отношения, выход которого соединен с первым входом блока (17) формирования суммы, выход которого соединен с первым входом блока (20) формирования произведения, выход которого соединен с первым входом блока (34) формирования произведения, выход которого соединен с первым входом блока (40) формирования суммы, выход которого соединен со вторым входом блока (41) формирования отношения, выход которого является выходом устройства, первый выход блока (3) хранения констант соединен с первым входом блока 6, второй выход блока (3) соединен со вторым входом блока (5), выход которого соединен с первым входом блока (10) формирования отношения, выход которого соединен с первым входом блока (16) формирования суммы, выход которого соединен со входом блока (23) формирования функции sign, выход которого соединен с первым входом блока (26) формирования произведения, выход которого соединен с первым входом блока (31) формирования произведения, с первым входом блока (32) формирования произведения и первым входом блока (33) формирования произведения, выход которого соединен со вторым входом блока (40), третий выход блока (3) соединен со входом блока (9) возведения в степень «-1» и третьим входом блока (8) формирования произведения, выход которого соединен со вторым входом блока (11) и вторым входом блока (10), четвертый выход блока (3) соединен со входом (12.8) блока (12) и входом (13.8) блока (13), выход которого соединен с первым входом блока (18) формирования произведения, выход которого соединен с первым входом блока (21) формирования суммы, выход которого соединен с первым входом блока (24) формирования функции min, выход которого соединен с первым входом блока (27) формирования произведения, вторым входом блока (36) формирования произведения и вторым входом блока (35) формирования произведения, выход которого соединен со вторым входом блока (34) и четвертым входом блока (39) формирования суммы, выход которого соединен с первым входом блока (41), пятый выход блока (3) соединен со входом (12.7) блока (12), выход которого соединен со вторым входом блока (24), шестой выход блока (3) соединен со входом (13.7) блока (13), седьмой выход блока (3) соединен со входом (14.8) блока (14) расчета функции принадлежности и входом (15.8) блока (15) расчета функции принадлежности, выход которого соединен с первым входом блока (19) формирования произведения, выход которого соединен с первым входом блока (22) формирования суммы, выход которого соединен с первым входом блока (25) формирования функции min, выход которого соединен с первым входом блока (35), первым входом блока (37) формирования произведения и первым входом блока (28) формирования произведения, выход которого соединен с первым входом блока (30) формирования суммы, выход которого соединен с первым входом блока (36) и первым входом блока (38) формирования произведения, выход которого соединен с первым входом блока (39) и вторым входом блока (31), выход которого соединен с четвертым входом блока (40), восьмой выход блока (3) соединен со входом (14.7) блока (14), выход которого соединен со вторым входом блока (25), девятый выход блока (3) соединен со входом (15.7) блока (15), десятый выход блока (3) соединен со входом (12.9) блока (12), входом (13.9) блока (13), входом (14.9) блока (14), входом (15.9) блока (15), вторым входом блока (21), вторым входом блока (22), вторым входом блока (30) и вторым входом блока (29) формирования суммы, выход которого соединен со вторым входом блока (38) и вторым входом блока (37), выход которого соединен со вторым входом блока (39) и вторым входом блока (32), выход которого соединен с третьим входом блока (40), одиннадцатый выход блока (3) соединен с четвертым входом блока (8), вторым входом блока (18), вторым входом блока (19), вторым входом блока (27), вторым входом блока (28) и вторым входом блока (7), выход которого соединен со вторым входом блока (16) и вторым входом блока (17), двенадцатый выход блока (3) соединен с третьим входом блока (20) и третьим входом блока (26), выход блока (27) соединен с первым входом блока (29), выход блока (9) соединен со вторым входом блока (20) и вторым входом блока (26), выход блока (36) соединен с третьим входом блока (39) и вторым входом блока (33), выход блока (1) соединен с входом (14.6) блока (14), входом (15.6) блока (15), первым входом блока (8) и входом блока (4) формирования модуля, выход которого соединен со вторым входом блока (8), при этом вход (12.6) соединен с первым входом блока (12.1) формирования суммы, выход которого соединен с первым входом блока (12.2) формирования произведения, выход которого соединен со входом блока (12.3) формирования экспоненты, выход которого соединен с первым входом блока (12.4) формирования суммы, выход которого соединен с первым входом блока (12.5) формирования отношения, выход которого является выходом блок расчёта функций принадлежности (12.10), вход (12.7) соединен со вторым входом блока (12.1), вход (12.8) соединен со вторым входом блока (12.2), вход (12.9) соединен со вторым входом блока (12.4) и вторым входом блока (12.5).

Технической задачей изобретения является повышение быстродействия за счет выбора нечётких режимов функционирования по фазе и частоте.

Указанная техническая задача достигается за счет реализации устройства контура фазовой автоподстройки частоты с обратной связью на основе объединенного принципа максимума и нечётко-логического вывода.

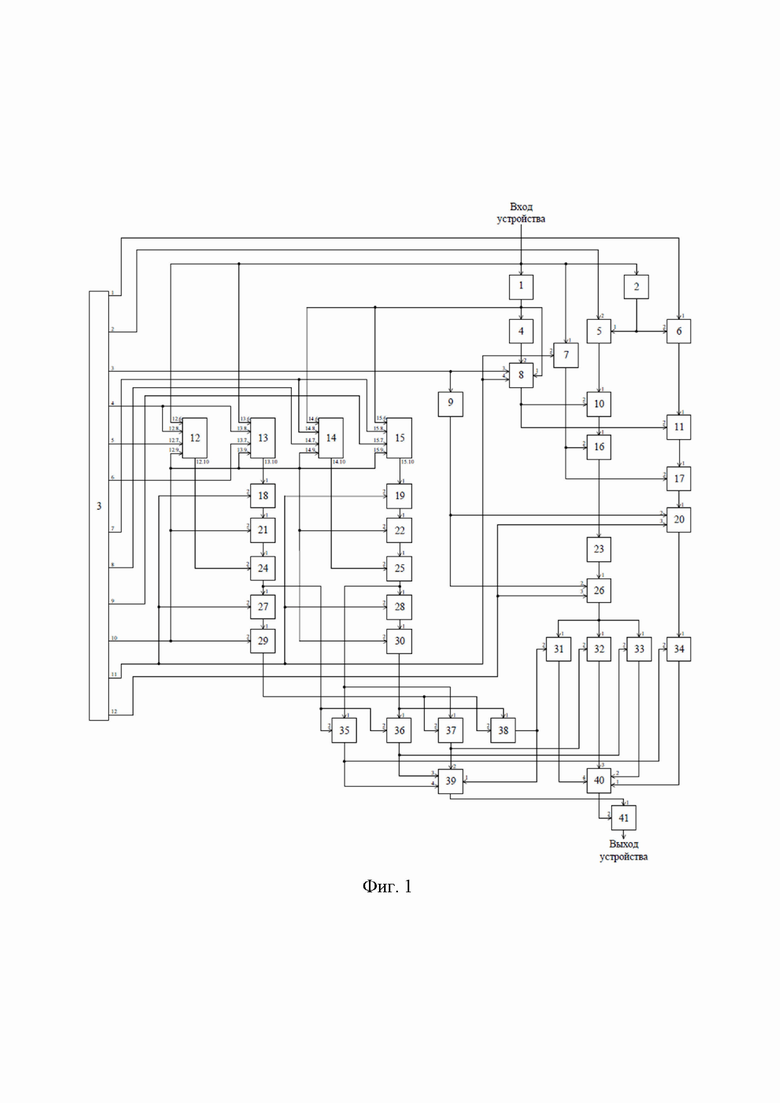

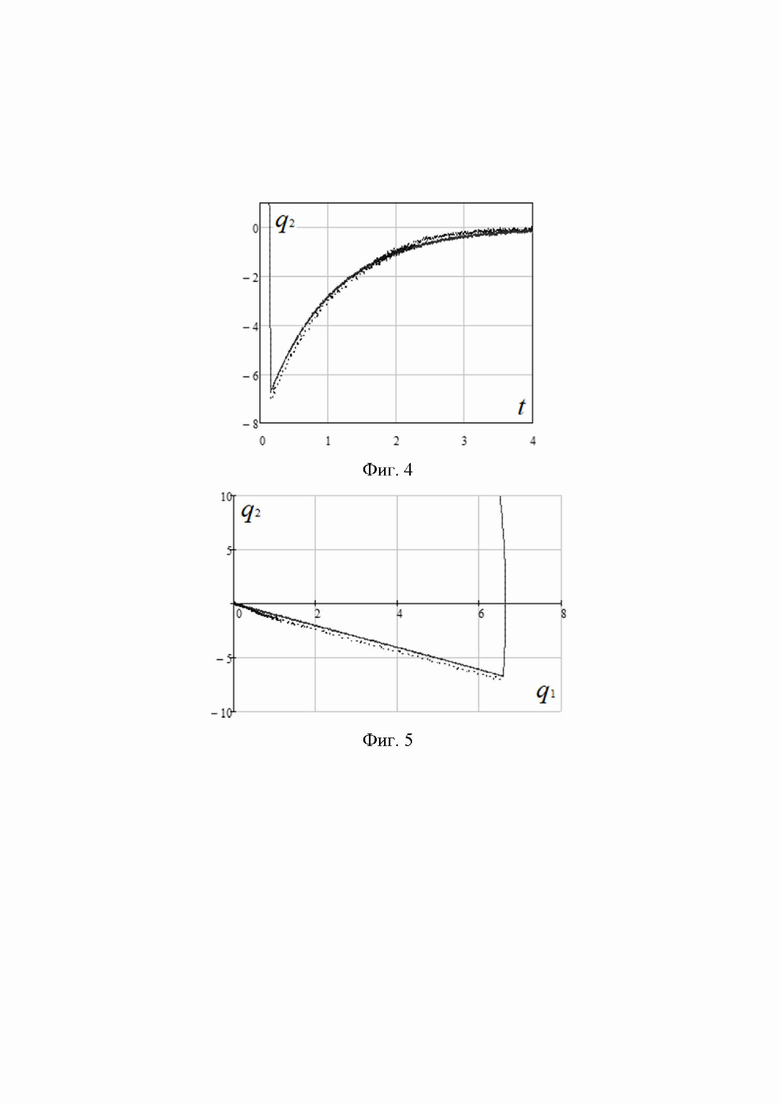

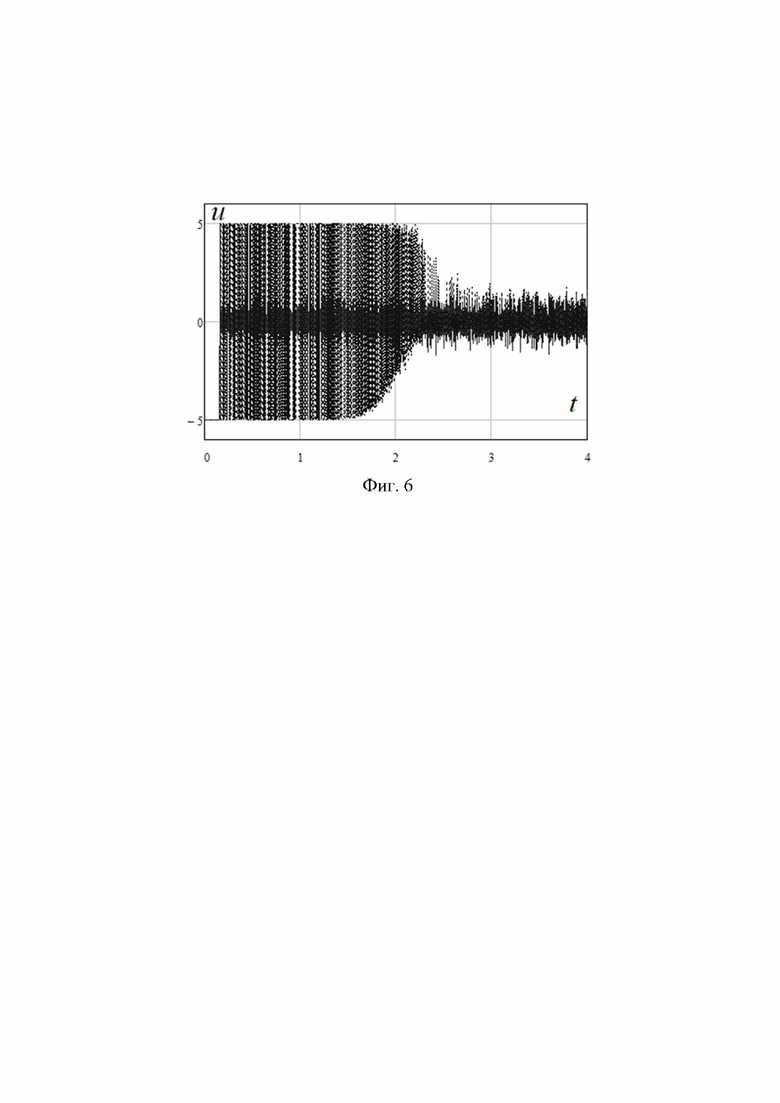

Сущность изобретения поясняется чертежом, где на

фиг. 1 - изображена схема устройства синхронизации с нечетким контроллером;

фиг. 2 - структура блока расчета функций принадлежности;

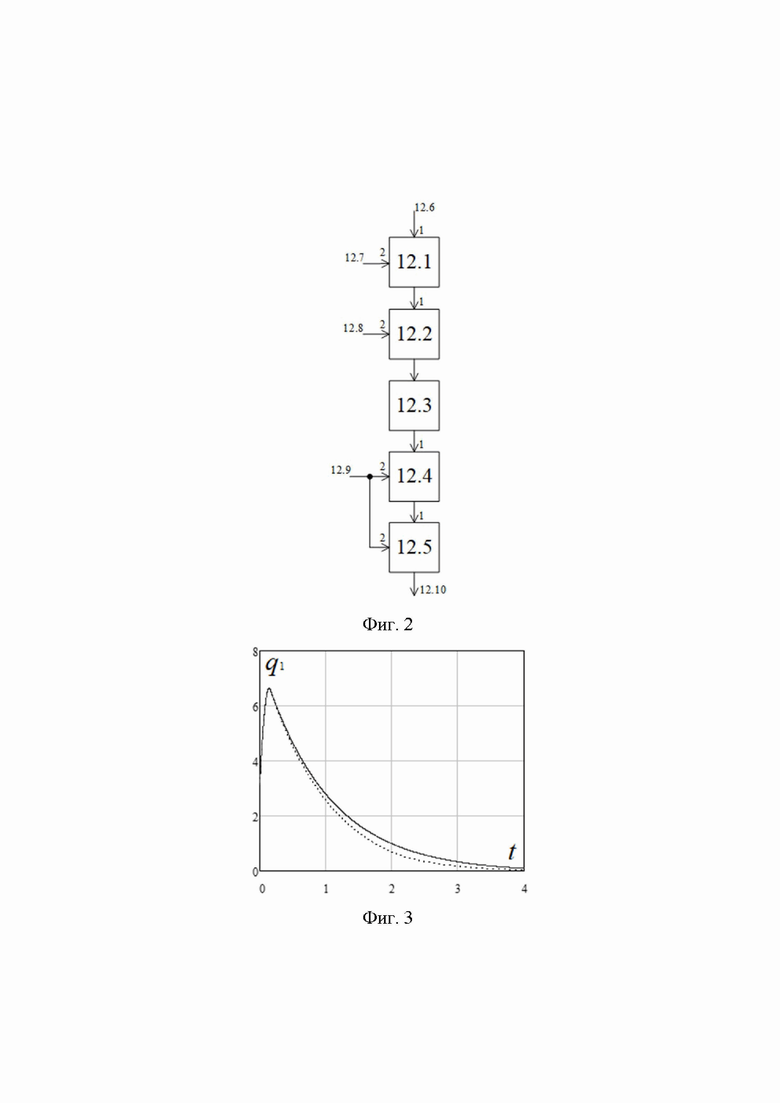

фиг. 3 - динамика процесса захвата по фазе;

фиг. 4 - динамика процесса захвата по частоте;

фиг. 5 - фазовый портрет процесса;

фиг. 6 - обратная связь на основе нечёткого контроллера.

Устройство синхронизации содержит блок формирования задержки 1; блоки формирования модуля 2, 4; блок хранения констант 3; блоки формирования суммы 5, 6, 16, 17, 21, 22, 29, 30, 39, 40; блоки формирования произведения 7, 8, 18, 19, 20, 26, 27, 28, 31, 32, 33, 34, 35, 36, 37, 38; блок возведения в степень «-1» 9; блоки формирования отношения 10, 11, 41; блоки расчёта функций принадлежности 12, 13, 14, 15; блок формирования функции sign 23; блоки формирования функции min 24, 25.

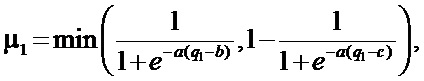

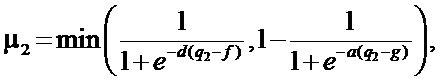

В свою очередь, блок расчёта функций принадлежности 12 имеет структуру, представленную на фиг. 2, которая состоит из блоков формирования суммы 12.1 и 12.4, блока формирования произведения 12.2, блока формирования экспоненты 12.3 и блока формирования отношения 12.5. Также блок расчета функции принадлежности имеет входы 12.6, 12.7, 12.8, 12.9 и выход 12.10. Блоки расчёта функций принадлежности 13, 14, 15 имеют идентичную структуру.

Результаты математического моделирования приведены на фигуре 3, 4, 5, 6, где сплошной линией обозначены кривые, соответствующие управлению (11), пунктирной линией кривые, соответствующие управлению (6).

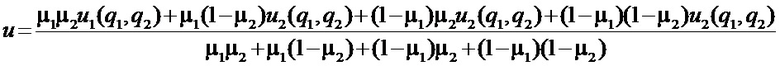

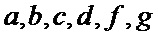

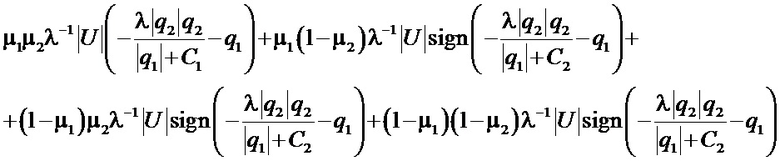

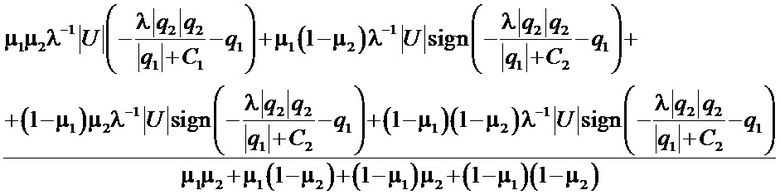

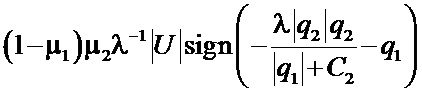

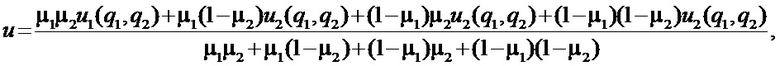

Работа устройства поясняется выражением:

где

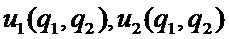

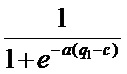

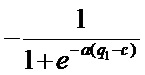

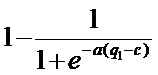

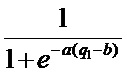

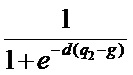

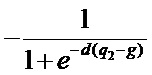

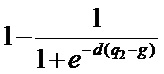

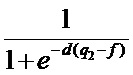

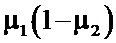

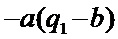

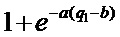

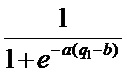

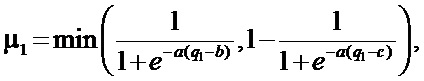

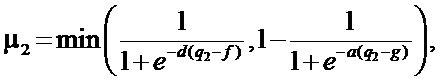

Функции принадлежности имеют форму

где

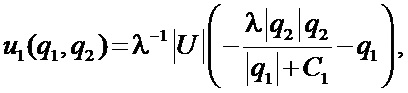

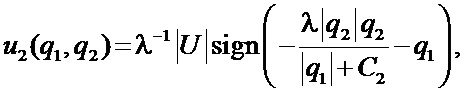

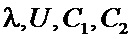

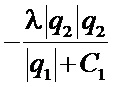

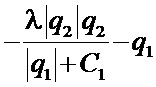

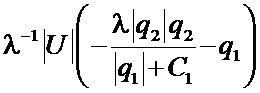

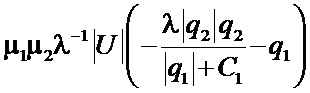

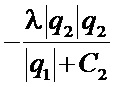

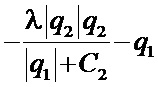

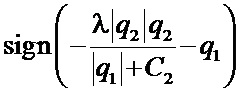

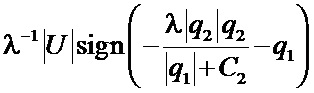

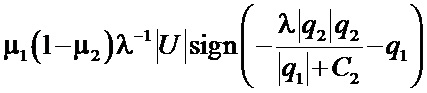

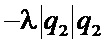

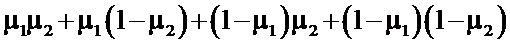

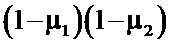

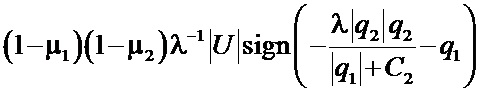

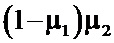

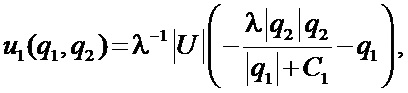

Режимы управления имеют форму

где

Устройство работает следующим образом: в момент времени

Блок расчёта функции принадлежности, изображенный на фиг. 2 работает следующим образом: каждый такт со входа 12.6 значение

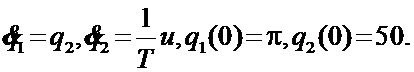

Пример. Рассматривается заданная с точностью до обратной связи система ФАПЧ в безразмерных величинах

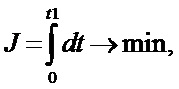

Требуется синтезировать ФАПЧ из условия минимума целевого функционала

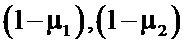

при ограничении

Использование условий максимума функции обобщенной мощности позволяет получить квазиоптимальное решение задачи синтеза [1 - 5] на нечеткой границе области допустимых управлений, которая определяется выбором функций принадлежности

Предлагается структура нечеткого управления

Для сравнения выбран вариант управления:

Анализ представленных результатов позволяет сделать вывод о том, что модификация нечётко-логического вывода в системе ФАПЧ с нечётким контроллером позволяет повысить скорость достижения терминальной точки. Расчеты показывают, что полученный результат выигрывает по быстродействию на 16.5% в сравнении с прототипом. Результаты, приведенные в примере, позволяют сделать заключение о достижении заявленного технического результата.

Литература

1. Патент № 2713726 C1 Российская Федерация, МПК H03L 7/06. Многорежимное устройство синхронизации с адаптацией : № 2019118698 : заявл. 17.06.2019 : опубл. 07.02.2020 / А. А. Костоглотов, С. В. Лазаренко, И. В. Пугачев [и др.].

2 Kostoglotov, A. A. Synthesis of adaptive tracking systems based on the hypothesis of stationarity of the Hamiltonian on the switching hypersurface / A. A. Kostoglotov, S. V. Lazarenko // Journal of Communications Technology and Electronics. - 2017. - Vol. 62, No. 2. - P. 123-127.

3. Kostoglotov, A. A. Joint maximum principle in the problem of synthesizing an optimal control of nonlinear systems / A. A. Kostoglotov, A. I. Kostoglotov, S. V. Lazarenko // Automatic Control and Computer Sciences. - 2007. - Vol. 41, No. 5. - P. 274-281.

4. Kostoglotov, A. Fuzzy Control Laws in the Basis of Solutions of Synthesis Problems of the Combined Maximum Principle / A. Kostoglotov, S. Lazarenko, I. Derabkin, A. Kuzin, I. Pugachev, O. Manaenkova // Advances in Intelligent Systems and Computing. - 2017. - Vol. 679. - P. 321-329.

5. Synthesis of Phase-locked Loop System Structure with Adaptation Based on Combined-maximum Principle / A. A. Kostoglotov, I. V. Deryabkin, S. V. Lazarenko, D. S. Andrashitov // MATEC Web of Conferences: 2016 3rd International Conference on Mechanics and Mechatronics Research, ICMMR 2016, Chongqing, Vol. 77. - Chongqing: EDP Sciences, 2016. - P. 15002.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТУРА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ С ОБРАТНОЙ СВЯЗЬЮ НА ОСНОВЕ ОБЪЕДИНЕННОГО ПРИНЦИПА МАКСИМУМА | 2013 |

|

RU2547635C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ БОРТОВЫХ СИСТЕМ ЛЕТАТЕЛЬНЫХ АППАРАТОВ ПО РЕЗУЛЬТАТАМ ОЦЕНКИ ПАРАМЕТРОВ | 2013 |

|

RU2544765C1 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ С АДАПТАЦИЕЙ | 2019 |

|

RU2713726C1 |

| Устройство для распознавания образов | 1987 |

|

SU1531115A1 |

| Способ и устройство для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ | 2018 |

|

RU2709125C2 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| УСТРОЙСТВО ИДЕНТИФИКАЦИИ ЛАГРАНЖЕВЫХ ДИНАМИЧЕСКИХ СИСТЕМ НА ОСНОВЕ ИТЕРАЦИОННОЙ РЕГУЛЯРИЗАЦИИ | 2013 |

|

RU2528133C1 |

| МЯГКИЙ ДЕКОДЕР ПОСЛЕДОВАТЕЛЬНОГО ТУРБОКОДА | 2013 |

|

RU2538331C2 |

| ТРАНСПОРТНОЕ СРЕДСТВО С СИСТЕМОЙ ИДЕНТИФИКАЦИИ | 2009 |

|

RU2531115C2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МЕСТОПОЛОЖЕНИЯ ОБЪЕКТА ПРИ ИСПОЛЬЗОВАНИИ ГЛОБАЛЬНЫХ НАВИГАЦИОННЫХ СПУТНИКОВЫХ СИСТЕМ И СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2492499C1 |

Изобретение относится к области радиоавтоматики. Технический результат заключается в повышении скорости фазовой синхронизации за счет выбора нечётких режимов функционирования по фазе и частоте. Устройство синхронизации с нечетким контроллером, содержит блок формирования задержки, блоки формирования модуля, блок хранения констант, блоки формирования суммы, блоки формирования произведения, блок возведения в степень «-1», блоки формирования отношения, блоки расчёта функций принадлежности, блок формирования функции sign, блоки формирования функции min. 6 ил.

Устройство синхронизации с нечетким контроллером, содержащее вход устройства соединенный со входом (12.6) блока (12) расчета функции принадлежности, входом (13.6) блока (13) расчета функции принадлежности, входом блока (1) формирования задержки, первым входом блока (7) формирования произведения и входом блока (2) формирования модуля, выход которого соединен с первым входом блока (5) формирования суммы и вторым входом блока (6) формирования суммы, выход которого соединен с первым входом блока (11) формирования отношения, выход которого соединен с первым входом блока (17) формирования суммы, выход которого соединен с первым входом блока (20) формирования произведения, выход которого соединен с первым входом блока (34) формирования произведения, выход которого соединен с первым входом блока (40) формирования суммы, выход которого соединен со вторым входом блока (41) формирования отношения, выход которого является выходом устройства, первый выход блока (3) хранения констант соединен с первым входом блока 6, второй выход блока (3) соединен со вторым входом блока (5), выход которого соединен с первым входом блока (10) формирования отношения, выход которого соединен с первым входом блока (16) формирования суммы, выход которого соединен со входом блока (23) формирования функции sign, выход которого соединен с первым входом блока (26) формирования произведения, выход которого соединен с первым входом блока (31) формирования произведения, с первым входом блока (32) формирования произведения и первым входом блока (33) формирования произведения, выход которого соединен со вторым входом блока (40), третий выход блока (3) соединен со входом блока (9) возведения в степень «-1» и третьим входом блока (8) формирования произведения, выход которого соединен со вторым входом блока (11) и вторым входом блока (10), четвертый выход блока (3) соединен со входом (12.8) блока (12) и входом (13.8) блока (13), выход которого соединен с первым входом блока (18) формирования произведения, выход которого соединен с первым входом блока (21) формирования суммы, выход которого соединен с первым входом блока (24) формирования функции min, выход которого соединен с первым входом блока (27) формирования произведения, вторым входом блока (36) формирования произведения и вторым входом блока (35) формирования произведения, выход которого соединен со вторым входом блока (34) и четвертым входом блока (39) формирования суммы, выход которого соединен с первым входом блока (41), пятый выход блока (3) соединен со входом (12.7) блока (12), выход которого соединен со вторым входом блока (24), шестой выход блока (3) соединен со входом (13.7) блока (13), седьмой выход блока (3) соединен со входом (14.8) блока (14) расчета функции принадлежности и входом (15.8) блока (15) расчета функции принадлежности, выход которого соединен с первым входом блока (19) формирования произведения, выход которого соединен с первым входом блока (22) формирования суммы, выход которого соединен с первым входом блока (25) формирования функции min, выход которого соединен с первым входом блока (35), первым входом блока (37) формирования произведения и первым входом блока (28) формирования произведения, выход которого соединен с первым входом блока (30) формирования суммы, выход которого соединен с первым входом блока (36) и первым входом блока (38) формирования произведения, выход которого соединен с первым входом блока (39) и вторым входом блока (31), выход которого соединен с четвертым входом блока (40), восьмой выход блока (3) соединен со входом (14.7) блока (14), выход которого соединен со вторым входом блока (25), девятый выход блока (3) соединен со входом (15.7) блока (15), десятый выход блока (3) соединен со входом (12.9) блока (12), входом (13.9) блока (13), входом (14.9) блока (14), входом (15.9) блока (15), вторым входом блока (21), вторым входом блока (22), вторым входом блока (30) и вторым входом блока (29) формирования суммы, выход которого соединен со вторым входом блока (38) и вторым входом блока (37), выход которого соединен со вторым входом блока (39) и вторым входом блока (32), выход которого соединен с третьим входом блока (40), одиннадцатый выход блока (3) соединен с четвертым входом блока (8), вторым входом блока (18), вторым входом блока (19), вторым входом блока (27), вторым входом блока (28) и вторым входом блока (7), выход которого соединен со вторым входом блока (16) и вторым входом блока (17), двенадцатый выход блока (3) соединен с третьим входом блока (20) и третьим входом блока (26), выход блока (27) соединен с первым входом блока (29), выход блока (9) соединен со вторым входом блока (20) и вторым входом блока (26), выход блока (36) соединен с третьим входом блока (39) и вторым входом блока (33), выход блока (1) соединен с входом (14.6) блока (14), входом (15.6) блока (15), первым входом блока (8) и входом блока (4) формирования модуля, выход которого соединен со вторым входом блока (8), при этом вход (12.6) соединен с первым входом блока (12.1) формирования суммы, выход которого соединен с первым входом блока (12.2) формирования произведения, выход которого соединен со входом блока (12.3) формирования экспоненты, выход которого соединен с первым входом блока (12.4) формирования суммы, выход которого соединен с первым входом блока (12.5) формирования отношения, выход которого является выходом блок расчёта функций принадлежности (12.10), вход (12.7) соединен со вторым входом блока (12.1), вход (12.8) соединен со вторым входом блока (12.2), вход (12.9) соединен со вторым входом блока (12.4) и вторым входом блока (12.5).

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ С АДАПТАЦИЕЙ | 2019 |

|

RU2713726C1 |

| УСТРОЙСТВО КОНТУРА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ С ОБРАТНОЙ СВЯЗЬЮ НА ОСНОВЕ ОБЪЕДИНЕННОГО ПРИНЦИПА МАКСИМУМА | 2013 |

|

RU2547635C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЭНЕРГОРАЙОНА С СЕТЬЮ ЭНЕРГОСИСТЕМЫ | 2022 |

|

RU2789163C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

Авторы

Даты

2023-12-27—Публикация

2023-06-16—Подача